Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 41.667MHz                                                                   |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 55                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3808 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 15x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-TQFP                                                                     |

| Supplier Device Package    | 80-TQFP (12x12)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f87j60t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| File Name | Bit 7        | Bit 6                              | Bit 5         | Bit 4          | Bit 3                         | Bit 2         | Bit 1  | Bit 0  | Values on<br>POR, BOR | Details on<br>Page: |  |  |  |

|-----------|--------------|------------------------------------|---------------|----------------|-------------------------------|---------------|--------|--------|-----------------------|---------------------|--|--|--|

| ESTAT     | _            | BUFER                              | _             | r              | _                             | RXBUSY        | TXABRT | PHYRDY | -0-0 -000             | 73, 228             |  |  |  |

| EIE       | _            | PKTIE                              | DMAIE         | LINKIE         | LINKIE TXIE – TXERIE RXERIE - |               |        |        |                       |                     |  |  |  |

| EDMACSH   | DMA Checks   | 0000 0000                          | 73, 265       |                |                               |               |        |        |                       |                     |  |  |  |

| EDMACSL   | DMA Checks   | MA Checksum Register Low Byte      |               |                |                               |               |        |        |                       |                     |  |  |  |

| EDMADSTH  | _            | DMA Destination Register High Byte |               |                |                               |               |        |        |                       |                     |  |  |  |

| EDMADSTL  | DMA Destina  | ation Register                     | Low Byte      | •              |                               |               |        |        | 0000 0000             | 73, 265             |  |  |  |

| EDMANDH   | _            | _                                  | _             | DMA End Re     | gister High By                | rte           |        |        | 0 0000                | 73, 265             |  |  |  |

| EDMANDL   | DMA End Re   | egister Low By                     | te            | •              |                               |               |        |        | 0000 0000             | 73, 265             |  |  |  |

| EDMASTH   | _            | _                                  | _             | DMA Start Re   | egister High B                | yte           |        |        | 0 0000                | 73, 265             |  |  |  |

| EDMASTL   | DMA Start R  | egister Low B                      | /te           | •              |                               |               |        |        | 0000 0000             | 73, 265             |  |  |  |

| ERXWRPTH  | _            | _                                  | _             | Receive Buffe  | er Write Pointe               | er High Byte  |        |        | 0 0000                | 73, 225             |  |  |  |

| ERXWRPTL  | Receive Buff | fer Write Point                    | er Low Byte   |                |                               |               |        |        | 0000 0000             | 73, 225             |  |  |  |

| ERXRDPTH  | —            | —                                  | —             | Receive Buffe  | er Read Pointe                | er High Byte  |        |        | 0 0101                | 73, 225             |  |  |  |

| ERXRDPTL  | Receive Buff | fer Read Point                     | er Low Byte   |                |                               |               |        |        | 1111 1010             | 73, 225             |  |  |  |

| ERXNDH    | _            | _                                  | —             | Receive End    | Register High                 | Byte          |        |        | 1 1111                | 73, 225             |  |  |  |

| ERXNDL    | Receive End  | Register Low                       | Byte          |                |                               |               |        |        | 1111 1111             | 73, 225             |  |  |  |

| ERXSTH    | _            | _                                  | —             | Receive Star   | t Register Higl               | n Byte        |        |        | 0 0101                | 73, 225             |  |  |  |

| ERXSTL    | Receive Star | rt Register Lov                    | v Byte        | •              |                               |               |        |        | 1111 1010             | 73, 225             |  |  |  |

| ETXNDH    | _            | _                                  | _             | Transmit End   | Register High                 | n Byte        |        |        | 0 0000                | 74, 226             |  |  |  |

| ETXNDL    | Transmit En  | d Register Lov                     | v Byte        |                |                               |               |        |        | 0000 0000             | 74, 226             |  |  |  |

| ETXSTH    | _            | _                                  | _             | Transmit Star  | t Register Hig                | h Byte        |        |        | 0 0000                | 74, 226             |  |  |  |

| ETXSTL    | Transmit Sta | rt Register Lov                    | w Byte        |                |                               |               |        |        | 0000 0000             | 74, 226             |  |  |  |

| EWRPTH    | _            | _                                  | _             | Buffer Write F | Pointer High B                | yte           |        |        | 0 0000                | 74, 223             |  |  |  |

| EWRPTL    | Buffer Write | Pointer Low B                      | yte           |                |                               |               |        |        | 0000 0000             | 74, 223             |  |  |  |

| EPKTCNT   | Ethernet Pac | cket Count Re                      | gister        |                |                               |               |        |        | 0000 0000             | 74, 252             |  |  |  |

| ERXFCON   | UCEN         | ANDOR                              | CRCEN         | PMEN           | MPEN                          | HTEN          | MCEN   | BCEN   | 1010 0001             | 74, 260             |  |  |  |

| EPMOH     | —            | _                                  | _             | Pattern Matc   | h Offset Regis                | ter High Byte |        |        | 0 0000                | 74, 263             |  |  |  |

| EPMOL     | Pattern Mato | ch Offset Regis                    | ster Low Byte |                |                               |               |        |        | 0000 0000             | 74, 263             |  |  |  |

| EPMCSH    | Pattern Mato | ch Checksum I                      | Register High | Byte           |                               |               |        |        | 0000 0000             | 74, 263             |  |  |  |

| EPMCSL    | Pattern Mato | ch Checksum I                      | Register Low  | Byte           |                               |               |        |        | 0000 0000             | 74, 263             |  |  |  |

| EPMM7     | Pattern Mate | h Mask Regis                       | ter Byte 7    |                |                               |               |        |        | 0000 0000             | 74, 263             |  |  |  |

| EPMM6     | Pattern Mate | h Mask Regis                       | ter Byte 6    |                |                               |               |        |        | 0000 0000             | 74, 263             |  |  |  |

| EPMM5     | Pattern Mate | h Mask Regis                       | ter Byte 5    |                |                               |               |        |        | 0000 0000             | 74, 263             |  |  |  |

| EPMM4     | Pattern Mato | h Mask Regis                       | ter Byte 4    |                |                               |               |        |        | 0000 0000             | 74, 263             |  |  |  |

| EPMM3     | Pattern Mate | h Mask Regis                       | ter Byte 3    |                |                               |               |        |        | 0000 0000             | 74, 263             |  |  |  |

| EPMM2     | Pattern Mate | h Mask Regis                       | ter Byte 2    |                |                               |               |        |        | 0000 0000             | 74, 263             |  |  |  |

| EPMM1     | Pattern Mato | h Mask Regis                       | ter Byte 1    |                |                               |               |        |        | 0000 0000             | 74, 263             |  |  |  |

| EPMM0     | Pattern Mate | h Mask Regis                       | ter Byte 0    |                |                               |               |        |        | 0000 0000             | 74, 263             |  |  |  |

#### TABLE 6-5: REGISTER FILE SUMMARY (PIC18F97J60 FAMILY) (CONTINUED)

Legend: x = unknown; u = unchanged; - = unimplemented, read as '0'; q = value depends on condition; r = reserved bit, do not modify. Shaded cells are unimplemented, read as '0'.

Note 1: Bit 7 and bit 6 are cleared by user software or by a POR.

2: Bit 21 of the PC is only available in Serial Programming modes.

3: Reset value is '0' when Two-Speed Start-up is enabled and '1' if disabled.

4: Alternate names and definitions for these bits when the MSSP module is operating in  $I^2C^{TM}$  Slave mode.

5: These bits and/or registers are only available in 100-pin devices; otherwise, they are unimplemented and read as '0'. Reset values shown apply only to 100-pin devices.

6: These bits and/or registers are only available in 80-pin and 100-pin devices. In 64-pin devices, they are unimplemented and read as '0'. Reset values are shown for 100-pin devices.

7: In Microcontroller mode, the bits in this register are unwritable and read as '0'.

8: PLLEN is only available when either ECPLL or HSPLL Oscillator mode is selected; otherwise, read as '0'.

9: Implemented in 100-pin devices in Microcontroller mode only.

#### 6.3.6 STATUS REGISTER

The STATUS register, shown in Register 6-3, contains the arithmetic status of the ALU. The STATUS register can be the operand for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC, C, OV or N bits, then the write to these five bits is disabled.

These bits are set or cleared according to the device logic. Therefore, the result of an instruction with the STATUS register as destination may be different than intended. For example, CLRF STATUS will set the Z bit but leave the other bits unchanged. The STATUS

register then reads back as '000u u1uu'. It is recommended, therefore, that only BCF, BSF, SWAPF, MOVFF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C, DC, OV or N bits in the STATUS register.

For other instructions not affecting any Status bits, see the instruction set summaries in Table 26-2 and Table 26-3.

Note: The C and DC bits operate as a Borrow and Digit Borrow bit respectively, in subtraction.

#### REGISTER 6-3: STATUS REGISTER

| U-0       | U-0                                                          | U-0                                                        | R/W-x             | R/W-x                                   | R/W-x           | R/W-x             | R/W-x            |

|-----------|--------------------------------------------------------------|------------------------------------------------------------|-------------------|-----------------------------------------|-----------------|-------------------|------------------|

|           | —                                                            | _                                                          | N                 | OV                                      | Z               | DC <sup>(1)</sup> | C <sup>(2)</sup> |

| oit 7     |                                                              |                                                            |                   |                                         |                 |                   | bit              |

| Legend:   |                                                              |                                                            |                   |                                         |                 |                   |                  |

| R = Read  | dable bit                                                    | W = Writable                                               | e bit             | U = Unimplen                            | nented bit, rea | ıd as '0'         |                  |

| -n = Valu | e at POR                                                     | '1' = Bit is se                                            | t                 | '0' = Bit is cle                        |                 | x = Bit is unkr   | nown             |

| bit 7-5   | Unimpleme                                                    | nted: Read as                                              | <b>'</b> ∩'       |                                         |                 |                   |                  |

| oit 4     | N: Negative                                                  |                                                            | 0                 |                                         |                 |                   |                  |

| 511 4     | 0                                                            | ed for signed a                                            | rithmetic (2's    | complement). It                         | indicates whe   | ther the result w | vas negative     |

|           | 1 = Result w<br>0 = Result w                                 | •                                                          |                   |                                         |                 |                   |                  |

| bit 3     | which cause                                                  | ed for signed a<br>s the sign bit (b                       | oit 7 of the resu | ult) to change s                        | tate.           | verflow of the 7- | bit magnitude    |

|           | 1 = Overflow<br>0 = No overf                                 |                                                            | igned arithme     | tic (in this arithn                     | netic operatior | ו)                |                  |

| bit 2     | Z: Zero bit                                                  |                                                            |                   |                                         |                 |                   |                  |

|           |                                                              | It of an arithme<br>It of an arithme                       |                   | eration is zero<br>eration is non-z     | ero             |                   |                  |

| bit 1     | 0                                                            | rry/ <mark>Borrow</mark> bit <sup>(1</sup><br>ADDLW, SUBLW |                   | structions:                             |                 |                   |                  |

|           |                                                              | out from the 4th<br>-out from the 4                        |                   | of the result oc<br>t of the result     | curred          |                   |                  |

| bit 0     | C: Carry/Bor                                                 |                                                            |                   |                                         |                 |                   |                  |

|           |                                                              | DDLW, SUBLW                                                | and SUBWF ins     | structions:                             |                 |                   |                  |

|           |                                                              |                                                            |                   | bit of the result<br>t bit of the resul |                 |                   |                  |

| Note 1:   | For Borrow, the po<br>operand. For rotat                     |                                                            |                   |                                         |                 |                   |                  |

| 2:        | For Borrow, the po<br>operand. For rotal<br>source register. | plarity is revers                                          | ed. A subtracti   | on is executed                          | by adding the   | 2's complement    | of the second    |

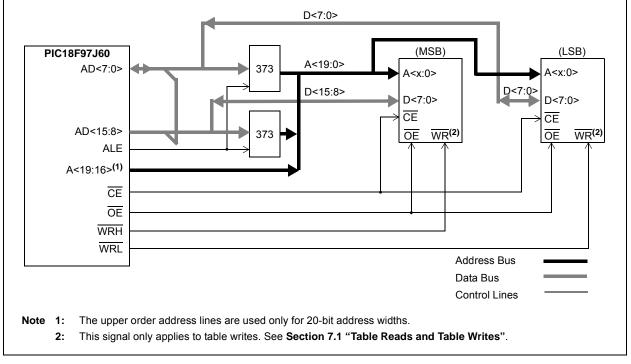

#### 8.6.1 16-BIT BYTE WRITE MODE

Figure 8-1 shows an example of 16-Bit Byte Write mode for PIC18F97J60 family devices. This mode is used for two separate 8-bit memories connected for 16-bit operation. This generally includes basic EPROM and Flash devices. It allows table writes to byte-wide external memories. During a TBLWT instruction cycle, the TABLAT data is presented on the upper and lower bytes of the AD<15:0> bus. The appropriate WRH or WRL control line is strobed on the LSb of the TBLPTR.

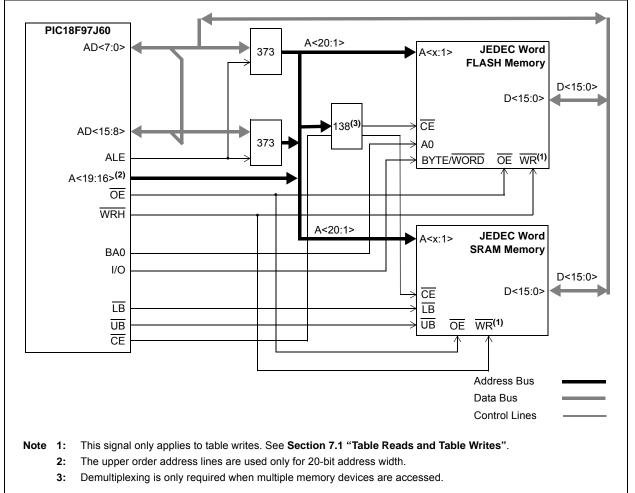

#### 8.6.3 16-BIT BYTE SELECT MODE

Figure 8-3 shows an example of 16-Bit Byte Select mode. This mode allows table write operations to word-wide external memories with byte selection capability. This generally includes both word-wide Flash and SRAM devices.

During a TBLWT cycle, the TABLAT data is presented on the upper and lower byte of the AD<15:0> bus. The WRH signal is strobed for each write cycle; the WRL pin is not used. The BA0 or UB/LB signals are used to select the byte to be written based on the Least Significant bit of the TBLPTR register. Flash and SRAM devices use different control signal combinations to implement Byte Select mode. JEDEC standard Flash memories require that a controller I/O port pin be connected to the memory's BYTE/WORD pin to provide the select signal. They also use the BA0 signal from the controller as a byte address. JEDEC standard, static RAM memories, on the other hand, use the UB or LB signals to select the byte.

Example 9-3 shows the sequence to do a 16 x 16 unsigned multiplication. Equation 9-1 shows the algorithm that is used. The 32-bit result is stored in four registers (RES3:RES0).

#### EQUATION 9-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 | <br>ARG1H:ARG1L • ARG2H:ARG2L<br>(ARG1H • ARG2H • $2^{16}$ ) +<br>(ARG1H • ARG2L • $2^{8}$ ) +<br>(ARG1L • ARG2H • $2^{8}$ ) +<br>(ARG1L • ARG2L) |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|           | $(ARG1L \bullet ARG2L)$                                                                                                                           |

#### EXAMPLE 9-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

|   | MOVF   | ARG1L, W    |                   |

|---|--------|-------------|-------------------|

|   | MULWF  | ARG2L       | ; ARG1L * ARG2L-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVFF  | PRODH, RES1 | ;                 |

|   | MOVFF  | PRODL, RESO | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1H, W    |                   |

|   | MULWF  | ARG2H       | ; ARG1H * ARG2H-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVFF  | PRODH, RES3 | ;                 |

|   | MOVFF  | PRODL, RES2 | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1L, W    |                   |

|   | MULWF  | ARG2H       | ; ARG1L * ARG2H-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVF   | PRODL, W    | ;                 |

|   | ADDWF  | RES1, F     |                   |

|   | MOVF   | PRODH, W    | ; products        |

|   | ADDWFC | RES2, F     | ;                 |

|   | CLRF   | WREG        | ;                 |

|   | ADDWFC | RES3, F     | ;                 |

| ; |        |             |                   |

|   | MOVF   | ARG1H, W    | ;                 |

|   | MULWF  | ARG2L       | ; ARG1H * ARG2L-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVF   |             | ;                 |

|   | ADDWF  | RES1, F     | ; Add cross       |

|   | MOVF   |             | ; products        |

|   | ADDWFC | RES2, F     | ;                 |

|   | CLRF   | WREG        | ;                 |

|   | ADDWFC | RES3, F     | ;                 |

|   |        |             |                   |

Example 9-4 shows the sequence to do a 16 x 16 signed multiply. Equation 9-2 shows the algorithm used. The 32-bit result is stored in four registers (RES3:RES0). To account for the sign bits of the arguments, the MSb for each argument pair is tested and the appropriate subtractions are done.

#### EQUATION 9-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

| RES3:RES0=ARG1H:ARG1L • ARG2H:ARG2L                             |

|-----------------------------------------------------------------|

| $= (ARG1H \bullet ARG2H \bullet 2^{16}) +$                      |

| $(ARG1H \bullet ARG2L \bullet 2^8) +$                           |

| $(ARG1L \bullet ARG2H \bullet 2^8) +$                           |

| $(ARG1L \bullet ARG2L) +$                                       |

| $(-1 \bullet ARG2H < 7 > \bullet ARG1H:ARG1L \bullet 2^{16}) +$ |

| $(-1 \bullet ARG1H < 7 > \bullet ARG2H:ARG2L \bullet 2^{16})$   |

#### EXAMPLE 9-4: 16 x 16 SIGNED MULTIPLY ROUTINE

| -   |        | MOEI              |                    |

|-----|--------|-------------------|--------------------|

|     | MOVF   | ARG1L, W          |                    |

|     | MULWF  |                   | ; ARG1L * ARG2L -> |

|     |        |                   | ; PRODH:PRODL      |

|     | MOVFF  | PRODH, RES1       | ;                  |

|     | MOVFF  | PRODL, RESO       |                    |

| ;   |        | 110002, 11200     |                    |

|     | MOVF   | ARG1H, W          |                    |

|     | MULWF  |                   | ; ARG1H * ARG2H -> |

|     | NOLWI  | AROZII            | ; PRODH:PRODL      |

|     | MOVEE  | PRODH, RES3       |                    |

|     | MOVFF  | PRODL, RESS       | ;                  |

| ;   | MOVFF  | PRODL, RE52       | ,                  |

| '   | MOVF   | ARG1L, W          |                    |

|     |        | ARG1L, W<br>ARG2H |                    |

|     | MOTME  | ARGZH             | ; ARG1L * ARG2H -> |

|     | NOTE   | DDODI II          | ; PRODH:PRODL      |

|     | MOVF   | PRODL, W          | ;                  |

|     | ADDWF  | RES1, F           | ; Add cross        |

|     |        |                   | ; products         |

|     |        | RES2, F           | i                  |

|     | CLRF   |                   | ;                  |

|     | ADDWFC | RES3, F           | ;                  |

| ;   |        |                   |                    |

|     |        | ARG1H, W          | ;                  |

|     | MULWF  | ARG2L             | ; ARG1H * ARG2L -> |

|     |        |                   | ; PRODH:PRODL      |

|     | MOVF   | PRODL, W          | ;                  |

|     |        | RES1, F           | ; Add cross        |

|     |        |                   | ; products         |

|     |        | RES2, F           | ;                  |

|     |        | WREG              | ;                  |

|     | ADDWFC | RES3, F           | ;                  |

| ;   |        |                   |                    |

|     |        |                   | ; ARG2H:ARG2L neg? |

|     | BRA    | SIGN_ARG1         | ; no, check ARG1   |

|     |        | ARG1L, W          | ;                  |

|     | SUBWF  | RES2              | ;                  |

|     |        | ARG1H, W          | ;                  |

|     | SUBWFB | RES3              |                    |

| ;   |        |                   |                    |

| SIG | N_ARG1 |                   |                    |

|     |        | ARG1H, 7          | ; ARG1H:ARG1L neg? |

|     | BRA    | CONT_CODE         | ; no, done         |

|     | MOVF   | ARG2L, W          | ;                  |

|     | SUBWF  | RES2              | ;                  |

|     |        | ARG2H, W          | ;                  |

|     | SUBWFB | RES3              |                    |

| ;   |        |                   |                    |

| CON | T_CODE |                   |                    |

|     | :      |                   |                    |

| 1   |        |                   |                    |

#### REGISTER 10-3: INTCON3: INTERRUPT CONTROL REGISTER 3

| R/W-      | 1 R/W-1                      | R/W-0                              | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0            |

|-----------|------------------------------|------------------------------------|------------------|------------------|------------------|-----------------|------------------|

| INT2      | IP INT1IP                    | INT3IE                             | INT2IE           | INT1IE           | INT3IF           | INT2IF          | INT1IF           |

| bit 7     |                              |                                    |                  |                  |                  |                 | bit C            |

|           |                              |                                    |                  |                  |                  |                 |                  |

| Legend:   |                              |                                    |                  |                  |                  |                 |                  |

| R = Read  |                              | W = Writable                       |                  | -                | nented bit, read |                 |                  |

| -n = valu | e at POR                     | '1' = Bit is set                   |                  | '0' = Bit is cle | ared             | x = Bit is unkr | nown             |

| bit 7     | INT2IP: INT                  | 2 External Interr                  | upt Priority bit | t                |                  |                 |                  |

|           | 1 = High pri                 |                                    |                  |                  |                  |                 |                  |

|           | 0 = Low price                | ority                              |                  |                  |                  |                 |                  |

| bit 6     |                              | 1 External Interr                  | upt Priority bit | İ                |                  |                 |                  |

|           | 1 = High pri<br>0 = Low pric |                                    |                  |                  |                  |                 |                  |

| bit 5     | ·                            | 3 External Interr                  | unt Enable hit   |                  |                  |                 |                  |

| bit 5     |                              | the INT3 extern                    | •                |                  |                  |                 |                  |

|           |                              | s the INT3 exter                   | •                |                  |                  |                 |                  |

| bit 4     | INT2IE: INT                  | 2 External Interr                  | upt Enable bit   |                  |                  |                 |                  |

|           |                              | the INT2 extern                    |                  |                  |                  |                 |                  |

|           |                              | s the INT2 exter                   | •                |                  |                  |                 |                  |

| bit 3     |                              | 1 External Interr                  | •                |                  |                  |                 |                  |

|           |                              | the INT1 extern<br>the INT1 extern |                  |                  |                  |                 |                  |

| bit 2     |                              | 3 External Interr                  | •                |                  |                  |                 |                  |

|           |                              | 3 external inter                   |                  | (must be clear   | ed in software)  |                 |                  |

|           |                              | 3 external inter                   |                  |                  |                  |                 |                  |

| bit 1     | INT2IF: INT2                 | 2 External Interr                  | upt Flag bit     |                  |                  |                 |                  |

|           |                              | 2 external inter                   |                  | ·                | ed in software)  |                 |                  |

|           |                              | 2 external inter                   | •                | cur              |                  |                 |                  |

| bit 0     |                              | 1 External Interr                  |                  |                  |                  |                 |                  |

|           |                              | 1 external inter                   |                  |                  | ed in software)  |                 |                  |

|           |                              | 1 external inter                   | מים מומ חטל סל   | CUI              |                  |                 |                  |

| Note:     | Interrupt flag bits          |                                    |                  |                  |                  |                 |                  |

|           | enable bit or the (          |                                    |                  |                  |                  |                 | errupt flag bits |

|           | are clear prior to           | enabling an inte                   | errupt. This fea | ature allows for | software pollin  | g.              |                  |

## 15.0 TIMER3 MODULE

The Timer3 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR3H and TMR3L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt on overflow

- Module Reset on CCPx/ECCPx Special Event Trigger

A simplified block diagram of the Timer3 module is shown in Figure 15-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 15-2.

The Timer3 module is controlled through the T3CON register (Register 15-1). It also selects the clock source options for the CCPx and ECCPx modules; see Section 17.1.1 "CCPx/ECCPx Modules and Timer Resources" for more information.

#### REGISTER 15-1: T3CON: TIMER3 CONTROL REGISTER

| R/W-0 | R/W-0 R/W-0             |  | R/W-0 R/W-0 R/W-0 R/W-0 R |        |        |        | R/W-0  |

|-------|-------------------------|--|---------------------------|--------|--------|--------|--------|

| RD16  | RD16 T3CCP2 T3CKPS1 T3C |  | T3CKPS0                   | T3CCP1 | T3SYNC | TMR3CS | TMR3ON |

| bit 7 |                         |  |                           |        |        |        | bit 0  |

| Legend:      |                                                            |                                                                  |                                            |  |  |  |  |  |  |

|--------------|------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------|--|--|--|--|--|--|

| R = Readab   | le bit W = Writable                                        | bit U = Unimplemented                                            | l bit, read as '0'                         |  |  |  |  |  |  |

| -n = Value a | t POR '1' = Bit is se                                      | '0' = Bit is cleared                                             | x = Bit is unknown                         |  |  |  |  |  |  |

| hit 7        | RD16: 16-Bit Read/Write M                                  | ada Enabla bit                                                   |                                            |  |  |  |  |  |  |

| bit 7        |                                                            | rite of Timer3 in one 16-bit operatic                            |                                            |  |  |  |  |  |  |

|              | C C                                                        | rite of Timer3 in two 8-bit operation                            |                                            |  |  |  |  |  |  |

| bit 6,3      | •                                                          | imer1 to CCPx/ECCPx Enable bits                                  | 0                                          |  |  |  |  |  |  |

|              |                                                            | the clock sources for all CCPx/EC                                | CPx modules                                |  |  |  |  |  |  |

|              |                                                            | the clock sources for ECCP3, CCF                                 |                                            |  |  |  |  |  |  |

|              | Timer1 and Timer2 ar                                       | the clock sources for ECCP1 and                                  | ECCP2                                      |  |  |  |  |  |  |

|              |                                                            | the clock sources for ECCP2, ECC                                 | CP3, CCP4 and CCP5;                        |  |  |  |  |  |  |

|              |                                                            | the clock sources for ECCP1<br>the clock sources for all CCPx/EC | CBy modulos                                |  |  |  |  |  |  |

| L:1 F 4      |                                                            |                                                                  | CFX modules                                |  |  |  |  |  |  |

| bit 5-4      |                                                            | t Clock Prescale Select bits                                     |                                            |  |  |  |  |  |  |

|              | 11 = 1:8 Prescale value<br>10 = 1:4 Prescale value         |                                                                  |                                            |  |  |  |  |  |  |

|              | 01 = 1.2 Prescale value                                    |                                                                  |                                            |  |  |  |  |  |  |

|              | 00 = 1:1 Prescale value                                    |                                                                  |                                            |  |  |  |  |  |  |

| bit 2        | T3SYNC: Timer3 External                                    | Clock Input Synchronization Select b                             | bit                                        |  |  |  |  |  |  |

|              | (not usable if the device clo                              | ck comes from Timer1/Timer3)                                     |                                            |  |  |  |  |  |  |

|              | When TMR3CS = 1:                                           |                                                                  |                                            |  |  |  |  |  |  |

|              | 1 = Do not synchronize ext                                 |                                                                  |                                            |  |  |  |  |  |  |

|              | 0 = Synchronize external c                                 | ock input                                                        |                                            |  |  |  |  |  |  |

|              | <u>When TMR3CS = 0:</u><br>This bit is ignored. Timer3.    | ses the internal clock when TMR3C                                | <b>S</b> = 0                               |  |  |  |  |  |  |

| L:1 4        | •                                                          |                                                                  | .5 – 0.                                    |  |  |  |  |  |  |

| bit 1        | TMR3CS: Timer3 Clock Sc                                    |                                                                  | , vision adve. often the first falling adv |  |  |  |  |  |  |

|              | 1 = External clock input fo<br>0 = Internal clock (Fosc/4) | n nimer i oscillator or i 130Ki (on the                          | e rising edge after the first falling edge |  |  |  |  |  |  |

| bit 0        | TMR3ON: Timer3 On bit                                      |                                                                  |                                            |  |  |  |  |  |  |

|              | 1 = Enables Timer3                                         |                                                                  |                                            |  |  |  |  |  |  |

|              | 0 = Stops Timer3                                           |                                                                  |                                            |  |  |  |  |  |  |

#### 17.1 CCPx Module Configuration

Each Capture/Compare/PWM module is associated with a control register (generically, CCPxCON) and a data register (CCPRx). The data register, in turn, is comprised of two 8-bit registers: CCPRxL (low byte) and CCPRxH (high byte). All registers are both readable and writable.

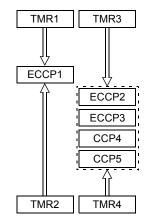

#### 17.1.1 CCPx/ECCPx MODULES AND TIMER RESOURCES

The CCPx/ECCPx modules utilize Timers 1, 2, 3 or 4, depending on the mode selected. Timer1 and Timer3 are available to modules in Capture or Compare modes, while Timer2 and Timer4 are available for modules in PWM mode.

#### TABLE 17-1: CCPx/ECCPx MODE – TIMER RESOURCE

| CCPx/ECCPx Mode | Timer Resource   |

|-----------------|------------------|

| Capture         | Timer1 or Timer3 |

| Compare         | Timer1 or Timer3 |

| PWM             | Timer2 or Timer4 |

The assignment of a particular timer to a module is determined by the timer to CCPx enable bits in the T3CON register (Register 15-1, page 183). Depending on the configuration selected, up to four timers may be active at once, with modules in the same configuration (Capture/Compare or PWM) sharing timer resources. The possible configurations are shown in Figure 17-1.

#### 17.1.2 ECCP2 PIN ASSIGNMENT

The pin assignment for ECCP2 (Capture input, Compare and PWM output) can change based on device configuration. The CCP2MX Configuration bit determines which pin ECCP2 is multiplexed to. By default, it is assigned to RC1 (CCP2MX = 1). If the Configuration bit is cleared, ECCP2 is multiplexed with RE7 on 80-pin and 100-pin devices in Microcontroller mode and RB3 on 100-pin devices in Extended Microcontroller mode.

Changing the pin assignment of ECCP2 does not automatically change any requirements for configuring the port pin. Users must always verify that the appropriate TRIS register is configured correctly for ECCP2 operation, regardless of where it is located.

#### FIGURE 17-1: CCPx/ECCPx AND TIMER INTERCONNECT CONFIGURATIONS

T3CCP<2:1> = 00 TMR1 TMR3 ECCP1 ECCP2 ECCP3 CCP4 CCP4 CCP5 TMR2 TMR4

T3CCP<2:1> = 01

Timer1 is used for all Capture and Compare operations for all CCPx modules. Timer2 is used for PWM operations for all CCPx modules. Modules may share either timer resource as a common time base.

Timer3 and Timer4 are not available.

Timer1 and Timer2 are used for Capture and Compare or PWM operations for ECCP1 only (depending on selected mode).

All other modules use either Timer3 or Timer4. Modules may share either timer resource as a common time base if they are in Capture/Compare or PWM modes. Timer1 and Timer2 are used for Capture and Compare or PWM operations for ECCP1 and ECCP2 only (depending on the mode selected for each module). Both modules may use a timer as a common time base if they are both in Capture/Compare or PWM modes.

T3CCP<2:1> = 10

TMR3

ECCP3

CCP4

CCP5

TMR4

TMR1

ECCP1

ECCP2

TMR2

The other modules use either Timer3 or Timer4. Modules may share either timer resource as a common time base if they are in Capture/Compare or PWM modes. TMR2 TMR4 Timer3 is used for all Capture and Compare operations for all CCPx modules. Timer4 is used for PWM operations for all CCPx modules. Modules

T3CCP<2:1> = 11

TMR3

ECCP1

ECCP2

ECCP3

CCP4 CCP5

TMR1

all CCPx modules. Modules may share either timer resource as a common time base.

Timer1 and Timer2 are not available.

#### TABLE 19-3: PIC18F97J60 FAMILY PHY REGISTER SUMMARY

| Addr | Name    | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11  | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4   | Bit 3 | Bit 2  | Bit 1 | Bit 0 | Reset Values        |

|------|---------|--------|--------|--------|--------|---------|--------|--------|--------|--------|--------|--------|---------|-------|--------|-------|-------|---------------------|

| 00h  | PHCON1  | r      | r      |        | —      | r       | r      | _      | PDPXMD | r      | _      | —      |         |       |        | —     |       | 00 00-0 0           |

| 01h  | PHSTAT1 | _      | _      |        | r      | r       | _      | _      | _      | _      | _      | —      | —       | _     | LLSTAT | r     | _     | 1 100-              |

| 10h  | PHCON2  | _      | FRCLNK | r      | r      | r       | r      | r      | HDLDIS | r      | r      | r      | RXAPDIS | r     | r      | r     | r     | -000 0000 0000 0000 |

| 11h  | PHSTAT2 | _      | _      | TXSTAT | RXSTAT | COLSTAT | LSTAT  | r      | _      |        | -      | r      | _       | _     |        | _     | _     | 0 00x0              |

| 12h  | PHIE    | r      | r      | r      | r      | r       | r      | r      | r      | r      | r      | r      | PLNKIE  | r     | r      | PGEIE | r     | xxxx xxxx xx00 xx00 |

| 13h  | PHIR    | r      | r      | r      | r      | r       | r      | r      | r      | r      | r      | r      | PLNKIF  | r     | PGIF   | r     | r     | xxxx xxxx xx00 00x0 |

| 14h  | PHLCON  | r      | r      | r      | r      | LACFG3  | LACFG2 | LACFG1 | LACFG0 | LBCFG3 | LBCFG2 | LBCFG1 | LBCFG0  | LFRQ1 | LFRQ0  | STRCH | r     | 0011 0100 0010 001x |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0', r = reserved, do not modify. Shaded cells are unimplemented, read as '0'.

### 19.5 Transmitting and Receiving Data

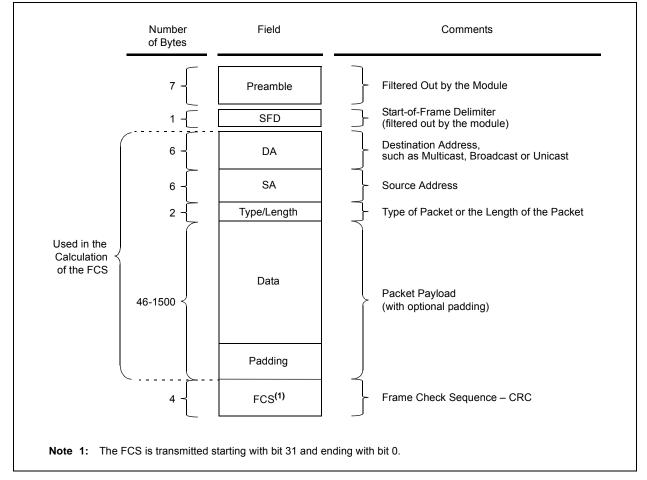

The Ethernet protocol (IEEE Standard 802.3) provides an extremely detailed description of the 10 Mbps, frame-based serial communications system. Before discussing the actual use of the Ethernet module, a brief review of the structure of a typical Ethernet data frame may be appropriate. It is assumed that users already have some familiarity with IEEE 802.3. Those requiring more information should refer to the official standard, or other Ethernet reference texts, for a more comprehensive explanation.

#### 19.5.1 PACKET FORMAT

Normal IEEE 802.3 compliant Ethernet frames are between 64 and 1518 bytes long. They are made up of five or six different fields: a destination MAC address, a source MAC address, a type/length field, data payload, an optional padding field and a Cyclic Redundancy Check (CRC). Additionally, when transmitted on the Ethernet medium, a 7-byte preamble field and Start-of-Frame (SOF) delimiter byte are appended to the beginning of the Ethernet packet. Thus, traffic seen on the twisted-pair cabling will appear as shown in Figure 19-8.

#### 19.5.1.1 Preamble/Start-of-Frame Delimiter

When transmitting and receiving data with the Ethernet module, the preamble and Start-of-Frame delimiter bytes are automatically generated, or stripped from the packets, when they are transmitted or received. It can also automatically generate CRC fields and padding as needed on transmission, and verify CRC data on reception. The user application does not need to create or process these fields, or manually verify CRC data. However, the padding and CRC fields are written into the receive buffer when packets arrive, so they may be evaluated by the user application as needed.

FIGURE 19-8: ETHERNET PACKET FORMAT

#### 19.10 Module Resets

The Ethernet module provides selective module Resets:

- Transmit Only Reset

- · Receive Only Reset

#### 19.10.1 MICROCONTROLLER RESETS

Following any standard Reset event, the Ethernet module returns to a known state. The contents of the Ethernet buffer memory are unknown. All SFR and PHY registers are loaded with their specified Reset values, depending on the type of Reset event. However, the PHY registers must not be accessed until the PHY start-up timer has expired and the PHYRDY bit (ESTAT<0>) becomes set, or at least 1 ms has passed since the ETHEN bit was set. For more details, see **Section 19.1.3.1 "Start-up Timer"**.

#### 19.10.2 TRANSMIT ONLY RESET

The Transmit Only Reset is performed by writing a '1' to the TXRST bit (ECON1<7>). This resets the transmit logic only. Other register and control blocks, such as buffer management and host interface, are not affected by a Transmit Only Reset event. To return to normal operation, the TXRST bit must be cleared in software. After clearing TXRST, firmware must not write to any Ethernet module SFRs for at least 1.6  $\mu$ s. After the delay, normal operation can resume.

#### 19.10.3 RECEIVE ONLY RESET

The Receive Only Reset is performed by writing a '1' to the RXRST bit (ECON1<6>). This action resets receive logic only. Other register and control blocks, such as the buffer management and host interface blocks, are not affected by a Receive Only Reset event. To return to normal operation, the RXRST bit is cleared in software. After clearing RXRST, firmware must not write to any Ethernet module SFRs for at least 1.6  $\mu$ s. After the delay, normal operation can resume.

#### EQUATION 21-1: CALCULATING BAUD RATE ERROR

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG: Desired Baud Rate = Fosc/(64 ([SPBRGHx:SPBRGx] + 1)) Solving for SPBRGHx:SPBRGx: X = ((Fosc/Desired Baud Rate)/64) - 1 = ((16000000/9600)/64) - 1 = [25.042] = 25Calculated Baud Rate=16000000/(64 (25 + 1))

= 9615

Error = (Calculated Baud Rate – Desired Baud Rate)/Desired Baud Rate (0.015 - 0.000)/0.000 = 0.160

= (9615 - 9600)/9600 = 0.16%

#### TABLE 21-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name     | Bit 7                                          | Bit 6     | Bit 5       | Bit 4        | Bit 3  | Bit 2 | Bit 1 | Bit 0 | Reset Values<br>on Page: |

|----------|------------------------------------------------|-----------|-------------|--------------|--------|-------|-------|-------|--------------------------|

| TXSTAx   | CSRC                                           | TX9       | TXEN        | SYNC         | SENDB  | BRGH  | TRMT  | TX9D  | 71                       |

| RCSTAx   | SPEN                                           | RX9       | SREN        | CREN         | ADDEN  | FERR  | OERR  | RX9D  | 71                       |

| BAUDCONx | ABDOVF                                         | RCIDL     | RXDTP       | TXCKP        | BRG16  | —     | WUE   | ABDEN | 72                       |

| SPBRGHx  | EUSARTx Baud Rate Generator Register High Byte |           |             |              |        |       | 72    |       |                          |

| SPBRGx   | EUSARTx                                        | Baud Rate | Generator I | Register Lov | w Byte |       |       |       | 72                       |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the BRG.

NOTES:

| RETU         | JRN            | m Subro                                                                                 | outine                                                                                                                                                                                                                                                                                                                                  |      |                      |  |  |  |

|--------------|----------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------|--|--|--|

| Synta        | ax:            | RETURN                                                                                  | {s}                                                                                                                                                                                                                                                                                                                                     |      |                      |  |  |  |

| Oper         | ands:          | s ∈ [0,1]                                                                               |                                                                                                                                                                                                                                                                                                                                         |      |                      |  |  |  |

| Oper         | ation:         | if s = 1,<br>(WS) $\rightarrow$ W<br>(STATUSS<br>(BSRS) $\rightarrow$                   | $(TOS) \rightarrow PC;$<br>if s = 1,<br>$(WS) \rightarrow W,$<br>$(STATUSS) \rightarrow STATUS,$<br>$(BSRS) \rightarrow BSR,$<br>PCLATU, PCLATH are unchanged                                                                                                                                                                           |      |                      |  |  |  |

| Statu        | s Affected:    | None                                                                                    |                                                                                                                                                                                                                                                                                                                                         |      |                      |  |  |  |

| Enco         | ding:          | 0000                                                                                    | 0000                                                                                                                                                                                                                                                                                                                                    | 0001 | 001s                 |  |  |  |

| Description: |                | is loaded in<br>'s'= 1, the<br>registers W<br>loaded into<br>registers W<br>'s' = 0, no | Return from subroutine. The stack is<br>popped and the top of the stack (TOS)<br>is loaded into the program counter. If<br>'s'= 1, the contents of the shadow<br>registers WS, STATUSS and BSRS are<br>loaded into their corresponding<br>registers W, STATUS and BSR. If<br>'s' = 0, no update of these registers<br>occurs (default). |      |                      |  |  |  |

| Word         | ls:            | 1                                                                                       |                                                                                                                                                                                                                                                                                                                                         |      |                      |  |  |  |

| Cycles:      |                | 2                                                                                       |                                                                                                                                                                                                                                                                                                                                         |      |                      |  |  |  |

| QC           | ycle Activity: |                                                                                         |                                                                                                                                                                                                                                                                                                                                         |      |                      |  |  |  |

|              | Q1             | Q2                                                                                      | Q                                                                                                                                                                                                                                                                                                                                       | 3    | Q4                   |  |  |  |

|              | Decode         | No<br>operation                                                                         | Proce<br>Dat                                                                                                                                                                                                                                                                                                                            |      | POP PC<br>from stack |  |  |  |

|              | No             | No                                                                                      | No                                                                                                                                                                                                                                                                                                                                      |      | No                   |  |  |  |

|              | operation      | operation                                                                               | opera                                                                                                                                                                                                                                                                                                                                   | tion | operation            |  |  |  |

| <u>Exan</u>  | nple:          | RETURN                                                                                  |                                                                                                                                                                                                                                                                                                                                         |      |                      |  |  |  |

| After Inst | ruction: |

|------------|----------|

| PC         | = TOS    |

| Syntax:                                      | RLCF f {,d {,a}}                                                                                                                                                                                                                                                                    |     |  |  |  |  |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|

| Operands:                                    | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                 |     |  |  |  |  |

| Operation:                                   | $(f < n >) \rightarrow dest < n + 1 >,$<br>$(f < 7 >) \rightarrow C,$<br>$(C) \rightarrow dest < 0 >$                                                                                                                                                                               |     |  |  |  |  |

| Status Affected:                             | C, N, Z                                                                                                                                                                                                                                                                             |     |  |  |  |  |

| Encoding:                                    | 0011 01da ffff fff                                                                                                                                                                                                                                                                  | Ē£  |  |  |  |  |

| Description:                                 | The contents of register 'f' are rotated<br>one bit to the left through the Carry flag.<br>If 'd' is '0', the result is placed in W. If 'd'<br>is '1', the result is stored back in register<br>'f' (default).                                                                      |     |  |  |  |  |

|                                              | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).                                                                                                                                                                  |     |  |  |  |  |

|                                              | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 26.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details |     |  |  |  |  |

|                                              | set is enabled, this instruction operation in Indexed Literal Offset Addressing mode whenever $f \le 95$ (5Fh). See Section 26.2.3 "Byte-Oriented and                                                                                                                               | tes |  |  |  |  |

|                                              | set is enabled, this instruction operat<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 26.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexe                                                                                  | tes |  |  |  |  |

| Words:                                       | set is enabled, this instruction operat<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 26.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexe<br>Literal Offset Mode" for details.                                                 | tes |  |  |  |  |

| Words:<br>Cycles:                            | set is enabled, this instruction operation in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See Section 26.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexe Literal Offset Mode" for details.                                                             | tes |  |  |  |  |

| Cycles:                                      | set is enabled, this instruction operation in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See Section 26.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexe Literal Offset Mode" for details.                                                             | tes |  |  |  |  |

|                                              | set is enabled, this instruction operation in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See Section 26.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexe Literal Offset Mode" for details.                                                             | tes |  |  |  |  |

| Cycles:<br>Q Cycle Activity:                 | set is enabled, this instruction operat<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 26.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexe<br>Literal Offset Mode" for details.                                                 | ed  |  |  |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1           | set is enabled, this instruction operat<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 26.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexe<br>Literal Offset Mode" for details.                                                 | ed  |  |  |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode | set is enabled, this instruction operation in Indexed Literal Offset Addressing mode whenever $f \le 95$ (5Fh). See Section 26.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details.<br>C - register f                                      | ed  |  |  |  |  |

#### 28.2 DC Characteristics: Power-Down and Supply Current PIC18F97J60 Family (Industrial) (Continued)

| PIC18F97J60 Family<br>(Industrial) |                                     | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |       |       |       |                                       |                                                        |  |  |  |

|------------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|---------------------------------------|--------------------------------------------------------|--|--|--|

| Param<br>No.                       | Device                              | Тур                                                                                                                                | Max   | Units |       | Conditions                            |                                                        |  |  |  |

|                                    | Supply Current (IDD) <sup>(2)</sup> |                                                                                                                                    |       |       |       |                                       |                                                        |  |  |  |

|                                    | All devices                         | 22.0                                                                                                                               | 45.0  | μΑ    | -10°C |                                       |                                                        |  |  |  |

|                                    |                                     | 22.0                                                                                                                               | 45.0  | μΑ    | +25°C | VDD = 2.0V, $VDDCORE = 2.0V(4)$       |                                                        |  |  |  |

|                                    |                                     | 78.0                                                                                                                               | 114.0 | μA    | +70°C |                                       |                                                        |  |  |  |

|                                    | All devices                         | 27.0                                                                                                                               | 52.0  | μΑ    | -10°C |                                       | Fosc = 32 kHz <sup>(3)</sup><br>( <b>SEC_RUN</b> mode, |  |  |  |

|                                    |                                     | 27.0                                                                                                                               | 52.0  | μA    | +25°C | VDD = 2.5V,<br>$VDDCORE = 2.5V^{(4)}$ |                                                        |  |  |  |

|                                    |                                     | 92.0                                                                                                                               | 135.0 | μA    | +70°C |                                       | Timer1 as clock)                                       |  |  |  |

|                                    | All devices                         | 106.0                                                                                                                              | 168.0 | μA    | -10°C |                                       |                                                        |  |  |  |

|                                    |                                     | 106.0                                                                                                                              | 168.0 | μA    | +25°C | VDD = 3.3V <sup>(5)</sup>             |                                                        |  |  |  |

|                                    |                                     | 188.0                                                                                                                              | 246.0 | μA    | +70°C |                                       |                                                        |  |  |  |

|                                    | All devices                         | 18.0                                                                                                                               | 37.0  | μA    | -10°C | $\lambda = 0.0 \lambda$               |                                                        |  |  |  |

|                                    |                                     | 18.0                                                                                                                               | 37.0  | μA    | +25°C | VDD = 2.0V, $VDDCORE = 2.0V(4)$       |                                                        |  |  |  |

|                                    |                                     | 75.0                                                                                                                               | 105.0 | μA    | +70°C |                                       |                                                        |  |  |  |

|                                    | All devices                         | 21.0                                                                                                                               | 40.0  | μΑ    | -10°C |                                       | Fosc = 32 kHz <sup>(3)</sup>                           |  |  |  |

|                                    |                                     | 21.0                                                                                                                               | 40.0  | μΑ    | +25°C | VDD = 2.5V,<br>$VDDCORE = 2.5V^{(4)}$ | (SEC_IDLE mode,                                        |  |  |  |

|                                    |                                     | 84.0                                                                                                                               | 98.0  | μΑ    | +70°C |                                       | Timer1 as clock)                                       |  |  |  |

|                                    | All devices                         | 94.0                                                                                                                               | 152.0 | μΑ    | -10°C |                                       |                                                        |  |  |  |

|                                    |                                     | 94.0                                                                                                                               | 152.0 | μΑ    | +25°C | VDD = 3.3V <sup>(5)</sup>             |                                                        |  |  |  |

|                                    |                                     | 182.0                                                                                                                              | 225.0 | μA    | +70°C |                                       |                                                        |  |  |  |

Note 1: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or Vss, and all features that add delta current disabled (such as WDT, Timer1 oscillator, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

- **3:** Standard, low-cost 32 kHz crystals have an operating temperature range of -10°C to +70°C. Extended temperature crystals are available at a much higher cost.

- **4:** Voltage regulator disabled (ENVREG = 0, tied to Vss).

- 5: Voltage regulator enabled (ENVREG = 1, tied to VDD).

- 6: For △IETH, the specified current includes current sunk through TPOUT+ and TPOUT-. LEDA and LEDB are disabled for all testing.

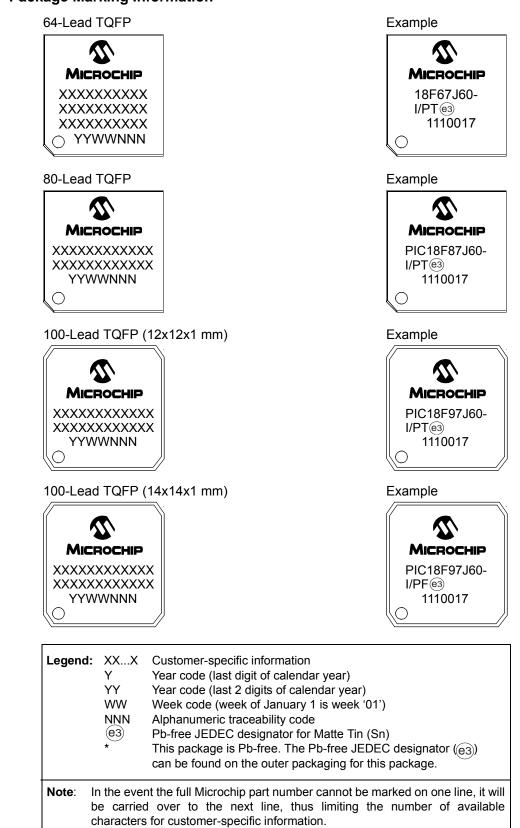

### 29.0 PACKAGING INFORMATION

### 29.1 Package Marking Information

NOTES:

| Baud Rate Generator<br>Operation                                                                                                                                                                                                                                                                                                                                                                                  |                                                                           |