Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 41.667MHz                                                                  |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 70                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3808 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                  |

| Data Converters            | A/D 16x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

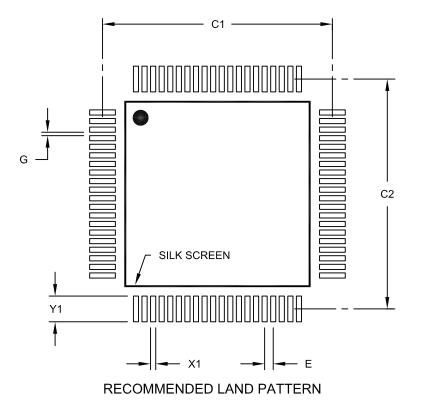

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-TQFP                                                                   |

| Supplier Device Package    | 100-TQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f96j60-i-pf |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2011, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

#### ISBN: 978-1-61341-069-1

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

| Pin Name                                                         | Pin Number         | Pin                           | Buffer                       | Description                                                                                                                                                                                                                                              |

|------------------------------------------------------------------|--------------------|-------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fin Name                                                         | TQFP               | Туре                          | Туре                         | Description                                                                                                                                                                                                                                              |

|                                                                  |                    |                               |                              | PORTD is a bidirectional I/O port.                                                                                                                                                                                                                       |

| RD0/AD0/PSP0<br>RD0<br>AD0<br>PSP0                               | 92                 | I/O<br>I/O<br>I/O             | ST<br>TTL<br>TTL             | Digital I/O.<br>External Memory Address/Data 0.<br>Parallel Slave Port data.                                                                                                                                                                             |

| RD1/AD1/PSP1<br>RD1<br>AD1<br>PSP1                               | 91                 | I/O<br>I/O<br>I/O             | ST<br>TTL<br>TTL             | Digital I/O.<br>External Memory Address/Data 1.<br>Parallel Slave Port data.                                                                                                                                                                             |

| RD2/AD2/PSP2<br>RD2<br>AD2<br>PSP2                               | 90                 | I/O<br>I/O<br>I/O             | ST<br>TTL<br>TTL             | Digital I/O.<br>External Memory Address/Data 2.<br>Parallel Slave Port data.                                                                                                                                                                             |

| RD3/AD3/PSP3<br>RD3<br>AD3<br>PSP3                               | 89                 | I/O<br>I/O<br>I/O             | ST<br>TTL<br>TTL             | Digital I/O.<br>External Memory Address/Data 3.<br>Parallel Slave Port data.                                                                                                                                                                             |

| RD4/AD4/PSP4/SDO2<br>RD4<br>AD4<br>PSP4<br>SDO2                  | 88                 | I/O<br>I/O<br>I/O<br>O        | ST<br>TTL<br>TTL<br>—        | Digital I/O.<br>External Memory Address/Data 4.<br>Parallel Slave Port data.<br>SPI data out.                                                                                                                                                            |

| RD5/AD5/PSP5/<br>SDI2/SDA2<br>RD5<br>AD5<br>PSP5<br>SDI2<br>SDA2 | 87                 | I/O<br>I/O<br>I/O<br>I<br>I/O | ST<br>TTL<br>TTL<br>ST<br>ST | Digital I/O.<br>External Memory Address/Data 5.<br>Parallel Slave Port data.<br>SPI data in.<br>I <sup>2</sup> C™ data I/O.                                                                                                                              |

| RD6/AD6/PSP6/<br>SCK2/SCL2<br>RD6<br>AD6<br>PSP6<br>SCK2<br>SCL2 | 84                 | I/O<br>I/O<br>I/O<br>I/O      | ST<br>TTL<br>TTL<br>ST<br>ST | Digital I/O.<br>External Memory Address/Data 6.<br>Parallel Slave Port data.<br>Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C™ mode.                                                 |

| RD7/AD7/PSP7/SS2<br>RD7<br>AD7<br>PSP7<br>SS2                    | 83                 | I/O<br>I/O<br>I/O<br>I        | ST<br>TTL<br>TTL<br>TTL      | Digital I/O.<br>External Memory Address/Data 7.<br>Parallel Slave Port data.<br>SPI slave select input.                                                                                                                                                  |

| I = Input<br>P = Power<br>Note 1: Alternate assig                | tt Trigger input v | P2/P2A v                      | when CCP                     | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD)<br>2MX Configuration bit is cleared (Extended Microcontroller mode)<br>es in all operating modes (CCP2MX Configuration bit is set). |

#### TABLE 1-6: PIC18F96J60/96J65/97J60 PINOUT I/O DESCRIPTIONS (CONTINUED)

3: Default assignments for P1B/P1C/P3B/P3C (ECCPMX Configuration bit is set).

4: Alternate assignment for ECCP2/P2A when CCP2MX Configuration bit is cleared (Microcontroller mode).

Alternate assignment for P1B/P1C/P3B/P3C (ECCPMX Configuration bit is cleared (Microcon)

Alternate assignments for P1B/P1C/P3B/P3C (ECCPMX Configuration bit is cleared).

NOTES:

#### REGISTER 11-1: PSPCON: PARALLEL SLAVE PORT CONTROL REGISTER

| R-0            | R-0                                               | R/W-0                                              | R/W-0                              | U-0              | U-0              | U-0             | U-0          |

|----------------|---------------------------------------------------|----------------------------------------------------|------------------------------------|------------------|------------------|-----------------|--------------|

| IBF            | OBF                                               | IBOV                                               | PSPMODE                            | _                | —                | —               | _            |

| bit 7          |                                                   |                                                    |                                    |                  |                  |                 | bit 0        |

| Legend:        |                                                   |                                                    |                                    |                  |                  |                 |              |

| R = Readable   | e bit                                             | W = Writable                                       | bit                                | U = Unimpler     | nented bit, read | as '0'          |              |

| -n = Value at  | POR                                               | '1' = Bit is se                                    | t                                  | '0' = Bit is cle | ared             | x = Bit is unkr | nown         |

| bit 7<br>bit 6 | 0 = No word h OBF: Output                         | as been receiv<br>nas been rece<br>Buffer Full Sta | ed and is waiti<br>ived<br>tus bit | -                |                  |                 |              |

| bit 5          | 0 = The output<br>0 = The output<br>IBOV: Input B | ut buffer has b                                    |                                    | iy whiten word   |                  |                 |              |

|                | 1 = A write oc<br>0 = No overflo                  |                                                    | a previously inp                   | out word has n   | ot been read (m  | ust be cleared  | in software) |

| bit 4          | PSPMODE: F<br>1 = Parallel S<br>0 = General F     | lave Port mod                                      | •                                  | ect bit          |                  |                 |              |

| bit 3-0        | Unimplemen                                        |                                                    |                                    |                  |                  |                 |              |

#### FIGURE 11-3: PARALLEL SLAVE PORT WRITE WAVEFORMS

|              | Q1   Q2   Q3   Q4                     | Q1   Q2   Q3 | Q4          | Q1   Q2   Q3   C       |

|--------------|---------------------------------------|--------------|-------------|------------------------|

| CS           |                                       |              |             | -<br>                  |

| WR           |                                       |              | 1<br>       | I<br>I<br>I            |

| RD -         |                                       |              |             | 1<br>1<br>1            |

| PORTD<7:0> — | -{                                    |              | ı<br>       |                        |

| IBF          |                                       |              |             |                        |

| OBF —        | · · · · · · · · · · · · · · · · · · · |              | 1<br>1<br>1 | 1<br>1<br><del> </del> |

| PSPIF        |                                       |              |             | 1<br>1<br>1            |

### 15.0 TIMER3 MODULE

The Timer3 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR3H and TMR3L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt on overflow

- Module Reset on CCPx/ECCPx Special Event Trigger

A simplified block diagram of the Timer3 module is shown in Figure 15-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 15-2.

The Timer3 module is controlled through the T3CON register (Register 15-1). It also selects the clock source options for the CCPx and ECCPx modules; see Section 17.1.1 "CCPx/ECCPx Modules and Timer Resources" for more information.

### REGISTER 15-1: T3CON: TIMER3 CONTROL REGISTER

| R/W-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|--------|---------|---------|--------|--------|--------|--------|

| RD16  | T3CCP2 | T3CKPS1 | T3CKPS0 | T3CCP1 | T3SYNC | TMR3CS | TMR3ON |

| bit 7 |        |         |         |        |        |        | bit 0  |

| Legend:      |                                                                                     |                                                                      |                                          |  |  |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------|--|--|--|--|--|--|

| R = Readab   | ble bit W = Writable I                                                              | t U = Unimplemented b                                                | bit, read as '0'                         |  |  |  |  |  |  |

| -n = Value a | t POR '1' = Bit is set                                                              | '0' = Bit is cleared                                                 | x = Bit is unknown                       |  |  |  |  |  |  |

| bit 7        | RD16: 16-Bit Read/Write Mo                                                          | e Enable bit                                                         |                                          |  |  |  |  |  |  |

|              | 1 = Enables register read/wr                                                        | te of Timer3 in one 16-bit operation                                 |                                          |  |  |  |  |  |  |

|              | 0                                                                                   | te of Timer3 in two 8-bit operations                                 |                                          |  |  |  |  |  |  |

| bit 6,3      | T3CCP<2:1>: Timer3 and Ti                                                           | ner1 to CCPx/ECCPx Enable bits                                       |                                          |  |  |  |  |  |  |

|              |                                                                                     | he clock sources for all CCPx/ECC                                    |                                          |  |  |  |  |  |  |

|              |                                                                                     | he clock sources for ECCP3, CCP4                                     |                                          |  |  |  |  |  |  |

|              |                                                                                     | he clock sources for ECCP1 and E<br>he clock sources for ECCP2, ECCF |                                          |  |  |  |  |  |  |

|              |                                                                                     | he clock sources for ECCP2, ECCP                                     | -3, CCF4 and CCF5,                       |  |  |  |  |  |  |

|              |                                                                                     | he clock sources for all CCPx/ECC                                    | Px modules                               |  |  |  |  |  |  |

| bit 5-4      | T3CKPS<1:0>: Timer3 Input Clock Prescale Select bits                                |                                                                      |                                          |  |  |  |  |  |  |

|              | 11 = 1:8 Prescale value                                                             |                                                                      |                                          |  |  |  |  |  |  |

|              | 10 = 1:4 Prescale value                                                             |                                                                      |                                          |  |  |  |  |  |  |

|              | 01 = 1:2 Prescale value                                                             |                                                                      |                                          |  |  |  |  |  |  |

|              | 00 = 1:1 Prescale value                                                             |                                                                      |                                          |  |  |  |  |  |  |

| bit 2        |                                                                                     | ock Input Synchronization Select bit                                 |                                          |  |  |  |  |  |  |

|              | (not usable if the device cloc                                                      | comes from Timer1/Timer3)                                            |                                          |  |  |  |  |  |  |

|              | <u>When TMR3CS = 1:</u><br>1 = Do not synchronize external clock input              |                                                                      |                                          |  |  |  |  |  |  |

|              | 0 = Synchronize external clo                                                        | •                                                                    |                                          |  |  |  |  |  |  |

|              | When TMR3CS = $0$ :                                                                 |                                                                      |                                          |  |  |  |  |  |  |

|              | This bit is ignored. Timer3 us                                                      | s the internal clock when TMR3CS                                     | s = 0.                                   |  |  |  |  |  |  |

| bit 1        | TMR3CS: Timer3 Clock Sou                                                            | ce Select bit                                                        |                                          |  |  |  |  |  |  |

|              | <ul><li>1 = External clock input from</li><li>0 = Internal clock (Fosc/4)</li></ul> | Timer1 oscillator or T13CKI (on the r                                | rising edge after the first falling edge |  |  |  |  |  |  |

| bit 0        | TMR3ON: Timer3 On bit                                                               |                                                                      |                                          |  |  |  |  |  |  |

|              | 1 = Enables Timer3<br>0 = Stops Timer3                                              |                                                                      |                                          |  |  |  |  |  |  |

#### 15.2 Timer3 16-Bit Read/Write Mode

Timer3 can be configured for 16-bit reads and writes (see Figure 15-2). When the RD16 control bit (T3CON<7>) is set, the address for TMR3H is mapped to a buffer register for the high byte of Timer3. A read from TMR3L will load the contents of the high byte of Timer3 into the Timer3 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer3 must also take place through the TMR3H Buffer register. The Timer3 high byte is updated with the contents of TMR3H when a write occurs to TMR3L. This allows a user to write all 16 bits to both the high and low bytes of Timer3 at once.

The high byte of Timer3 is not directly readable or writable in this mode. All reads and writes must take place through the Timer3 High Byte Buffer register.

Writes to TMR3H do not clear the Timer3 prescaler. The prescaler is only cleared on writes to TMR3L.

#### 15.3 Using the Timer1 Oscillator as the Timer3 Clock Source

The Timer1 internal oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. To use it as the Timer3 clock source, the TMR3CS bit must also be set. As previously noted, this also configures Timer3 to increment on every rising edge of the oscillator source.

The Timer1 oscillator is described in Section 13.0 "Timer1 Module".

#### 15.4 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments from 0000h to FFFFh, and overflows to 0000h. The Timer3 interrupt, if enabled, is generated on overflow and is latched in interrupt flag bit, TMR3IF (PIR2<1>). This interrupt can be enabled or disabled by setting or clearing the Timer3 Interrupt Enable bit, TMR3IE (PIE2<1>).

#### 15.5 Resetting Timer3 Using the ECCPx Special Event Trigger

If ECCP1 or ECCP2 is configured to use Timer3 and to generate a Special Event Trigger in Compare mode (CCPxM<3:0> = 1011), this signal will reset Timer3. The trigger from ECCP2 will also start an A/D conversion if the A/D module is enabled (see Section 18.2.1 "Special Event Trigger" for more information).

The module must be configured as either a timer or synchronous counter to take advantage of this feature. When used this way, the CCPRxH:CCPRxL register pair effectively becomes a Period register for Timer3.

If Timer3 is running in Asynchronous Counter mode, the Reset operation may not work.

In the event that a write to Timer3 coincides with a Special Event Trigger from an ECCPx module, the write will take precedence.

Note: The Special Event Triggers from the ECCPx module will not set the TMR3IF interrupt flag bit (PIR2<1>).

| Bit 7                       | Bit 6                                                                              | Bit 5                                                                                                                                            | Bit 4                                                                                                                                                  | Bit 3                                                                                                                                                                         | Bit 2                                                                                                                                                                                                                                       | Bit 1                                                                                                                                                                                                                                   | Bit 0                                                                                                                                                                                                                                                                     | Reset<br>Values<br>on Page:                                                                                                                                                                                                                                                                                                                    |  |  |

|-----------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| GIE/GIEH                    | PEIE/GIEL                                                                          | TMR0IE                                                                                                                                           | INT0IE                                                                                                                                                 | RBIE                                                                                                                                                                          | TMR0IF                                                                                                                                                                                                                                      | INT0IF                                                                                                                                                                                                                                  | RBIF                                                                                                                                                                                                                                                                      | 69                                                                                                                                                                                                                                                                                                                                             |  |  |

| OSCFIF                      | CMIF                                                                               | ETHIF                                                                                                                                            | r                                                                                                                                                      | BCL1IF                                                                                                                                                                        | _                                                                                                                                                                                                                                           | TMR3IF                                                                                                                                                                                                                                  | CCP2IF                                                                                                                                                                                                                                                                    | 71                                                                                                                                                                                                                                                                                                                                             |  |  |

| OSCFIE                      | CMIE                                                                               | ETHIE                                                                                                                                            | r                                                                                                                                                      | BCL1IE                                                                                                                                                                        | _                                                                                                                                                                                                                                           | TMR3IE                                                                                                                                                                                                                                  | CCP2IE                                                                                                                                                                                                                                                                    | 71                                                                                                                                                                                                                                                                                                                                             |  |  |

| OSCFIP                      | CMIP                                                                               | ETHIP                                                                                                                                            | r                                                                                                                                                      | BCL1IP                                                                                                                                                                        |                                                                                                                                                                                                                                             | TMR3IP                                                                                                                                                                                                                                  | CCP2IP                                                                                                                                                                                                                                                                    | 71                                                                                                                                                                                                                                                                                                                                             |  |  |

| 3L Timer3 Register Low Byte |                                                                                    |                                                                                                                                                  |                                                                                                                                                        |                                                                                                                                                                               |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                |  |  |

| I Timer3 Register High Byte |                                                                                    |                                                                                                                                                  |                                                                                                                                                        |                                                                                                                                                                               |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                |  |  |

| RD16                        | T1RUN                                                                              | T1CKPS1                                                                                                                                          | T1CKPS0                                                                                                                                                | T1OSCEN                                                                                                                                                                       | T1SYNC                                                                                                                                                                                                                                      | TMR1CS                                                                                                                                                                                                                                  | TMR10N                                                                                                                                                                                                                                                                    | 70                                                                                                                                                                                                                                                                                                                                             |  |  |

| RD16                        | T3CCP2                                                                             | T3CKPS1                                                                                                                                          | T3CKPS0                                                                                                                                                | T3CCP1                                                                                                                                                                        | <b>T3SYNC</b>                                                                                                                                                                                                                               | TMR3CS                                                                                                                                                                                                                                  | TMR3ON                                                                                                                                                                                                                                                                    | 71                                                                                                                                                                                                                                                                                                                                             |  |  |

|                             | GIE/GIEH<br>OSCFIF<br>OSCFIE<br>OSCFIP<br>Timer3 Reg<br>Timer3 Reg<br>RD16<br>RD16 | GIE/GIEH PEIE/GIEL<br>OSCFIF CMIF<br>OSCFIE CMIE<br>OSCFIP CMIP<br>Timer3 Register Low By<br>Timer3 Register High B<br>RD16 T1RUN<br>RD16 T3CCP2 | GIE/GIEHPEIE/GIELTMR0IEOSCFIFCMIFETHIFOSCFIECMIEETHIEOSCFIPCMIPETHIPTimer3 Register Low ByteTimer3 Register High ByteRD16T1RUNT1CKPS1RD16T3CCP2T3CKPS1 | GIE/GIEHPEIE/GIELTMROIEINTOIEOSCFIFCMIFETHIFrOSCFIECMIEETHIErOSCFIPCMIPETHIPrTimer3 Register Low ByteTimer3 Register High ByteRD16T1RUNT1CKPS1T1CKPS0RD16T3CCP2T3CKPS1T3CKPS0 | GIE/GIEHPEIE/GIELTMROIEINTOIERBIEOSCFIFCMIFETHIFrBCL1IFOSCFIECMIEETHIErBCL1IEOSCFIPCMIPETHIPrBCL1IPOSCFIPCMIPETHIPrBCL1IPTimer3 Register Low ByteETHIPrBCL1IPTimer3 Register High ByteRD16T1RUNT1CKPS1T1CKPS0RD16T3CCP2T3CKPS1T3CKPS0T3CCP1 | GIE/GIEHPEIE/GIELTMR0IEINT0IERBIETMR0IFOSCFIFCMIFETHIFrBCL1IF—OSCFIECMIEETHIErBCL1IE—OSCFIPCMIPETHIPrBCL1IP—OSCFIPCMIPETHIPrBCL1IP—Timer3 Register Low ByteEEEERD16T1RUNT1CKPS1T1CKPS0T1OSCENT1SYNCRD16T3CCP2T3CKPS1T3CKPS0T3CCP1T3SYNC | GIE/GIEHPEIE/GIELTMROIEINTOIERBIETMROIFINTOIFOSCFIFCMIFETHIFrBCL1IF—TMR3IFOSCFIECMIEETHIErBCL1IE—TMR3IEOSCFIPCMIPETHIPrBCL1IP—TMR3IPTimer3 Register Low ByteTimer3 Register High ByteRD16T1RUNT1CKPS1T1CKPS0T1OSCENT1SYNCTMR1CSRD16T3CCP2T3CKPS1T3CKPS0T3CCP1T3SYNCTMR3CS | GIE/GIEHPEIE/GIELTMROIEINTOIERBIETMROIFINTOIFRBIFOSCFIFCMIFETHIFrBCL1IF—TMR3IFCCP2IFOSCFIECMIEETHIErBCL1IE—TMR3IECCP2IEOSCFIPCMIPETHIPrBCL1IP—TMR3IPCCP2IPOSCFIPCMIPETHIPrBCL1IP—TMR3IPCCP2IPTimer3 Register Low ByteTimer3 Register High ByteRD16T1RUNT1CKPS1T1CKPS0T10SCENT1SYNCTMR1CSTMR10NRD16T3CCP2T3CKPS1T3CKPS0T3CCP1T3SYNCTMR3CSTMR3ON |  |  |

TABLE 15-1: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

**Legend:** — = unimplemented, read as '0', r = reserved. Shaded cells are not used by the Timer3 module.

| ECCP Mode                                                                             | CCP3CON<br>Configuration | RD1 or<br>RG0 <sup>(1)</sup> | RE4            | RE3             | RD2 or<br>RG3 <sup>(1)</sup> | RH5 <sup>(2)</sup> | RH4 <sup>(2)</sup> |  |  |  |  |

|---------------------------------------------------------------------------------------|--------------------------|------------------------------|----------------|-----------------|------------------------------|--------------------|--------------------|--|--|--|--|

| 64-Pin Devices; 80-Pin Devices, ECCPMX = 1;                                           |                          |                              |                |                 |                              |                    |                    |  |  |  |  |

| 100-Pin Devices, ECCPMX = 1, Microcontroller mode:                                    |                          |                              |                |                 |                              |                    |                    |  |  |  |  |

| Compatible CCP                                                                        | 00xx 11xx                | ECCP3                        | RE4            | RE3             | RD2/RG3                      | RH5/AN13           | RH4/AN12           |  |  |  |  |

| Dual PWM                                                                              | 10xx 11xx                | P3A                          | P3B            | RE3             | RD2/RG3                      | RH5/AN13           | RH4/AN12           |  |  |  |  |

| Quad PWM                                                                              | x1xx 11xx                | P3A                          | P3B            | P3C             | P3D                          | RH5/AN13           | RH4/AN12           |  |  |  |  |

| 80-Pin Devices, ECCPMX = 0;<br>100-Pin Devices, ECCPMX = 0, All Program Memory modes: |                          |                              |                |                 |                              |                    |                    |  |  |  |  |

| Compatible CCP                                                                        | 00xx 11xx                | ECCP3                        | RE6/AD14       | RE5/AD13        | RD2/RG3                      | RH5/AN13           | RH4/AN12           |  |  |  |  |

| Dual PWM                                                                              | 10xx 11xx                | P3A                          | RE6/AD14       | RE5/AD13        | RD2/RG3                      | P3B                | RH4/AN12           |  |  |  |  |

| Quad PWM <sup>(3)</sup>                                                               | x1xx 11xx                | P3A                          | RE6/AD14       | RE5/AD13        | P3D                          | P3B                | P3C                |  |  |  |  |

| 100                                                                                   | -Pin Devices, E          | CCPMX = 1, I                 | Extended Mic   | rocontroller v  | with 12-Bit Ac               | Idress Width:      |                    |  |  |  |  |

| Compatible CCP                                                                        | 00xx 11xx                | ECCP3                        | RE4/AD12       | RE3/AD11        | RD2/RG3                      | RH5/AN13           | RH4/AN12           |  |  |  |  |

| Dual PWM                                                                              | 10xx 11xx                | P3A                          | P3B            | RE3/AD11        | RD2/RG3                      | RH5/AN13           | RH4/AN12           |  |  |  |  |

| 100-Pin Dev                                                                           | vices, ECCPMX            | = 1, Extende                 | d Microcontro  | oller mode wi   | th 16-Bit or 2               | 0-Bit Address      | s Width:           |  |  |  |  |

| Compatible CCP                                                                        | 00xx 11xx                | ECCP3                        | RE6/AD14       | RE5/AD13        | RD2/RG3                      | RH5/AN13           | RH4/AN12           |  |  |  |  |

| Leaend: x = Do                                                                        | n't care. Shaded         | cells indicate r             | oin assignment | s not used by F | CCP3 in a giv                | en mode            |                    |  |  |  |  |

#### TABLE 18-3: PIN CONFIGURATIONS FOR ECCP3

Don't care. Shaded cells indicate pin assignments not used by ECCP3 in a given mode. na: x

Note 1: ECCP3/P3A and CCP4/P3D are multiplexed with RD1 and RD2 in 64-pin devices, and RG0 and RG3 in 80-pin and 100-pin devices.

2: These pin options are not available in 64-pin devices.

3: With ECCP3 in Quad PWM mode, the CCP4 pin's output is overridden by P3D; otherwise, CCP4 is fully operational.

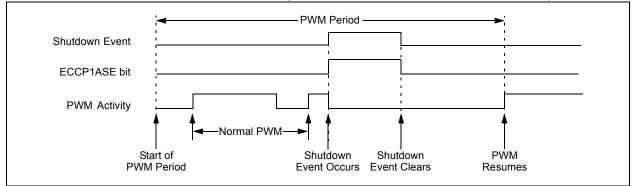

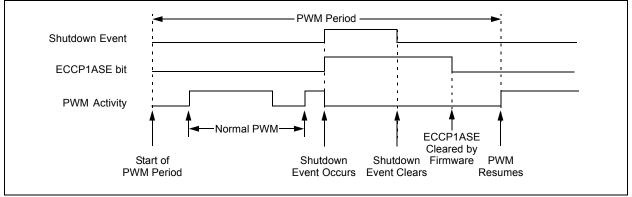

#### 18.4.7.1 Auto-Shutdown and Automatic Restart

The auto-shutdown feature can be configured to allow automatic restarts of the module following a shutdown event. This is enabled by setting the P1RSEN bit of the ECCP1DEL register (ECCP1DEL<7>).

In Shutdown mode with P1RSEN = 1 (Figure 18-10), the ECCP1ASE bit will remain set for as long as the cause of the shutdown continues. When the shutdown condition clears, the ECCP1ASE bit is cleared. If P1RSEN = 0 (Figure 18-11), once a shutdown condition occurs, the ECCP1ASE bit will remain set until it is cleared by firmware. Once ECCP1ASE is cleared, the Enhanced PWM will resume at the beginning of the next PWM period.

| Note: | Writing to the ECCP1ASE bit is disabled |

|-------|-----------------------------------------|

|       | while a shutdown condition is active.   |

Independent of the P1RSEN bit setting, if the auto-shutdown source is one of the comparators, the shutdown condition is a level. The ECCP1ASE bit cannot be cleared as long as the cause of the shutdown persists.

The Auto-Shutdown mode can be forced by writing a '1' to the ECCP1ASE bit.

### 18.4.8 START-UP CONSIDERATIONS

When the ECCP1 module is used in the PWM mode, the application hardware must use the proper external pull-up and/or pull-down resistors on the PWM output pins. When the microcontroller is released from Reset, all of the I/O pins are in the high-impedance state. The external circuits must keep the power switch devices in the OFF state until the microcontroller drives the I/O pins with the proper signal levels, or activates the PWM output(s).

The CCP1M<1:0> bits (CCP1CON<1:0>) allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (P1A/P1C and P1B/P1D). The PWM output polarities must be selected before the PWM pins are configured as outputs. Changing the polarity configuration while the PWM pins are configured as outputs is not recommended since it may result in damage to the application circuits.

The P1A, P1B, P1C and P1D output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pins for output at the same time as the ECCP1 module may cause damage to the application circuit. The ECCP1 module must be enabled in the proper Output mode and complete a full PWM cycle before configuring the PWM pins as outputs. The completion of a full PWM cycle is indicated by the TMR2IF bit being set as the second PWM period begins.

#### FIGURE 18-10: PWM AUTO-SHUTDOWN (P1RSEN = 1, AUTO-RESTART ENABLED)

### REGISTER 19-15: EIR: ETHERNET INTERRUPT REQUEST (FLAG) REGISTER

| U-0   | R-0   | R/C-0 | R-0    | R/C-0 | U-0 | R/C-0  | R/C-0  |

|-------|-------|-------|--------|-------|-----|--------|--------|

| —     | PKTIF | DMAIF | LINKIF | TXIF  | —   | TXERIF | RXERIF |

| bit 7 |       |       |        |       |     |        | bit 0  |

| Legend:          |                   |                                                                                   |                                    |                                    |  |  |  |

|------------------|-------------------|-----------------------------------------------------------------------------------|------------------------------------|------------------------------------|--|--|--|

| R = Readable bit |                   | C = Clearable bit                                                                 | U = Unimplemented bit, read as '0' |                                    |  |  |  |

| -n = Value       | at POR            | '1' = Bit is set                                                                  | '0' = Bit is cleared               | x = Bit is unknown                 |  |  |  |

| bit 7            | Unimple           | mented: Read as '0'                                                               |                                    |                                    |  |  |  |

| bit 6            | PKTIF: R          | eceive Packet Pending Inter                                                       | rupt Flag bit                      |                                    |  |  |  |

|                  | 1 = Rece<br>decre | •                                                                                 | more unprocessed packets;          | cleared only when EPKTCNT i        |  |  |  |

| bit 5            | DMAIF:            | DMA Interrupt Flag bit                                                            |                                    |                                    |  |  |  |

|                  |                   | copy or checksum calculation<br>MA interrupt is pending                           | on has completed                   |                                    |  |  |  |

| bit 4            | LINKIF: L         | ink Change Interrupt Flag b                                                       | it                                 |                                    |  |  |  |

|                  |                   | reports that the link status h<br>status has not changed                          | as changed; read PHIR regis        | ter to clear                       |  |  |  |

| bit 3            | 1 = Tran          | nsmit Interrupt Flag bit<br>smit request has ended<br>ansmit interrupt is pending |                                    |                                    |  |  |  |

| bit 2            | Unimple           | mented: Read as '0'                                                               |                                    |                                    |  |  |  |

| bit 1            | TXERIF:           | Transmit Error Interrupt Flag                                                     | ı bit                              |                                    |  |  |  |

|                  |                   | nsmit error has occurred                                                          |                                    |                                    |  |  |  |

|                  | 0 = No tr         | ansmit error has occurred                                                         |                                    |                                    |  |  |  |

| bit 0            | RXERIF:           | Receive Error Interrupt Flag                                                      | bit                                |                                    |  |  |  |

|                  | •                 | cket was aborted because the ceive error interrupt is pend                        | •                                  | e, or a buffer overrun has occurre |  |  |  |

#### REGISTER 19-18: MABBIPG: MAC BACK-TO-BACK INTER-PACKET GAP REGISTER

| U-0   | R/W-0  |

|-------|--------|--------|--------|--------|--------|--------|--------|

| —     | BBIPG6 | BBIPG5 | BBIPG4 | BBIPG3 | BBIPG2 | BBIPG1 | BBIPG0 |

| bit 7 |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 7 Unimplemented: Read as '0'

bit 6-0 BBIPG<6:0>: Back-to-Back Inter-Packet Gap Delay Time bits

When FULDPX (MACON3<0>) = 1:

Nibble time offset delay between the end of one transmission and the beginning of the next in a back-to-back sequence. The register value should be programmed to the desired period in nibble times minus 3. The recommended setting is 15h which represents the minimum IEEE specified Inter-Packet Gap (IPG) of 9.6  $\mu$ s.

When FULDPX (MACON3<0>) = 0:

Nibble time offset delay between the end of one transmission and the beginning of the next in a back-to-back sequence. The register value should be programmed to the desired period in nibble times minus 6. The recommended setting is 12h which represents the minimum IEEE specified Inter-Packet Gap (IPG) of 9.6  $\mu$ s.

#### 19.4.6 PHY INITIALIZATION SETTINGS

Depending on the application, bits in three of the PHY module's registers may also require configuration.

The PDPXMD bit (PHCON1<8>) controls the PHY half/full-duplex configuration. The application must program the bit properly, along with the FULDPX bit (MACON3<0>).

The HDLDIS bit (PHCON2<8>) disables automatic loopback of data. For proper operation, always set both HDLDIS and RXAPDIS (PHCON2<4>).

The PHY register, PHLCON (Register 19-13), controls the outputs of LEDA and LEDB. If an application requires a LED configuration other than the default, alter this register to match the new requirements. The settings for LED operation are discussed in Section 19.1.2 "LED Configuration".

#### 19.4.7 DISABLING THE ETHERNET MODULE

There may be circumstances during which the Ethernet module is not needed for prolonged periods. For example, in situations where the application only needs to transmit or receive Ethernet packets on the occurrence of a particular event. In these cases, the module can be selectively powered down.

To selectively disable the module:

- 1. Turn off packet reception by clearing the RXEN bit.

- Wait for any in-progress packets to finish being received by polling the RXBUSY bit (ESTAT<2>). This bit should be clear before proceeding.

- Wait for any current transmissions to end by confirming that the TXRTS bit (ECON1<3>) is clear.

- Clear the ETHEN bit. This removes power and clock sources from the module, and makes the PHY registers inaccessible. The PHYRDY bit is also cleared automatically.

| R/W-1         | R/W-0                                                    | R/W-1                                                                                          | R/W-0           | R/W-0            | R/W-0                                 | R/W-0            | R/W-1 |

|---------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------|------------------|---------------------------------------|------------------|-------|

| UCEN          | ANDOR                                                    | CRCEN                                                                                          | PMEN            | MPEN             | HTEN                                  | MCEN             | BCEN  |

| bit 7         |                                                          |                                                                                                |                 |                  |                                       |                  | bit C |

| Legend:       |                                                          |                                                                                                |                 |                  |                                       |                  |       |

| R = Readable  | e bit                                                    | W = Writable                                                                                   | bit             | U = Unimple      | mented bit, read                      | d as '0'         |       |

| -n = Value at | POR                                                      | '1' = Bit is set                                                                               |                 | '0' = Bit is cle | eared                                 | x = Bit is unkr  | nown  |

|               |                                                          |                                                                                                |                 |                  |                                       |                  |       |

| bit 7         | When ANDC<br>1 = Packets<br>0 = Filter is o<br>When ANDC | not having a de<br>disabled<br><u>)R = 0:</u><br>with a destination                            | stination addr  | -                | the local MAC a                       |                  |       |

| bit 6         | 1 <b>= AND: Pa</b>                                       |                                                                                                | ected unless    |                  | ers accept the p<br>ers reject the pa |                  |       |

| bit 5         | 1 = All packe                                            | st-Filter CRC Cl<br>ets with an inval<br>C validity will be                                    | id CRC will be  |                  |                                       |                  |       |

| bit 4         | When ANDC<br>1 = Packets<br>0 = Filter is o<br>When ANDC | must meet the I<br>disabled<br><u><math>OR = 0:</math><br/>which meet the</u>                  | Pattern Match   |                  | y will be discard<br>e accepted       | ed               |       |

| bit 3         | When ANDC<br>1 = Packets<br>0 = Filter is o<br>When ANDC | must be Magic<br>disabled<br><u>)R = 0:</u><br>ackets for the lo                               | Packets for th  |                  | iddress or they v                     | will be discarde | d     |

| bit 2         | When ANDC<br>1 = Packets<br>0 = Filter is o<br>When ANDC | must meet the I<br>disabled<br>DR = 0:<br>which meet the                                       | Hash Table cri  | ,                | vill be discarded                     |                  |       |

| bit 1         | When ANDC<br>1 = The LSb<br>0 = Filter is o<br>When ANDC | of the first byte of the first byte of the first byte of $\frac{1}{2} = 0$ :<br>which have the | of the packet's |                  | dress must be se<br>lestination addre |                  |       |

| bit 0         | When ANDC<br>1 = Packets<br>0 = Filter is o<br>When ANDC | must have a de<br>disabled<br><u>)R = 0:</u><br>which have a de                                | stination addr  |                  | FF-FF-FF-FF or<br>-FF-FF-FF w         | -                |       |

### REGISTER 19-20: ERXFCON: ETHERNET RECEIVE FILTER CONTROL REGISTER

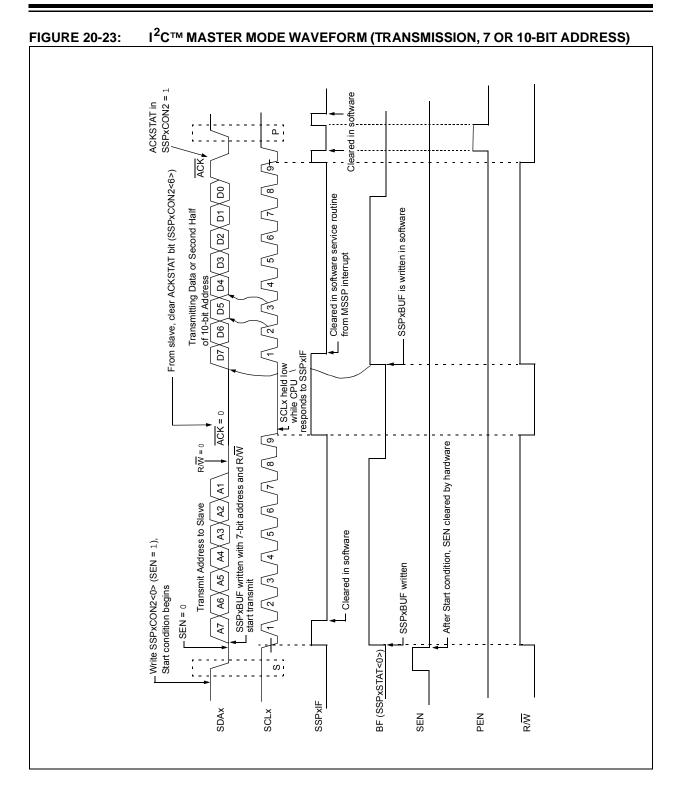

#### 20.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPxBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDAx pin after the falling edge of SCLx is asserted (see data hold time specification Parameter 106). SCLx is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCLx is released high (see data setup time specification Parameter 107). When the SCLx pin is released high, it is held that way for TBRG. The data on the SDAx pin must remain stable for that duration and some hold time after the next falling edge of SCLx. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDAx. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared; if not, the bit is set. After the ninth clock, the SSPxIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPxBUF, leaving SCLx low and SDAx unchanged (Figure 20-23).

After the write to the SSPxBUF, each bit of the address will be shifted out on the falling edge of SCLx until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDAx pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDAx pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPxCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPxIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPxBUF takes place, holding SCLx low and allowing SDAx to float.

#### 20.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPxSTAT<0>) is set when the CPU writes to SSPxBUF, and is cleared when all 8 bits are shifted out.

#### 20.4.10.2 WCOL Status Flag

If the user writes to the SSPxBUF when a transmit is already in progress (i.e., SSPxSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur) after 2 TcY after the SSPxBUF write. If SSPxBUF is rewritten within 2 TcY, the WCOL bit is set and SSPxBUF is updated. This may result in a corrupted transfer. The user should verify that the WCOL is clear after each write to SSPxBUF to ensure the transfer is correct. In all cases, WCOL must be cleared in software.

#### 20.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPxCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

#### 20.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPxCON2<3>).

| Note: | The MSSP module must be in an Idle      |

|-------|-----------------------------------------|

|       | state before the RCEN bit is set or the |

|       | RCEN bit will be disregarded.           |

The Baud Rate Generator begins counting and on each rollover. The state of the SCLx pin changes (high-to-low/low-to-high) and data is shifted into the SSPxSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPxSR are loaded into the SSPxBUF, the BF flag bit is set, the SSPxIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCLx low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPxCON2<4>).

#### 20.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPxBUF from SSPxSR. It is cleared when the SSPxBUF register is read.

#### 20.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPxSR and the BF flag bit is already set from a previous reception.

#### 20.4.11.3 WCOL Status Flag

If the user writes the SSPxBUF when a receive is already in progress (i.e., SSPxSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

### REGISTER 25-6: CONFIG3H: CONFIGURATION REGISTER 3 HIGH (BYTE ADDRESS 300005h)

| U-0        | U-0                | U-0                                  | U-0            | U-0              | R/WO-1           | R/WO-1                | R/WO-1                |

|------------|--------------------|--------------------------------------|----------------|------------------|------------------|-----------------------|-----------------------|

| (1)        | (1)                | (1)                                  | (1)            | _                | ETHLED           | ECCPMX <sup>(2)</sup> | CCP2MX <sup>(2)</sup> |

| bit 7      |                    |                                      |                |                  | L                |                       | bit 0                 |

|            |                    |                                      |                |                  |                  |                       |                       |

| Legend:    |                    |                                      |                |                  |                  |                       |                       |

| R = Read   | able bit           | WO = Write-O                         | nce bit        | U = Unimplem     | nented bit, read | d as '0'              |                       |

| -n = Value | e when device is u | nprogrammed                          |                | '1' = Bit is set |                  | '0' = Bit is clea     | ared                  |

|            |                    |                                      |                |                  |                  |                       |                       |

| bit 7-3    | Unimplemer         | ted: Read as '0                      | ,              |                  |                  |                       |                       |

| bit 2      | ETHLED: Eth        | nernet LED Enal                      | ble bit        |                  |                  |                       |                       |

|            | 1 = RA0/RA         | 1 are multiplexed                    | d with LEDA/L  | EDB when the     | Ethernet modu    | le is enabled a       | nd function as        |

|            |                    | the Ethernet is                      |                |                  |                  |                       |                       |

|            |                    | 1 function as I/O                    | regardless of  | Ethernet modu    | ile status       |                       |                       |

| bit 1      | ECCPMX: EC         | CCP MUX bit <sup>(2)</sup>           |                |                  |                  |                       |                       |

|            |                    | outputs (P1B/P1                      | <i>'</i>       |                  |                  |                       |                       |

|            |                    | outputs (P3B/P3                      |                |                  |                  |                       |                       |

|            |                    | outputs (P1B/P1<br>outputs (P3B/P3   |                |                  |                  |                       |                       |

| bit 0      |                    | CCP2 MUX bit <sup>(2)</sup>          |                |                  |                  |                       |                       |

|            |                    |                                      |                |                  |                  |                       |                       |

|            |                    | P2A is multiplex<br>P2A is multiplex |                | Microcontrollo   | r mada (90 pir   | and 100 nin d         |                       |

|            |                    | B3 in Extended                       |                |                  | • •              | •                     | evices)               |

|            |                    |                                      |                |                  |                  |                       |                       |

| Note 1:    | The value of thes  |                                      | -              | •                | 1'. This ensure  | es that the locat     | tion is               |

|            | executed as a NO   | ) P If It Is acciden                 | tally executed | •                |                  |                       |                       |

2: Implemented in 80-pin and 100-pin devices only.

| IORL                                                                                               | w              | Inclusive OR Literal with W |                   |   |               |  |

|----------------------------------------------------------------------------------------------------|----------------|-----------------------------|-------------------|---|---------------|--|

| Synta                                                                                              | ax:            | IORLW k                     |                   |   |               |  |

| Oper                                                                                               | ands:          | $0 \le k \le 258$           | 5                 |   |               |  |

| Oper                                                                                               | ation:         | (W) .OR. k                  | $x \rightarrow W$ |   |               |  |

| Statu                                                                                              | is Affected:   | N, Z                        |                   |   |               |  |

| Enco                                                                                               | oding:         | 0000 1001 kkkk kkkk         |                   |   |               |  |

| Description: The contents of W are ORed with the eight-bit literal 'k'. The result is placed in W. |                |                             |                   |   |               |  |

| Words: 1                                                                                           |                |                             |                   |   |               |  |

| Cycle                                                                                              | es:            | 1                           |                   |   |               |  |

| QC                                                                                                 | ycle Activity: |                             |                   |   |               |  |

|                                                                                                    | Q1             | Q2                          | Q3                | 5 | Q4            |  |

|                                                                                                    | Decode         | Read<br>literal 'k'         | Proce<br>Data     |   | Write to<br>W |  |

| Example: IORLW 35h                                                                                 |                |                             |                   |   |               |  |

| Before Instruction<br>W = 9Ah<br>After Instruction                                                 |                |                             |                   |   |               |  |

| IORWF                      | Inclusive (                                                         | OR W wit                                                                                                                                                                                                                                                                             | :h f |                        |  |  |  |