Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 41.667MHz                                                                   |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 70                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3808 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 16x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-TQFP                                                                    |

| Supplier Device Package    | 100-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f96j60t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.2 Other Special Features

- Communications: The PIC18F97J60 family incorporates a range of serial communication peripherals, including up to two independent Enhanced USARTs and up to two Master SSP modules, capable of both SPI and I<sup>2</sup>C<sup>™</sup> (Master and Slave) modes of operation. In addition, one of the general purpose I/O ports can be reconfigured as an 8-bit Parallel Slave Port for direct processor-to-processor communications.

- CCP Modules: All devices in the family incorporate two Capture/Compare/PWM (CCP) modules and three Enhanced CCP (ECCP) modules to maximize flexibility in control applications. Up to four different time bases may be used to perform several different operations at once. Each of the three ECCP modules offers up to four PWM outputs, allowing for a total of twelve PWMs. The ECCP modules also offer many beneficial features, including polarity selection, programmable dead time, auto-shutdown and restart and Half-Bridge and Full-Bridge Output modes.

- **10-Bit A/D Converter:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period and thus, reducing code overhead.

- Extended Watchdog Timer (WDT): This enhanced version incorporates a 16-bit prescaler, allowing an extended time-out range. See Section 28.0 "Electrical Characteristics" for time-out periods.

#### 1.3 Details on Individual Family Members

Devices in the PIC18F97J60 family are available in 64-pin, 80-pin and 100-pin packages. Block diagrams for the three groups are shown in Figure 1-1, Figure 1-2 and Figure 1-3.

The devices are differentiated from each other in four ways:

- Flash program memory (three sizes, ranging from 64 Kbytes for PIC18FX6J60 devices to 128 Kbytes for PIC18FX7J60 devices).

- A/D channels (eleven for 64-pin devices, fifteen for 80-pin pin devices and sixteen for 100-pin devices).

- Serial communication modules (one EUSART module and one MSSP module on 64-pin devices, two EUSART modules and one MSSP module on 80-pin devices and two EUSART modules and two MSSP modules on 100-pin devices).

- 4. I/O pins (39 on 64-pin devices, 55 on 80-pin devices and 70 on 100-pin devices).

All other features for devices in this family are identical. These are summarized in Table 1-1, Table 1-2 and Table 1-3.

The pinouts for all devices are listed in Table 1-4, Table 1-5 and Table 1-6.

NOTES:

#### 7.5.2 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

### 7.5.3 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed if needed. If the write operation is interrupted by a MCLR Reset, or a WDT Time-out Reset during normal operation, the user can check the WRERR bit and rewrite the location(s) as needed.

#### 7.5.4 PROTECTION AGAINST SPURIOUS WRITES

To protect against spurious writes to Flash program memory, the write initiate sequence must also be followed. See **Section 25.0** "**Special Features of the CPU**" for more details.

#### 7.6 Flash Program Operation During Code Protection

See Section 25.6 "Program Verification and Code Protection" for details on code protection of Flash program memory.

| Name    | Bit 7                                                                                         | Bit 6       | Bit 5     | Bit 4       | Bit 3      | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values<br>on Page: |

|---------|-----------------------------------------------------------------------------------------------|-------------|-----------|-------------|------------|--------|--------|-------|-----------------------------|

| TBLPTRU | —         —         bit 21         Program Memory Table Pointer Upper Byte<br>(TBLPTR<20:16>) |             |           |             |            |        |        |       |                             |

| TBPLTRH | Program Memory Table Pointer High Byte (TBLPTR<15:8>)                                         |             |           |             |            |        |        |       |                             |

| TBLPTRL | Program M                                                                                     | emory Table | Pointer L | ow Byte (TB | LPTR<7:0>) |        |        |       | 69                          |

| TABLAT  | Program M                                                                                     | emory Table | e Latch   |             |            |        |        |       | 69                          |

| INTCON  | GIE/GIEH                                                                                      | PEIE/GIEL   | TMR0IE    | INT0IE      | RBIE       | TMR0IF | INT0IF | RBIF  | 69                          |

| EECON2  | EEPROM Control Register 2 (not a physical register)                                           |             |           |             |            |        |        |       |                             |

| EECON1  | —                                                                                             | _           | _         | FREE        | WRERR      | WREN   | WR     | —     | 71                          |

#### TABLE 7-2: REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

#### 8.6.1 16-BIT BYTE WRITE MODE

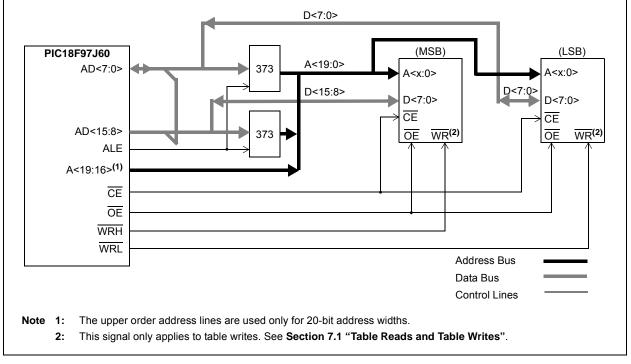

Figure 8-1 shows an example of 16-Bit Byte Write mode for PIC18F97J60 family devices. This mode is used for two separate 8-bit memories connected for 16-bit operation. This generally includes basic EPROM and Flash devices. It allows table writes to byte-wide external memories. During a TBLWT instruction cycle, the TABLAT data is presented on the upper and lower bytes of the AD<15:0> bus. The appropriate WRH or WRL control line is strobed on the LSb of the TBLPTR.

| Pin Name     | Function            | TRIS<br>Setting | I/O | I/О<br>Туре | Description                                                                                                                                             |

|--------------|---------------------|-----------------|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/AD8/RD/  | RE0                 | 0               | 0   | DIG         | LATE<0> data output.                                                                                                                                    |

| P2D          |                     | 1               | I   | ST          | PORTE<0> data input; weak pull-up when REPU bit is set.                                                                                                 |

|              | AD8 <sup>(1)</sup>  | x               | 0   | DIG         | External memory interface, Address/Data Bit 8 output. <sup>(2)</sup>                                                                                    |

|              |                     | х               | I   | TTL         | External memory interface, Data bit 8 input. <sup>(2)</sup>                                                                                             |

|              | RD <sup>(6)</sup>   | 1               | I   | TTL         | Parallel Slave Port read enable control input.                                                                                                          |

|              | P2D                 | 0               | 0   | DIG         | ECCP2 Enhanced PWM output, Channel D; takes priority over port<br>and PSP data. May be configured for tri-state during Enhanced PWM<br>shutdown events. |

| RE1/AD9/WR/  | RE1                 | 0               | 0   | DIG         | LATE<1> data output.                                                                                                                                    |

| P2C          |                     | 1               | I   | ST          | PORTE<1> data input; weak pull-up when REPU bit is set.                                                                                                 |

|              | AD9 <sup>(1)</sup>  | х               | 0   | DIG         | External memory interface, Address/Data Bit 9 output. <sup>(2)</sup>                                                                                    |

|              |                     | х               | Ι   | TTL         | External memory interface, Data Bit 9 input. <sup>(2)</sup>                                                                                             |

|              | WR(6)               | 1               | Ι   | TTL         | Parallel Slave Port write enable control input.                                                                                                         |

|              | P2C                 | 0               | 0   | DIG         | ECCP2 Enhanced PWM output, Channel C; takes priority over port<br>and PSP data. May be configured for tri-state during Enhanced PWM<br>shutdown events. |

| RE2/AD10/CS/ | RE2                 | 0               | 0   | DIG         | LATE<2> data output.                                                                                                                                    |

| P2B          |                     | 1               | Ι   | ST          | PORTE<2> data input; weak pull-up when REPU bit is set.                                                                                                 |

|              | AD10 <sup>(1)</sup> | х               | 0   | DIG         | External memory interface, Address/Data Bit 10 output. <sup>(2)</sup>                                                                                   |

|              |                     | х               | I   | TTL         | External memory interface, Data Bit 10 input. <sup>(2)</sup>                                                                                            |

|              | CS <sup>(6)</sup>   | 1               | Ι   | TTL         | Parallel Slave Port chip select control input.                                                                                                          |

|              | P2B                 | 0               | 0   | DIG         | ECCP2 Enhanced PWM output, Channel B; takes priority over port<br>and PSP data. May be configured for tri-state during Enhanced PWM<br>shutdown events. |

| RE3/AD11/    | RE3                 | 0               | 0   | DIG         | LATE<3> data output.                                                                                                                                    |

| P3C          |                     | 1               | Ι   | ST          | PORTE<3> data input; weak pull-up when REPU bit is set.                                                                                                 |

|              | AD11 <sup>(1)</sup> | x               | 0   | DIG         | External memory interface, Address/Data Bit 11 output. <sup>(2)</sup>                                                                                   |

|              |                     | х               | I   | TTL         | External memory interface, Data Bit 11 input. <sup>(2)</sup>                                                                                            |

|              | P3C <sup>(3)</sup>  | 0               | 0   | DIG         | ECCP3 Enhanced PWM output, Channel C; takes priority over port<br>and PSP data. May be configured for tri-state during Enhanced PWM<br>shutdown events. |

| RE4/AD12/    | RE4                 | 0               | 0   | DIG         | LATE<4> data output.                                                                                                                                    |

| P3B          |                     | 1               | Ι   | ST          | PORTE<4> data input; weak pull-up when REPU bit is set.                                                                                                 |

|              | AD12 <sup>(1)</sup> | х               | 0   | DIG         | External memory interface, Address/Data Bit 12 output. <sup>(2)</sup>                                                                                   |

|              |                     | х               | Ι   | TTL         | External memory interface, Data Bit 12 input. <sup>(2)</sup>                                                                                            |

|              | P3B <sup>(3)</sup>  | 0               | 0   | DIG         | ECCP3 Enhanced PWM output, channel B; takes priority over port and PSP data. May be configured for tri-state during Enhanced PWM shutdown events.       |

#### TABLE 11-11: PORTE FUNCTIONS

Legend: O = Output, I = Input, DIG = Digital Output, ST = Schmitt Buffer Input, TTL = TTL Buffer Input,

${\rm x}$  = Don't care (TRIS bit does not affect port direction or is overridden for this option).

**Note 1:** EMB functions are implemented on 100-pin devices only.

2: External memory interface I/O takes priority over all other digital and PSP I/O.

3: Default assignments for P1B/P1C and P3B/P3C when ECCPMX Configuration bit is set (80-pin and 100-pin devices).

**4:** Unimplemented on 64-pin devices.

5: Alternate assignment for ECCP2/P2A when CCP2MX Configuration bit is cleared (80-pin and 100-pin devices in Microcontroller mode).

6: Unimplemented on 64-pin and 80-pin devices.

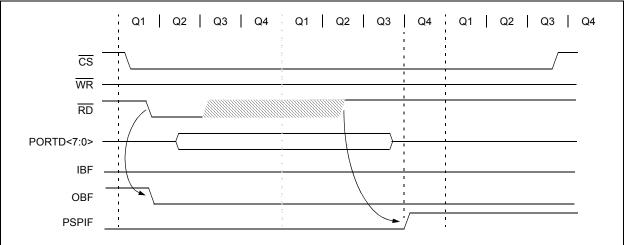

#### FIGURE 11-4: PARALLEL SLAVE PORT READ WAVEFORMS

#### TABLE 11-21: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Name   | Bit 7    | Bit 6     | Bit 5  | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|--------|----------|-----------|--------|---------|--------|--------|--------|--------|-----------------------------|

| PORTD  | RD7      | RD6       | RD5    | RD4     | RD3    | RD2    | RD1    | RD0    | 72                          |

| LATD   | LATD7    | LATD6     | LATD5  | LATD4   | LATD3  | LATD2  | LATD1  | LATD0  | 72                          |

| TRISD  | TRISD7   | TRISD6    | TRISD5 | TRISD4  | TRISD3 | TRISD2 | TRISD1 | TRISD0 | 71                          |

| PORTE  | RE7      | RE6       | RE5    | RE4     | RE3    | RE2    | RE1    | RE0    | 72                          |

| LATE   | LATE7    | LATE6     | LATE5  | LATE4   | LATE3  | LATE2  | LATE1  | LATE0  | 72                          |

| TRISE  | TRISE7   | TRISE6    | TRISE5 | TRISE4  | TRISE3 | TRISE2 | TRISE1 | TRISE0 | 71                          |

| PSPCON | IBF      | OBF       | IBOV   | PSPMODE | _      | _      | _      | _      | 71                          |

| INTCON | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE  | RBIE   | TMR0IF | INT0IF | RBIF   | 69                          |

| PIR1   | PSPIF    | ADIF      | RC1IF  | TX1IF   | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 71                          |

| PIE1   | PSPIE    | ADIE      | RC1IE  | TX1IE   | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 71                          |

| IPR1   | PSPIP    | ADIP      | RC1IP  | TX1IP   | SSP1IP | CCP1IP | TMR2IP | TMR1IP | 71                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

#### 13.1 **Timer1 Operation**

Timer1 can operate in one of these modes:

- Timer

- Synchronous Counter

T1OSO/T13CKI

T10SI

Asynchronous Counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>). When TMR1CS is cleared (= 0), Timer1 increments on every internal instruction

read as '0'. **TIMER1 BLOCK DIAGRAM** Timer1 Oscillator Timer1 Clock Input On/Off 1 1 Prescaler Synchronize 0 1, 2, 4, 8 F Detect Fosc/4 0 Internal

2

TMR1L

cycle (Fosc/4). When the bit is set, Timer1 increments

on every rising edge of the Timer1 external clock input

When Timer1 is enabled, the RC1/T1OSI and

RC0/T1OSO/T13CKI pins become inputs. This means the values of TRISC<1:0> are ignored and the pins are

Sleep Input

TMR1

High Byte

Timer1

On/Off

Set

TMR1IF

on Overflow

or the Timer1 oscillator, if enabled.

#### **FIGURE 13-1:**

T1OSCEN(1)

T1CKPS<1:0> T1SYNC TMR10N

Clock

TMR1CS

Clear TMR1

(ECCPx Special Event Trigger)

Note 1: When enable bit, T1OSCEN, is cleared, the inverter and feedback resistor are turned off to eliminate power drain.

**FIGURE 13-2:** TIMER1 BLOCK DIAGRAM (16-BIT READ/WRITE MODE) Timer1 Oscillator Timer1 Clock Input 1 T1OSO/T13CKI 1 Synchronize Prescaler 0 1, 2, 4, 8 Detect Fosc/4 Internal T10SI Clock 2 Sleep Input T1OSCEN(1) TMR1CS Timer1 On/Off T1CKPS<1:0> T1SYNC TMR10N Set TMR1IF TMR1 Clear TMR1 TMR1L High Byte (ECCPx Special Event Trigger) on Overflow Read TMR1L Write TMR1L 8 TMR1H 8

Note 1: When enable bit, T1OSCEN, is cleared, the inverter and feedback resistor are turned off to eliminate power drain.

Internal Data Bus

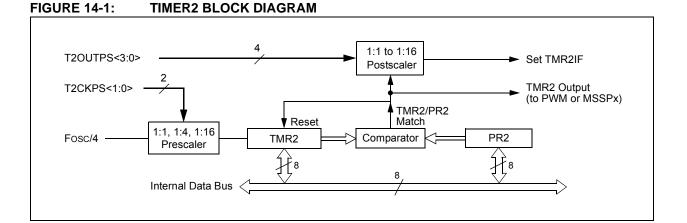

#### 14.2 Timer2 Interrupt

Timer2 can also generate an optional device interrupt. The Timer2 output signal (TMR2 to PR2 match) provides the input for the 4-bit output counter/postscaler. This counter generates the TMR2 match interrupt flag which is latched in TMR2IF (PIR1<1>). The interrupt is enabled by setting the TMR2 Match Interrupt Enable bit, TMR2IE (PIE1<1>).

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, T2OUTPS<3:0> (T2CON<6:3>).

#### 14.3 Timer2 Output

The unscaled output of TMR2 is available primarily to the CCP modules, where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSPx modules operating in SPI mode. Additional information is provided in Section 20.0 "Master Synchronous Serial Port (MSSP) Module".

#### TABLE 14-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Name   | Bit 7       | Bit 6        | Bit 5    | Bit 4    | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Reset<br>Values<br>on Page: |

|--------|-------------|--------------|----------|----------|----------|--------|---------|---------|-----------------------------|

| INTCON | GIE/GIEH    | PEIE/GIEL    | TMR0IE   | INT0IE   | RBIE     | TMR0IF | INT0IF  | RBIF    | 69                          |

| PIR1   | PSPIF       | ADIF         | RC1IF    | TX1IF    | SSP1IF   | CCP1IF | TMR2IF  | TMR1IF  | 71                          |

| PIE1   | PSPIE       | ADIE         | RC1IE    | TX1IE    | SSP1IE   | CCP1IE | TMR2IE  | TMR1IE  | 71                          |

| IPR1   | PSPIP       | ADIP         | RC1IP    | TX1IP    | SSP1IP   | CCP1IP | TMR2IP  | TMR1IP  | 71                          |

| TMR2   | Timer2 Reg  | gister       |          |          |          |        |         |         | 70                          |

| T2CON  | —           | T2OUTPS3     | T2OUTPS2 | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 70                          |

| PR2    | Timer2 Peri | iod Register |          |          |          |        |         |         | 70                          |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

NOTES:

| R/W-0         | R/W-0                     | R/W-0                               | R/W-0          | R/W-0             | R/W-0           | R/W-0             | R/W-0           |

|---------------|---------------------------|-------------------------------------|----------------|-------------------|-----------------|-------------------|-----------------|

| PxM1          | PxM0                      | DCxB1                               | DCxB0          | CCPxM3            | CCPxM2          | CCPxM1            | CCPxM0          |

| bit 7         | ·                         |                                     |                |                   |                 |                   | bit C           |

|               |                           |                                     |                |                   |                 |                   |                 |

| Legend:       | - h:t                     |                                     | L:4            |                   | anntad bit was  | d aa '0'          |                 |

| R = Readable  |                           | W = Writable                        |                | -                 | nented bit, rea |                   |                 |

| -n = Value at | PUR                       | '1' = Bit is set                    |                | '0' = Bit is clea | ared            | x = Bit is unki   | nown            |

| bit 7-6       | PxM<1:0>:                 | Enhanced PWM                        | Output Confi   | guration bits     |                 |                   |                 |

|               | If CCPxM<3                | : <u>2&gt; = 00, 01, 10</u>         | <u>):</u>      |                   |                 |                   |                 |

|               | xx = PxA as               | ssigned as Capt                     | ure/Compare    | input/output; P>  | kB, PxC, PxD a  | assigned as por   | t pins          |

|               | If CCPxM<3                |                                     |                |                   |                 |                   |                 |

|               | •                         | output: PxA mo<br>idge output forw  |                |                   | • • •           |                   |                 |

|               |                           | idge output: P1A                    |                |                   |                 |                   | ed as port pins |

|               |                           | idge output reve                    |                |                   |                 |                   |                 |

| bit 5-4       | DCxB<1:0>                 | : ECCPx Module                      | e PWM Duty (   | Cycle Bit 1 and   | Bit 0           |                   |                 |

|               | Capture mo                | <u>de:</u>                          |                |                   |                 |                   |                 |

|               | Unused.                   |                                     |                |                   |                 |                   |                 |

|               | Compare me                | <u>ode</u> :                        |                |                   |                 |                   |                 |

|               | Unused.                   |                                     |                |                   |                 |                   |                 |

|               | PWM mode<br>These bits ar | <u>.</u><br>e the 2 LSbs of th      | e 10-bit PWM   | duty cycle. The 8 | 8 MSbs of the d | utv cvcle are fou | nd in CCPRxI    |

| bit 3-0       |                           | >: ECCPx Modu                       |                |                   |                 |                   |                 |

|               |                           | ture/Compare/P                      |                |                   | (module)        |                   |                 |

|               | 0001 = Res                |                                     |                |                   |                 |                   |                 |

|               |                           | npare mode; tog                     | gle output on  | match             |                 |                   |                 |

|               | 0011 = Cap                | iture mode<br>iture mode; ever      | v falling edge |                   |                 |                   |                 |

|               |                           | oture mode; ever                    |                |                   |                 |                   |                 |

|               |                           | ture mode; ever                     |                | dge               |                 |                   |                 |

|               |                           | ture mode; ever                     |                |                   |                 |                   |                 |

|               |                           | npare mode; init                    |                |                   |                 |                   |                 |

|               |                           | npare mode; init<br>npare mode; ger |                |                   |                 |                   |                 |

|               | 1011 <b>= Con</b>         | npare mode; tri<br>CPx trigger also | gger special   | event (ECCPx      | resets TMR1     | or TMR3, set      |                 |

|               |                           | M mode; PxA, P                      |                |                   |                 |                   |                 |

|               |                           | M mode; PxA, P<br>M mode; PxA, P    |                |                   |                 |                   |                 |

|               |                           |                                     |                |                   |                 |                   |                 |

### **Note 1:** Implemented only for ECCP1 and ECCP2; same as '1010' for ECCP3.

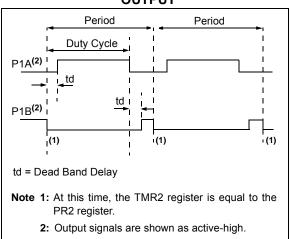

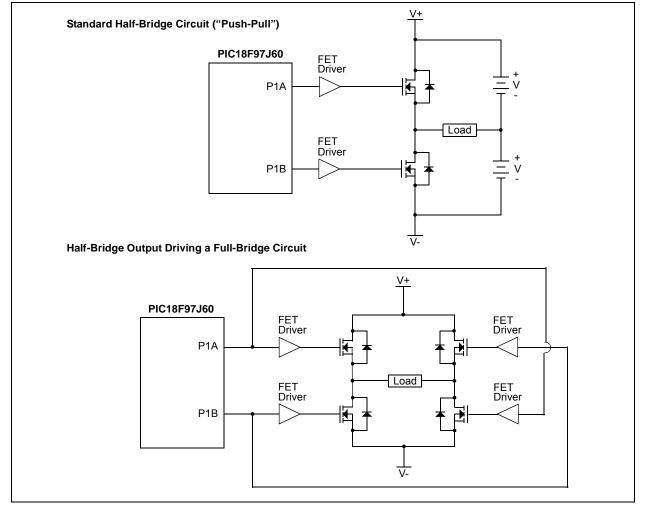

#### 18.4.4 HALF-BRIDGE MODE

In the Half-Bridge Output mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the P1A pin, while the complementary PWM output signal is output on the P1B pin (Figure 18-4). This mode can be used for half-bridge applications, as shown in Figure 18-5, or for full-bridge applications, where four power switches are being modulated with two PWM signals.

In Half-Bridge Output mode, the programmable dead-band delay can be used to prevent shoot-through current in half-bridge power devices. The value of bits, P1DC<6:0>, sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See **Section 18.4.6 "Programmable Dead-Band Delay"** for more details on dead-band delay operations.

Since the P1A and P1B outputs are multiplexed with the PORTC<2> and PORTE<6> data latches, the TRISC<2> and TRISE<6> bits must be cleared to configure P1A and P1B as outputs.

#### FIGURE 18-4: HALF-BRIDGE PWM OUTPUT

#### FIGURE 18-5: EXAMPLES OF HALF-BRIDGE OUTPUT MODE APPLICATIONS

| U-0         | R/W-0         | R/W-0             | R/W-0           | R/W-0            | U-0             | R/W-0           | R/W-0  |

|-------------|---------------|-------------------|-----------------|------------------|-----------------|-----------------|--------|

|             | PKTIE         | DMAIE             | LINKIE          | TXIE             |                 | TXERIE          | RXERIE |

| pit 7       |               |                   |                 |                  |                 |                 | bit C  |

|             |               |                   |                 |                  |                 |                 |        |

| Legend:     |               |                   |                 |                  |                 |                 |        |

| R = Readat  | ole bit       | W = Writable      | bit             | U = Unimpler     | mented bit, rea | d as '0'        |        |

| n = Value a | at POR        | '1' = Bit is set  |                 | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |

|             |               |                   |                 |                  |                 |                 |        |

| oit 7       | Unimplemer    | nted: Read as '   | 0'              |                  |                 |                 |        |

| oit 6       |               | eive Packet Per   | • ·             |                  |                 |                 |        |

|             |               | eceive packet     |                 |                  |                 |                 |        |

|             |               | receive packet    |                 | upt              |                 |                 |        |

| oit 5       |               | A Interrupt Enal  | ble bit         |                  |                 |                 |        |

|             |               | DMA interrupt     |                 |                  |                 |                 |        |

| oit 4       |               | Status Change     | Interrunt End   | ble bit          |                 |                 |        |

| //( 4       |               | ink change inte   | •               |                  |                 |                 |        |

|             |               | link change inte  |                 |                  |                 |                 |        |

| oit 3       | TXIE: Transn  | •                 |                 |                  |                 |                 |        |

|             | 1 = Enable t  | ransmit interrup  | ot              |                  |                 |                 |        |

|             | 0 = Disable f | transmit interru  | pt              |                  |                 |                 |        |

| bit 2       | Unimplemer    | nted: Read as '   | 0'              |                  |                 |                 |        |

| oit 1       | TXERIE: Trai  | nsmit Error Inte  | errupt Enable I | bit              |                 |                 |        |

|             |               | ransmit error in  |                 |                  |                 |                 |        |

|             | 0 = Disable f | transmit error ir | nterrupt        |                  |                 |                 |        |

| bit 0       |               | ceive Error Inte  | •               | bit              |                 |                 |        |

|             |               | eceive error int  |                 |                  |                 |                 |        |

|             | 0 = Disable I | receive error in  | terrupt         |                  |                 |                 |        |

#### REGISTER 19-14: EIE: ETHERNET INTERRUPT ENABLE REGISTER

#### 20.4.7 BAUD RATE

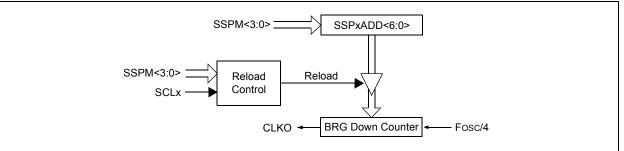

In I<sup>2</sup>C Master mode, the Baud Rate Generator (BRG) reload value is placed in the lower 7 bits of the SSPxADD register (Figure 20-19). When a write occurs to SSPxBUF, the Baud Rate Generator will automatically begin counting. The BRG counts down to 0 and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (TcY) on the Q2 and Q4 clocks. In I<sup>2</sup>C Master mode, the BRG is reloaded automatically.

Once the given operation is complete (i.e., transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCLx pin will remain in its last state.

Table 20-3 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPxADD.

#### 20.4.7.1 Baud Rate and Module Interdependence

Because MSSP1 and MSSP2 are independent, they can operate simultaneously in I<sup>2</sup>C Master mode at different baud rates. This is done by using different BRG reload values for each module.

Because this mode derives its basic clock source from the system clock, any changes to the clock will affect both modules in the same proportion. It may be possible to change one or both baud rates back to a previous value by changing the BRG reload value.

#### FIGURE 20-19: BAUD RATE GENERATOR BLOCK DIAGRAM

#### TABLE 20-3: I<sup>2</sup>C<sup>™</sup> CLOCK RATE w/BRG

| Fosc       | BRG Value | FscL<br>(2 Rollovers of BRG) |

|------------|-----------|------------------------------|

| 41.667 MHz | 19h       | 400 kHz <sup>(1)</sup>       |

| 41.667 MHz | 67h       | 100 kHz                      |

| 31.25 MHz  | 13h       | 400 kHz <sup>(1)</sup>       |

| 31.25 MHz  | 4Dh       | 100 kHz                      |

| 20.833 MHz | 09h       | 400 kHz <sup>(1)</sup>       |

| 20.833 MHz | 33h       | 100 kHz                      |

**Note 1:** The I<sup>2</sup>C<sup>™</sup> interface does not conform to the 400 kHz I<sup>2</sup>C specification (which applies to rates greater than 100 kHz) in all details, but may be used with care where higher rates are required by the application.

#### EQUATION 21-1: CALCULATING BAUD RATE ERROR

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG: Desired Baud Rate = Fosc/(64 ([SPBRGHx:SPBRGx] + 1)) Solving for SPBRGHx:SPBRGx: X = ((Fosc/Desired Baud Rate)/64) - 1 = ((16000000/9600)/64) - 1 = [25.042] = 25Calculated Baud Rate=16000000/(64 (25 + 1))

= 9615

Error = (Calculated Baud Rate – Desired Baud Rate)/Desired Baud Rate (0.015 - 0.000)/0.000 = 0.160

= (9615 - 9600)/9600 = 0.16%

#### TABLE 21-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name     | Bit 7   | Bit 6     | Bit 5       | Bit 4        | Bit 3  | Bit 2 | Bit 1 | Bit 0 | Reset Values<br>on Page: |

|----------|---------|-----------|-------------|--------------|--------|-------|-------|-------|--------------------------|

| TXSTAx   | CSRC    | TX9       | TXEN        | SYNC         | SENDB  | BRGH  | TRMT  | TX9D  | 71                       |

| RCSTAx   | SPEN    | RX9       | SREN        | CREN         | ADDEN  | FERR  | OERR  | RX9D  | 71                       |

| BAUDCONx | ABDOVF  | RCIDL     | RXDTP       | TXCKP        | BRG16  | —     | WUE   | ABDEN | 72                       |

| SPBRGHx  | EUSARTx |           | 72          |              |        |       |       |       |                          |

| SPBRGx   | EUSARTx | Baud Rate | Generator I | Register Lov | w Byte |       |       |       | 72                       |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the BRG.

| Name     | Bit 7    | Bit 6       | Bit 5       | Bit 4                | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|----------|----------|-------------|-------------|----------------------|--------|--------|--------|--------|-----------------------------|

| INTCON   | GIE/GIEH | PEIE/GIEL   | TMR0IE      | INT0IE               | RBIE   | TMR0IF | INT0IF | RBIF   | 69                          |

| PIR1     | PSPIF    | ADIF        | RC1IF       | TX1IF                | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 71                          |

| PIE1     | PSPIE    | ADIE        | RC1IE       | TX1IE                | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 71                          |

| IPR1     | PSPIP    | ADIP        | RC1IP       | TX1IP                | SSP1IP | CCP1IP | TMR2IP | TMR1IP | 71                          |

| PIR3     | SSP2IF   | BCL2IF      | RC2IF       | TX2IF <sup>(1)</sup> | TMR4IF | CCP5IF | CCP4IF | CCP3IF | 71                          |

| PIE3     | SSP2IE   | BCL2IE      | RC2IE       | TX2IE <sup>(1)</sup> | TMR4IE | CCP5IE | CCP4IE | CCP3IE | 71                          |

| IPR3     | SSP2IP   | BCL2IP      | RC2IP       | TX2IP <sup>(1)</sup> | TMR4IP | CCP5IP | CCP4IP | CCP3IP | 71                          |

| RCSTAx   | SPEN     | RX9         | SREN        | CREN                 | ADDEN  | FERR   | OERR   | RX9D   | 71                          |

| TXREGx   | EUSARTx  | Transmit Re | gister      |                      |        |        |        |        | 71                          |

| TXSTAx   | CSRC     | TX9         | TXEN        | SYNC                 | SENDB  | BRGH   | TRMT   | TX9D   | 71                          |

| BAUDCONx | ABDOVF   | RCIDL       | RXDTP       | TXCKP                | BRG16  | —      | WUE    | ABDEN  | 72                          |

| SPBRGHx  | EUSARTx  | Baud Rate C | Generator R | egister Hig          | h Byte | •      |        | •      | 72                          |

| SPBRGx   | EUSARTx  | Baud Rate C | Generator R | egister Low          | / Byte |        |        |        | 72                          |

#### TABLE 21-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

**Note 1:** These bits are only available in 80-pin and 100-pin devices; otherwise, they are unimplemented and read as '0'.

#### 21.4.2 EUSARTx SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of Sleep or any Idle mode, and bit, SREN, which is a "don't care" in Slave mode.

If receive is enabled by setting the CREN bit prior to entering Sleep or any Idle mode, then a word may be received while in this low-power mode. Once the word is received, the RSR register will transfer the data to the RCREGx register. If the RCxIE enable bit is set, the interrupt generated will wake the chip from the low-power mode. If the global interrupt is enabled, the program will branch to the interrupt vector. To set up a Synchronous Slave Reception:

- 1. Enable the synchronous master serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. If interrupts are desired, set enable bit, RCxIE.

- 3. If the signal from the CKx pin is to be inverted, set the TXCKP bit. If the signal from the DTx pin is to be inverted, set the RXDTP bit.

- 4. If 9-bit reception is desired, set bit, RX9.

- 5. To enable reception, set enable bit, CREN.

- Flag bit, RCxIF, will be set when reception is complete. An interrupt will be generated if enable bit, RCxIE, was set.

- Read the RCSTAx register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREGx register.

- 9. If any error occurred, clear the error by clearing bit, CREN.

- 10. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name     | Bit 7    | Bit 6                                         | Bit 5                | Bit 4       | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |  |  |

|----------|----------|-----------------------------------------------|----------------------|-------------|--------|--------|--------|--------|-----------------------------|--|--|

| INTCON   | GIE/GIEH | PEIE/GIEL                                     | TMR0IE               | INT0IE      | RBIE   | TMR0IF | INT0IF | RBIF   | 69                          |  |  |

| PIR1     | PSPIF    | ADIF                                          | RC1IF                | TX1IF       | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 71                          |  |  |

| PIE1     | PSPIE    | ADIE                                          | RC1IE                | TX1IE       | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 71                          |  |  |

| IPR1     | PSPIP    | ADIP                                          | RC1IP                | TX1IP       | SSP1IP | CCP1IP | TMR2IP | TMR1IP | 71                          |  |  |

| PIR3     | SSP2IF   | BCL2IF                                        | RC2IF <sup>(1)</sup> | TX2IF       | TMR4IF | CCP5IF | CCP4IF | CCP3IF | 71                          |  |  |

| PIE3     | SSP2IE   | BCL2IE                                        | RC2IE <sup>(1)</sup> | TX2IE       | TMR4IE | CCP5IE | CCP4IE | CCP3IE | 71                          |  |  |

| IPR3     | SSP2IP   | BCL2IP                                        | RC2IP <sup>(1)</sup> | TX2IP       | TMR4IP | CCP5IP | CCP4IP | CCP3IP | 71                          |  |  |

| RCSTAx   | SPEN     | RX9                                           | SREN                 | CREN        | ADDEN  | FERR   | OERR   | RX9D   | 71                          |  |  |

| RCREGx   | EUSARTx  | Receive Reg                                   | gister               |             |        |        |        |        | 71                          |  |  |

| TXSTAx   | CSRC     | TX9                                           | TXEN                 | SYNC        | SENDB  | BRGH   | TRMT   | TX9D   | 71                          |  |  |

| BAUDCONx | ABDOVF   | RCIDL                                         | RXDTP                | TXCKP       | BRG16  | —      | WUE    | ABDEN  | 72                          |  |  |

| SPBRGHx  | EUSARTx  | USARTx Baud Rate Generator Register High Byte |                      |             |        |        |        |        |                             |  |  |

| SPBRGx   | EUSARTx  | Baud Rate G                                   | Generator R          | egister Low | Byte   |        |        |        | 72                          |  |  |

#### TABLE 21-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception.

Note 1: These bits are only available in 80-pin and 100-pin devices; otherwise, they are unimplemented and read as '0'.

#### REGISTER 25-9: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0                 |

|-------|-----|-----|-----|-----|-----|-----|-----------------------|

| —     | —   | —   | —   | —   | —   | —   | SWDTEN <sup>(1)</sup> |

| bit 7 |     |     |     |     |     |     | bit 0                 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-1 Unimplemented: Read as '0'

bit 0 SWDTEN: Software Controlled Watchdog Timer Enable bit<sup>(1)</sup> 1 = Watchdog Timer is on

0 = Watchdog Timer is off

**Note 1:** This bit has no effect if the Configuration bit, WDTEN, is enabled.

#### TABLE 25-2: SUMMARY OF WATCHDOG TIMER REGISTERS

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Reset Values<br>on Page: |

|--------|-------|-------|-------|-------|-------|-------|-------|--------|--------------------------|

| RCON   | IPEN  | _     | CM    | RI    | TO    | PD    | POR   | BOR    | 70                       |

| WDTCON | —     | _     | _     | _     | _     | _     | _     | SWDTEN | 70                       |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Watchdog Timer.

#### TABLE 26-1: OPCODE FIELD DESCRIPTIONS

| Field           | Description                                                                                                                                 |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| a               | RAM access bit:                                                                                                                             |  |  |  |

|                 | a = 0: RAM location in Access RAM (BSR register is ignored)                                                                                 |  |  |  |

|                 | a = 1: RAM bank is specified by BSR register                                                                                                |  |  |  |

| bbb             | Bit address within an 8-bit file register (0 to 7).                                                                                         |  |  |  |

| BSR             | Bank Select Register. Used to select the current RAM bank.                                                                                  |  |  |  |

| C, DC, Z, OV, N | ALU Status bits: Carry, Digit Carry, Zero, Overflow, Negative.                                                                              |  |  |  |

| d               | Destination select bit:                                                                                                                     |  |  |  |

|                 | d = 0: store result in WREG                                                                                                                 |  |  |  |

|                 | d = 1: store result in file register f                                                                                                      |  |  |  |

| dest            | Destination: either the WREG register or the specified register file location.                                                              |  |  |  |

| f               | 8-bit Register file address (00h to FFh), or 2-bit FSR designator (0h to 3h).                                                               |  |  |  |

| fs              | 12-bit Register file address (000h to FFFh). This is the source address.                                                                    |  |  |  |

| f <sub>d</sub>  | 12-bit Register file address (000h to FFFh). This is the destination address.                                                               |  |  |  |

| GIE             | Global Interrupt Enable bit.                                                                                                                |  |  |  |

| k               | Literal field, constant data or label (may be either an 8-bit, 12-bit or a 20-bit value).                                                   |  |  |  |

| label           | Label name.                                                                                                                                 |  |  |  |

| mm              | The mode of the TBLPTR register for the table read and table write instructions.<br>Only used with table read and table write instructions: |  |  |  |

| *               | No Change to register (such as TBLPTR with table reads and writes)                                                                          |  |  |  |

| *+              | Post-Increment register (such as TBLPTR with table reads and writes)                                                                        |  |  |  |

| *_              | Post-Decrement register (such as TBLPTR with table reads and writes)                                                                        |  |  |  |

| +*              | Pre-Increment register (such as TBLPTR with table reads and writes)                                                                         |  |  |  |

| n               | The relative address (2's complement number) for relative branch instructions or the direct address for                                     |  |  |  |

| 11              | Call/Branch and Return instructions.                                                                                                        |  |  |  |

| PC              | Program Counter.                                                                                                                            |  |  |  |

| PCL             | Program Counter Low Byte.                                                                                                                   |  |  |  |

| PCH             | Program Counter High Byte.                                                                                                                  |  |  |  |

| PCLATH          | Program Counter High Byte Latch.                                                                                                            |  |  |  |

| PCLATU          | Program Counter Upper Byte Latch.                                                                                                           |  |  |  |

| PD              | Power-Down bit.                                                                                                                             |  |  |  |

| PRODH           | Product of Multiply High Byte.                                                                                                              |  |  |  |

| PRODL           | Product of Multiply Low Byte.                                                                                                               |  |  |  |

| s               | Fast Call/Return mode select bit:                                                                                                           |  |  |  |

|                 | s = 0: do not update into/from shadow registers                                                                                             |  |  |  |

|                 | s = 1: certain registers loaded into/from shadow registers (Fast mode)                                                                      |  |  |  |

| TBLPTR          | 21-bit Table Pointer (points to a program memory location).                                                                                 |  |  |  |

| TABLAT          | 8-bit Table Latch.                                                                                                                          |  |  |  |

| TO              | Time-out bit.                                                                                                                               |  |  |  |

| TOS             | Top-of-Stack.                                                                                                                               |  |  |  |

| u               | Unused or Unchanged.                                                                                                                        |  |  |  |

| WDT             | Watchdog Timer.                                                                                                                             |  |  |  |

| WREG            | Working register (accumulator).                                                                                                             |  |  |  |

| x               | Don't care ('0' or '1'). The assembler will generate code with $x = 0$ . It is the recommended form of use for                              |  |  |  |

|                 | compatibility with all Microchip software tools.                                                                                            |  |  |  |

| Z <sub>S</sub>  | 7-bit offset value for indirect addressing of register files (source).                                                                      |  |  |  |

| z <sub>d</sub>  | 7-bit offset value for indirect addressing of register files (destination).                                                                 |  |  |  |

| { }             | Optional argument.                                                                                                                          |  |  |  |

| [text]          | Indicates an indexed address.                                                                                                               |  |  |  |

| (text)          | The contents of text.                                                                                                                       |  |  |  |

| [expr] <n></n>  | Specifies bit n of the register indicated by the pointer expr.                                                                              |  |  |  |

| $\rightarrow$   | Assigned to.                                                                                                                                |  |  |  |

| < >             | Register bit field.                                                                                                                         |  |  |  |

| E               | In the set of.                                                                                                                              |  |  |  |

| italics         | User-defined term (font is Courier New).                                                                                                    |  |  |  |

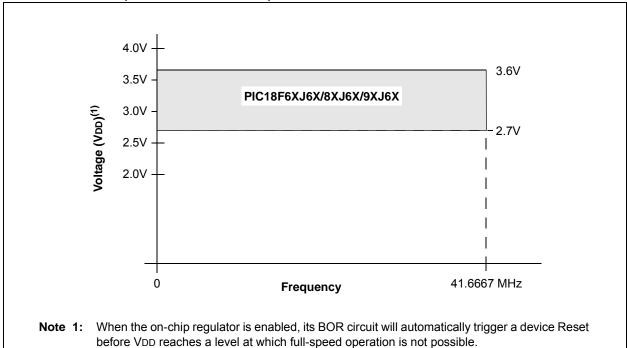

### FIGURE 28-1: PIC18F97J60 FAMILY VOLTAGE-FREQUENCY GRAPH, REGULATOR ENABLED (ENVREG TIED TO VDD)

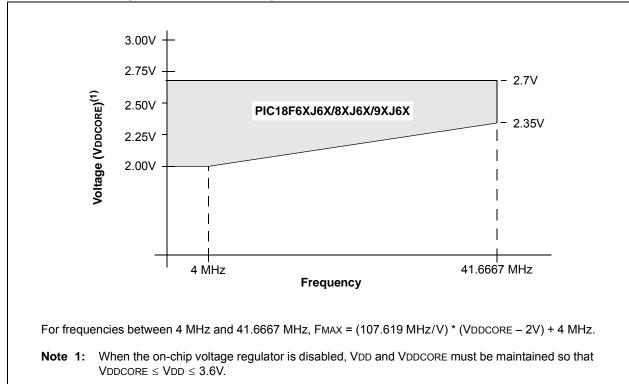

### FIGURE 28-2: PIC18F97J60 FAMILY VOLTAGE-FREQUENCY GRAPH, REGULATOR DISABLED (ENVREG TIED TO Vss)

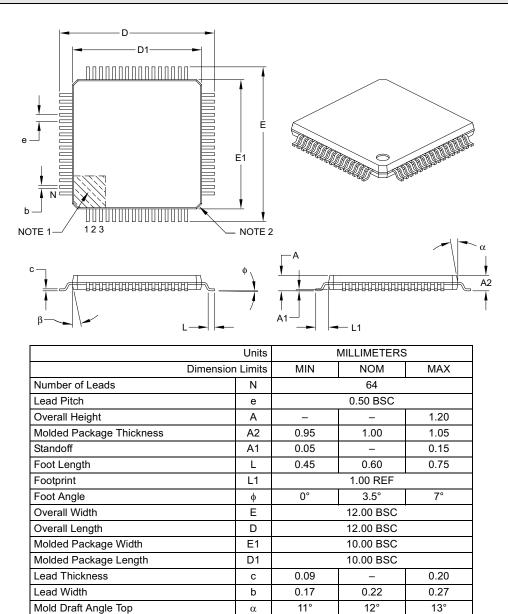

#### 29.2 Package Details

The following sections give the technical details of the packages.

#### 64-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

Mold Draft Angle Bottom

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

β

11°

12°

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085B

13°