Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 41.667MHz                                                                   |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 70                                                                          |

| Program Memory Size        | 96KB (48K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3808 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 16x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-TQFP                                                                    |

| Supplier Device Package    | 100-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f96j65t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Features                                 | PIC18F66J60                                                                         | PIC18F66J65               | PIC18F67J60       |  |  |

|------------------------------------------|-------------------------------------------------------------------------------------|---------------------------|-------------------|--|--|

| Operating Frequency                      | DC – 41.667 MHz                                                                     | DC – 41.667 MHz           | DC – 41.667 MHz   |  |  |

| Program Memory (Bytes)                   | 64K                                                                                 | 96K                       | 128K              |  |  |

| Program Memory (Instructions)            | 32764                                                                               | 49148                     | 65532             |  |  |

| Data Memory (Bytes)                      |                                                                                     | 3808                      |                   |  |  |

| Interrupt Sources                        |                                                                                     | 26                        |                   |  |  |

| I/O Ports                                | F                                                                                   | Ports A, B, C, D, E, F, O | G                 |  |  |

| I/O Pins                                 |                                                                                     | 39                        |                   |  |  |

| Timers                                   | 5                                                                                   |                           |                   |  |  |

| Capture/Compare/PWM Modules              | 2                                                                                   |                           |                   |  |  |

| Enhanced Capture/Compare/PWM Modules     | 3                                                                                   |                           |                   |  |  |

| Serial Communications                    | MSSP (1), Enhanced USART (1)                                                        |                           |                   |  |  |

| Ethernet Communications (10Base-T)       |                                                                                     | Yes                       |                   |  |  |

| Parallel Slave Port Communications (PSP) | No                                                                                  |                           |                   |  |  |

| External Memory Bus                      | No                                                                                  |                           |                   |  |  |

| 10-Bit Analog-to-Digital Module          | 11 Input Channels                                                                   |                           |                   |  |  |

| Resets (and Delays)                      | POR, BOR, RESET Instruction, Stack Full,<br>Stack Underflow, MCLR , WDT (PWRT, OST) |                           |                   |  |  |

| Instruction Set                          | 75 Instructions, 8                                                                  | 3 with Extended Instru    | ction Set Enabled |  |  |

| Packages                                 | 64-Pin TQFP                                                                         |                           |                   |  |  |

# TABLE 1-1: DEVICE FEATURES FOR THE PIC18F97J60 FAMILY (64-PIN DEVICES)

#### TABLE 1-2: DEVICE FEATURES FOR THE PIC18F97J60 FAMILY (80-PIN DEVICES)

| Features                                 | PIC18F86J60                                                                         | PIC18F86J65            | PIC18F87J60       |  |

|------------------------------------------|-------------------------------------------------------------------------------------|------------------------|-------------------|--|

| Operating Frequency                      | DC – 41.667 MHz                                                                     | DC – 41.667 MHz        | DC – 41.667 MHz   |  |

| Program Memory (Bytes)                   | 64K                                                                                 | 96K                    | 128K              |  |

| Program Memory (Instructions)            | 32764                                                                               | 49148                  | 65532             |  |

| Data Memory (Bytes)                      |                                                                                     | 3808                   |                   |  |

| Interrupt Sources                        |                                                                                     | 27                     |                   |  |

| I/O Ports                                | Ports A, B, C, D, E, F, G, H, J                                                     |                        |                   |  |

| I/O Pins                                 | 55                                                                                  |                        |                   |  |

| Timers                                   | 5                                                                                   |                        |                   |  |

| Capture/Compare/PWM Modules              | 2                                                                                   |                        |                   |  |

| Enhanced Capture/Compare/PWM Modules     |                                                                                     | 3                      |                   |  |

| Serial Communications                    | MSS                                                                                 | P (1), Enhanced USAF   | RT (2)            |  |

| Ethernet Communications (10Base-T)       |                                                                                     | Yes                    |                   |  |

| Parallel Slave Port Communications (PSP) |                                                                                     | No                     |                   |  |

| External Memory Bus                      |                                                                                     | No                     |                   |  |

| 10-Bit Analog-to-Digital Module          |                                                                                     | 15 Input Channels      |                   |  |

| Resets (and Delays)                      | POR, BOR, RESET Instruction, Stack Full,<br>Stack Underflow, MCLR , WDT (PWRT, OST) |                        |                   |  |

| Instruction Set                          | 75 Instructions, 8                                                                  | 3 with Extended Instru | ction Set Enabled |  |

| Packages                                 |                                                                                     | 80-Pin TQFP            |                   |  |

|                                        | Pin Number | Pin           | Buffer            |                                                                                                                      |

|----------------------------------------|------------|---------------|-------------------|----------------------------------------------------------------------------------------------------------------------|

| Pin Name                               | TQFP       | Туре          | Туре              | Description                                                                                                          |

|                                        |            |               |                   | PORTF is a bidirectional I/O port.                                                                                   |

| RF1/AN6/C2OUT<br>RF1<br>AN6<br>C2OUT   | 23         | I/O<br>I<br>O | ST<br>Analog<br>— | Digital I/O.<br>Analog Input 6.<br>Comparator 2 output.                                                              |

| RF2/AN7/C1OUT<br>RF2<br>AN7<br>C1OUT   | 18         | I/O<br>I<br>O | ST<br>Analog<br>— | Digital I/O.<br>Analog Input 7.<br>Comparator 1 output.                                                              |

| RF3/AN8<br>RF3<br>AN8                  | 17         | I/O<br>I      | ST<br>Analog      | Digital I/O.<br>Analog Input 8.                                                                                      |

| RF4/AN9<br>RF4<br>AN9                  | 16         | I/O<br>I      | ST<br>Analog      | Digital I/O.<br>Analog Input 9.                                                                                      |

| RF5/AN10/CVREF<br>RF5<br>AN10<br>CVREF | 15         | I/O<br>I<br>O | ST<br>Analog<br>— | Digital I/O.<br>Analog Input 10.<br>Comparator reference voltage output.                                             |

| RF6/AN11<br>RF6<br>AN11                | 14         | I/O<br>I      | ST<br>Analog      | Digital I/O.<br>Analog Input 11.                                                                                     |

| RF7/ <u>SS1</u><br>RF7<br>SS1          | 13         | I/O<br>I      | ST<br>TTL         | Digital I/O.<br>SPI slave select input.                                                                              |

|                                        |            | with CM0      | OS levels         | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD) |

| TABLE 1-5: | PIC18F86J60/86J65/87J60 PINOUT I/O DESCRIPTIONS (CONTINUED) |

|------------|-------------------------------------------------------------|

|            |                                                             |

Note 1: Default assignment for ECCP2/P2A when CCP2MX Configuration bit is set.

2: Default assignments for P1B/P1C/P3B/P3C (ECCPMX Configuration bit is set).

3: Alternate assignment for ECCP2/P2A when CCP2MX Configuration bit is cleared.

4: Alternate assignments for P1B/P1C/P3B/P3C (ECCPMX Configuration bit is cleared).

# PIC18F97J60 FAMILY

| TABLE 5-2                             |             | INITIALIZATION CONDITIONS FOR |             |                                    | MCLR Reset,                                                           |                                 |

|---------------------------------------|-------------|-------------------------------|-------------|------------------------------------|-----------------------------------------------------------------------|---------------------------------|

| Register   A     STATUS   PIC18F6XJ6X |             | pplicable Device              | 9S          | Power-on Reset,<br>Brown-out Reset | WDT Reset,<br>RESET Instruction,<br>St <u>ack</u> Resets,<br>CM Reset | Wake-up via WDT<br>or Interrupt |

|                                       |             | PIC18F8XJ6X                   | PIC18F9XJ6X | x xxxx                             | u uuuu                                                                | u uuuu                          |

| TMR0H                                 | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | 0000 0000                          | 0000 0000                                                             | uuuu uuuu                       |

| TMR0L                                 | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | xxxx xxxx                          | uuuu uuuu                                                             | uuuu uuuu                       |

| T0CON                                 | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | 1111 1111                          | 1111 1111                                                             | uuuu uuuu                       |

| OSCCON                                | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | 0 q-00                             | 0 q-00                                                                | u q-uu                          |

| ECON1                                 | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | 0000 00                            | 0000 00                                                               | uuuu uu                         |

| WDTCON                                | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | 0                                  | 0                                                                     | u                               |

| RCON <sup>(4)</sup>                   | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | 0-q1 1100                          | 0-uq qquu                                                             | u-uu qquu                       |

| TMR1H                                 | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | xxxx xxxx                          | uuuu uuuu                                                             | uuuu uuuu                       |

| TMR1L                                 | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | xxxx xxxx                          | uuuu uuuu                                                             | uuuu uuuu                       |

| T1CON                                 | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | 0000 0000                          | u0uu uuuu                                                             | uuuu uuuu                       |

| TMR2                                  | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | 0000 0000                          | 0000 0000                                                             | uuuu uuuu                       |

| PR2                                   | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | 1111 1111                          | 1111 1111                                                             | 1111 1111                       |

| T2CON                                 | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | -000 0000                          | -000 0000                                                             | -uuu uuuu                       |

| SSP1BUF                               | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | xxxx xxxx                          | uuuu uuuu                                                             | uuuu uuuu                       |

| SSP1ADD                               | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | 0000 0000                          | 0000 0000                                                             | uuuu uuuu                       |

| SSP1STAT                              | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | 0000 0000                          | 0000 0000                                                             | uuuu uuuu                       |

| SSP1CON1                              | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | 0000 0000                          | 0000 0000                                                             | uuuu uuuu                       |

| SSP1CON2                              | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | 0000 0000                          | 0000 0000                                                             | uuuu uuuu                       |

| ADRESH                                | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | xxxx xxxx                          | uuuu uuuu                                                             | uuuu uuuu                       |

| ADRESL                                | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | xxxx xxxx                          | uuuu uuuu                                                             | uuuu uuuu                       |

| ADCON0                                | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | 0-00 0000                          | 0-00 0000                                                             | u-uu uuuu                       |

| ADCON1                                | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | 00 0000                            | 00 0000                                                               | uu uuuu                         |

| ADCON2                                | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | 0-00 0000                          | 0-00 0000                                                             | u-uu uuuu                       |

| CCPR1H                                | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | xxxx xxxx                          | uuuu uuuu                                                             | uuuu uuuu                       |

| CCPR1L                                | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | xxxx xxxx                          | uuuu uuuu                                                             | uuuu uuuu                       |

| CCP1CON                               | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | 0000 0000                          | 0000 0000                                                             | uuuu uuuu                       |

| CCPR2H                                | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | xxxx xxxx                          | uuuu uuuu                                                             | uuuu uuuu                       |

| CCPR2L                                | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | xxxx xxxx                          | uuuu uuuu                                                             | uuuu uuuu                       |

| CCP2CON                               | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | 0000 0000                          | 0000 0000                                                             | uuuu uuuu                       |

| CCPR3H                                | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | xxxx xxxx                          | uuuu uuuu                                                             | uuuu uuuu                       |

| CCPR3L                                | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | xxxx xxxx                          | uuuu uuuu                                                             | uuuu uuuu                       |

| CCP3CON                               | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | 0000 0000                          | 0000 0000                                                             | uuuu uuuu                       |

| ECCP1AS                               | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | 0000 0000                          | 0000 0000                                                             | uuuu uuuu                       |

| CVRCON                                | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | 0000 0000                          | 0000 0000                                                             | uuuu uuuu                       |

| CMCON                                 | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | 0000 0111                          | 0000 0111                                                             | uuuu uuuu                       |

| TMR3H                                 | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | xxxx xxxx                          | uuuu uuuu                                                             | uuuu uuuu                       |

| TMR3L                                 | PIC18F6XJ6X | PIC18F8XJ6X                   | PIC18F9XJ6X | xxxx xxxx                          | uuuu uuuu                                                             | uuuu uuuu                       |

#### TABLE 5-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Legend:u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.Shaded cells indicate conditions do not apply for the designated device.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

4: See Table 5-1 for Reset value for specific condition.

## REGISTER 7-1: EECON1: EEPROM CONTROL REGISTER 1

| U-0   | U-0 | U-0 | R/W-0 | R/W-x | R/W-0 | R/S-0 | U-0   |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | FREE  | WRERR | WREN  | WR    | —     |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | S = Settable bit |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                         |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | FREE: Flash Row Erase Enable bit                                                                                                                                                                                                                                                   |

|         | <ul> <li>1 = Erase the program memory row addressed by TBLPTR on the next WR command (cleared by completion of erase operation)</li> <li>0 = Perform write-only</li> </ul>                                                                                                         |

| bit 3   | WRERR: Flash Program Error Flag bit                                                                                                                                                                                                                                                |

|         | <ul> <li>1 = A write operation is prematurely terminated (any Reset during self-timed programming in normal operation or an improper write attempt)</li> <li>0 = The write operation completed</li> </ul>                                                                          |

| bit 2   | WREN: Flash Program Write Enable bit                                                                                                                                                                                                                                               |

|         | <ul> <li>1 = Allows write cycles to Flash program memory</li> <li>0 = Inhibits write cycles to Flash program memory</li> </ul>                                                                                                                                                     |

| bit 1   | WR: Write Control bit                                                                                                                                                                                                                                                              |

|         | <ul> <li>1 = Initiates a program memory erase cycle or write cycle         (The operation is self-timed and the bit is cleared by hardware once the write is complete.         The WR bit can only be set (not cleared) in software.)</li> <li>0 = Write cycle complete</li> </ul> |

| bit 0   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                         |

# 10.1 INTCON Registers

The INTCON registers are readable and writable registers which contain various enable, priority and flag bits.

Note: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

## REGISTER 10-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0           | R/W-0                                                         | R/W-0                                                                 | R/W-0          | R/W-0                                   | R/W-0            | R/W-0    | R/W-x               |  |

|-----------------|---------------------------------------------------------------|-----------------------------------------------------------------------|----------------|-----------------------------------------|------------------|----------|---------------------|--|

| GIE/GIEH        | PEIE/GIEL                                                     | TMR0IE                                                                | INT0IE         | RBIE                                    | TMR0IF           | INT0IF   | RBIF <sup>(1)</sup> |  |

| bit 7           | •                                                             |                                                                       |                |                                         | ·                |          | bit 0               |  |

|                 |                                                               |                                                                       |                |                                         |                  |          |                     |  |

| Legend:         |                                                               |                                                                       |                |                                         |                  |          |                     |  |

| R = Readable    | bit                                                           | W = Writable                                                          | bit            | U = Unimpler                            | mented bit, read | l as '0' |                     |  |

| -n = Value at F | POR                                                           | '1' = Bit is set                                                      |                | '0' = Bit is cleared x = Bit is unknown |                  |          |                     |  |

| bit 7           | When IPEN =<br>1 = Enables a<br>0 = Disables a<br>When IPEN = | III unmasked in<br>all interrupts<br><u>1:</u><br>III high-priority i | terrupts       |                                         |                  |          |                     |  |

| bit 6           | <b>PEIE/GIEL</b> : P<br>When IPFN =                           | Peripheral Inter                                                      | rupt Enable bi | it                                      |                  |          |                     |  |

|         | <u>When IPEN = 0:</u><br>1 = Enables all unmasked interrupts<br>0 = Disables all interrupts                                                                               |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <u>When IPEN = 1:</u><br>1 = Enables all high-priority interrupts<br>0 = Disables all interrupts                                                                          |

| bit 6   | PEIE/GIEL: Peripheral Interrupt Enable bit                                                                                                                                |

|         | <u>When IPEN = 0:</u><br>1 = Enables all unmasked peripheral interrupts<br>0 = Disables all peripheral interrupts                                                         |

|         | <u>When IPEN = 1:</u><br>1 = Enables all low-priority peripheral interrupts<br>0 = Disables all low-priority peripheral interrupts                                        |

| bit 5   | TMR0IE: TMR0 Overflow Interrupt Enable bit                                                                                                                                |

|         | <ul><li>1 = Enables the TMR0 overflow interrupt</li><li>0 = Disables the TMR0 overflow interrupt</li></ul>                                                                |

| bit 4   | INTOIE: INTO External Interrupt Enable bit                                                                                                                                |

|         | <ul> <li>1 = Enables the INT0 external interrupt</li> <li>0 = Disables the INT0 external interrupt</li> </ul>                                                             |

| bit 3   | RBIE: RB Port Change Interrupt Enable bit                                                                                                                                 |

|         | <ul> <li>1 = Enables the RB port change interrupt</li> <li>0 = Disables the RB port change interrupt</li> </ul>                                                           |

| bit 2   | TMR0IF: TMR0 Overflow Interrupt Flag bit                                                                                                                                  |

|         | <ul><li>1 = TMR0 register has overflowed (must be cleared in software)</li><li>0 = TMR0 register did not overflow</li></ul>                                               |

| bit 1   | INTOIF: INTO External Interrupt Flag bit                                                                                                                                  |

|         | <ul> <li>1 = The INT0 external interrupt occurred (must be cleared in software)</li> <li>0 = The INT0 external interrupt did not occur</li> </ul>                         |

| bit 0   | RBIF: RB Port Change Interrupt Flag bit <sup>(1)</sup>                                                                                                                    |

|         | <ul> <li>1 = At least one of the RB&lt;7:4&gt; pins changed state (must be cleared in software)</li> <li>0 = None of the RB&lt;7:4&gt; pins have changed state</li> </ul> |

| Note 1. | A mismatch condition will continue to set this bit. Reading PORTB will end the mismatch condition a                                                                       |

**Note 1:** A mismatch condition will continue to set this bit. Reading PORTB will end the mismatch condition and allow the bit to be cleared.

# REGISTER 10-9: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

| R/W-0                 | R/W-0                                             | R-0                  | R-0                      | R/W-0                 | R/W-0               | R/W-0           | R/W-0  |

|-----------------------|---------------------------------------------------|----------------------|--------------------------|-----------------------|---------------------|-----------------|--------|

| SSP2IE <sup>(1)</sup> | BCL2IE <sup>(1)</sup>                             | RC2IE <sup>(2)</sup> | TX2IE <sup>(2)</sup>     | TMR4IE                | CCP5IE              | CCP4IE          | CCP3IE |

| bit 7                 |                                                   |                      |                          |                       |                     | ·               | bit C  |

|                       |                                                   |                      |                          |                       |                     |                 |        |

| Legend:               |                                                   |                      |                          |                       |                     |                 |        |

| R = Readable          |                                                   | W = Writable         |                          | -                     | nented bit, read    |                 |        |

| -n = Value at F       | POR                                               | '1' = Bit is set     |                          | '0' = Bit is clea     | ared                | x = Bit is unkr | IOWN   |

| bit 7                 | SSP2IE: MSS                                       | SP2 Interrupt E      | nable bit <sup>(1)</sup> |                       |                     |                 |        |

|                       | 1 = Enabled<br>0 = Disabled                       |                      |                          |                       |                     |                 |        |

| bit 6                 | BCL2IE: Bus<br>1 = Enabled<br>0 = Disabled        | Collision Interr     | upt Enable bit           | : (MSSP2 mod          | ule) <sup>(1)</sup> |                 |        |

| bit 5                 |                                                   | RT2 Receive          | Interrupt Enab           | le bit <sup>(2)</sup> |                     |                 |        |

| bit 4                 | 0 = Disabled                                      | RT2 Transmit         | Interrupt Enab           | le bit <sup>(2)</sup> |                     |                 |        |

|                       | 1 = Enabled<br>0 = Disabled                       |                      |                          |                       |                     |                 |        |

| bit 3                 | <b>TMR4IE:</b> TMF<br>1 = Enabled<br>0 = Disabled | R4 to PR4 Mate       | ch Interrupt Er          | hable bit             |                     |                 |        |

| bit 2                 | <b>CCP5IE:</b> CCF<br>1 = Enabled<br>0 = Disabled | 25 Interrupt En      | able bit                 |                       |                     |                 |        |

| bit 1                 | <b>CCP4IE:</b> CCF<br>1 = Enabled<br>0 = Disabled | P4 Interrupt En      | able bit                 |                       |                     |                 |        |

| bit 0                 |                                                   | CP3 Interrupt E      | nable bit                |                       |                     |                 |        |

2: Implemented in 80-pin and 100-pin devices only.

| Pin Name                       | Function           | TRIS<br>Setting | I/O                                                | I/О<br>Туре | Description                                                                                                        |

|--------------------------------|--------------------|-----------------|----------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------|

| RF0/AN5 <sup>(1)</sup>         | RF0 <sup>(1)</sup> | 0               | 0                                                  | DIG         | LATF<0> data output; not affected by analog input.                                                                 |

|                                |                    | 1               | I                                                  | ST          | PORTF<0> data input; disabled when analog input is enabled.                                                        |

|                                | AN5 <sup>(1)</sup> | 1               | Ι                                                  | ANA         | A/D Input Channel 5. Default configuration on POR.                                                                 |

| RF1/AN6/                       | RF1                | 0               | 0                                                  | DIG         | LATF<1> data output; not affected by analog input.                                                                 |

| C2OUT                          |                    | 1               | I                                                  | ST          | PORTF<1> data input; disabled when analog input is enabled.                                                        |

|                                | AN6                | 1               | Ι                                                  | ANA         | A/D Input Channel 6. Default configuration on POR.                                                                 |

|                                | C2OUT              | 0               | 0                                                  | DIG         | Comparator 2 output; takes priority over port data.                                                                |

| RF2/AN7/                       | RF2                | 0               | 0                                                  | DIG         | LATF<2> data output; not affected by analog input.                                                                 |

| C1OUT                          |                    | 1               | I                                                  | ST          | PORTF<2> data input; disabled when analog input is enabled.                                                        |

|                                | AN7                | 1               | Ι                                                  | ANA         | A/D Input Channel 7. Default configuration on POR.                                                                 |

|                                | C10UT              | 0               | 0                                                  | TTL         | Comparator 1 output; takes priority over port data.                                                                |

| RF3/AN8 RF3 0 O DIG LATF<3> da |                    | DIG             | LATF<3> data output; not affected by analog input. |             |                                                                                                                    |

|                                |                    | 1               | Ι                                                  | ST          | PORTF<3> data input; disabled when analog input is enabled.                                                        |

|                                | AN8                | 1               | I                                                  | ANA         | A/D Input Channel 8 and Comparator C2+ input. Default input configuration on POR; not affected by analog output.   |

| RF4/AN9                        | RF4                | 0               | 0                                                  | DIG         | LATF<4> data output; not affected by analog input.                                                                 |

|                                |                    | 1               | Ι                                                  | ST          | PORTF<4> data input; disabled when analog input is enabled.                                                        |

|                                | AN9                | 1               | Ι                                                  | ANA         | A/D Input Channel 9 and Comparator C2- input. Default input configuration on POR; does not affect digital output.  |

| RF5/AN10/<br>CVref             | RF5                | 0               | 0                                                  | DIG         | LATF<5> data output; not affected by analog input. Disabled when CVREF output is enabled.                          |

|                                |                    | 1               | I                                                  | ST          | PORTF<5> data input; disabled when analog input is enabled. Disabled when CVREF output is enabled.                 |

|                                | AN10               | 1               | Ι                                                  | ANA         | A/D Input Channel 10 and Comparator C1+ input. Default input configuration on POR.                                 |

|                                | CVREF              | x               | 0                                                  | ANA         | Comparator voltage reference output. Enabling this feature disables digital I/O.                                   |

| RF6/AN11                       | RF6                | 0               | 0                                                  | DIG         | LATF<6> data output; not affected by analog input.                                                                 |

|                                |                    | 1               | Ι                                                  | ST          | PORTF<6> data input; disabled when analog input is enabled.                                                        |

|                                | AN11               | 1               | I                                                  | ANA         | A/D Input Channel 11 and Comparator C1- input. Default input configuration on POR; does not affect digital output. |

| RF7/SS1                        | RF7                | 0               | 0                                                  | DIG         | LATF<7> data output.                                                                                               |

|                                |                    | 1               | Ι                                                  | ST          | PORTF<7> data input.                                                                                               |

|                                | SS1                | 1               | I                                                  | TTL         | Slave select input for MSSP1 module.                                                                               |

## TABLE 11-13: PORTF FUNCTIONS

**Legend:** O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input, TTL = TTL Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: Implemented on 100-pin devices only.

#### TABLE 11-14: SUMMARY OF REGISTERS ASSOCIATED WITH PORTF

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0                 | Reset<br>Values<br>on Page: |

|--------|--------|--------|--------|--------|--------|--------|--------|-----------------------|-----------------------------|

| PORTF  | RF7    | RF6    | RF5    | RF4    | RF3    | RF2    | RF1    | RF0 <sup>(1)</sup>    | 72                          |

| LATF   | LATF7  | LATF6  | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  | LATF0 <sup>(1)</sup>  | 72                          |

| TRISF  | TRISF7 | TRISF6 | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 <sup>(1)</sup> | 71                          |

| ADCON1 | _      | —      | VCFG1  | VCFG0  | PCFG3  | PCFG2  | PCFG1  | PCFG0                 | 70                          |

| CMCON  | C2OUT  | C10UT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0                   | 70                          |

| CVRCON | CVREN  | CVROE  | CVRR   | CVRSS  | CVR3   | CVR2   | CVR1   | CVR0                  | 70                          |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PORTF.

Note 1: Implemented on 100-pin devices only.

# 14.0 TIMER2 MODULE

The Timer2 timer module incorporates the following features:

- 8-Bit Timer and Period registers (TMR2 and PR2, respectively)

- · Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4 and 1:16)

- Software programmable postscaler (1:1 through 1:16)

- Interrupt on TMR2 to PR2 match

- Optional use as the shift clock for the MSSPx modules

This module is controlled through the T2CON register (Register 14-1) which enables or disables the timer and configures the prescaler and postscaler. Timer2 can be shut off by clearing control bit, TMR2ON (T2CON<2>), to minimize power consumption.

A simplified block diagram of the module is shown in Figure 14-1.

# 14.1 Timer2 Operation

In normal operation, TMR2 is incremented from 00h on each clock (Fosc/4). A 4-bit counter/prescaler on the clock input gives direct input, divide-by-4 and divide-by-16 prescale options. These options are selected by the prescaler control bits, T2CKPS<1:0> (T2CON<1:0>). The value of TMR2 is compared to that of the Period register, PR2, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMR2 to 00h on the next cycle and drives the output counter/postscaler (see **Section 14.2** "**Timer2 Interrupt**").

The TMR2 and PR2 registers are both directly readable and writable. The TMR2 register is cleared on any device Reset, while the PR2 register initializes at FFh. Both the prescaler and postscaler counters are cleared on the following events:

- · A write to the TMR2 register

- · A write to the T2CON register

- Any device Reset (Power-on Reset, MCLR Reset, Watchdog Timer Reset or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

| U-0          | R/W-0               | R/W-0            | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0   |

|--------------|---------------------|------------------|----------------|-------------------|------------------|-----------------|---------|

| _            | T2OUTPS3            | T2OUTPS2         | T2OUTPS1       | T2OUTPS0          | TMR2ON           | T2CKPS1         | T2CKPS0 |

| bit 7        |                     |                  |                |                   |                  |                 | bit 0   |

| Legend:      |                     |                  |                |                   |                  |                 |         |

| R = Readal   | ole bit             | W = Writable     | bit            | U = Unimplen      | nented bit, read | l as '0'        |         |

| -n = Value a | at POR              | '1' = Bit is set |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |

|              |                     |                  |                |                   |                  |                 |         |

| bit 7        | Unimplement         | ted: Read as '   | כ'             |                   |                  |                 |         |

| bit 6-3      | T2OUTPS<3:          | 0>: Timer2 Ou    | tput Postscale | Select bits       |                  |                 |         |

|              | 0000 = 1:1 Po       | ostscale         |                |                   |                  |                 |         |

|              | 0001 <b>= 1:2 P</b> | ostscale         |                |                   |                  |                 |         |

|              | •                   |                  |                |                   |                  |                 |         |

|              | •                   |                  |                |                   |                  |                 |         |

|              | •                   | <b>N</b>         |                |                   |                  |                 |         |

|              | 1111 = 1:16 F       | 001000.10        |                |                   |                  |                 |         |

| bit 2        | TMR2ON: Tim         | ner2 On bit      |                |                   |                  |                 |         |

|              | 1 = Timer2 is       | •••              |                |                   |                  |                 |         |

|              | 0 = Timer2 is       | off              |                |                   |                  |                 |         |

| bit 1-0      | T2CKPS<1:0          | >: Timer2 Cloc   | k Prescale Se  | lect bits         |                  |                 |         |

|              | 00 = Prescale       | er is 1          |                |                   |                  |                 |         |

|              | 01 = Prescale       |                  |                |                   |                  |                 |         |

|              | 1x = Prescale       | er is 16         |                |                   |                  |                 |         |

# REGISTER 14-1: T2CON: TIMER2 CONTROL REGISTER

# PIC18F97J60 FAMILY

# 18.4.9 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the ECCP1 module for PWM operation:

- 1. Configure the PWM pins, P1A and P1B (and P1C and P1D, if used), as inputs by setting the corresponding TRIS bits.

- 2. Set the PWM period by loading the PR2 (PR4) register.

- Configure the ECCP1 module for the desired PWM mode and configuration by loading the CCP1CON register with the appropriate values:

- Select one of the available output configurations and direction with the P1M<1:0> bits.

- Select the polarities of the PWM output signals with the CCP1M<3:0> bits.

- 4. Set the PWM duty cycle by loading the CCPR1L register and the CCP1CON<5:4> bits.

- 5. For auto-shutdown:

- Disable auto-shutdown; ECCP1ASE = 0

- · Configure auto-shutdown source

- Wait for Run condition

- 6. For Half-Bridge Output mode, set the dead-band delay by loading ECCP1DEL<6:0> with the appropriate value.

- 7. If auto-shutdown operation is required, load the ECCP1AS register:

- Select the auto-shutdown sources using the ECCP1AS<2:0> bits.

- Select the shutdown states of the PWM output pins using PSS1AC<1:0> and PSS1BD<1:0> bits.

- Set the ECCP1ASE bit (ECCP1AS<7>).

- 8. If auto-restart operation is required, set the P1RSEN bit (ECCP1DEL<7>).

- 9. Configure and start TMR2 (TMR4):

- Clear the TMRx interrupt flag bit by clearing the TMRxIF bit (PIR1<1> for Timer2 or PIR3<3> for Timer4).

- Set the TMRx prescale value by loading the TxCKPS bits (T2CON<1:0> for Timer2 or T4CON<1:0> for Timer4).

- Enable Timer2 (or Timer4) by setting the TMRxON bit (T2CON<2> for Timer2 or T4CON<2> for Timer4).

- 10. Enable PWM outputs after a new PWM cycle has started:

- Wait until TMR2 (TMR4) overflows (TMRxIF bit is set).

- Enable the ECCP1/P1A, P1B, P1C and/or P1D pin outputs by clearing the respective TRIS bits.

- Clear the ECCP1ASE bit (ECCP1AS<7>).

#### 18.4.10 EFFECTS OF A RESET

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the CCPx/ECCPx registers to their Reset states.

This forces the Enhanced CCPx modules to reset to a state compatible with the standard CCPx modules.

# REGISTER 19-13: PHLCON: PHY MODULE LED CONTROL REGISTER

| R/W-0           | R/W-0                     | R/W-1                                      | R/W-1             | R/W-0                                 | R/W-1                     | R/W-0            | R/W-0  |

|-----------------|---------------------------|--------------------------------------------|-------------------|---------------------------------------|---------------------------|------------------|--------|

| r               | r                         | r                                          | r                 | LACFG3                                | LACFG2                    | LACFG1           | LACFG0 |

| bit 15          | •                         |                                            |                   |                                       |                           |                  | bit 8  |

|                 |                           |                                            |                   |                                       |                           |                  |        |

| R/W-0           | R/W-0                     | R/W-1                                      | R/W-0             | R/W-0                                 | R/W-0                     | R/W-1            | R/W-x  |

| LBCFG3          | LBCFG2                    | LBCFG1                                     | LBCFG0            | LFRQ1                                 | LFRQ0                     | STRCH            | r      |

| bit 7           |                           |                                            |                   |                                       |                           |                  | bit 0  |

| Legend:         |                           | r = Reserved b                             | it                |                                       |                           |                  |        |

| R = Readable    | bit                       | W = Writable b                             |                   | U = Unimplem                          | ented bit, read           | as '0'           |        |

| -n = Value at F | POR                       | '1' = Bit is set                           |                   | '0' = Bit is clea                     |                           | x = Bit is unkno | wn     |

|                 |                           |                                            |                   |                                       |                           |                  |        |

| bit 15-14       | Reserved: Wr              | i <b>te as</b> '0'                         |                   |                                       |                           |                  |        |

| bit 13-12       | Reserved: Wr              | ite as '1'                                 |                   |                                       |                           |                  |        |

| bit 11-8        | LACFG<3:0>:               | LEDA Configur                              | ation bits        |                                       |                           |                  |        |

|                 | 0000 = Reserv             |                                            | <i></i>           |                                       |                           |                  |        |

|                 |                           | y transmit activity<br>y receive activity  |                   |                                       |                           |                  |        |

|                 |                           | y collision activity                       |                   |                                       |                           |                  |        |

|                 | 0100 = Displa             |                                            | ., (00.0          |                                       |                           |                  |        |

|                 |                           | y duplex status                            |                   |                                       |                           |                  |        |

|                 | 0110 = Reserv             |                                            | anaiva antivity ( | otrotoboblo)                          |                           |                  |        |

|                 | 1000 = On                 | y transmit and re                          | eceive activity ( | stretchable)                          |                           |                  |        |

|                 | 1001 <b>= Off</b>         |                                            |                   |                                       |                           |                  |        |

|                 | 1010 <b>= Blink f</b>     |                                            |                   |                                       |                           |                  |        |

|                 | 1011 = Blink s            | slow<br>y link status and                  | roccivo octiviti  | (always strate                        |                           |                  |        |

|                 |                           | y link status and                          |                   |                                       | ,                         |                  |        |

|                 | 111x = Reserv             | -                                          |                   | , , , , , , , , , , , , , , , , , , , | , , , , , , , , , , , , , |                  |        |

| bit 7-4         | LBCFG<3:0>:               | LEDB Configur                              | ation bits        |                                       |                           |                  |        |

|                 | 0000 = Reserv             |                                            |                   |                                       |                           |                  |        |

|                 |                           | y transmit activit                         |                   |                                       |                           |                  |        |

|                 |                           | y receive activity<br>y collision activity |                   |                                       |                           |                  |        |

|                 | 0100 = Displa             |                                            | ., (00.0          |                                       |                           |                  |        |

|                 |                           | y duplex status                            |                   |                                       |                           |                  |        |

|                 | 0110 = Reserv             | ved<br>y transmit and re                   | acaiva activity ( | stratchable)                          |                           |                  |        |

|                 | 1000 = On                 | y transmit and to                          | eceive activity ( | stretchable)                          |                           |                  |        |

|                 | 1001 <b>= Off</b>         |                                            |                   |                                       |                           |                  |        |

|                 | 1010 = Blink f            |                                            |                   |                                       |                           |                  |        |

|                 | 1011 = Blink s            | siow<br>y link status and                  | receive activity  | v (always stretch                     | ned)                      |                  |        |

|                 |                           | y link status and                          |                   |                                       | ,                         |                  |        |

|                 | 111x = Reserv             | -                                          |                   |                                       |                           |                  |        |

| bit 3-2         | <b>LFRQ&lt;1:0&gt;:</b> L | ED Pulse Streto                            | h Time Configu    | uration bits (see                     | Table 19-1)               |                  |        |

|                 | 11 = Reserved             |                                            |                   |                                       |                           |                  |        |

|                 |                           | ED events by Ti<br>ED events by Ti         |                   |                                       |                           |                  |        |

|                 |                           | ED events by Tr                            |                   |                                       |                           |                  |        |

| bit 1           |                           | Pulse Stretching                           |                   |                                       |                           |                  |        |

| -               |                           | -                                          |                   | nened LED pulse                       | es based on LF            | RQ<1:0> configu  | ration |

|                 |                           | le LED events w                            |                   |                                       |                           | 5                |        |

| bit 0           | Reserved: Wr              | i <b>te as</b> '0'                         |                   |                                       |                           |                  |        |

|                 |                           |                                            |                   |                                       |                           |                  |        |

# 19.8 Receive Filters

To minimize microcontroller processing overhead, the Ethernet module incorporates a range of different receive filters which can automatically reject packets which are not needed. Six different types of packet filters are implemented:

- Unicast

- Multicast

- Broadcast

- Pattern Match

- Magic Packet<sup>™</sup>

- Hash Table

The individual filters are all configured by the ERXFCON register (Register 19-20). More than one filter can be active at any given time. Additionally, the filters can be configured by the ANDOR bit to either logically AND or logically OR the tests of several filters. In other words, the filters may be set so that only packets accepted by all active filters are accepted, or a packet accepted by any one filter is accepted. The flowcharts in Figure 19-13 and Figure 19-14 show the effect that each of the filters will have, depending on the setting of ANDOR.

The device can enter Promiscuous mode and receive all legal packets by setting the ERXFCON register to 20h (enabling only the CRC filter for valid packets). The proper setting of the register will depend on the application requirements.

#### 19.8.1 UNICAST FILTER

The Unicast receive filter checks the destination address of all incoming packets. If the destination address exactly matches the contents of the MAADR registers, the packet meets the Unicast filter criteria.

#### 19.8.2 MULTICAST FILTER

The Multicast receive filter checks the destination address of all incoming packets. If the Least Significant bit of the first byte of the destination address is set, the packet meets the Multicast filter criteria.

# 19.8.3 BROADCAST FILTER

The Broadcast receive filter checks the destination address of all incoming packets. If the destination address is FF-FF-FF-FF-FF, the packet meets the Broadcast filter criteria.

# 19.8.4 HASH TABLE FILTER

The Hash Table receive filter is typically used to receive traffic sent to a specific Multicast group address. Because it checks the specific destination address of packets, it is capable of filtering out more unwanted packets than the Multicast filter.

The filter performs a 32-bit CRC over the six destination address bytes in the packet, using the polynomial, 4C11DB7h. From the resulting 32-bit binary number, a 6-bit value is derived from bits<28:23>. This value, in turn, points to a location in a table formed by the Ethernet Hash Table registers, ETH0 through ETH7. If the bit in that location is set, the packet meets the Hash Table filter criteria and is accepted. The specific pointer values for each bit location in the table are shown in Table 19-9.

An example of the Hash Table operation is shown in Example 19-1. In this case, the destination address, 01-00-00-00-01-2C, produces a Table Pointer value of 34h, which points to bit 4 of ETH6. If this bit is '1', the packet will be accepted.

By extension, clearing every bit in the Hash Table registers means that the filter criteria will never be met. Similarly, if every bit in the Hash Table is set, the filter criteria will always be met.

# TABLE 19-9:BIT ASSIGNMENTS IN HASH<br/>TABLE REGISTERS

| Periotor | Bit Number in Hash Table |    |    |    |    |    |    |    |  |  |  |

|----------|--------------------------|----|----|----|----|----|----|----|--|--|--|

| Register | 7                        | 6  | 5  | 4  | 3  | 2  | 1  | 0  |  |  |  |

| EHT0     | 07                       | 06 | 05 | 04 | 03 | 02 | 01 | 00 |  |  |  |

| EHT1     | 0F                       | 0E | 0D | 0C | 0B | 0A | 09 | 08 |  |  |  |

| EHT2     | 17                       | 16 | 15 | 14 | 13 | 12 | 11 | 10 |  |  |  |

| EHT3     | 1F                       | 1E | 1D | 1C | 1B | 1A | 19 | 18 |  |  |  |

| EHT4     | 27                       | 26 | 25 | 24 | 23 | 22 | 21 | 20 |  |  |  |

| EHT5     | 2F                       | 2E | 2D | 2C | 2B | 2A | 29 | 28 |  |  |  |

| EHT6     | 37                       | 36 | 35 | 34 | 33 | 32 | 31 | 30 |  |  |  |

| EHT7     | 3F                       | 3E | 3D | 3C | 3B | 3A | 39 | 38 |  |  |  |

# EXAMPLE 19-1: DERIVING A HASH TABLE LOCATION

| Packet Destination Address:        |                                    |  |  |  |  |  |  |

|------------------------------------|------------------------------------|--|--|--|--|--|--|

|                                    | 01-00-00-00-01-2C (hex)            |  |  |  |  |  |  |

| Result of CRC-32 with              | n 4C11DB7h:                        |  |  |  |  |  |  |

| 110 <b>1 1010 0</b> 000 10         | 11 0100 0101 0111 0101<br>(binary) |  |  |  |  |  |  |

| Pointer Derived from               | bits<28:23> of CRC Result:         |  |  |  |  |  |  |

|                                    | 110100 (binary) or 34 (hex)        |  |  |  |  |  |  |

| Corresponding Hash Table Location: |                                    |  |  |  |  |  |  |

|                                    | ETH6<4>                            |  |  |  |  |  |  |

# 21.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is one of two serial I/O modules. (Generically, the EUSART is also known as a Serial Communications Interface or SCI.) The EUSART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers. It can also be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The Enhanced USART module implements additional features, including automatic baud rate detection and calibration, automatic wake-up on Sync Break reception and 12-bit Break character transmit. These features make it ideally suited for use in Local Interconnect Network bus (LIN/J2602 bus) systems.

The 64-pin devices of the PIC18F97J60 family are equipped with one EUSART module, referred to as EUSART1. The 80-pin and 100-pin devices each have two independent EUSART modules, referred to as EUSART1 and EUSART2. They can be configured in the following modes:

- Asynchronous (full-duplex) with:

- Auto-Wake-up on Character Reception

- Auto-Baud Calibration

- 12-Bit Break Character Transmission

- Synchronous Master (half-duplex) with Selectable Clock Polarity

- Synchronous Slave (half-duplex) with Selectable Clock Polarity

The pins of EUSART1 and EUSART2 are multiplexed with the functions of PORTC (RC6/TX1/CK1 and RC7/RX1/DT1) and PORTG (RG1/TX2/CK2 and RG2/RX2/DT2), respectively. In order to configure these pins as an EUSART:

- For EUSART1:

- SPEN bit (RCSTA1<7>) must be set (= 1)

- TRISC<7> bit must be set (= 1)

- TRISC<6> bit must be cleared (= 0) for Asynchronous and Synchronous Master modes

- TRISC<6> bit must be set (= 1) for Synchronous Slave mode

- For EUSART2:

- SPEN bit (RCSTA2<7>) must be set (= 1)

- TRISG<2> bit must be set (= 1)

- TRISG<1> bit must be cleared (= 0) for Asynchronous and Synchronous Master modes

- TRISG<1> bit must be set (= 1) for Synchronous Slave mode

Note: The EUSARTx control will automatically reconfigure the pin from input to output as needed.

The operation of each Enhanced USART module is controlled through three registers:

- Transmit Status and Control (TXSTAx)

- Receive Status and Control (RCSTAx)

- Baud Rate Control (BAUDCONx)

These are detailed on the following pages in Register 21-1, Register 21-2 and Register 21-3, respectively.

Note: Throughout this section, references to register and bit names that may be associated with a specific EUSART module are referred to generically by the use of 'x' in place of the specific module number. Thus, "RCSTAx" might refer to the Receive Status register for either EUSART1 or EUSART2.

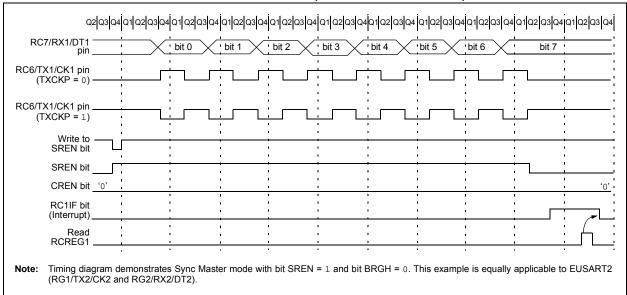

#### 21.3.2 EUSARTx SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either the Single Receive Enable bit, SREN (RCSTAx<5>), or the Continuous Receive Enable bit, CREN (RCSTAx<4>). Data is sampled on the RXx pin on the falling edge of the clock.

If enable bit, SREN, is set, only a single word is received. If enable bit, CREN, is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence.

To set up a Synchronous Master Reception:

- 1. Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. Ensure bits, CREN and SREN, are clear.

- 4. If the signal from the CKx pin is to be inverted, set the TXCKP bit. If the signal from the DTx pin is to be inverted, set the RXDTP bit.

- 5. If interrupts are desired, set enable bit, RCxIE.

- 6. If 9-bit reception is desired, set bit, RX9.

- 7. If a single reception is required, set bit, SREN. For continuous reception, set bit, CREN.

- 8. Interrupt flag bit, RCxIF, will be set when reception is complete and an interrupt will be generated if the enable bit, RCxIE, was set.

- 9. Read the RCSTAx register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREGx register.

- 11. If any error occurred, clear the error by clearing bit, CREN.

- 12. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

# FIGURE 21-13: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

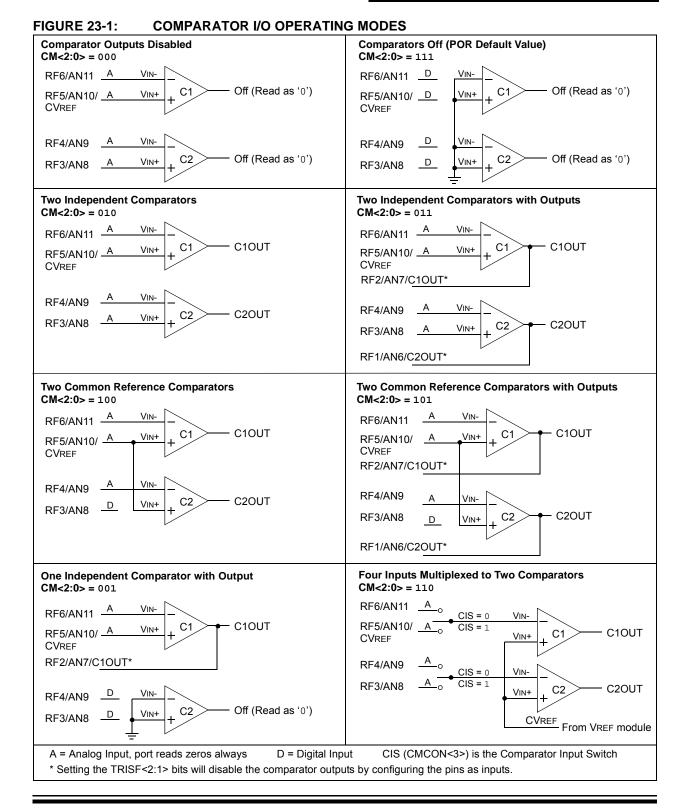

# 23.1 Comparator Configuration

There are eight modes of operation for the comparators, shown in Figure 23-1. Bits CM<2:0> of the CMCON register are used to select these modes. The TRISF register controls the data direction of the comparator pins for each mode. If the Comparator mode is changed, the comparator output level may not be valid for the specified mode change delay shown in **Section 28.0 "Electrical Characteristics"**.

Note: Comparator interrupts should be disabled during a Comparator mode change; otherwise, a false interrupt may occur.

| Byte-oriented file register operations                                                                                                                                                                                                                | Example Instruction  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 15 10 9 8 7 0                                                                                                                                                                                                                                         |                      |

| OPCODE d a f (FILE #)                                                                                                                                                                                                                                 | ADDWF MYREG, W, B    |

| <ul> <li>d = 0 for result destination to be WREG register</li> <li>d = 1 for result destination to be file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul> |                      |

| Byte to Byte move operations (2-word)                                                                                                                                                                                                                 |                      |

| <u>15 12 11 0</u>                                                                                                                                                                                                                                     |                      |