# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | C166                                                                        |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 25MHz                                                                       |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                    |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 77                                                                          |

| Program Memory Size        | -                                                                           |

| Program Memory Type        | ROMIess                                                                     |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                 |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-LQFP                                                                    |

| Supplier Device Package    | PG-TQFP-100                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/c165l25fhabxuma1 |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2000-12

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 2000. All Rights Reserved.

#### **Attention please!**

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide.

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

#### C165

| <b>Revision History:</b>                                                 |                                                                                                                                                                                      | 2000-12                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Previous Version:                                                        |                                                                                                                                                                                      | <ul> <li>1998-12 Update 0.5μ technology</li> <li>01.96 3 Volt Addendum</li> <li>07.95 25 MHz Addendum</li> <li>09.94 Data Sheet</li> </ul>                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Subjects (r                                                              | major change                                                                                                                                                                         | es since last revision)                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Converted                                                                | to Infineon lay                                                                                                                                                                      | vout                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| ROM derivatives removed, 25-MHz derivatives and 3 V derivatives included |                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Pin number                                                               | Pin numbers for TQFP added                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Address wi                                                               | ndow arbitrati                                                                                                                                                                       | on and master/slave mode introduced                                                                                                                                                                                                                                                                                                                                                                                                       | ł                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| New standa                                                               | ard layout for                                                                                                                                                                       | section "Absolute Maximum Ratings"                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Section "Op                                                              | perating Cond                                                                                                                                                                        | litions" added                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Parameter                                                                | "RSTIN pullup                                                                                                                                                                        | o" replaced by "RSTIN current"                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| DC Charac                                                                | teristics for re                                                                                                                                                                     | duced supply voltage added                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Separate sp                                                              | pecification fo                                                                                                                                                                      | r power consumption with greatly impr                                                                                                                                                                                                                                                                                                                                                                                                     | oved values                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Description                                                              | of clock gene                                                                                                                                                                        | eration improved                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Timing ada                                                               | pted to 25 MF                                                                                                                                                                        | łz                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Timing for r                                                             | educed suppl                                                                                                                                                                         | ly voltage added                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                                                                          | Subjects (r<br>Converted t<br>ROM deriva<br>included<br>Pin number<br>Address wir<br>New standa<br>Section "Op<br>Parameter<br>DC Charac<br>Separate sp<br>Description<br>Timing ada | ersion:       1998-12<br>01.96<br>07.95<br>09.94         Subjects (major change<br>Converted to Infineon lay<br>ROM derivatives remove<br>included         Pin numbers for TQFP a         Address window arbitrati         New standard layout for         Section "Operating Cond<br>Parameter "RSTIN pullup<br>DC Characteristics for re         Separate specification fo         Description of clock gene<br>Timing adapted to 25 MH | ersion:       1998-12       Update 0.5μ technology         01.96       3 Volt Addendum         07.95       25 MHz Addendum         09.94       Data Sheet         Subjects (major changes since last revision)         Converted to Infineon layout         ROM derivatives removed, 25-MHz derivatives and 3 V derivatives |  |  |  |  |

### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

#### mcdocu.comments@infineon.com

#### Introduction

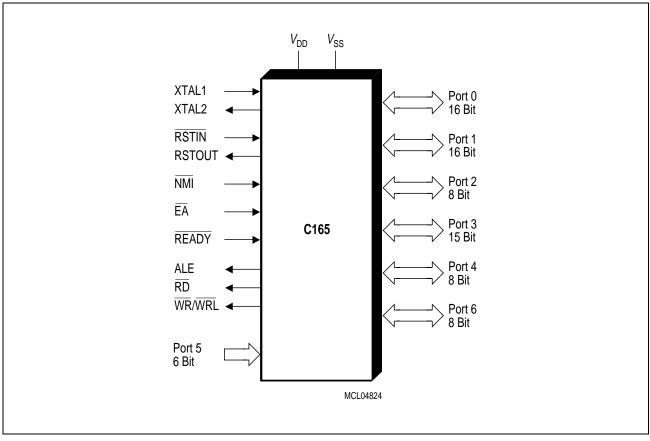

The C165 is a derivative of the Infineon C166 Family of full featured single-chip CMOS microcontrollers. It combines high CPU performance (up to 12.5 million instructions per second) with peripheral functionality and enhanced IO-capabilities. The C165 is especially suited for cost sensitive applications.

Figure 1 Logic Symbol

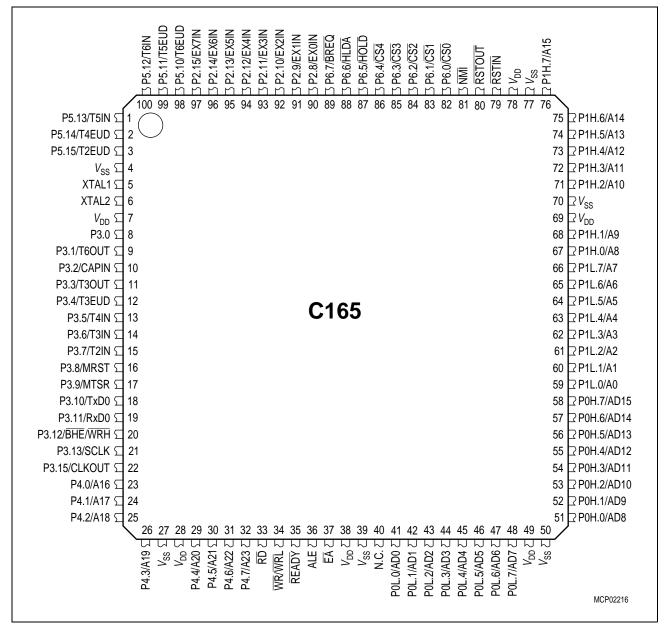

#### Pin Configuration TQFP Package

(top view)

Figure 2

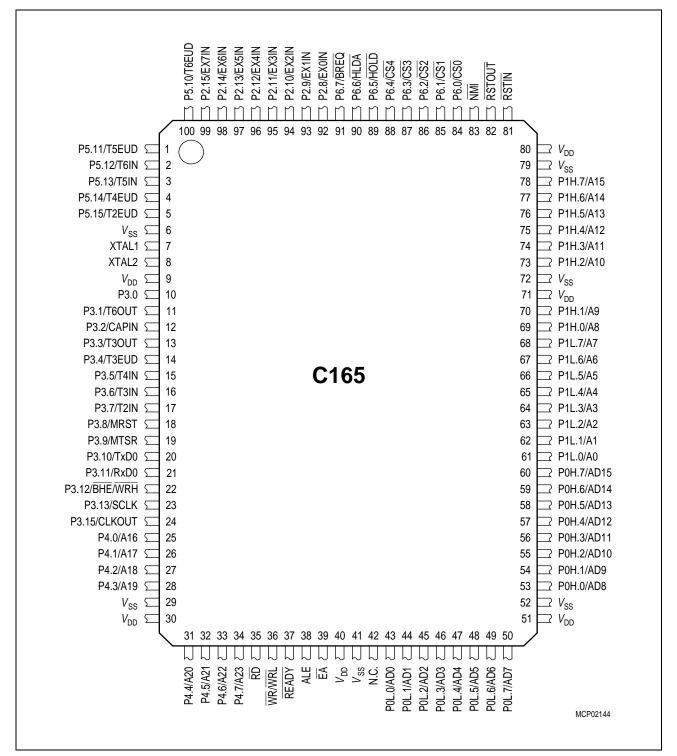

#### Pin Configuration MQFP Package

(top view)

#### Figure 3

| Symbol | Pin Nr<br>TQFP | Pin Nr<br>MQFP | Input<br>Outp. | Function                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|--------|----------------|----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| XTAL1  | 5              | 7              | I              | XTAL1:                                                                                                                                                                                                                                                              | Input to the oscillator amplifier and input to the internal clock generator                                                                                                                                                                                                   |  |  |  |  |  |

| XTAL2  | 6              | 8              | Ο              | XTAL2: Output of the oscillator amplifier circuit.<br>To clock the device from an external source, drive<br>XTAL1, while leaving XTAL2 unconnected.<br>Minimum and maximum high/low and rise/fall times<br>specified in the AC Characteristics must be<br>observed. |                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Ρ3     |                |                | IO             | programma<br>For a pin co<br>into high-in<br>configured                                                                                                                                                                                                             | 15-bit bidirectional I/O port. It is bit-wise<br>able for input or output via direction bits.<br>onfigured as input, the output driver is put<br>npedance state. Port 3 outputs can be<br>as push/pull or open drain drivers. The<br>serve for following alternate functions: |  |  |  |  |  |

| P3.0   | 8              | 10             |                |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| P3.1   | 9              | 11             | 0              | T6OUT                                                                                                                                                                                                                                                               | GPT2 Timer T6 Toggle Latch Output                                                                                                                                                                                                                                             |  |  |  |  |  |

| P3.2   | 10             | 12             |                | CAPIN                                                                                                                                                                                                                                                               | GPT2 Register CAPREL Capture Input                                                                                                                                                                                                                                            |  |  |  |  |  |

| P3.3   | 11             | 13             | 0              | T3OUT                                                                                                                                                                                                                                                               | GPT1 Timer T3 Toggle Latch Output                                                                                                                                                                                                                                             |  |  |  |  |  |

| P3.4   | 12             | 14             |                | T3EUD                                                                                                                                                                                                                                                               | GPT1 Timer T3 Ext. Up/Down Ctrl Input                                                                                                                                                                                                                                         |  |  |  |  |  |

| P3.5   | 13             | 15             | 1              | T4IN                                                                                                                                                                                                                                                                | GPT1 Timer T4                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|        |                | 10             |                | TOIN                                                                                                                                                                                                                                                                | Count/Gate/Reload/Capture Input                                                                                                                                                                                                                                               |  |  |  |  |  |

| P3.6   | 14             | 16             |                | T3IN                                                                                                                                                                                                                                                                | GPT1 Timer T3 Count/Gate Input                                                                                                                                                                                                                                                |  |  |  |  |  |

| P3.7   | 15             | 17             | 1              | T2IN                                                                                                                                                                                                                                                                | GPT1 Timer T2                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| P3.8   | 16             | 18             | I/O            | MRST                                                                                                                                                                                                                                                                | Count/Gate/Reload/Capture Input<br>SSC Master-Receive/Slave-Transmit<br>Input/Output                                                                                                                                                                                          |  |  |  |  |  |

| P3.9   | 17             | 19             | I/O            | MTSR                                                                                                                                                                                                                                                                | SSC Master-Transmit/Slave-Receive                                                                                                                                                                                                                                             |  |  |  |  |  |

| P3.10  | 18             | 20             | 0              | TxD0                                                                                                                                                                                                                                                                | ASC0 Clock/Data Output (Asyn./Sync.)                                                                                                                                                                                                                                          |  |  |  |  |  |

| P3.11  | 19             | 21             | I/O            | RxD0                                                                                                                                                                                                                                                                | ASC0 Data Inp. (Asyn.) or In/Out (Sync)                                                                                                                                                                                                                                       |  |  |  |  |  |

| P3.12  | 20             | 22             | 0              | BHE                                                                                                                                                                                                                                                                 | Ext. Memory High Byte Enable Signal,                                                                                                                                                                                                                                          |  |  |  |  |  |

|        |                |                | 0              | WRH                                                                                                                                                                                                                                                                 | Ext. Memory High Byte Write Strobe                                                                                                                                                                                                                                            |  |  |  |  |  |

| P3.13  | 21             | 23             | I/O            | SCLK                                                                                                                                                                                                                                                                | SSC Master Cl. Output / Slave Cl. Input                                                                                                                                                                                                                                       |  |  |  |  |  |

| P3.15  | 22             | 24             | 0              | CLKOUT                                                                                                                                                                                                                                                              | System Clock Output (= CPU Clock)                                                                                                                                                                                                                                             |  |  |  |  |  |

### Table 2Pin Definitions and Functions

| Symbol                                                       | Pin Nr<br>TQFP                               | Pin Nr<br>MQFP                               | Input<br>Outp.                             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------|----------------------------------------------|----------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P4.0<br>P4.1<br>P4.2<br>P4.3<br>P4.4<br>P4.5<br>P4.6<br>P4.7 | 23<br>24<br>25<br>26<br>29<br>30<br>31<br>32 | 25<br>26<br>27<br>28<br>31<br>32<br>33<br>34 | IO<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O | Port 4 is an 8-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits.<br>For a pin configured as input, the output driver is put<br>into high-impedance state. Port 4 can be used to<br>output the segment address lines:<br>A16 Least Significant Segment Address Line<br>A17 Segment Address Line<br>A18 Segment Address Line<br>A19 Segment Address Line<br>A20 Segment Address Line<br>A21 Segment Address Line<br>A22 Segment Address Line<br>A23 Most Significant Segment Address Line |

| RD                                                           | 33                                           | 35                                           | 0                                          | External Memory Read Strobe. $\overline{RD}$ is activated for every external instruction or data read access.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| WR/<br>WRL                                                   | 34                                           | 36                                           | 0                                          | External Memory Write Strobe. In $\overline{\text{WR}}$ -mode this pin<br>is activated for every external data write access. In<br>WRL-mode this pin is activated for low byte data<br>write accesses on a 16-bit bus, and for every data<br>write access on an 8-bit bus. See WRCFG in register<br>SYSCON for mode selection.                                                                                                                                                                                                           |

| READY                                                        | 35                                           | 37                                           | 1                                          | Ready Input. When the Ready function is enabled, a<br>high level at this pin during an external memory<br>access will force the insertion of memory cycle<br>waitstates until the pin returns to a low level.<br>An internal pullup device holds this pin high when<br>nothing is driving it.                                                                                                                                                                                                                                            |

| ALE                                                          | 36                                           | 38                                           | 0                                          | Address Latch Enable Output. Can be used for latching the address into external memory or an address latch in the multiplexed bus modes.                                                                                                                                                                                                                                                                                                                                                                                                 |

| ĒĀ                                                           | 37                                           | 39                                           | 1                                          | External Access Enable pin. A low level at this pin<br>during and after Reset forces the C165 to begin<br>instruction execution out of external memory. A high<br>level forces execution out of the internal program<br>memory.                                                                                                                                                                                                                                                                                                          |

# Table 2Pin Definitions and Functions (cont'd)

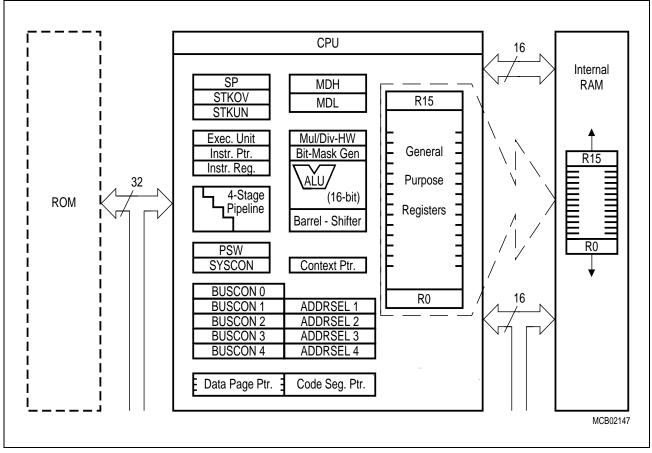

#### **Central Processing Unit (CPU)**

The main core of the CPU consists of a 4-stage instruction pipeline, a 16-bit arithmetic and logic unit (ALU) and dedicated SFRs. Additional hardware has been spent for a separate multiply and divide unit, a bit-mask generator and a barrel shifter.

Based on these hardware provisions, most of the C165's instructions can be executed in just one machine cycle which requires 80 ns at 25 MHz CPU clock. For example, shift and rotate instructions are always processed during one machine cycle independent of the number of bits to be shifted. All multiple-cycle instructions have been optimized so that they can be executed very fast as well: branches in 2 cycles, a  $16 \times 16$  bit multiplication in 5 cycles and a 32-/16 bit division in 10 cycles. Another pipeline optimization, the so-called 'Jump Cache', allows reducing the execution time of repeatedly performed jumps in a loop from 2 cycles to 1 cycle.

Figure 5

**CPU Block Diagram**

The CPU has a register context consisting of up to 16 wordwide GPRs at its disposal. These 16 GPRs are physically allocated within the on-chip RAM area. A Context Pointer (CP) register determines the base address of the active register bank to be accessed by the CPU at any time. The number of register banks is only restricted by the available internal RAM space. For easy parameter passing, a register bank may overlap others.

A system stack of up to 1024 words is provided as a storage for temporary data. The system stack is allocated in the on-chip RAM area, and it is accessed by the CPU via the stack pointer (SP) register. Two separate SFRs, STKOV and STKUN, are implicitly compared against the stack pointer value upon each stack access for the detection of a stack overflow or underflow.

The high performance offered by the hardware implementation of the CPU can efficiently be utilized by a programmer via the highly efficient C165 instruction set which includes the following instruction classes:

- Arithmetic Instructions

- Logical Instructions

- Boolean Bit Manipulation Instructions

- Compare and Loop Control Instructions

- Shift and Rotate Instructions

- Prioritize Instruction

- Data Movement Instructions

- System Stack Instructions

- Jump and Call Instructions

- Return Instructions

- System Control Instructions

- Miscellaneous Instructions

The basic instruction length is either 2 or 4 bytes. Possible operand types are bits, bytes and words. A variety of direct, indirect or immediate addressing modes are provided to specify the required operands.

Table 3

C165 Interrupt Nodes

| Source of Interrupt or | Request | Enable        | Interrupt<br>Vector | Vector<br>Location   | Trap<br>Number  |

|------------------------|---------|---------------|---------------------|----------------------|-----------------|

| PEC Service Request    | Flag    | Flag          |                     |                      |                 |

| External Interrupt 0   | CC8IR   | CC8IE         | CC8INT              | 00'0060 <sub>H</sub> | 18 <sub>H</sub> |

| External Interrupt 1   | CC9IR   | CC9IE         | CC9INT              | 00'0064 <sub>H</sub> | 19 <sub>H</sub> |

| External Interrupt 2   | CC10IR  | CC10IE        | CC10INT             | 00'0068 <sub>H</sub> | 1A <sub>H</sub> |

| External Interrupt 3   | CC11IR  | CC11IE        | CC11INT             | 00'006C <sub>H</sub> | 1B <sub>H</sub> |

| External Interrupt 4   | CC12IR  | CC12IE        | CC12INT             | 00'0070 <sub>H</sub> | 1C <sub>H</sub> |

| External Interrupt 5   | CC13IR  | CC13IE        | CC13INT             | 00'0074 <sub>H</sub> | 1D <sub>H</sub> |

| External Interrupt 6   | CC14IR  | CC14IE        | CC14INT             | 00'0078 <sub>H</sub> | 1E <sub>H</sub> |

| External Interrupt 7   | CC15IR  | CC15IE        | CC15INT             | 00'007C <sub>H</sub> | 1F <sub>H</sub> |

| GPT1 Timer 2           | T2IR    | T2IE          | T2INT               | 00'0088 <sub>H</sub> | 22 <sub>H</sub> |

| GPT1 Timer 3           | T3IR    | T3IE          | T3INT               | 00'008C <sub>H</sub> | 23 <sub>H</sub> |

| GPT1 Timer 4           | T4IR    | T4IE          | T4INT               | 00'0090 <sub>H</sub> | 24 <sub>H</sub> |

| GPT2 Timer 5           | T5IR    | T5IE          | T5INT               | 00'0094 <sub>H</sub> | 25 <sub>H</sub> |

| GPT2 Timer 6           | T6IR    | T6IE          | T6INT               | 00'0098 <sub>H</sub> | 26 <sub>H</sub> |

| GPT2 CAPREL Reg.       | CRIR    | CRIE          | CRINT               | 00'009C <sub>H</sub> | 27 <sub>H</sub> |

| ASC0 Transmit          | S0TIR   | SOTIE         | SOTINT              | 00'00A8 <sub>H</sub> | 2A <sub>H</sub> |

| ASC0 Transmit Buffer   | S0TBIR  | <b>S0TBIE</b> | <b>S0TBINT</b>      | 00'011C <sub>H</sub> | 47 <sub>H</sub> |

| ASC0 Receive           | SORIR   | SORIE         | SORINT              | 00'00AC <sub>H</sub> | 2B <sub>H</sub> |

| ASC0 Error             | S0EIR   | SOEIE         | SOEINT              | 00'00B0 <sub>H</sub> | 2C <sub>H</sub> |

| SSC Transmit           | SCTIR   | SCTIE         | SCTINT              | 00'00B4 <sub>H</sub> | 2D <sub>H</sub> |

| SSC Receive            | SCRIR   | SCRIE         | SCRINT              | 00'00B8 <sub>H</sub> | 2E <sub>H</sub> |

| SSC Error              | SCEIR   | SCEIE         | SCEINT              | 00'00BC <sub>H</sub> | 2F <sub>H</sub> |

| Unassigned node        | XP0IR   | XP0IE         | XP0INT              | 00'0100 <sub>H</sub> | 40 <sub>H</sub> |

| Unassigned node        | XP1IR   | XP1IE         | XP1INT              | 00'0104 <sub>H</sub> | 41 <sub>H</sub> |

| Unassigned node        | XP2IR   | XP2IE         | XP2INT              | 00'0108 <sub>H</sub> | 42 <sub>H</sub> |

| Unassigned node        | XP3IR   | XP3IE         | XP3INT              | 00'010C <sub>H</sub> | 43 <sub>H</sub> |

| Unassigned node        | CC29IR  | CC29IE        | CC29INT             | 00'0110 <sub>H</sub> | 44 <sub>H</sub> |

| Unassigned node        | CC30IR  | CC30IE        | CC30INT             | 00'0114 <sub>H</sub> | 45 <sub>H</sub> |

| Unassigned node        | CC31IR  | CC31IE        | CC31INT             | 00'0118 <sub>H</sub> | 46 <sub>H</sub> |

|                        | 1       | I             | 1                   | 1                    | 1               |

#### **General Purpose Timer (GPT) Unit**

The GPT unit represents a very flexible multifunctional timer/counter structure which may be used for many different time related tasks such as event timing and counting, pulse width and duty cycle measurements, pulse generation, or pulse multiplication.

The GPT unit incorporates five 16-bit timers which are organized in two separate modules, GPT1 and GPT2. Each timer in each module may operate independently in a number of different modes, or may be concatenated with another timer of the same module.

Each of the three timers T2, T3, T4 of **module GPT1** can be configured individually for one of four basic modes of operation, which are Timer, Gated Timer, Counter, and Incremental Interface Mode. In Timer Mode, the input clock for a timer is derived from the CPU clock, divided by a programmable prescaler, while Counter Mode allows a timer to be clocked in reference to external events.

Pulse width or duty cycle measurement is supported in Gated Timer Mode, where the operation of a timer is controlled by the 'gate' level on an external input pin. For these purposes, each timer has one associated port pin (TxIN) which serves as gate or clock input. The maximum resolution of the timers in module GPT1 is 16 TCL.

The count direction (up/down) for each timer is programmable by software or may additionally be altered dynamically by an external signal on a port pin (TxEUD) to facilitate e.g. position tracking.

In Incremental Interface Mode the GPT1 timers (T2, T3, T4) can be directly connected to the incremental position sensor signals A and B via their respective inputs TxIN and TxEUD. Direction and count signals are internally derived from these two input signals, so the contents of the respective timer Tx corresponds to the sensor position. The third position sensor signal TOP0 can be connected to an interrupt input.

Timer T3 has an output toggle latch (T3OTL) which changes its state on each timer overflow/underflow. The state of this latch may be output on pin T3OUT e.g. for time out monitoring of external hardware components, or may be used internally to clock timers T2 and T4 for measuring long time periods with high resolution.

In addition to their basic operating modes, timers T2 and T4 may be configured as reload or capture registers for timer T3. When used as capture or reload registers, timers T2 and T4 are stopped. The contents of timer T3 is captured into T2 or T4 in response to a signal at their associated input pins (TxIN). Timer T3 is reloaded with the contents of T2 or T4 triggered either by an external signal or by a selectable state transition of its toggle latch T3OTL. When both T2 and T4 are configured to alternately reload T3 on opposite state transitions of T3OTL with the low and high times of a PWM signal, this signal can be constantly generated without software intervention.

| Table 6C165 Registers, Ordered by Name (cont'd) |                   |                   |                |                 |                                         |                   |  |  |  |

|-------------------------------------------------|-------------------|-------------------|----------------|-----------------|-----------------------------------------|-------------------|--|--|--|

| Name                                            | Physica<br>Addres |                   | 8-Bit<br>Addr. | Description     | Reset<br>Value                          |                   |  |  |  |

| СР                                              |                   | FE10 <sub>H</sub> |                | 08 <sub>H</sub> | CPU Context Pointer Register            | FC00 <sub>H</sub> |  |  |  |

| CRIC                                            | b                 | FF6A <sub>H</sub> |                | B5 <sub>H</sub> | GPT2 CAPREL Interrupt Ctrl. Reg.        | 0000 <sub>H</sub> |  |  |  |

| CSP                                             |                   | FE08 <sub>H</sub> |                | 04 <sub>H</sub> | CPU Code Seg. Pointer Reg. (read only)  | 0000 <sub>H</sub> |  |  |  |

| DP0H                                            | b                 | F102 <sub>H</sub> | Ε              | 81 <sub>H</sub> | P0H Direction Control Register          | 00 <sub>H</sub>   |  |  |  |

| DP0L                                            | b                 | F100 <sub>H</sub> | Ε              | 80 <sub>H</sub> | P0L Direction Control Register          | 00 <sub>H</sub>   |  |  |  |

| DP1H                                            | b                 | F106 <sub>H</sub> | Ε              | 83 <sub>H</sub> | P1H Direction Control Register          | 00 <sub>H</sub>   |  |  |  |

| DP1L                                            | b                 | F104 <sub>H</sub> | Ε              | 82 <sub>H</sub> | P1L Direction Control Register          | 00 <sub>H</sub>   |  |  |  |

| DP2                                             | b                 | FFC2 <sub>H</sub> |                | E1 <sub>H</sub> | Port 2 Direction Control Register       | 0000 <sub>H</sub> |  |  |  |

| DP3                                             | b                 | FFC6 <sub>H</sub> |                | E3 <sub>H</sub> | Port 3 Direction Control Register       | 0000 <sub>H</sub> |  |  |  |

| DP4                                             | b                 | FFCA <sub>H</sub> |                | E5 <sub>H</sub> | Port 4 Direction Control Register       | 00 <sub>H</sub>   |  |  |  |

| DP6                                             | b                 | FFCE <sub>H</sub> |                | E7 <sub>H</sub> | Port 6 Direction Control Register       | 00 <sub>H</sub>   |  |  |  |

| DPP0                                            |                   | FE00 <sub>H</sub> |                | 00 <sub>H</sub> | CPU Data Page Pointer 0 Reg. (10 bits)  | 0000 <sub>H</sub> |  |  |  |

| DPP1                                            |                   | FE02 <sub>H</sub> |                | 01 <sub>H</sub> | CPU Data Page Pointer 1 Reg. (10 bits)  | 0001 <sub>H</sub> |  |  |  |

| DPP2                                            |                   | FE04 <sub>H</sub> |                | 02 <sub>H</sub> | CPU Data Page Pointer 2 Reg. (10 bits)  | 0002 <sub>H</sub> |  |  |  |

| DPP3                                            |                   | FE06 <sub>H</sub> |                | 03 <sub>H</sub> | CPU Data Page Pointer 3 Reg. (10 bits)  | 0003 <sub>H</sub> |  |  |  |

| EXICON                                          | b                 | F1C0 <sub>H</sub> | Ε              | E0 <sub>H</sub> | External Interrupt Control Register     | 0000 <sub>H</sub> |  |  |  |

| IDCHIP                                          |                   | F07C <sub>H</sub> | Ε              | 3E <sub>H</sub> | Identifier                              | 05XX <sub>H</sub> |  |  |  |

| IDMANUF                                         |                   | F07E <sub>H</sub> | Ε              | 3F <sub>H</sub> | Identifier                              | 1820 <sub>H</sub> |  |  |  |

| IDMEM                                           |                   | F07A <sub>H</sub> | Ε              | 3D <sub>H</sub> | Identifier                              | 0000 <sub>H</sub> |  |  |  |

| IDMEM2                                          |                   | F076 <sub>H</sub> | Ε              | 3B <sub>H</sub> | Identifier                              | 0000 <sub>H</sub> |  |  |  |

| IDPROG                                          |                   | F078 <sub>H</sub> | Ε              | 3C <sub>H</sub> | Identifier                              | 0000 <sub>H</sub> |  |  |  |

| MDC                                             | b                 | FF0E <sub>H</sub> |                | 87 <sub>H</sub> | CPU Multiply Divide Control Register    | 0000 <sub>H</sub> |  |  |  |

| MDH                                             |                   | FE0C <sub>H</sub> |                | 06 <sub>H</sub> | CPU Multiply Divide Reg. – High Word    | 0000 <sub>H</sub> |  |  |  |

| MDL                                             |                   | FE0E <sub>H</sub> |                | 07 <sub>H</sub> | CPU Multiply Divide Reg. – Low Word     | 0000 <sub>H</sub> |  |  |  |

| ODP2                                            | b                 | F1C2 <sub>H</sub> | Ε              | E1 <sub>H</sub> | Port 2 Open Drain Control Register      | 0000 <sub>H</sub> |  |  |  |

| ODP3                                            | b                 | F1C6 <sub>H</sub> | Ε              | E3 <sub>H</sub> | Port 3 Open Drain Control Register      | 0000 <sub>H</sub> |  |  |  |

| ODP6                                            | b                 | F1CE <sub>H</sub> | Ε              | E7 <sub>H</sub> | Port 6 Open Drain Control Register      | 00 <sub>H</sub>   |  |  |  |

| ONES                                            | b                 | FF1E <sub>H</sub> |                | 8F <sub>H</sub> | Constant Value 1's Register (read only) | FFFF <sub>H</sub> |  |  |  |

|                                                 |                   | 1                 |                | 1               |                                         |                   |  |  |  |

P0H

P0L

00<sub>H</sub>

00<sub>H</sub>

Port 0 High Reg. (Upper half of PORT0)

Port 0 Low Reg. (Lower half of PORT0)

81<sub>H</sub>

80<sub>H</sub>

FF02<sub>H</sub>

$FF00_{H}$

b

b

### **Absolute Maximum Ratings**

| Parameter                                                                  | Symbol            | Limit | Values                | Unit | Notes      |

|----------------------------------------------------------------------------|-------------------|-------|-----------------------|------|------------|

|                                                                            |                   | min.  | max.                  |      |            |

| Storage temperature                                                        | T <sub>ST</sub>   | - 65  | 150                   | °C   | _          |

| Junction temperature                                                       | TJ                | - 40  | 150                   | °C   | under bias |

| Voltage on $V_{\text{DD}}$ pins with respect to ground ( $V_{\text{SS}}$ ) | V <sub>DD</sub>   | - 0.5 | 6.5                   | V    | -          |

| Voltage on any pin with respect to ground $(V_{SS})$                       | V <sub>IN</sub>   | - 0.5 | V <sub>DD</sub> + 0.5 | V    | -          |

| Input current on any pin during overload condition                         | -                 | - 10  | 10                    | mA   | -          |

| Absolute sum of all input<br>currents during overload<br>condition         | -                 | -     | 100                   | mA   | -          |

| Power dissipation                                                          | P <sub>DISS</sub> | -     | 1.5                   | W    | -          |

#### Table 7 Absolute Maximum Rating Parameters

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DD}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DD}$  pins with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

#### **Parameter Interpretation**

The parameters listed in the following partly represent the characteristics of the C165 and partly its demands on the system. To aid in interpreting the parameters right, when evaluating them for a design, they are marked in column "Symbol":

CC (Controller Characteristics):

The logic of the C165 will provide signals with the respective timing characteristics.

**SR** (**S**ystem **R**equirement):

The external system must provide signals with the respective timing characteristics to the C165.

#### DC Characteristics (Standard Supply Voltage Range)

(Operating Conditions apply)<sup>1)</sup>

| Parameter                                                                                          | Symbol                          | Limit '                      | Values                       | Unit | <b>Test Condition</b>                           |  |

|----------------------------------------------------------------------------------------------------|---------------------------------|------------------------------|------------------------------|------|-------------------------------------------------|--|

|                                                                                                    |                                 | min.                         | max.                         |      |                                                 |  |

| Input low voltage (TTL,<br>all except XTAL1)                                                       | V <sub>IL</sub> SR              | - 0.5                        | 0.2 V <sub>DD</sub><br>- 0.1 | V    | -                                               |  |

| Input low voltage XTAL1                                                                            | $V_{IL2}$ SR                    | - 0.5                        | 0.3 V <sub>DD</sub>          | V    | -                                               |  |

| Input high voltage (TTL,<br>all except RSTIN and XTAL1)                                            | V <sub>IH</sub> SR              | 0.2 V <sub>DD</sub><br>+ 0.9 | V <sub>DD</sub> + 0.5        | V    | _                                               |  |

| Input high voltage RSTIN<br>(when operated as input)                                               | V <sub>IH1</sub> SR             | 0.6 V <sub>DD</sub>          | V <sub>DD</sub> + 0.5        | V    | _                                               |  |

| Input high voltage XTAL1                                                                           | V <sub>IH2</sub> SR             | 0.7 V <sub>DD</sub>          | V <sub>DD</sub> +<br>0.5     | V    | _                                               |  |

| Output low voltage<br>(PORT0, PORT1, Port 4, ALE,<br>RD, WR, BHE, RSTOUT,<br>RSTIN <sup>2)</sup> ) | V <sub>OL</sub> CC              | -                            | 0.45                         | V    | I <sub>OL</sub> = 2.4 mA                        |  |

| Output low voltage<br>(all other outputs)                                                          | V <sub>OL1</sub> CC             | _                            | 0.45                         | V    | <i>I</i> <sub>OL</sub> = 1.6 mA                 |  |

| Output high voltage <sup>3)</sup>                                                                  | V <sub>OH</sub> CC              | 2.4                          | _                            | V    | I <sub>OH</sub> = - 2.4 mA                      |  |

| (PORT0, PORT1, Port 4, ALE,<br>RD, WR, BHE, RSTOUT)                                                |                                 | 0.9 V <sub>DD</sub>          | _                            | V    | I <sub>OH</sub> = - 0.5 mA                      |  |

| Output high voltage <sup>3)</sup>                                                                  | V <sub>OH1</sub> CC             | 2.4                          | _                            | V    | I <sub>OH</sub> = - 1.6 mA                      |  |

| (all other outputs)                                                                                |                                 | 0.9 V <sub>DD</sub>          | _                            | V    | I <sub>OH</sub> = - 0.5 mA                      |  |

| Input leakage current (Port 5)                                                                     | I <sub>OZ1</sub> CC             | -                            | ± 200                        | nA   | $0 V < V_{IN} < V_{DD}$                         |  |

| Input leakage current (all other)                                                                  | I <sub>OZ2</sub> CC             | _                            | ± 500                        | nA   | $0.45 \text{ V} < V_{\text{IN}} < V_{\text{E}}$ |  |

| RSTIN inactive current <sup>4)</sup>                                                               | I <sub>RSTH</sub> <sup>5)</sup> | _                            | - 10                         | μA   | $V_{\rm IN} = V_{\rm IH1}$                      |  |

# DC Characteristics (Reduced Supply Voltage Range) (cont'd)

(Operating Conditions apply)<sup>1)</sup>

| Parameter                                                 | Symbol                                | Limit Values |      | Unit | Test Condition                      |

|-----------------------------------------------------------|---------------------------------------|--------------|------|------|-------------------------------------|

|                                                           |                                       | min.         | max. |      |                                     |

| PORT0 configuration current <sup>8)</sup>                 | I <sub>P0H</sub> <sup>5)</sup>        | _            | - 5  | μA   | $V_{\rm IN} = V_{\rm IHmin}$        |

|                                                           | <i>I</i> <sub>P0L</sub> <sup>6)</sup> | - 100        | _    | μA   | $V_{\rm IN} = V_{\rm ILmax}$        |

| XTAL1 input current                                       | I <sub>IL</sub> CC                    | _            | ± 20 | μA   | $0 V < V_{IN} < V_{DD}$             |

| Pin capacitance <sup>9)</sup><br>(digital inputs/outputs) | C <sub>IO</sub> CC                    | _            | 10   | pF   | f = 1  MHz<br>$T_A = 25 \text{ °C}$ |

<sup>1)</sup> Keeping signal levels within the levels specified in this table, ensures operation without overload conditions. For signal levels outside these specifications also refer to the specification of the overload current  $I_{OV}$ .

<sup>2)</sup> Valid in bidirectional reset mode only.

<sup>3)</sup> This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage results from the external circuitry.

- <sup>4)</sup> These parameters describe the  $\overline{\text{RSTIN}}$  pullup, which equals a resistance of ca. 50 to 250 k $\Omega$ .

- <sup>5)</sup> The maximum current may be drawn while the respective signal line remains inactive.

- <sup>6)</sup> The minimum current must be drawn in order to drive the respective signal line active.

- <sup>7)</sup> This specification is valid during Reset and during Hold-mode or Adapt-mode. During Hold-mode Port 6 pins are only affected, if they are used (configured) for CS output and the open drain function is not enabled. The READY-pullup is always active, except for Powerdown mode.

- <sup>8)</sup> This specification is valid during Reset and during Adapt-mode.

- <sup>9)</sup> Not 100% tested, guaranteed by design and characterization.

#### **Memory Cycle Variables**

The timing tables below use three variables which are derived from the BUSCONx registers and represent the special characteristics of the programmed memory cycle. The following table describes, how these variables are to be computed.

#### Table 12Memory Cycle Variables

| Description                  | Symbol         | Values                      |

|------------------------------|----------------|-----------------------------|

| ALE Extension                | t <sub>A</sub> | TCL × <alectl></alectl>     |

| Memory Cycle Time Waitstates | t <sub>C</sub> | 2TCL × (15 - <mctc>)</mctc> |

| Memory Tristate Time         | t <sub>F</sub> | 2TCL × (1 - <mttc>)</mttc>  |

Note: Please respect the maximum operating frequency of the respective derivative.

#### **AC Characteristics**

#### Multiplexed Bus (Standard Supply Voltage Range)

(Operating Conditions apply)

ALE cycle time = 6 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (120 ns at 25 MHz CPU clock without waitstates)

| Parameter                                                   |                        | nbol | Max. CPU Clock<br>= 25 MHz   |      | Variable (<br>1 / 2TCL =             | Unit    |    |

|-------------------------------------------------------------|------------------------|------|------------------------------|------|--------------------------------------|---------|----|

|                                                             |                        |      | min.                         | max. | min.                                 | max.    |    |

| ALE high time                                               | <i>t</i> 5             | CC   | $10 + t_{A}$                 | _    | TCL - 10<br>+ <i>t</i> <sub>A</sub>  | -       | ns |

| Address setup to ALE                                        | <i>t</i> <sub>6</sub>  | CC   | $4 + t_A$                    | _    | TCL - 16<br>+ <i>t</i> <sub>A</sub>  | -       | ns |

| Address hold after ALE                                      | <i>t</i> <sub>7</sub>  | CC   | $10 + t_{A}$                 | _    | TCL - 10<br>+ <i>t</i> <sub>A</sub>  | _       | ns |

| ALE falling edge to $\overline{RD}$ ,<br>WR (with RW-delay) | <i>t</i> 8             | CC   | $10 + t_{A}$                 | _    | TCL - 10<br>+ <i>t</i> <sub>A</sub>  | _       | ns |

| ALE falling edge to $\overline{RD}$ ,<br>WR (no RW-delay)   | t <sub>9</sub>         | СС   | - 10 + <i>t</i> <sub>A</sub> | _    | - 10 + <i>t</i> <sub>A</sub>         | _       | ns |

| Address float after RD,<br>WR (with RW-delay)               | t <sub>10</sub>        | CC   | -                            | 6    | -                                    | 6       | ns |

| Address float after RD,<br>WR (no RW-delay)                 | <i>t</i> <sub>11</sub> | CC   | -                            | 26   | -                                    | TCL + 6 | ns |

| RD, WR low time<br>(with RW-delay)                          | t <sub>12</sub>        | CC   | $30 + t_{\rm C}$             | _    | 2TCL - 10<br>+ <i>t</i> <sub>C</sub> | _       | ns |

### Multiplexed Bus (Standard Supply Voltage Range) (cont'd)

(Operating Conditions apply)

ALE cycle time = 6 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (120 ns at 25 MHz CPU clock without waitstates)

| Parameter                                                                               | Symbol                 |    | Max. CPU Clock<br>= 25 MHz |                            | Variable (<br>1 / 2TCL =             | Unit                                                         |    |

|-----------------------------------------------------------------------------------------|------------------------|----|----------------------------|----------------------------|--------------------------------------|--------------------------------------------------------------|----|

|                                                                                         |                        |    | min.                       | max.                       | min.                                 | max.                                                         |    |

| RD, WR low time<br>(no RW-delay)                                                        | <i>t</i> <sub>13</sub> | CC | $50 + t_{\rm C}$           | -                          | 3TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                                            | ns |

| RD to valid data in (with RW-delay)                                                     | <i>t</i> <sub>14</sub> | SR | -                          | $20 + t_{\rm C}$           | -                                    | 2TCL - 20<br>+ <i>t</i> <sub>C</sub>                         | ns |

| RD to valid data in (no RW-delay)                                                       | t <sub>15</sub>        | SR | _                          | $40 + t_{\rm C}$           | -                                    | 3TCL - 20<br>+ <i>t</i> <sub>C</sub>                         | ns |

| ALE low to valid data in                                                                | t <sub>16</sub>        | SR | _                          | $40 + t_A + t_C$           | _                                    | 3TCL - 20<br>+ <i>t</i> <sub>A</sub> + <i>t</i> <sub>C</sub> | ns |

| Address to valid data in                                                                | t <sub>17</sub>        | SR | _                          | $50 + 2t_A + t_C$          | _                                    | $4TCL - 30 + 2t_A + t_C$                                     | ns |

| Data hold after RD rising edge                                                          | t <sub>18</sub>        | SR | 0                          | _                          | 0                                    | -                                                            | ns |

| Data float after RD                                                                     | t <sub>19</sub>        | SR | _                          | 26 + <i>t</i> <sub>F</sub> | -                                    | 2TCL - 14<br>+ <i>t</i> <sub>F</sub>                         | ns |

| Data valid to WR                                                                        | t <sub>22</sub>        | CC | $20 + t_{\rm C}$           | -                          | 2TCL - 20<br>+ <i>t</i> <sub>C</sub> | -                                                            | ns |

| Data hold after $\overline{WR}$                                                         | t <sub>23</sub>        | CC | 26 + <i>t</i> <sub>F</sub> | -                          | 2TCL - 14<br>+ <i>t</i> <sub>F</sub> | -                                                            | ns |

| $\frac{\text{ALE rising edge after }\overline{\text{RD}},}{\overline{\text{WR}}}$       | t <sub>25</sub>        | CC | 26 + <i>t</i> <sub>F</sub> | -                          | 2TCL - 14<br>+ <i>t</i> <sub>F</sub> | -                                                            | ns |

| Address hold after RD,<br>WR                                                            | t <sub>27</sub>        | CC | 26 + <i>t</i> <sub>F</sub> | -                          | 2TCL - 14<br>+ <i>t</i> <sub>F</sub> | -                                                            | ns |

| ALE falling edge to $\overline{CS}^{1)}$                                                | t <sub>38</sub>        | CC | - 4 - t <sub>A</sub>       | 10 - <i>t</i> <sub>A</sub> | - 4 - t <sub>A</sub>                 | 10 - <i>t</i> <sub>A</sub>                                   | ns |

| CS low to Valid Data In <sup>1)</sup>                                                   | t <sub>39</sub>        | SR | _                          | $40 + t_{C} + 2t_{A}$      | -                                    | $3TCL - 20 + t_{C} + 2t_{A}$                                 | ns |

| $\overline{\text{CS}}$ hold after $\overline{\text{RD}}$ , $\overline{\text{WR}}^{(1)}$ | <i>t</i> <sub>40</sub> | CC | 46 + <i>t</i> <sub>F</sub> | -                          | 3TCL - 14<br>+ <i>t</i> <sub>F</sub> | -                                                            | ns |

| ALE fall. edge to RdCS,<br>WrCS (with RW delay)                                         | <i>t</i> <sub>42</sub> | CC | 16 + <i>t</i> <sub>A</sub> | -                          | TCL - 4<br>+ <i>t</i> <sub>A</sub>   | -                                                            | ns |

| ALE fall. edge to RdCS,<br>WrCS (no RW delay)                                           | t <sub>43</sub>        | CC | $-4 + t_{A}$               | -                          | - 4<br>+ <i>t</i> <sub>A</sub>       | -                                                            | ns |

## Demultiplexed Bus (Standard Supply Voltage Range) (cont'd)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (80 ns at 25 MHz CPU clock without waitstates)

| Parameter                                              | Symbol                    | I Max. CPU Clock<br>= 25 MHz |                            | Variable CPU Clock<br>1 / 2TCL = 1 to 25 MHz |                                   | Unit |

|--------------------------------------------------------|---------------------------|------------------------------|----------------------------|----------------------------------------------|-----------------------------------|------|

|                                                        |                           | min.                         | max.                       | min.                                         | max.                              |      |

| Data float after RdCS<br>(with RW-delay) <sup>1)</sup> | <i>t</i> <sub>53</sub> SR | _                            | 20 + <i>t</i> <sub>F</sub> | -                                            | 2TCL - 20<br>+ $2t_A + t_F$<br>1) | ns   |

| Data float after RdCS<br>(no RW-delay) <sup>1)</sup>   | <i>t</i> <sub>68</sub> SR | -                            | 0 + <i>t</i> <sub>F</sub>  | -                                            | TCL - 20<br>+ $2t_A + t_F$<br>1)  | ns   |

| Address hold after<br>RdCS, WrCS                       | <i>t</i> <sub>55</sub> CC | - 6 + <i>t</i> <sub>F</sub>  | -                          | - 6 + <i>t</i> <sub>F</sub>                  | -                                 | ns   |