Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | -                                                                           |

| Core Size                  | -                                                                           |

| Speed                      | -                                                                           |

| Connectivity               | -                                                                           |

| Peripherals                | -                                                                           |

| Number of I/O              | -                                                                           |

| Program Memory Size        | -                                                                           |

| Program Memory Type        | -                                                                           |

| EEPROM Size                | -                                                                           |

| RAM Size                   | -                                                                           |

| Voltage - Supply (Vcc/Vdd) | -                                                                           |

| Data Converters            | -                                                                           |

| Oscillator Type            | -                                                                           |

| Operating Temperature      | -                                                                           |

| Mounting Type              | -                                                                           |

| Package / Case             | -                                                                           |

| Supplier Device Package    | -                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/c165lf3vhabxuma1 |

#### **Edition 2000-12**

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany

© Infineon Technologies AG 2000.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide.

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

### C165

| Revision History: 2000-12         |                                                                          | V2.0                                                                                                                                       |                                                |  |  |  |  |

|-----------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--|--|--|--|

| Previous Version:                 |                                                                          | <ul> <li>1998-12 Update 0.5μ technology</li> <li>01.96 3 Volt Addendum</li> <li>07.95 25 MHz Addendum</li> <li>09.94 Data Sheet</li> </ul> |                                                |  |  |  |  |

| Page                              | Subjects (r                                                              | major changes since last revision)                                                                                                         |                                                |  |  |  |  |

| All                               | Converted t                                                              | Converted to Infineon layout                                                                                                               |                                                |  |  |  |  |

| 2                                 | ROM derivatives removed, 25-MHz derivatives and 3 V derivatives included |                                                                                                                                            |                                                |  |  |  |  |

| 6ff                               | Pin number                                                               | Pin numbers for TQFP added                                                                                                                 |                                                |  |  |  |  |

| 14                                | Address wir                                                              | ndow arbitration                                                                                                                           | on and master/slave mode introduced            |  |  |  |  |

| 32                                | New standa                                                               | ard layout for s                                                                                                                           | section "Absolute Maximum Ratings"             |  |  |  |  |

| 33                                | Section "Op                                                              | erating Cond                                                                                                                               | itions" added                                  |  |  |  |  |

| <b>34</b> f                       | Parameter '                                                              | 'RSTIN pullup                                                                                                                              | o" replaced by "RSTIN current"                 |  |  |  |  |

| <b>36</b> f                       | DC Charact                                                               | teristics for red                                                                                                                          | duced supply voltage added                     |  |  |  |  |

| <b>38</b> f                       | Separate sp                                                              | ecification for                                                                                                                            | power consumption with greatly improved values |  |  |  |  |

| <b>40</b> ff                      | Description                                                              | of clock gene                                                                                                                              | ration improved                                |  |  |  |  |

| <b>45</b> , <b>55</b> , <b>65</b> | Timing adap                                                              | oted to 25 MH                                                                                                                              | z                                              |  |  |  |  |

| 48, 58, 66                        | Timing for r                                                             | educed suppl                                                                                                                               | y voltage added                                |  |  |  |  |

## **We Listen to Your Comments**

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

This document describes several derivatives of the C165 group. **Table 1** enumerates these derivatives and summarizes the differences. As this document refers to all of these derivatives, some descriptions may not apply to a specific product.

Table 1 C165 Derivative Synopsis

| Derivative <sup>1)</sup> | Max. Operating Frequency | Operating Voltage | Package  |

|--------------------------|--------------------------|-------------------|----------|

| SAF-C165-LM              | 20 MHz                   | 4.5 to 5.5 V      | MQFP-100 |

| SAB-C165-LM              | 20 MHz                   | 4.5 to 5.5 V      | MQFP-100 |

| SAF-C165-L25M            | 25 MHz                   | 4.5 to 5.5 V      | MQFP-100 |

| SAB-C165-L25M            | 25 MHz                   | 4.5 to 5.5 V      | MQFP-100 |

| SAF-C165-LF              | 20 MHz                   | 4.5 to 5.5 V      | TQFP-100 |

| SAB-C165-LF              | 20 MHz                   | 4.5 to 5.5 V      | TQFP-100 |

| SAF-C165-L25F            | 25 MHz                   | 4.5 to 5.5 V      | TQFP-100 |

| SAB-C165-L25F            | 25 MHz                   | 4.5 to 5.5 V      | TQFP-100 |

| SAF-C165-LM3V            | 20 MHz                   | 3.0 to 3.6 V      | MQFP-100 |

| SAB-C165-LM3V            | 20 MHz                   | 3.0 to 3.6 V      | MQFP-100 |

| SAF-C165-LF3V            | 20 MHz                   | 3.0 to 3.6 V      | TQFP-100 |

| SAB-C165-LF3V            | 20 MHz                   | 3.0 to 3.6 V      | TQFP-100 |

<sup>1)</sup> This Data Sheet is valid for devices starting with and including design step HA.

For simplicity all versions are referred to by the term C165 throughout this document.

#### **Ordering Information**

The ordering code for Infineon microcontrollers provides an exact reference to the required product. This ordering code identifies:

- the derivative itself, i.e. its function set, the temperature range, and the supply voltage

- the package and the type of delivery.

For the available ordering codes for the C165 please refer to the "**Product Catalog Microcontrollers**", which summarizes all available microcontroller variants.

Note: The ordering codes for Mask-ROM versions are defined for each product after verification of the respective ROM code.

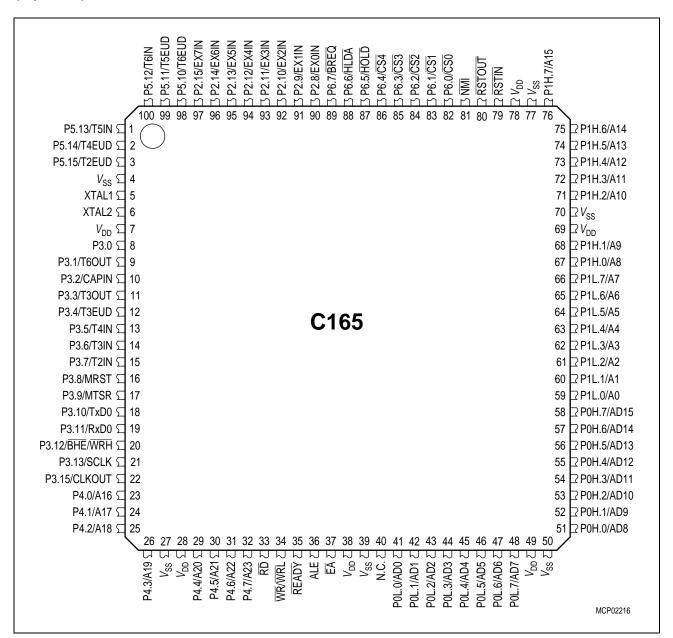

## Pin Configuration TQFP Package

(top view)

Figure 2

Table 2 Pin Definitions and Functions (cont'd)

| Symbol     | Pin Nr<br>TQFP | Pin Nr<br>MQFP | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                   |

|------------|----------------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P4         |                |                | Ю              | Port 4 is an 8-bit bidirectional I/O port. It is bit-wise programmable for input or output via direction bits. For a pin configured as input, the output driver is put into high-impedance state. Port 4 can be used to output the segment address lines:                                  |

| P4.0       | 23             | 25             | 0              | A16 Least Significant Segment Address Line                                                                                                                                                                                                                                                 |

| P4.1       | 24             | 26             | 0              | A17 Segment Address Line                                                                                                                                                                                                                                                                   |

| P4.2       | 25             | 27             | 0              | A18 Segment Address Line                                                                                                                                                                                                                                                                   |

| P4.3       | 26             | 28             | 0              | A19 Segment Address Line                                                                                                                                                                                                                                                                   |

| P4.4       | 29             | 31             | 0              | A20 Segment Address Line                                                                                                                                                                                                                                                                   |

| P4.5       | 30             | 32             | 0              | A21 Segment Address Line                                                                                                                                                                                                                                                                   |

| P4.6       | 31             | 33             | 0              | A22 Segment Address Line                                                                                                                                                                                                                                                                   |

| P4.7       | 32             | 34             | 0              | A23 Most Significant Segment Address Line                                                                                                                                                                                                                                                  |

| RD         | 33             | 35             | 0              | External Memory Read Strobe. RD is activated for every external instruction or data read access.                                                                                                                                                                                           |

| WR/<br>WRL | 34             | 36             | 0              | External Memory Write Strobe. In WR-mode this pin is activated for every external data write access. In WRL-mode this pin is activated for low byte data write accesses on a 16-bit bus, and for every data write access on an 8-bit bus. See WRCFG in register SYSCON for mode selection. |

| READY      | 35             | 37             | I              | Ready Input. When the Ready function is enabled, a high level at this pin during an external memory access will force the insertion of memory cycle waitstates until the pin returns to a low level. An internal pullup device holds this pin high when nothing is driving it.             |

| ALE        | 36             | 38             | 0              | Address Latch Enable Output. Can be used for latching the address into external memory or an address latch in the multiplexed bus modes.                                                                                                                                                   |

| ĒĀ         | 37             | 39             | I              | External Access Enable pin. A low level at this pin during and after Reset forces the C165 to begin instruction execution out of external memory. A high level forces execution out of the internal program memory.  "ROMless" versions must have this pin tied to '0'.                    |

Table 2 Pin Definitions and Functions (cont'd)

| Symbol                      | Pin Nr<br>TQFP | Pin Nr<br>MQFP           | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                               |  |  |  |  |  |

|-----------------------------|----------------|--------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NC                          | 40             | 42                       | _              | This pin is not conne<br>No connection to the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                               |  |  |  |  |  |

| PORTO<br>POL.0-7            | 41-48          | 43-50                    | Ю              | ports P0L and P0H.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PORT0 consists of the two 8-bit bidirectional I/O ports P0L and P0H. It is bit-wise programmable for input or output via direction bits. For a pin configured |  |  |  |  |  |

| P0H.0-7                     | 51-58          | 53-60                    |                | input or output via direction bits. For a pin configured as input, the output driver is put into high-impedance state. In case of an external bus configuration, PORT0 serves as the address (A) and address/data (AD) bus in multiplexed bus modes and as the data (D) bus in demultiplexed bus modes.  Demultiplexed bus modes:  Data Path Width: 8-bit 16-bit POL.0 - POL.7: DO - D7 POH.0 - POH.7: I/O D8 - D15  Multiplexed bus modes:  Data Path Width: 8-bit 16-bit POL.0 - POL.7: AD0 - AD7 AD0 - AD7 POH.0 - POH.7: AB0 - AD7 AD0 - AD7 |                                                                                                                                                               |  |  |  |  |  |

| PORT1<br>P1L.0-7<br>P1H.0-7 |                | 61-68<br>69-70,<br>73-78 | Ю              | PORT1 consists of the two 8-bit bidirectional I/O ports P1L and P1H. It is bit-wise programmable for input or output via direction bits. For a pin configured as input, the output driver is put into high-impedance state. PORT1 is used as the 16-bit address bus (A) in demultiplexed bus modes and also after switching                                                                                                                                                                                                                      |                                                                                                                                                               |  |  |  |  |  |

|                             |                |                          |                | from a demultiplexed mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                               |  |  |  |  |  |

Table 2 Pin Definitions and Functions (cont'd)

| Symbol     | Pin Nr<br>TQFP | Pin Nr<br>MQFP | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|----------------|----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSTIN      | 79             | 81             | I/O            | Reset Input with Schmitt-Trigger characteristics. A low level at this pin while the oscillator is running resets the C165. An internal pullup resistor permits power-on reset using only a capacitor connected to $V_{\rm SS}$ . A spike filter suppresses input pulses < 10 ns. Input pulses >100 ns safely pass the filter. The minimum duration for a safe recognition should be 100 ns + 2 CPU clock cycles. In bidirectional reset mode (enabled by setting bit BDRSTEN in register SYSCON) the RSTIN line is internally pulled low for the duration of the internal reset sequence upon any reset (HW, SW, WDT). See note below this table. |

|            |                |                |                | Note: To let the reset configuration of PORT0 settle a reset duration of ca. 1 ms is recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RST<br>OUT | 80             | 82             | 0              | Internal Reset Indication Output. This pin is set to a low level when the part is executing either a hardware-, a software- or a watchdog timer reset.  RSTOUT remains low until the EINIT (end of initialization) instruction is executed.                                                                                                                                                                                                                                                                                                                                                                                                       |

| NMI        | 81             | 83             | I              | Non-Maskable Interrupt Input. A high to low transition at this pin causes the CPU to vector to the NMI trap routine. When the PWRDN (power down) instruction is executed, the NMI pin must be low in order to force the C165 to go into power down mode. If NMI is high, when PWRDN is executed, the part will continue to run in normal mode. If not used, pin NMI should be pulled high externally.                                                                                                                                                                                                                                             |

The CPU has a register context consisting of up to 16 wordwide GPRs at its disposal. These 16 GPRs are physically allocated within the on-chip RAM area. A Context Pointer (CP) register determines the base address of the active register bank to be accessed by the CPU at any time. The number of register banks is only restricted by the available internal RAM space. For easy parameter passing, a register bank may overlap others.

A system stack of up to 1024 words is provided as a storage for temporary data. The system stack is allocated in the on-chip RAM area, and it is accessed by the CPU via the stack pointer (SP) register. Two separate SFRs, STKOV and STKUN, are implicitly compared against the stack pointer value upon each stack access for the detection of a stack overflow or underflow.

The high performance offered by the hardware implementation of the CPU can efficiently be utilized by a programmer via the highly efficient C165 instruction set which includes the following instruction classes:

- Arithmetic Instructions

- Logical Instructions

- Boolean Bit Manipulation Instructions

- Compare and Loop Control Instructions

- Shift and Rotate Instructions

- Prioritize Instruction

- Data Movement Instructions

- System Stack Instructions

- Jump and Call Instructions

- Return Instructions

- System Control Instructions

- Miscellaneous Instructions

The basic instruction length is either 2 or 4 bytes. Possible operand types are bits, bytes and words. A variety of direct, indirect or immediate addressing modes are provided to specify the required operands.

## **Interrupt System**

With an interrupt response time within a range from just 5 to 12 CPU clocks (in case of internal program execution), the C165 is capable of reacting very fast to the occurrence of non-deterministic events.

The architecture of the C165 supports several mechanisms for fast and flexible response to service requests that can be generated from various sources internal or external to the microcontroller. Any of these interrupt requests can be programmed to being serviced by the Interrupt Controller or by the Peripheral Event Controller (PEC).

In contrast to a standard interrupt service where the current program execution is suspended and a branch to the interrupt vector table is performed, just one cycle is 'stolen' from the current CPU activity to perform a PEC service. A PEC service implies a single byte or word data transfer between any two memory locations with an additional increment of either the PEC source or the destination pointer. An individual PEC transfer counter is implicity decremented for each PEC service except when performing in the continuous transfer mode. When this counter reaches zero, a standard interrupt is performed to the corresponding source related vector location. PEC services are very well suited, for example, for supporting the transmission or reception of blocks of data. The C165 has 8 PEC channels each of which offers such fast interrupt-driven data transfer capabilities.

A separate control register which contains an interrupt request flag, an interrupt enable flag and an interrupt priority bitfield exists for each of the possible interrupt sources. Via its related register, each source can be programmed to one of sixteen interrupt priority levels. Once having been accepted by the CPU, an interrupt service can only be interrupted by a higher prioritized service request. For the standard interrupt processing, each of the possible interrupt sources has a dedicated vector location.

Fast external interrupt inputs are provided to service external interrupts with high precision requirements. These fast interrupt inputs feature programmable edge detection (rising edge, falling edge or both edges).

Software interrupts are supported by means of the 'TRAP' instruction in combination with an individual trap (interrupt) number.

**Table 3** shows all of the possible C165 interrupt sources and the corresponding hardware-related interrupt flags, vectors, vector locations and trap (interrupt) numbers.

Note: Interrupt nodes which are not used by associated peripherals, may be used to generate software controlled interrupt requests by setting the respective interrupt request bit (xIR).

The C165 also provides an excellent mechanism to identify and to process exceptions or error conditions that arise during run-time, so-called 'Hardware Traps'. Hardware traps cause immediate non-maskable system reaction which is similar to a standard interrupt service (branching to a dedicated vector table location). The occurence of a hardware trap is additionally signified by an individual bit in the trap flag register (TFR). Except when another higher prioritized trap service is in progress, a hardware trap will interrupt any actual program execution. In turn, hardware trap services can normally not be interrupted by standard or PEC interrupts.

**Table 4** shows all of the possible exceptions or error conditions that can arise during runtime:

Table 4 Hardware Trap Summary

| Exception Condition                                                                    | Trap<br>Flag          | Trap<br>Vector                | Vector<br>Location                                                                        | Trap<br>Number                                        | Trap<br>Priority           |

|----------------------------------------------------------------------------------------|-----------------------|-------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------|

| Reset Functions:  - Hardware Reset  - Software Reset  - W-dog Timer Overflow           | _                     | RESET<br>RESET<br>RESET       | 00'0000 <sub>H</sub>                                                                      | 00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub> |                            |

| Class A Hardware Traps:  - Non-Maskable Interrupt  - Stack Overflow  - Stack Underflow | NMI<br>STKOF<br>STKUF | NMITRAP<br>STOTRAP<br>STUTRAP | 00'0008 <sub>H</sub><br>00'0010 <sub>H</sub><br>00'0018 <sub>H</sub>                      | 02 <sub>H</sub><br>04 <sub>H</sub><br>06 <sub>H</sub> | <br>  <br>  <br>           |

| Class B Hardware Traps:  - Undefined Opcode  - Protected Instruction Fault             | UNDOPC<br>PRTFLT      | BTRAP<br>BTRAP                | 00'0028 <sub>H</sub><br>00'0028 <sub>H</sub>                                              | 0A <sub>H</sub><br>0A <sub>H</sub>                    | <br>                       |

| <ul> <li>Illegal Word Operand<br/>Access</li> </ul>                                    | ILLOPA                | BTRAP                         | 00'0028 <sub>H</sub>                                                                      | 0A <sub>H</sub>                                       | I                          |

| <ul> <li>Illegal Instruction</li> <li>Access</li> </ul>                                | ILLINA                | BTRAP                         | 00'0028 <sub>H</sub>                                                                      | 0A <sub>H</sub>                                       | I                          |

| <ul><li>Illegal External Bus<br/>Access</li></ul>                                      | ILLBUS                | BTRAP                         | 00'0028 <sub>H</sub>                                                                      | 0A <sub>H</sub>                                       | 1                          |

| Reserved                                                                               | _                     | _                             | [2C <sub>H</sub> –<br>3C <sub>H</sub> ]                                                   | [0B <sub>H</sub> –<br>0F <sub>H</sub> ]               | _                          |

| Software Traps  – TRAP Instruction                                                     | _                     | _                             | Any<br>[00'0000 <sub>H</sub> -<br>00'01FC <sub>H</sub> ]<br>in steps<br>of 4 <sub>H</sub> | Any<br>[00 <sub>H</sub> –<br>7F <sub>H</sub> ]        | Current<br>CPU<br>Priority |

# **Instruction Set Summary**

Table 5 lists the instructions of the C165 in a condensed way.

The various addressing modes that can be used with a specific instruction, the operation of the instructions, parameters for conditional execution of instructions, and the opcodes for each instruction can be found in the "C166 Family Instruction Set Manual".

This document also provides a detailed description of each instruction.

Table 5 Instruction Set Summary

| Mnemonic           | Description                                                                                       | Bytes |

|--------------------|---------------------------------------------------------------------------------------------------|-------|

| ADD(B)             | Add word (byte) operands                                                                          | 2/4   |

| ADDC(B)            | Add word (byte) operands with Carry                                                               | 2/4   |

| SUB(B)             | Subtract word (byte) operands                                                                     | 2/4   |

| SUBC(B)            | Subtract word (byte) operands with Carry                                                          | 2/4   |

| MUL(U)             | (Un)Signed multiply direct GPR by direct GPR (16-16-bit)                                          | 2     |

| DIV(U)             | (Un)Signed divide register MDL by direct GPR (16-/16-bit)                                         | 2     |

| DIVL(U)            | (Un)Signed long divide reg. MD by direct GPR (32-/16-bit)                                         | 2     |

| CPL(B)             | Complement direct word (byte) GPR                                                                 | 2     |

| NEG(B)             | Negate direct word (byte) GPR                                                                     | 2     |

| AND(B)             | Bitwise AND, (word/byte operands)                                                                 | 2/4   |

| OR(B)              | Bitwise OR, (word/byte operands)                                                                  | 2/4   |

| XOR(B)             | Bitwise XOR, (word/byte operands)                                                                 | 2/4   |

| BCLR               | Clear direct bit                                                                                  | 2     |

| BSET               | Set direct bit                                                                                    | 2     |

| BMOV(N)            | Move (negated) direct bit to direct bit                                                           | 4     |

| BAND, BOR,<br>BXOR | AND/OR/XOR direct bit with direct bit                                                             | 4     |

| BCMP               | Compare direct bit to direct bit                                                                  | 4     |

| BFLDH/L            | Bitwise modify masked high/low byte of bit-addressable direct word memory with immediate data     | 4     |

| CMP(B)             | Compare word (byte) operands                                                                      | 2/4   |

| CMPD1/2            | Compare word data to GPR and decrement GPR by 1/2                                                 | 2/4   |

| CMPI1/2            | Compare word data to GPR and increment GPR by 1/2                                                 | 2/4   |

| PRIOR              | Determine number of shift cycles to normalize direct word GPR and store result in direct word GPR | 2     |

| SHL / SHR          | Shift left/right direct word GPR                                                                  | 2     |

| ROL / ROR          | Rotate left/right direct word GPR                                                                 | 2     |

| ASHR               | Arithmetic (sign bit) shift right direct word GPR                                                 | 2     |

## **Special Function Registers Overview**

The following table lists all SFRs which are implemented in the C165 in alphabetical order.

**Bit-addressable** SFRs are marked with the letter "**b**" in column "Name". SFRs within the **Extended SFR-Space** (ESFRs) are marked with the letter "**E**" in column "Physical Address". Registers within on-chip X-peripherals are marked with the letter "**X**" in column "Physical Address".

An SFR can be specified via its individual mnemonic name. Depending on the selected addressing mode, an SFR can be accessed via its physical address (using the Data Page Pointers), or via its short 8-bit address (without using the Data Page Pointers).

Table 6 C165 Registers, Ordered by Name

| Name     |   | Physical Address           | 8-Bit<br>Addr.  | Description                         | Reset<br>Value    |

|----------|---|----------------------------|-----------------|-------------------------------------|-------------------|

| ADDRSEL1 |   | FE18 <sub>H</sub>          | 0C <sub>H</sub> | Address Select Register 1           | 0000 <sub>H</sub> |

| ADDRSEL2 | 2 | FE1A <sub>H</sub>          | 0D <sub>H</sub> | Address Select Register 2           | 0000 <sub>H</sub> |

| ADDRSEL3 | 3 | FE1C <sub>H</sub>          | 0E <sub>H</sub> | Address Select Register 3           | 0000 <sub>H</sub> |

| ADDRSEL4 | ļ | FE1E <sub>H</sub>          | 0F <sub>H</sub> | Address Select Register 4           | 0000 <sub>H</sub> |

| BUSCON0  | b | FF0C <sub>H</sub>          | 86 <sub>H</sub> | Bus Configuration Register 0        | 0XX0 <sub>H</sub> |

| BUSCON1  | b | FF14 <sub>H</sub>          | 8A <sub>H</sub> | Bus Configuration Register 1        | 0000 <sub>H</sub> |

| BUSCON2  | b | FF16 <sub>H</sub>          | 8B <sub>H</sub> | Bus Configuration Register 2        | 0000 <sub>H</sub> |

| BUSCON3  | b | FF18 <sub>H</sub>          | 8C <sub>H</sub> | Bus Configuration Register 3        | 0000 <sub>H</sub> |

| BUSCON4  | b | FF1A <sub>H</sub>          | 8D <sub>H</sub> | Bus Configuration Register 4        | 0000 <sub>H</sub> |

| CAPREL   |   | FE4A <sub>H</sub>          | 25 <sub>H</sub> | GPT2 Capture/Reload Register        | 0000 <sub>H</sub> |

| CC10IC   | b | FF8C <sub>H</sub>          | C6 <sub>H</sub> | EX2IN Interrupt Control Register    | 0000 <sub>H</sub> |

| CC11IC   | b | FF8E <sub>H</sub>          | C7 <sub>H</sub> | EX3IN Interrupt Control Register    | 0000 <sub>H</sub> |

| CC12IC   | b | FF90 <sub>H</sub>          | C8 <sub>H</sub> | EX4IN Interrupt Control Register    | 0000 <sub>H</sub> |

| CC13IC   | b | FF92 <sub>H</sub>          | C9 <sub>H</sub> | EX5IN Interrupt Control Register    | 0000 <sub>H</sub> |

| CC14IC   | b | FF94 <sub>H</sub>          | CA <sub>H</sub> | EX6IN Interrupt Control Register    | 0000 <sub>H</sub> |

| CC15IC   | b | FF96 <sub>H</sub>          | CB <sub>H</sub> | EX7IN Interrupt Control Register    | 0000 <sub>H</sub> |

| CC29IC   | b | F184 <sub>H</sub> <b>E</b> | C2 <sub>H</sub> | Software Interrupt Control Register | 0000 <sub>H</sub> |

| CC30IC   | b | F18C <sub>H</sub> E        | C6 <sub>H</sub> | Software Interrupt Control Register | 0000 <sub>H</sub> |

| CC31IC   | b | F194 <sub>H</sub> <b>E</b> | CA <sub>H</sub> | Software Interrupt Control Register | 0000 <sub>H</sub> |

| CC8IC    | b | FF88 <sub>H</sub>          | C4 <sub>H</sub> | EX0IN Interrupt Control Register    | 0000 <sub>H</sub> |

| CC9IC    | b | FF8A <sub>H</sub>          | C5 <sub>H</sub> | EX1IN Interrupt Control Register    | 0000 <sub>H</sub> |

Table 6 C165 Registers, Ordered by Name (cont'd)

| Name   |   | Physical Address           | 8-Bit<br>Addr.  | Description                                                    | Reset<br>Value    |

|--------|---|----------------------------|-----------------|----------------------------------------------------------------|-------------------|

| P1H    | b | FF06 <sub>H</sub>          | 83 <sub>H</sub> | Port 1 High Reg. (Upper half of PORT1)                         | 00 <sub>H</sub>   |

| P1L    | b | FF04 <sub>H</sub>          | 82 <sub>H</sub> | Port 1 Low Reg.(Lower half of PORT1)                           | 00 <sub>H</sub>   |

| P2     | b | FFC0 <sub>H</sub>          | E0 <sub>H</sub> | Port 2 Register                                                | 0000 <sub>H</sub> |

| P3     | b | FFC4 <sub>H</sub>          | E2 <sub>H</sub> | Port 3 Register                                                | 0000 <sub>H</sub> |

| P4     | b | FFC8 <sub>H</sub>          | E4 <sub>H</sub> | Port 4 Register (8 bits)                                       | 00 <sub>H</sub>   |

| P5     | b | FFA2 <sub>H</sub>          | D1 <sub>H</sub> | Port 5 Register (read only)                                    | XXXX <sub>H</sub> |

| P6     | b | FFCC <sub>H</sub>          | E6 <sub>H</sub> | Port 6 Register (8 bits)                                       | 00 <sub>H</sub>   |

| PECC0  |   | FEC0 <sub>H</sub>          | 60 <sub>H</sub> | PEC Channel 0 Control Register                                 | 0000 <sub>H</sub> |

| PECC1  |   | FEC2 <sub>H</sub>          | 61 <sub>H</sub> | PEC Channel 1 Control Register                                 | 0000 <sub>H</sub> |

| PECC2  |   | FEC4 <sub>H</sub>          | 62 <sub>H</sub> | PEC Channel 2 Control Register                                 | 0000 <sub>H</sub> |

| PECC3  |   | FEC6 <sub>H</sub>          | 63 <sub>H</sub> | PEC Channel 3 Control Register                                 | 0000 <sub>H</sub> |

| PECC4  |   | FEC8 <sub>H</sub>          | 64 <sub>H</sub> | PEC Channel 4 Control Register                                 | 0000 <sub>H</sub> |

| PECC5  |   | FECA <sub>H</sub>          | 65 <sub>H</sub> | PEC Channel 5 Control Register                                 | 0000 <sub>H</sub> |

| PECC6  |   | FECC <sub>H</sub>          | 66 <sub>H</sub> | PEC Channel 6 Control Register                                 | 0000 <sub>H</sub> |

| PECC7  |   | FECE <sub>H</sub>          | 67 <sub>H</sub> | PEC Channel 7 Control Register                                 | 0000 <sub>H</sub> |

| PSW    | b | FF10 <sub>H</sub>          | 88 <sub>H</sub> | CPU Program Status Word                                        | 0000 <sub>H</sub> |

| RP0H   | b | F108 <sub>H</sub> <b>E</b> | 84 <sub>H</sub> | System Startup Config. Reg. (Rd. only)                         | XX <sub>H</sub>   |

| S0BG   |   | FEB4 <sub>H</sub>          | 5A <sub>H</sub> | Serial Channel 0 Baud Rate Generator<br>Reload Register        | 0000 <sub>H</sub> |

| S0CON  | b | FFB0 <sub>H</sub>          | D8 <sub>H</sub> | Serial Channel 0 Control Register                              | 0000 <sub>H</sub> |

| S0EIC  | b | FF70 <sub>H</sub>          | B8 <sub>H</sub> | Serial Channel 0 Error Interrupt Ctrl. Reg                     | 0000 <sub>H</sub> |

| S0RBUF |   | FEB2 <sub>H</sub>          | 59 <sub>H</sub> | Serial Channel 0 Receive Buffer Reg. (read only)               | XX <sub>H</sub>   |

| SORIC  | b | FF6E <sub>H</sub>          | B7 <sub>H</sub> | Serial Channel 0 Receive Interrupt<br>Control Register         | 0000 <sub>H</sub> |

| S0TBIC | b | F19C <sub>H</sub> <b>E</b> | CE <sub>H</sub> | Serial Channel 0 Transmit Buffer<br>Interrupt Control Register | 0000 <sub>H</sub> |

| S0TBUF |   | FEB0 <sub>H</sub>          | 58 <sub>H</sub> | Serial Channel 0 Transmit Buffer<br>Register (write only)      | 00 <sub>H</sub>   |

| S0TIC  | b | FF6C <sub>H</sub>          | B6 <sub>H</sub> | Serial Channel 0 Transmit Interrupt<br>Control Register        | 0000 <sub>H</sub> |

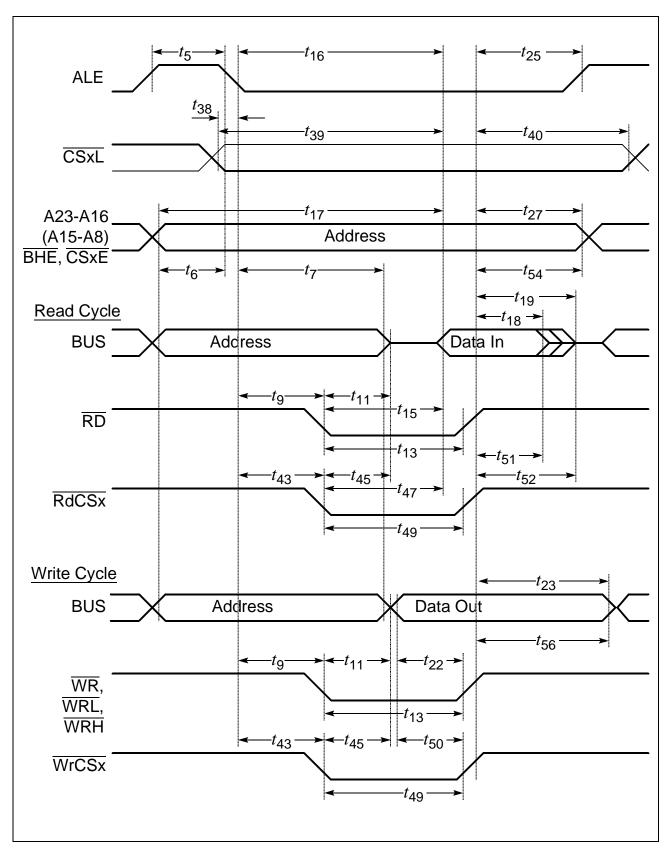

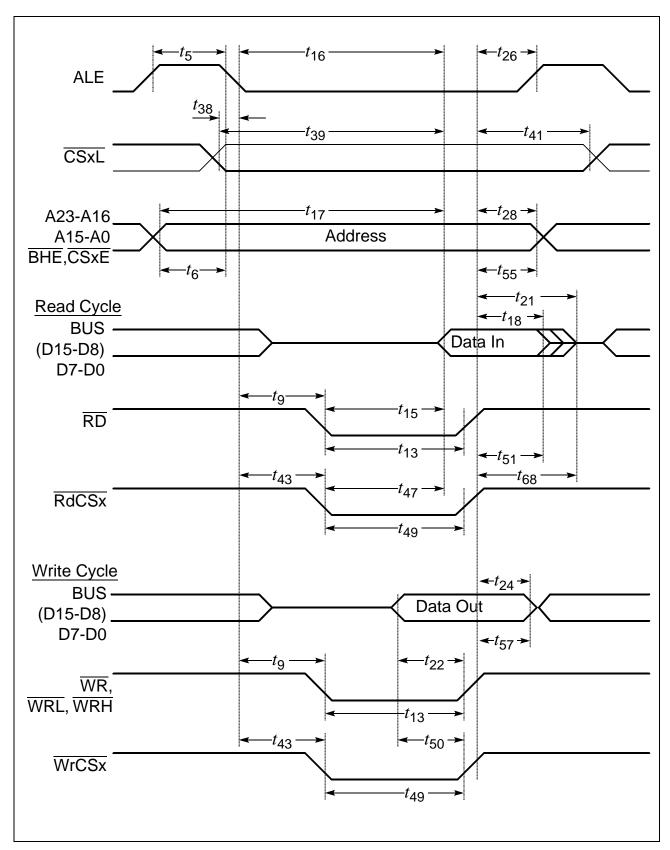

Figure 16 External Memory Cycle:

Multiplexed Bus, No Read/Write Delay, Extended ALE

### **AC Characteristics**

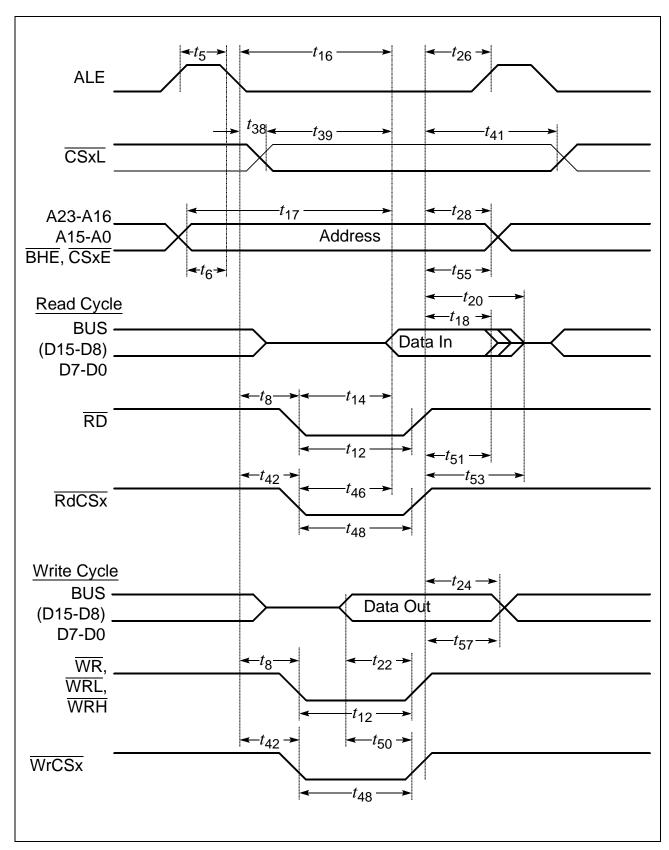

# **Demultiplexed Bus (Standard Supply Voltage Range)**

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (80 ns at 25 MHz CPU clock without waitstates)

| Parameter                                                      |                        | nbol | Max. CPU Clock<br>= 25 MHz |                                       | Variable (<br>1 / 2TCL =      | Unit                                                              |    |

|----------------------------------------------------------------|------------------------|------|----------------------------|---------------------------------------|-------------------------------|-------------------------------------------------------------------|----|

|                                                                |                        |      | min.                       | max.                                  | min.                          | max.                                                              |    |

| ALE high time                                                  | <i>t</i> <sub>5</sub>  | CC   | 10 + t <sub>A</sub>        | _                                     | TCL - 10<br>+ t <sub>A</sub>  | _                                                                 | ns |

| Address setup to ALE                                           | <i>t</i> <sub>6</sub>  | CC   | $4 + t_A$                  | _                                     | TCL - 16<br>+ t <sub>A</sub>  | _                                                                 | ns |

| ALE falling edge to RD, WR (with RW-delay)                     | <i>t</i> <sub>8</sub>  | CC   | 10 + t <sub>A</sub>        | _                                     | TCL - 10<br>+ t <sub>A</sub>  | _                                                                 | ns |

| ALE falling edge to RD, WR (no RW-delay)                       | <i>t</i> <sub>9</sub>  | CC   | - 10 + t <sub>A</sub>      | _                                     | - 10<br>+ t <sub>A</sub>      | _                                                                 | ns |

| RD, WR low time (with RW-delay)                                | <i>t</i> <sub>12</sub> | CC   | 30 + t <sub>C</sub>        | _                                     | 2TCL - 10<br>+ t <sub>C</sub> | _                                                                 | ns |

| RD, WR low time (no RW-delay)                                  | <i>t</i> <sub>13</sub> | CC   | 50 + t <sub>C</sub>        | _                                     | 3TCL - 10<br>+ t <sub>C</sub> | _                                                                 | ns |

| RD to valid data in (with RW-delay)                            | t <sub>14</sub>        | SR   | _                          | 20 + t <sub>C</sub>                   | _                             | 2TCL - 20<br>+ t <sub>C</sub>                                     | ns |

| RD to valid data in (no RW-delay)                              | <i>t</i> <sub>15</sub> | SR   | _                          | 40 + t <sub>C</sub>                   | _                             | 3TCL - 20<br>+ t <sub>C</sub>                                     | ns |

| ALE low to valid data in                                       | <i>t</i> <sub>16</sub> | SR   | _                          | 40 + t <sub>A</sub> + t <sub>C</sub>  | _                             | 3TCL - 20<br>+ t <sub>A</sub> + t <sub>C</sub>                    | ns |

| Address to valid data in                                       | <i>t</i> <sub>17</sub> | SR   | _                          | 50 + 2t <sub>A</sub> + t <sub>C</sub> | _                             | 4TCL - 30<br>+ 2t <sub>A</sub> + t <sub>C</sub>                   | ns |

| Data hold after RD rising edge                                 | <i>t</i> <sub>18</sub> | SR   | 0                          | _                                     | 0                             | _                                                                 | ns |

| Data float after RD rising edge (with RW-delay <sup>1)</sup> ) | t <sub>20</sub>        | SR   | _                          | $26 + 2t_A + t_F^{1)}$                | -                             | 2TCL - 14<br>+ 22t <sub>A</sub><br>+ t <sub>F</sub> <sup>1)</sup> | ns |

| Data float after RD rising edge (no RW-delay <sup>1)</sup> )   | t <sub>21</sub>        | SR   | _                          | $10 + 2t_A + t_F^{1)}$                | _                             | TCL - 10<br>+ 22t <sub>A</sub><br>+ t <sub>F</sub> <sup>1)</sup>  | ns |

Figure 17 External Memory Cycle:

Demultiplexed Bus, With Read/Write Delay, Normal ALE

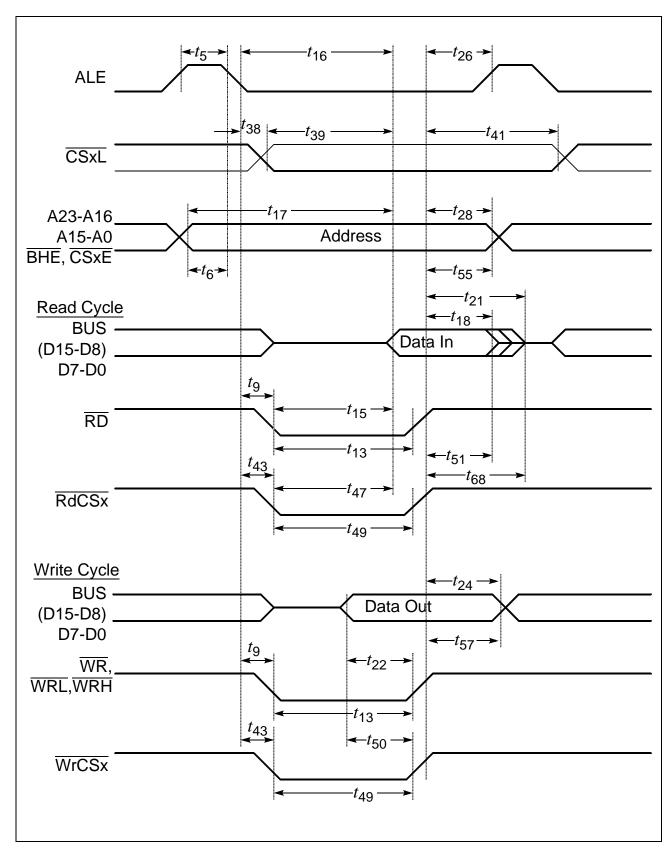

Figure 19 External Memory Cycle:

Demultiplexed Bus, No Read/Write Delay, Normal ALE

Figure 20 External Memory Cycle:

Demultiplexed Bus, No Read/Write Delay, Extended ALE

#### **AC Characteristics**

# **CLKOUT and READY (Standard Supply Voltage)**

(Operating Conditions apply)

| Parameter                                                                  |                        | nbol | Max. CPU Clock<br>= 25 MHz |                                          | Variable CPU Clock<br>1 / 2TCL = 1 to 25 MHz |                                                                                  | Unit |

|----------------------------------------------------------------------------|------------------------|------|----------------------------|------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------|------|

|                                                                            |                        |      | min.                       | max.                                     | min.                                         | max.                                                                             |      |

| CLKOUT cycle time                                                          | t <sub>29</sub>        | CC   | 40                         | 40                                       | 2TCL                                         | 2TCL                                                                             | ns   |

| CLKOUT high time                                                           | t <sub>30</sub>        | CC   | 14                         | _                                        | TCL - 6                                      | _                                                                                | ns   |

| CLKOUT low time                                                            | t <sub>31</sub>        | CC   | 10                         | _                                        | TCL - 10                                     | _                                                                                | ns   |

| CLKOUT rise time                                                           | t <sub>32</sub>        | CC   | _                          | 4                                        | _                                            | 4                                                                                | ns   |

| CLKOUT fall time                                                           | t <sub>33</sub>        | CC   | _                          | 4                                        | _                                            | 4                                                                                | ns   |

| CLKOUT rising edge to ALE falling edge                                     | t <sub>34</sub>        | CC   | $0 + t_{A}$                | 10 + t <sub>A</sub>                      | 0 + t <sub>A</sub>                           | 10 + t <sub>A</sub>                                                              | ns   |

| Synchronous READY setup time to CLKOUT                                     | t <sub>35</sub>        | SR   | 14                         | _                                        | 14                                           | _                                                                                | ns   |

| Synchronous READY hold time after CLKOUT                                   | t <sub>36</sub>        | SR   | 4                          | _                                        | 4                                            | _                                                                                | ns   |

| Asynchronous READY low time                                                | t <sub>37</sub>        | SR   | 54                         | _                                        | 2TCL + t <sub>58</sub>                       | _                                                                                | ns   |

| Asynchronous READY setup time <sup>1)</sup>                                | t <sub>58</sub>        | SR   | 14                         | _                                        | 14                                           | _                                                                                | ns   |

| Asynchronous READY hold time <sup>1)</sup>                                 | t <sub>59</sub>        | SR   | 4                          | _                                        | 4                                            | _                                                                                | ns   |

| Async. READY hold time after RD, WR high (Demultiplexed Bus) <sup>2)</sup> | <i>t</i> <sub>60</sub> | SR   | 0                          | 0<br>+ $2t_A$ +<br>$t_C$<br>+ $t_F^{2)}$ | 0                                            | TCL - 20<br>+ 2t <sub>A</sub> + t <sub>C</sub><br>+ t <sub>F</sub> <sup>2)</sup> | ns   |

<sup>1)</sup> These timings are given for test purposes only, in order to assure recognition at a specific clock edge.

<sup>&</sup>lt;sup>2)</sup> Demultiplexed bus is the worst case. For multiplexed bus 2TCL are to be added to the maximum values. This adds even more time for deactivating READY.

The  $2t_A$  and  $t_C$  refer to the next following bus cycle,  $t_F$  refers to the current bus cycle.

The maximum limit for  $t_{60}$  must be fulfilled if the next following bus cycle is  $\overline{\text{READY}}$  controlled.

# Infineon goes for Business Excellence

"Business excellence means intelligent approaches and clearly defined processes, which are both constantly under review and ultimately lead to good operating results.

Better operating results and business excellence mean less idleness and wastefulness for all of us, more professional success, more accurate information, a better overview and, thereby, less frustration and more satisfaction."

Dr. Ulrich Schumacher

http://www.infineon.com