# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | C166                                                                      |

| Core Size                  | 16-Bit                                                                    |

| Speed                      | 20MHz                                                                     |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                  |

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 77                                                                        |

| Program Memory Size        | -                                                                         |

| Program Memory Type        | ROMIess                                                                   |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                               |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 100-LQFP                                                                  |

| Supplier Device Package    | PG-TQFP-100                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/c165lfhabxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### C165

| <b>Revision History:</b>                                                 |                                                                                                                                                                                      | 2000-12                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                           |  |  |  |  |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Previous Version:                                                        |                                                                                                                                                                                      | Update 0.5µ technology<br>3 Volt Addendum<br>25 MHz Addendum<br>Data Sheet                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                           |  |  |  |  |

| Subjects (r                                                              | major change                                                                                                                                                                         | es since last revision)                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                           |  |  |  |  |

| Converted                                                                | to Infineon lay                                                                                                                                                                      | vout                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                           |  |  |  |  |

| ROM derivatives removed, 25-MHz derivatives and 3 V derivatives included |                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                           |  |  |  |  |

| Pin numbers for TQFP added                                               |                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                           |  |  |  |  |

| Address wi                                                               | ndow arbitrati                                                                                                                                                                       | on and master/slave mode introduced                                                                                                                                                                                                                                                                                                                                                     | ł                                                                                                                                                                                                                                                         |  |  |  |  |

| New standa                                                               | ard layout for                                                                                                                                                                       | section "Absolute Maximum Ratings"                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                           |  |  |  |  |

| Section "Op                                                              | perating Cond                                                                                                                                                                        | litions" added                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                           |  |  |  |  |

| Parameter                                                                | "RSTIN pullup                                                                                                                                                                        | o" replaced by "RSTIN current"                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                           |  |  |  |  |

| DC Charac                                                                | teristics for re                                                                                                                                                                     | duced supply voltage added                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                           |  |  |  |  |

| Separate sp                                                              | pecification fo                                                                                                                                                                      | r power consumption with greatly impr                                                                                                                                                                                                                                                                                                                                                   | oved values                                                                                                                                                                                                                                               |  |  |  |  |

| Description                                                              | of clock gene                                                                                                                                                                        | eration improved                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                           |  |  |  |  |

| Timing ada                                                               | pted to 25 MF                                                                                                                                                                        | łz                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                           |  |  |  |  |

| Timing for r                                                             | educed suppl                                                                                                                                                                         | ly voltage added                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                           |  |  |  |  |

|                                                                          | Subjects (r<br>Converted t<br>ROM deriva<br>included<br>Pin number<br>Address wir<br>New standa<br>Section "Op<br>Parameter<br>DC Charac<br>Separate sp<br>Description<br>Timing ada | ersion: 1998-12<br>01.96<br>07.95<br>09.94   Subjects (major change<br>Converted to Infineon lay<br>ROM derivatives remove<br>included   Pin numbers for TQFP a   Address window arbitrati   New standard layout for   Section "Operating Cond<br>Parameter "RSTIN pullup   DC Characteristics for re   Separate specification fo   Description of clock gene   Timing adapted to 25 MH | ersion: 1998-12 Update 0.5μ technology   01.96 3 Volt Addendum   07.95 25 MHz Addendum   09.94 Data Sheet   Subjects (major changes since last revision)   Converted to Infineon layout   ROM derivatives removed, 25-MHz derivatives and 3 V derivatives |  |  |  |  |

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

#### mcdocu.comments@infineon.com

### 16-Bit Single-Chip Microcontroller C166 Family

#### C165

•

- High Performance 16-bit CPU with 4-Stage Pipeline

- 80 ns Instruction Cycle Time at 25 MHz CPU Clock

- 400 ns Multiplication (16  $\times$  16 bit), 800 ns Division (32 / 16 bit)

- Enhanced Boolean Bit Manipulation Facilities

- Additional Instructions to Support HLL and Operating Systems

- Register-Based Design with Multiple Variable Register Banks

- Single-Cycle Context Switching Support

- 16 MBytes Total Linear Address Space for Code and Data

- 1024 Bytes On-Chip Special Function Register Area

- 16-Priority-Level Interrupt System with 28 Sources, Sample-Rate down to 40 ns

- 8-Channel Interrupt-Driven Single-Cycle Data Transfer Facilities via Peripheral Event Controller (PEC)

- Clock Generation via prescaler or via direct clock input

- On-Chip Memory Modules

- 2 KBytes On-Chip Internal RAM (IRAM)

- On-Chip Peripheral Modules

- Two Multi-Functional General Purpose Timer Units with 5 Timers

- Two Serial Channels (Synchronous/Asynchronous and High-Speed-Synchronous)

- Up to 16 MBytes External Address Space for Code and Data

- Programmable External Bus Characteristics for Different Address Ranges

- Multiplexed or Demultiplexed External Address/Data Buses with 8-Bit or 16-Bit Data Bus Width

- Five Programmable Chip-Select Signals

- Hold- and Hold-Acknowledge Bus Arbitration Support

- Idle and Power Down Modes

- Programmable Watchdog Timer

- Up to 77 General Purpose I/O Lines, partly with Selectable Input Thresholds and Hysteresis

- Power Supply: the C165 can operate from a 5 V or a 3 V power supply

- Supported by a Large Range of Development Tools like C-Compilers, Macro-Assembler Packages, Emulators, Evaluation Boards, HLL-Debuggers, Simulators, Logic Analyzer Disassemblers, Programming Boards

- On-Chip Bootstrap Loader

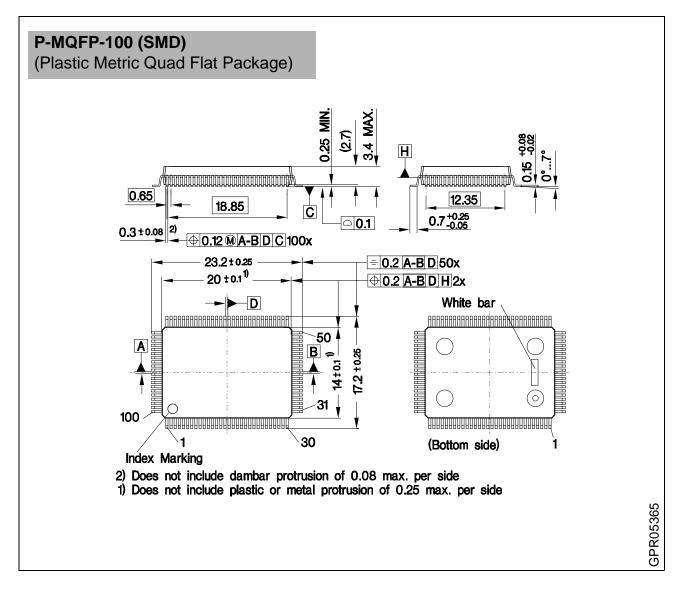

- 100-Pin MQFP Package (0.65 mm pitch)

- 100-Pin TQFP Package (0.5 mm pitch)

C165

| Symbol                                                       | Pin Nr<br>TQFP                               | Pin Nr<br>MQFP                               | Input<br>Outp.                             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------|----------------------------------------------|----------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P4.0<br>P4.1<br>P4.2<br>P4.3<br>P4.4<br>P4.5<br>P4.6<br>P4.7 | 23<br>24<br>25<br>26<br>29<br>30<br>31<br>32 | 25<br>26<br>27<br>28<br>31<br>32<br>33<br>34 | IO<br>O<br>O<br>O<br>O<br>O<br>O<br>O<br>O | Port 4 is an 8-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits.<br>For a pin configured as input, the output driver is put<br>into high-impedance state. Port 4 can be used to<br>output the segment address lines:<br>A16 Least Significant Segment Address Line<br>A17 Segment Address Line<br>A18 Segment Address Line<br>A19 Segment Address Line<br>A20 Segment Address Line<br>A21 Segment Address Line<br>A22 Segment Address Line<br>A23 Most Significant Segment Address Line |

| RD                                                           | 33                                           | 35                                           | 0                                          | External Memory Read Strobe. $\overline{RD}$ is activated for every external instruction or data read access.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| WR/<br>WRL                                                   | 34                                           | 36                                           | 0                                          | External Memory Write Strobe. In $\overline{\text{WR}}$ -mode this pin<br>is activated for every external data write access. In<br>WRL-mode this pin is activated for low byte data<br>write accesses on a 16-bit bus, and for every data<br>write access on an 8-bit bus. See WRCFG in register<br>SYSCON for mode selection.                                                                                                                                                                                                           |

| READY                                                        | 35                                           | 37                                           | 1                                          | Ready Input. When the Ready function is enabled, a<br>high level at this pin during an external memory<br>access will force the insertion of memory cycle<br>waitstates until the pin returns to a low level.<br>An internal pullup device holds this pin high when<br>nothing is driving it.                                                                                                                                                                                                                                            |

| ALE                                                          | 36                                           | 38                                           | 0                                          | Address Latch Enable Output. Can be used for latching the address into external memory or an address latch in the multiplexed bus modes.                                                                                                                                                                                                                                                                                                                                                                                                 |

| ĒĀ                                                           | 37                                           | 39                                           | 1                                          | External Access Enable pin. A low level at this pin<br>during and after Reset forces the C165 to begin<br>instruction execution out of external memory. A high<br>level forces execution out of the internal program<br>memory.                                                                                                                                                                                                                                                                                                          |

# Table 2Pin Definitions and Functions (cont'd)

| Table 2 | Pin Definitions and Functions (cont'd) |

|---------|----------------------------------------|

|---------|----------------------------------------|

| Symbol          | Pin Nr<br>TQFP                 | Pin Nr<br>MQFP              | Input<br>Outp. | Function                                                                                                               |

|-----------------|--------------------------------|-----------------------------|----------------|------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> | 7, 28,<br>38,<br>49,<br>69, 78 | 9, 30,<br>40, 51,<br>71, 80 | _              | Digital Supply Voltage:<br>+ 5 V or + 3 V during normal operation and idle<br>mode.<br>≥ 2.5 V during power down mode. |

| V <sub>SS</sub> | 4, 27,<br>39,<br>50,<br>70, 77 | 6, 29,<br>41, 52,<br>72, 79 | _              | Digital Ground.                                                                                                        |

Note: The following behavioural differences must be observed when the bidirectional reset is active:

- Bit BDRSTEN in register SYSCON cannot be changed after EINIT and is cleared automatically after a reset.

- The reset indication flags always indicate a long hardware reset.

- The PORT0 configuration is treated like on a hardware reset. Especially the bootstrap loader may be activated when P0L.4 is low.

- Pin RSTIN may only be connected to external reset devices with an open drain output driver.

- A short hardware reset is extended to the duration of the internal reset sequence.

#### External Bus Controller

All of the external memory accesses are performed by a particular on-chip External Bus Controller (EBC). It can be programmed either to Single Chip Mode when no external memory is required, or to one of four different external memory access modes, which are as follows:

- 16-/18-/20-/24-bit Addresses, 16-bit Data, Demultiplexed

- 16-/18-/20-/24-bit Addresses, 16-bit Data, Multiplexed

- 16-/18-/20-/24-bit Addresses, 8-bit Data, Multiplexed

- 16-/18-/20-/24-bit Addresses, 8-bit Data, Demultiplexed

In the demultiplexed bus modes, addresses are output on PORT1 and data is input/ output on PORT0 or P0L, respectively. In the multiplexed bus modes both addresses and data use PORT0 for input/output.

Important timing characteristics of the external bus interface (Memory Cycle Time, Memory Tri-State Time, Length of ALE and Read Write Delay) have been made programmable to allow the user the adaption of a wide range of different types of memories and external peripherals.

In addition, up to 4 independent address windows may be defined (via register pairs ADDRSELx / BUSCONx) which control the access to different resources with different bus characteristics. These address windows are arranged hierarchically where BUSCON4 overrides BUSCON3 and BUSCON2 overrides BUSCON1. All accesses to locations not covered by these 4 address windows are controlled by BUSCON0.

Up to 5 external  $\overline{CS}$  signals (4 windows plus default) can be generated in order to save external glue logic. The C165 offers the possibility to switch the  $\overline{CS}$  outputs to an unlatched mode. In this mode the internal filter logic is switched off and the  $\overline{CS}$  signals are directly generated from the address. The unlatched  $\overline{CS}$  mode is enabled by setting CSCFG (SYSCON.6).

Access to very slow memories or memories with varying access times is supported via a particular 'Ready' function.

A HOLD/HLDA protocol is available for bus arbitration and allows to share external resources with other bus masters. The bus arbitration is enabled by setting bit HLDEN in register PSW. After setting HLDEN once, pins P6.7 ... P6.5 (BREQ, HLDA, HOLD) are automatically controlled by the EBC. In Master Mode (default after reset) the HLDA pin is an output. By setting bit DP6.7 to '1' the Slave Mode is selected where pin HLDA is switched to input. This allows to directly connect the slave controller to another master controller without glue logic.

For applications which require less than 16 MBytes of external memory space, this address space can be restricted to 1 MByte, 256 KByte, or to 64 KByte. In this case Port 4 outputs four, two, or no address lines at all. It outputs all 8 address lines, if an address space of 16 MBytes is used.

The CPU has a register context consisting of up to 16 wordwide GPRs at its disposal. These 16 GPRs are physically allocated within the on-chip RAM area. A Context Pointer (CP) register determines the base address of the active register bank to be accessed by the CPU at any time. The number of register banks is only restricted by the available internal RAM space. For easy parameter passing, a register bank may overlap others.

A system stack of up to 1024 words is provided as a storage for temporary data. The system stack is allocated in the on-chip RAM area, and it is accessed by the CPU via the stack pointer (SP) register. Two separate SFRs, STKOV and STKUN, are implicitly compared against the stack pointer value upon each stack access for the detection of a stack overflow or underflow.

The high performance offered by the hardware implementation of the CPU can efficiently be utilized by a programmer via the highly efficient C165 instruction set which includes the following instruction classes:

- Arithmetic Instructions

- Logical Instructions

- Boolean Bit Manipulation Instructions

- Compare and Loop Control Instructions

- Shift and Rotate Instructions

- Prioritize Instruction

- Data Movement Instructions

- System Stack Instructions

- Jump and Call Instructions

- Return Instructions

- System Control Instructions

- Miscellaneous Instructions

The basic instruction length is either 2 or 4 bytes. Possible operand types are bits, bytes and words. A variety of direct, indirect or immediate addressing modes are provided to specify the required operands.

#### Interrupt System

With an interrupt response time within a range from just 5 to 12 CPU clocks (in case of internal program execution), the C165 is capable of reacting very fast to the occurrence of non-deterministic events.

The architecture of the C165 supports several mechanisms for fast and flexible response to service requests that can be generated from various sources internal or external to the microcontroller. Any of these interrupt requests can be programmed to being serviced by the Interrupt Controller or by the Peripheral Event Controller (PEC).

In contrast to a standard interrupt service where the current program execution is suspended and a branch to the interrupt vector table is performed, just one cycle is 'stolen' from the current CPU activity to perform a PEC service. A PEC service implies a single byte or word data transfer between any two memory locations with an additional increment of either the PEC source or the destination pointer. An individual PEC transfer counter is implicity decremented for each PEC service except when performing in the continuous transfer mode. When this counter reaches zero, a standard interrupt is performed to the corresponding source related vector location. PEC services are very well suited, for example, for supporting the transmission or reception of blocks of data. The C165 has 8 PEC channels each of which offers such fast interrupt-driven data transfer capabilities.

A separate control register which contains an interrupt request flag, an interrupt enable flag and an interrupt priority bitfield exists for each of the possible interrupt sources. Via its related register, each source can be programmed to one of sixteen interrupt priority levels. Once having been accepted by the CPU, an interrupt service can only be interrupted by a higher prioritized service request. For the standard interrupt processing, each of the possible interrupt sources has a dedicated vector location.

Fast external interrupt inputs are provided to service external interrupts with high precision requirements. These fast interrupt inputs feature programmable edge detection (rising edge, falling edge or both edges).

Software interrupts are supported by means of the 'TRAP' instruction in combination with an individual trap (interrupt) number.

**Table 3** shows all of the possible C165 interrupt sources and the corresponding hardware-related interrupt flags, vectors, vector locations and trap (interrupt) numbers.

Note: Interrupt nodes which are not used by associated peripherals, may be used to generate software controlled interrupt requests by setting the respective interrupt request bit (xIR).

# DC Characteristics (Standard Supply Voltage Range) (cont'd)

(Operating Conditions apply)<sup>1)</sup>

| Parameter                                                 | Symbol                          | Symbol Limit Values |      | Unit | <b>Test Condition</b>               |

|-----------------------------------------------------------|---------------------------------|---------------------|------|------|-------------------------------------|

|                                                           |                                 | min.                | max. | 1    |                                     |

| RSTIN active current <sup>4)</sup>                        | I <sub>RSTL</sub> <sup>6)</sup> | - 100               | -    | μA   | $V_{\rm IN} = V_{\rm IL}$           |

| READY/RD/WR inact. current <sup>7)</sup>                  | $I_{\text{RWH}}^{5)}$           | -                   | - 40 | μA   | $V_{OUT}$ = 2.4 V                   |

| READY/RD/WR active current <sup>7)</sup>                  | $I_{\rm RWL}^{6)}$              | - 500               | _    | μA   | $V_{OUT} = V_{OLmax}$               |

| ALE inactive current <sup>7)</sup>                        | I <sub>ALEL</sub> <sup>5)</sup> | _                   | 40   | μA   | $V_{\text{OUT}} = V_{\text{OLmax}}$ |

| ALE active current <sup>7)</sup>                          | I <sub>ALEH</sub> <sup>6)</sup> | 500                 | _    | μA   | $V_{\rm OUT}$ = 2.4 V               |

| Port 6 inactive current <sup>7)</sup>                     | I <sub>P6H</sub> <sup>5)</sup>  | -                   | - 40 | μA   | $V_{OUT}$ = 2.4 V                   |

| Port 6 active current <sup>7)</sup>                       | I <sub>P6L</sub> <sup>6)</sup>  | - 500               | _    | μA   | $V_{OUT} = V_{OL1max}$              |

| PORT0 configuration current <sup>8)</sup>                 | I <sub>P0H</sub> <sup>5)</sup>  | _                   | - 10 | μA   | $V_{\rm IN} = V_{\rm IHmin}$        |

|                                                           | $I_{P0L}^{6)}$                  | - 100               | _    | μA   | $V_{\rm IN} = V_{\rm ILmax}$        |

| XTAL1 input current                                       | I <sub>IL</sub> CC              | -                   | ± 20 | μA   | $0 V < V_{IN} < V_{DD}$             |

| Pin capacitance <sup>9)</sup><br>(digital inputs/outputs) | C <sub>IO</sub> CC              | _                   | 10   | pF   | f = 1  MHz<br>$T_A = 25 \text{ °C}$ |

<sup>1)</sup> Keeping signal levels within the levels specified in this table, ensures operation without overload conditions. For signal levels outside these specifications also refer to the specification of the overload current  $I_{OV}$ .

<sup>2)</sup> Valid in bidirectional reset mode only.

- <sup>3)</sup> This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage results from the external circuitry.

- <sup>4)</sup> These parameters describe the  $\overline{\text{RSTIN}}$  pullup, which equals a resistance of ca. 50 to 250 k $\Omega$ .

- <sup>5)</sup> The maximum current may be drawn while the respective signal line remains inactive.

- <sup>6)</sup> The minimum current must be drawn in order to drive the respective signal line active.

- <sup>7)</sup> This specification is valid during Reset and during Hold-mode or Adapt-mode. During Hold-mode Port 6 pins are only affected, if they are used (configured) for CS output and the open drain function is not enabled. The READY-pullup is always active, except for Powerdown mode.

- <sup>8)</sup> This specification is valid during Reset and during Adapt-mode.

- <sup>9)</sup> Not 100% tested, guaranteed by design and characterization.

#### Power Consumption C165 (Standard Supply Voltage Range)

(Operating Conditions apply)

| Parameter                                                 | Symbol            | Lim  | it Values                      | Unit | <b>Test Condition</b>                                                             |

|-----------------------------------------------------------|-------------------|------|--------------------------------|------|-----------------------------------------------------------------------------------|

|                                                           |                   | min. | max.                           |      |                                                                                   |

| Power supply current (active) with all peripherals active | I <sub>DD5</sub>  | -    | 15 +<br>1.8 × f <sub>CPU</sub> | mA   | $\overline{\text{RSTIN}} = V_{\text{IL}}$ $f_{\text{CPU}} \text{ in [MHz]}^{1)}$  |

| Idle mode supply current with all peripherals active      | I <sub>IDX5</sub> | -    | 2 +<br>0.4 × f <sub>CPU</sub>  | mA   | $\overline{\text{RSTIN}} = V_{\text{IH1}}$ $f_{\text{CPU}} \text{ in [MHz]}^{1)}$ |

| Power-down mode supply current                            | I <sub>PDO5</sub> | -    | 50                             | μA   | $V_{\rm DD} = V_{\rm DDmax}^{2)}$                                                 |

<sup>1)</sup> The supply current is a function of the operating frequency. This dependency is illustrated in Figure 8. These parameters are tested at V<sub>DDmax</sub> and maximum CPU clock with all outputs disconnected and all inputs at V<sub>IL</sub> or V<sub>IH</sub>.

<sup>2)</sup> This parameter is tested including leakage currents. All inputs (including pins configured as inputs) at 0 V to 0.1 V or at  $V_{DD}$  – 0.1 V to  $V_{DD}$ , all outputs (including pins configured as outputs) disconnected.

#### Power Consumption C165 (Reduced Supply Voltage Range)

(Operating Conditions apply)

| Parameter                                                 | Symbol            | Lim  | it Values                     | Unit | <b>Test Condition</b>                                                                |

|-----------------------------------------------------------|-------------------|------|-------------------------------|------|--------------------------------------------------------------------------------------|

|                                                           |                   | min. | max.                          |      |                                                                                      |

| Power supply current (active) with all peripherals active | I <sub>DD3</sub>  | -    | 3 +<br>1.3 × f <sub>CPU</sub> | mA   | $\overline{\text{RSTIN}} = V_{\text{IL}}$ $f_{\text{CPU}} \text{ in [MHz]}^{1)}$     |

| Idle mode supply current<br>with all peripherals active   | I <sub>IDX3</sub> | -    | 1 +<br>0.4 × f <sub>CPU</sub> | mA   | $\frac{\text{RSTIN} = V_{\text{IH1}}}{f_{\text{CPU}} \text{ in } [\text{MHz}]^{1)}}$ |

| Power-down mode supply current                            | I <sub>PDO3</sub> | -    | 30                            | μA   | $V_{\rm DD} = V_{\rm DDmax}^{2)}$                                                    |

<sup>1)</sup> The supply current is a function of the operating frequency. This dependency is illustrated in Figure 8. These parameters are tested at V<sub>DDmax</sub> and maximum CPU clock with all outputs disconnected and all inputs at V<sub>IL</sub> or V<sub>IH</sub>.

<sup>2)</sup> This parameter is tested including leakage currents. All inputs (including pins configured as inputs) at 0 V to 0.1 V or at  $V_{DD}$  – 0.1 V to  $V_{DD}$ , all outputs (including pins configured as outputs) disconnected.

#### **AC Characteristics**

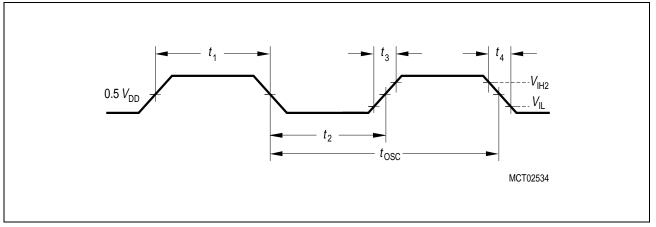

# Table 10External Clock Drive XTAL1 (Standard Supply Voltage Range)<br/>(Operating Conditions apply)

| Parameter               | Symbol                |    | Direct Drive<br>1:1 |      | P    | Prescaler<br>2:1 |    |  |

|-------------------------|-----------------------|----|---------------------|------|------|------------------|----|--|

|                         |                       |    | min.                | max. | min. | max.             |    |  |

| Oscillator period       | t <sub>OSC</sub>      | SR | 40                  | -    | 20   | _                | ns |  |

| High time <sup>1)</sup> |                       |    | 20 <sup>2)</sup>    | -    | 6    | _                | ns |  |

| Low time <sup>1)</sup>  | <i>t</i> <sub>2</sub> | SR | 20 <sup>2)</sup>    | _    | 6    | _                | ns |  |

| Rise time <sup>1)</sup> | t <sub>3</sub>        | SR | _                   | 10   | _    | 6                | ns |  |

| Fall time <sup>1)</sup> | <i>t</i> <sub>4</sub> | SR | -                   | 10   | -    | 6                | ns |  |

<sup>1)</sup> The clock input signal must reach the defined levels  $V_{\text{IL2}}$  and  $V_{\text{IH2}}$ .

<sup>2)</sup> The minimum high and low time refers to a duty cycle of 50%. The maximum operating frequency ( $f_{CPU}$ ) in direct drive mode depends on the duty cycle of the clock input signal.

# Table 11External Clock Drive XTAL1 (Reduced Supply Voltage Range)<br/>(Operating Conditions apply)

| Parameter               | Symbol                |    | ool Direct Drive<br>1:1 |      | Р    | Prescaler<br>2:1 |    |  |

|-------------------------|-----------------------|----|-------------------------|------|------|------------------|----|--|

|                         |                       |    | min.                    | max. | min. | max.             |    |  |

| Oscillator period       | t <sub>OSC</sub>      | SR | 50                      | _    | 25   | -                | ns |  |

| High time <sup>1)</sup> | t <sub>1</sub>        | SR | 25 <sup>2)</sup>        | _    | 8    | -                | ns |  |

| Low time <sup>1)</sup>  | <i>t</i> <sub>2</sub> | SR | 25 <sup>2)</sup>        | _    | 8    | _                | ns |  |

| Rise time <sup>1)</sup> | t <sub>3</sub>        | SR | -                       | 10   | -    | 6                | ns |  |

| Fall time <sup>1)</sup> | <i>t</i> <sub>4</sub> | SR | _                       | 10   | -    | 6                | ns |  |

<sup>1)</sup> The clock input signal must reach the defined levels  $V_{\text{IL2}}$  and  $V_{\text{IH2}}$ .

<sup>2)</sup> The minimum high and low time refers to a duty cycle of 50%. The maximum operating frequency ( $f_{CPU}$ ) in direct drive mode depends on the duty cycle of the clock input signal.

Figure 10 External Clock Drive XTAL1

Note: If the on-chip oscillator is used together with a crystal, the oscillator frequency is limited to a range of 4 MHz to 40 MHz.

It is strongly recommended to measure the oscillation allowance (or margin) in the final target system (layout) to determine the optimum parameters for the oscillator operation. Please refer to the limits specified by the crystal supplier.

When driven by an external clock signal it will accept the specified frequency range. Operation at lower input frequencies is possible but is guaranteed by design only (not 100% tested).

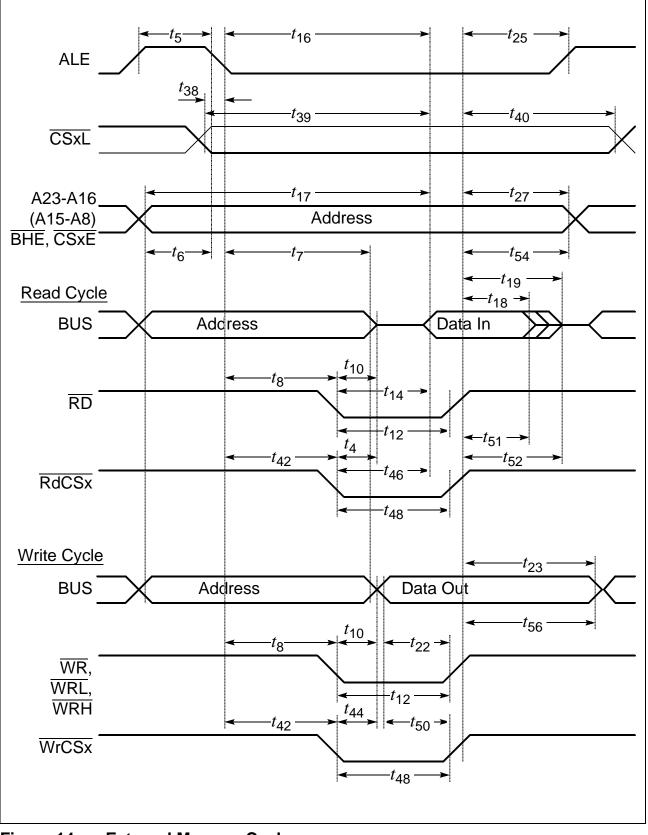

Figure 14 External Memory Cycle: Multiplexed Bus, With Read/Write Delay, Extended ALE

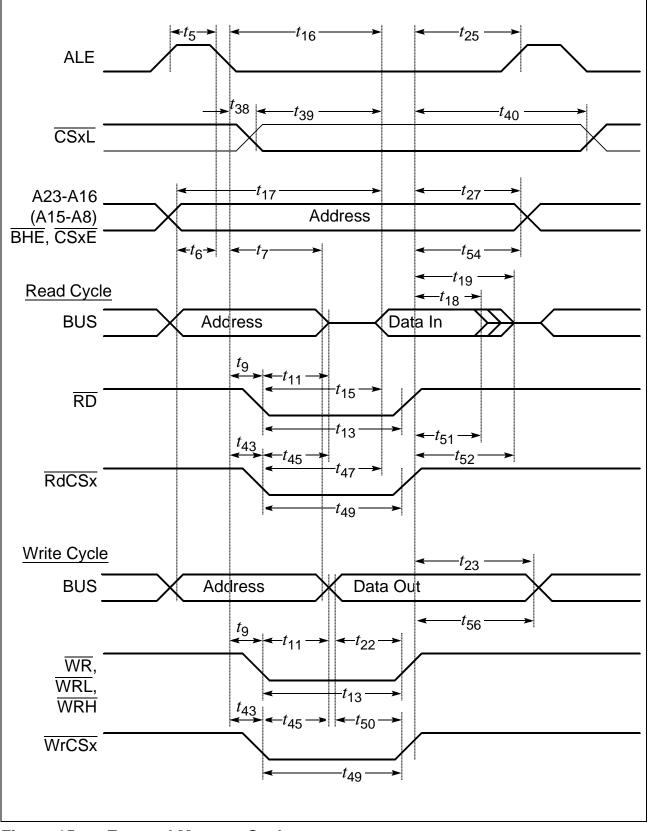

Figure 15 External Memory Cycle: Multiplexed Bus, No Read/Write Delay, Normal ALE

#### **AC Characteristics**

## Demultiplexed Bus (Standard Supply Voltage Range)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (80 ns at 25 MHz CPU clock without waitstates)

| Parameter                                                                   | Symbol                 |    |                  | PU Clock<br>5 MHz       | Variable (<br>1 / 2TCL =             | Unit                                                         |    |

|-----------------------------------------------------------------------------|------------------------|----|------------------|-------------------------|--------------------------------------|--------------------------------------------------------------|----|

|                                                                             |                        |    | min.             | max.                    | min.                                 | max.                                                         |    |

| ALE high time                                                               | <i>t</i> 5             | CC | $10 + t_{A}$     | -                       | TCL - 10<br>+ <i>t</i> <sub>A</sub>  | _                                                            | ns |

| Address setup to ALE                                                        | <i>t</i> <sub>6</sub>  | CC | $4 + t_A$        | _                       | TCL - 16<br>+ <i>t</i> <sub>A</sub>  | -                                                            | ns |

| ALE falling edge to $\overline{RD}$ ,<br>WR (with RW-delay)                 | <i>t</i> 8             | CC | $10 + t_{A}$     | _                       | TCL - 10<br>+ <i>t</i> <sub>A</sub>  | -                                                            | ns |

| ALE falling edge to $\overline{RD}$ ,<br>WR (no RW-delay)                   | t <sub>9</sub>         | CC | $-10 + t_A$      | _                       | - 10<br>+ <i>t</i> <sub>A</sub>      | -                                                            | ns |

| RD, WR low time<br>(with RW-delay)                                          | t <sub>12</sub>        | CC | $30 + t_{\rm C}$ | _                       | 2TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                                            | ns |

| RD, WR low time<br>(no RW-delay)                                            | t <sub>13</sub>        | CC | $50 + t_{\rm C}$ | _                       | 3TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                                            | ns |

| RD to valid data in (with RW-delay)                                         | <i>t</i> <sub>14</sub> | SR | _                | $20 + t_{\rm C}$        | -                                    | 2TCL - 20<br>+ <i>t</i> <sub>C</sub>                         | ns |

| RD to valid data in (no RW-delay)                                           | t <sub>15</sub>        | SR | _                | $40 + t_{\rm C}$        | _                                    | 3TCL - 20<br>+ <i>t</i> <sub>C</sub>                         | ns |

| ALE low to valid data in                                                    | t <sub>16</sub>        | SR | _                | $40 + t_{A} + t_{C}$    | _                                    | 3TCL - 20<br>+ <i>t</i> <sub>A</sub> + <i>t</i> <sub>C</sub> | ns |

| Address to valid data in                                                    | t <sub>17</sub>        | SR | _                | $50 + 2t_A + t_C$       | _                                    | $4TCL - 30 + 2t_A + t_C$                                     | ns |

| Data hold after RD rising edge                                              | t <sub>18</sub>        | SR | 0                | _                       | 0                                    | -                                                            | ns |

| Data float after $\overline{RD}$ rising edge (with RW-delay <sup>1)</sup> ) | <i>t</i> <sub>20</sub> | SR | -                | $26 + 2t_A + t_F^{(1)}$ | -                                    | 2TCL - 14<br>+ $22t_A$<br>+ $t_F^{(1)}$                      | ns |

| Data float after RD rising edge (no RW-delay <sup>1)</sup> )                | t <sub>21</sub>        | SR | -                | $10 + 2t_A + t_F^{(1)}$ | -                                    | TCL - 10<br>+ $22t_A$<br>+ $t_F^{(1)}$                       | ns |

### Demultiplexed Bus (Standard Supply Voltage Range) (cont'd)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (80 ns at 25 MHz CPU clock without waitstates)

| Parameter                                                                              | Symbol                    |                              | Max. CPU Clock<br>= 25 MHz    |                                      | Variable CPU Clock<br>1 / 2TCL = 1 to 25 MHz |    |  |

|----------------------------------------------------------------------------------------|---------------------------|------------------------------|-------------------------------|--------------------------------------|----------------------------------------------|----|--|

|                                                                                        |                           | min.                         | max.                          | min.                                 | max.                                         |    |  |

| Data valid to $\overline{WR}$                                                          | t <sub>22</sub> CC        | $20 + t_{\rm C}$             | _                             | 2TCL - 20<br>+ <i>t</i> <sub>C</sub> | -                                            | ns |  |

| Data hold after $\overline{WR}$                                                        | <i>t</i> <sub>24</sub> CC | 10 + <i>t</i> <sub>F</sub>   | _                             | TCL - 10<br>+ <i>t</i> <sub>F</sub>  | -                                            | ns |  |

| ALE rising edge after<br>RD, WR                                                        | <i>t</i> <sub>26</sub> CC | - 10 + <i>t</i> <sub>F</sub> | _                             | - 10 + <i>t</i> <sub>F</sub>         | -                                            | ns |  |

| Address hold after $\overline{WR}^{2)}$                                                | t <sub>28</sub> CC        | $0 + t_{F}$                  | -                             | $0 + t_{F}$                          | -                                            | ns |  |

| ALE falling edge to $\overline{\text{CS}}^{3)}$                                        | t <sub>38</sub> CC        | - 4 - t <sub>A</sub>         | 10 - <i>t</i> <sub>A</sub>    | - 4 - t <sub>A</sub>                 | 10 - <i>t</i> <sub>A</sub>                   | ns |  |

| $\overline{\text{CS}}$ low to Valid Data In <sup>3)</sup>                              | <i>t</i> <sub>39</sub> SR | -                            | $40 + t_{\rm C} + 2t_{\rm A}$ | -                                    | $3TCL - 20 + t_C + 2t_A$                     | ns |  |

| $\overline{\text{CS}}$ hold after $\overline{\text{RD}}$ , $\overline{\text{WR}}^{3)}$ | <i>t</i> <sub>41</sub> CC | $6 + t_{F}$                  | -                             | TCL - 14<br>+ <i>t</i> <sub>F</sub>  | -                                            | ns |  |

| ALE falling edge to<br>RdCS, WrCS (with RW-<br>delay)                                  | t <sub>42</sub> CC        | 16 + <i>t</i> <sub>A</sub>   | -                             | TCL - 4<br>+ <i>t</i> <sub>A</sub>   | -                                            | ns |  |

| ALE falling edge to<br>RdCS, WrCS (no RW-<br>delay)                                    | t <sub>43</sub> CC        | $-4 + t_{A}$                 | -                             | - 4<br>+ t <sub>A</sub>              | _                                            | ns |  |

| RdCS to Valid Data In (with RW-delay)                                                  | <i>t</i> <sub>46</sub> SR | -                            | 16 + <i>t</i> <sub>C</sub>    | -                                    | 2TCL - 24<br>+ <i>t</i> <sub>C</sub>         | ns |  |

| RdCS to Valid Data In (no RW-delay)                                                    | <i>t</i> <sub>47</sub> SR | -                            | $36 + t_{\rm C}$              | _                                    | 3TCL - 24<br>+ <i>t</i> <sub>C</sub>         | ns |  |

| RdCS, WrCS Low Time<br>(with RW-delay)                                                 | <i>t</i> <sub>48</sub> CC | $30 + t_{\rm C}$             | -                             | 2TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                            | ns |  |

| RdCS, WrCS Low Time<br>(no RW-delay)                                                   | <i>t</i> <sub>49</sub> CC | $50 + t_{\rm C}$             | -                             | 3TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                            | ns |  |

| Data valid to $\overline{WrCS}$                                                        | <i>t</i> <sub>50</sub> CC | $26 + t_{\rm C}$             | -                             | 2TCL - 14<br>+ <i>t</i> <sub>C</sub> | -                                            | ns |  |

| Data hold after RdCS                                                                   | <i>t</i> <sub>51</sub> SR | 0                            | _                             | 0                                    | -                                            | ns |  |

### Demultiplexed Bus (Reduced Supply Voltage Range) (cont'd)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (100 ns at 20 MHz CPU clock without waitstates)

| Parameter                                              | Syr             | nbol | Max. CPU Clock<br>= 20 MHz   |                           | Variable CPU Clock<br>1 / 2TCL = 1 to 20 MHz |                                   | Unit |

|--------------------------------------------------------|-----------------|------|------------------------------|---------------------------|----------------------------------------------|-----------------------------------|------|

|                                                        |                 |      | min.                         | max.                      | min.                                         | max.                              |      |

| Data float after RdCS<br>(with RW-delay) <sup>1)</sup> | t <sub>53</sub> | SR   | _                            | $30 + t_{\rm F}$          | _                                            | 2TCL - 20<br>+ $2t_A + t_F$<br>1) | ns   |

| Data float after RdCS<br>(no RW-delay) <sup>1)</sup>   | t <sub>68</sub> | SR   | -                            | 5 + <i>t</i> <sub>F</sub> | -                                            | TCL - 20<br>+ $2t_A + t_F$<br>1)  | ns   |

| Address hold after<br>RdCS, WrCS                       | t <sub>55</sub> | CC   | - 16 + <i>t</i> <sub>F</sub> | -                         | - 16 + <i>t</i> <sub>F</sub>                 | -                                 | ns   |

| Data hold after WrCS                                   | t <sub>57</sub> | CC   | 9 + <i>t</i> <sub>F</sub>    | _                         | TCL - 16<br>+ <i>t</i> <sub>F</sub>          | _                                 | ns   |

<sup>1)</sup> RW-delay and  $t_A$  refer to the next following bus cycle (including an access to an on-chip X-Peripheral).

<sup>2)</sup> Read data are latched with the same clock edge that triggers the address change and the rising RD edge. Therefore address changes before the end of RD have no impact on read cycles.

<sup>3)</sup> These parameters refer to the latched chip select signals (CSxL). The early chip select signals (CSxE) are specified together with the address and signal BHE (see figures below).

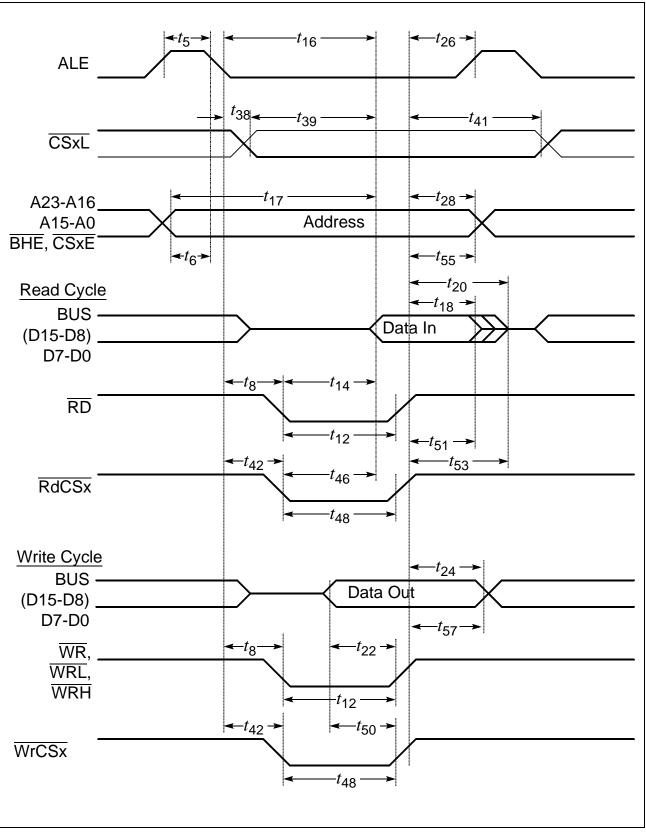

#### Figure 17 External Memory Cycle: Demultiplexed Bus, With Read/Write Delay, Normal ALE

#### AC Characteristics

#### External Bus Arbitration (Standard Supply Voltage)

(Operating Conditions apply)

| Parameter                                | Symbol                    | Max. CPU Clock<br>= 25 MHz |      | Variable CPU Clock<br>1 / 2TCL = 1 to 25 MHz |      | Unit |

|------------------------------------------|---------------------------|----------------------------|------|----------------------------------------------|------|------|

|                                          |                           | min.                       | max. | min.                                         | max. |      |

| HOLD input setup time to CLKOUT          | <i>t</i> <sub>61</sub> SR | 20                         | -    | 20                                           | -    | ns   |

| CLKOUT to HLDA high or BREQ low delay    | <i>t</i> <sub>62</sub> CC | -                          | 20   | -                                            | 20   | ns   |

| CLKOUT to HLDA low<br>or BREQ high delay | <i>t</i> <sub>63</sub> CC | -                          | 20   | -                                            | 20   | ns   |

| CSx release                              | <i>t</i> <sub>64</sub> CC | -                          | 20   | _                                            | 20   | ns   |

| CSx drive                                | t <sub>65</sub> CC        | - 4                        | 24   | - 4                                          | 24   | ns   |

| Other signals release                    | t <sub>66</sub> CC        | -                          | 20   | -                                            | 20   | ns   |

| Other signals drive                      | t <sub>67</sub> CC        | - 4                        | 24   | - 4                                          | 24   | ns   |

#### External Bus Arbitration (Reduced Supply Voltage)

(Operating Conditions apply)

| Parameter                                | Symbol                    | Max. CPU Clock<br>= 20 MHz |      | Variable CPU Clock<br>1 / 2TCL = 1 to 20 MHz |      | Unit |

|------------------------------------------|---------------------------|----------------------------|------|----------------------------------------------|------|------|

|                                          |                           | min.                       | max. | min.                                         | max. |      |

| HOLD input setup time to CLKOUT          | <i>t</i> <sub>61</sub> SR | 30                         | -    | 30                                           | -    | ns   |

| CLKOUT to HLDA high or BREQ low delay    | t <sub>62</sub> CC        | -                          | 20   | -                                            | 20   | ns   |

| CLKOUT to HLDA low<br>or BREQ high delay | t <sub>63</sub> CC        | -                          | 20   | -                                            | 20   | ns   |

| CSx release                              | t <sub>64</sub> CC        | -                          | 20   | -                                            | 20   | ns   |

| CSx drive                                | t <sub>65</sub> CC        | - 4                        | 30   | - 4                                          | 30   | ns   |

| Other signals release                    | t <sub>66</sub> CC        | -                          | 20   | -                                            | 20   | ns   |

| Other signals drive                      | t <sub>67</sub> CC        | - 4                        | 30   | - 4                                          | 30   | ns   |

#### **Package Outlines**

71

## Infineon goes for Business Excellence

"Business excellence means intelligent approaches and clearly defined processes, which are both constantly under review and ultimately lead to good operating results.

Better operating results and business excellence mean less idleness and wastefulness for all of us, more professional success, more accurate information, a better overview and, thereby, less frustration and more satisfaction."

Dr. Ulrich Schumacher

http://www.infineon.com