#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | C166                                                                        |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 20MHz                                                                       |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                    |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 77                                                                          |

| Program Memory Size        | -                                                                           |

| Program Memory Type        | ROMIess                                                                     |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-BQFP                                                                    |

| Supplier Device Package    | P-MQFP-100                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/c165Im3vhafxuma1 |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

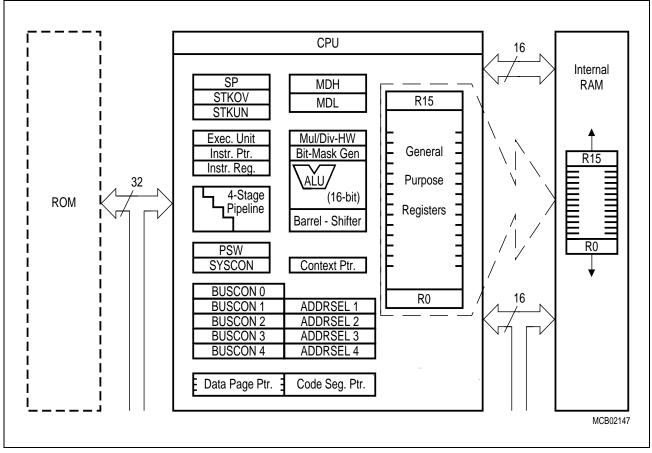

### **Central Processing Unit (CPU)**

The main core of the CPU consists of a 4-stage instruction pipeline, a 16-bit arithmetic and logic unit (ALU) and dedicated SFRs. Additional hardware has been spent for a separate multiply and divide unit, a bit-mask generator and a barrel shifter.

Based on these hardware provisions, most of the C165's instructions can be executed in just one machine cycle which requires 80 ns at 25 MHz CPU clock. For example, shift and rotate instructions are always processed during one machine cycle independent of the number of bits to be shifted. All multiple-cycle instructions have been optimized so that they can be executed very fast as well: branches in 2 cycles, a  $16 \times 16$  bit multiplication in 5 cycles and a 32-/16 bit division in 10 cycles. Another pipeline optimization, the so-called 'Jump Cache', allows reducing the execution time of repeatedly performed jumps in a loop from 2 cycles to 1 cycle.

Figure 5

**CPU Block Diagram**

The CPU has a register context consisting of up to 16 wordwide GPRs at its disposal. These 16 GPRs are physically allocated within the on-chip RAM area. A Context Pointer (CP) register determines the base address of the active register bank to be accessed by the CPU at any time. The number of register banks is only restricted by the available internal RAM space. For easy parameter passing, a register bank may overlap others.

A system stack of up to 1024 words is provided as a storage for temporary data. The system stack is allocated in the on-chip RAM area, and it is accessed by the CPU via the stack pointer (SP) register. Two separate SFRs, STKOV and STKUN, are implicitly compared against the stack pointer value upon each stack access for the detection of a stack overflow or underflow.

The high performance offered by the hardware implementation of the CPU can efficiently be utilized by a programmer via the highly efficient C165 instruction set which includes the following instruction classes:

- Arithmetic Instructions

- Logical Instructions

- Boolean Bit Manipulation Instructions

- Compare and Loop Control Instructions

- Shift and Rotate Instructions

- Prioritize Instruction

- Data Movement Instructions

- System Stack Instructions

- Jump and Call Instructions

- Return Instructions

- System Control Instructions

- Miscellaneous Instructions

The basic instruction length is either 2 or 4 bytes. Possible operand types are bits, bytes and words. A variety of direct, indirect or immediate addressing modes are provided to specify the required operands.

#### Interrupt System

With an interrupt response time within a range from just 5 to 12 CPU clocks (in case of internal program execution), the C165 is capable of reacting very fast to the occurrence of non-deterministic events.

The architecture of the C165 supports several mechanisms for fast and flexible response to service requests that can be generated from various sources internal or external to the microcontroller. Any of these interrupt requests can be programmed to being serviced by the Interrupt Controller or by the Peripheral Event Controller (PEC).

In contrast to a standard interrupt service where the current program execution is suspended and a branch to the interrupt vector table is performed, just one cycle is 'stolen' from the current CPU activity to perform a PEC service. A PEC service implies a single byte or word data transfer between any two memory locations with an additional increment of either the PEC source or the destination pointer. An individual PEC transfer counter is implicity decremented for each PEC service except when performing in the continuous transfer mode. When this counter reaches zero, a standard interrupt is performed to the corresponding source related vector location. PEC services are very well suited, for example, for supporting the transmission or reception of blocks of data. The C165 has 8 PEC channels each of which offers such fast interrupt-driven data transfer capabilities.

A separate control register which contains an interrupt request flag, an interrupt enable flag and an interrupt priority bitfield exists for each of the possible interrupt sources. Via its related register, each source can be programmed to one of sixteen interrupt priority levels. Once having been accepted by the CPU, an interrupt service can only be interrupted by a higher prioritized service request. For the standard interrupt processing, each of the possible interrupt sources has a dedicated vector location.

Fast external interrupt inputs are provided to service external interrupts with high precision requirements. These fast interrupt inputs feature programmable edge detection (rising edge, falling edge or both edges).

Software interrupts are supported by means of the 'TRAP' instruction in combination with an individual trap (interrupt) number.

**Table 3** shows all of the possible C165 interrupt sources and the corresponding hardware-related interrupt flags, vectors, vector locations and trap (interrupt) numbers.

Note: Interrupt nodes which are not used by associated peripherals, may be used to generate software controlled interrupt requests by setting the respective interrupt request bit (xIR).

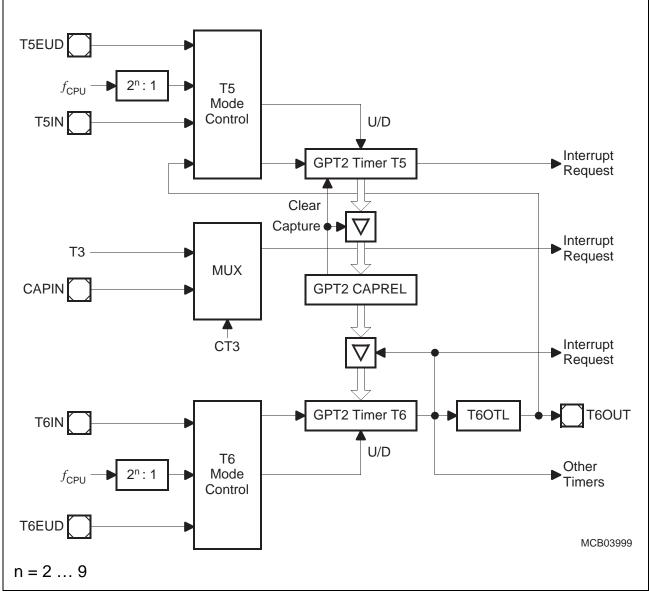

The capture trigger (timer T5 to CAPREL) may also be generated upon transitions of GPT1 timer T3's inputs T3IN and/or T3EUD. This is especially advantageous when T3 operates in Incremental Interface Mode.

### **Instruction Set Summary**

Table 5 lists the instructions of the C165 in a condensed way.

The various addressing modes that can be used with a specific instruction, the operation of the instructions, parameters for conditional execution of instructions, and the opcodes for each instruction can be found in the **"C166 Family Instruction Set Manual"**.

This document also provides a detailed description of each instruction.

| Mnemonic           | Description                                                                                          | Bytes |

|--------------------|------------------------------------------------------------------------------------------------------|-------|

| ADD(B)             | Add word (byte) operands                                                                             | 2/4   |

| ADDC(B)            | Add word (byte) operands with Carry                                                                  | 2/4   |

| SUB(B)             | Subtract word (byte) operands                                                                        | 2/4   |

| SUBC(B)            | Subtract word (byte) operands with Carry                                                             | 2/4   |

| MUL(U)             | (Un)Signed multiply direct GPR by direct GPR (16-16-bit)                                             | 2     |

| DIV(U)             | (Un)Signed divide register MDL by direct GPR (16-/16-bit)                                            | 2     |

| DIVL(U)            | (Un)Signed long divide reg. MD by direct GPR (32-/16-bit)                                            | 2     |

| CPL(B)             | Complement direct word (byte) GPR                                                                    | 2     |

| NEG(B)             | Negate direct word (byte) GPR                                                                        | 2     |

| AND(B)             | Bitwise AND, (word/byte operands)                                                                    | 2/4   |

| OR(B)              | Bitwise OR, (word/byte operands)                                                                     | 2/4   |

| XOR(B)             | Bitwise XOR, (word/byte operands)                                                                    | 2/4   |

| BCLR               | Clear direct bit                                                                                     | 2     |

| BSET               | Set direct bit                                                                                       | 2     |

| BMOV(N)            | Move (negated) direct bit to direct bit                                                              | 4     |

| BAND, BOR,<br>BXOR | AND/OR/XOR direct bit with direct bit                                                                | 4     |

| BCMP               | Compare direct bit to direct bit                                                                     | 4     |

| BFLDH/L            | Bitwise modify masked high/low byte of bit-addressable direct word memory with immediate data        | 4     |

| CMP(B)             | Compare word (byte) operands                                                                         | 2/4   |

| CMPD1/2            | Compare word data to GPR and decrement GPR by 1/2                                                    | 2/4   |

| CMPI1/2            | Compare word data to GPR and increment GPR by 1/2                                                    | 2/4   |

| PRIOR              | Determine number of shift cycles to normalize direct<br>word GPR and store result in direct word GPR | 2     |

| SHL / SHR          | Shift left/right direct word GPR                                                                     | 2     |

| ROL / ROR          | Rotate left/right direct word GPR                                                                    | 2     |

| ASHR               | Arithmetic (sign bit) shift right direct word GPR                                                    | 2     |

#### Table 5Instruction Set Summary

| Table 6C165 Registers, Ordered by Name (cont'd) |   |                   |             |                 |                                         |                   |  |  |

|-------------------------------------------------|---|-------------------|-------------|-----------------|-----------------------------------------|-------------------|--|--|

| Name Physical<br>Address                        |   | 8-Bit<br>Addr.    | Description | Reset<br>Value  |                                         |                   |  |  |

| СР                                              |   | FE10 <sub>H</sub> |             | 08 <sub>H</sub> | CPU Context Pointer Register            | FC00 <sub>H</sub> |  |  |

| CRIC                                            | b | FF6A <sub>H</sub> |             | B5 <sub>H</sub> | GPT2 CAPREL Interrupt Ctrl. Reg.        | 0000 <sub>H</sub> |  |  |

| CSP                                             |   | FE08 <sub>H</sub> |             | 04 <sub>H</sub> | CPU Code Seg. Pointer Reg. (read only)  | 0000 <sub>H</sub> |  |  |

| DP0H                                            | b | F102 <sub>H</sub> | Ε           | 81 <sub>H</sub> | P0H Direction Control Register          | 00 <sub>H</sub>   |  |  |

| DP0L                                            | b | F100 <sub>H</sub> | Ε           | 80 <sub>H</sub> | P0L Direction Control Register          | 00 <sub>H</sub>   |  |  |

| DP1H                                            | b | F106 <sub>H</sub> | Ε           | 83 <sub>H</sub> | P1H Direction Control Register          | 00 <sub>H</sub>   |  |  |

| DP1L                                            | b | F104 <sub>H</sub> | Ε           | 82 <sub>H</sub> | P1L Direction Control Register          | 00 <sub>H</sub>   |  |  |

| DP2                                             | b | FFC2 <sub>H</sub> |             | E1 <sub>H</sub> | Port 2 Direction Control Register       | 0000 <sub>H</sub> |  |  |

| DP3                                             | b | FFC6 <sub>H</sub> |             | E3 <sub>H</sub> | Port 3 Direction Control Register       | 0000 <sub>H</sub> |  |  |

| DP4                                             | b | FFCA <sub>H</sub> |             | E5 <sub>H</sub> | Port 4 Direction Control Register       | 00 <sub>H</sub>   |  |  |

| DP6                                             | b | FFCE <sub>H</sub> |             | E7 <sub>H</sub> | Port 6 Direction Control Register       | 00 <sub>H</sub>   |  |  |

| DPP0                                            |   | FE00 <sub>H</sub> |             | 00 <sub>H</sub> | CPU Data Page Pointer 0 Reg. (10 bits)  | 0000 <sub>H</sub> |  |  |

| DPP1                                            |   | FE02 <sub>H</sub> |             | 01 <sub>H</sub> | CPU Data Page Pointer 1 Reg. (10 bits)  | 0001 <sub>H</sub> |  |  |

| DPP2                                            |   | FE04 <sub>H</sub> |             | 02 <sub>H</sub> | CPU Data Page Pointer 2 Reg. (10 bits)  | 0002 <sub>H</sub> |  |  |

| DPP3                                            |   | FE06 <sub>H</sub> |             | 03 <sub>H</sub> | CPU Data Page Pointer 3 Reg. (10 bits)  | 0003 <sub>H</sub> |  |  |

| EXICON                                          | b | F1C0 <sub>H</sub> | Ε           | E0 <sub>H</sub> | External Interrupt Control Register     | 0000 <sub>H</sub> |  |  |

| IDCHIP                                          |   | F07C <sub>H</sub> | Ε           | 3E <sub>H</sub> | Identifier                              | 05XX <sub>H</sub> |  |  |

| IDMANUF                                         |   | F07E <sub>H</sub> | Ε           | 3F <sub>H</sub> | Identifier                              | 1820 <sub>H</sub> |  |  |

| IDMEM                                           |   | F07A <sub>H</sub> | Ε           | 3D <sub>H</sub> | Identifier                              | 0000 <sub>H</sub> |  |  |

| IDMEM2                                          |   | F076 <sub>H</sub> | Ε           | 3B <sub>H</sub> | Identifier                              | 0000 <sub>H</sub> |  |  |

| IDPROG                                          |   | F078 <sub>H</sub> | Ε           | 3C <sub>H</sub> | Identifier                              | 0000 <sub>H</sub> |  |  |

| MDC                                             | b | FF0E <sub>H</sub> |             | 87 <sub>H</sub> | CPU Multiply Divide Control Register    | 0000 <sub>H</sub> |  |  |

| MDH                                             |   | FE0C <sub>H</sub> |             | 06 <sub>H</sub> | CPU Multiply Divide Reg. – High Word    | 0000 <sub>H</sub> |  |  |

| MDL                                             |   | FE0E <sub>H</sub> |             | 07 <sub>H</sub> | CPU Multiply Divide Reg. – Low Word     | 0000 <sub>H</sub> |  |  |

| ODP2                                            | b | F1C2 <sub>H</sub> | Ε           | E1 <sub>H</sub> | Port 2 Open Drain Control Register      | 0000 <sub>H</sub> |  |  |

| ODP3                                            | b | F1C6 <sub>H</sub> | Ε           | E3 <sub>H</sub> | Port 3 Open Drain Control Register      | 0000 <sub>H</sub> |  |  |

| ODP6                                            | b | F1CE <sub>H</sub> | Ε           | E7 <sub>H</sub> | Port 6 Open Drain Control Register      | 00 <sub>H</sub>   |  |  |

| ONES                                            | b | FF1E <sub>H</sub> |             | 8F <sub>H</sub> | Constant Value 1's Register (read only) | FFFF <sub>H</sub> |  |  |

|                                                 |   | 1                 |             | 1               |                                         |                   |  |  |

P0H

P0L

00<sub>H</sub>

00<sub>H</sub>

Port 0 High Reg. (Upper half of PORT0)

Port 0 Low Reg. (Lower half of PORT0)

81<sub>H</sub>

80<sub>H</sub>

FF02<sub>H</sub>

$FF00_{H}$

b

b

| Table 6C165 Registers, Ordered by Name (cont'd) |   |                     |                 |                                                                       |                   |  |  |  |

|-------------------------------------------------|---|---------------------|-----------------|-----------------------------------------------------------------------|-------------------|--|--|--|

| lame                                            |   | Physical<br>Address | 8-Bit<br>Addr.  | Description                                                           | Reset<br>Value    |  |  |  |

| P1H                                             | b | FF06 <sub>H</sub>   | 83 <sub>H</sub> | Port 1 High Reg. (Upper half of PORT1)                                | 00 <sub>H</sub>   |  |  |  |

| 91L                                             | b | FF04 <sub>H</sub>   | 82 <sub>H</sub> | Port 1 Low Reg.(Lower half of PORT1)                                  | 00 <sub>H</sub>   |  |  |  |

| 2                                               | b | FFC0 <sub>H</sub>   | E0 <sub>H</sub> | Port 2 Register                                                       | 0000 <sub>H</sub> |  |  |  |

| <b>v</b> 3                                      | b | FFC4 <sub>H</sub>   | E2 <sub>H</sub> | Port 3 Register                                                       | 0000 <sub>H</sub> |  |  |  |

| 94                                              | b | FFC8 <sub>H</sub>   | E4 <sub>H</sub> | Port 4 Register (8 bits)                                              | 00 <sub>H</sub>   |  |  |  |

| <b>?</b> 5                                      | b | FFA2 <sub>H</sub>   | D1 <sub>H</sub> | Port 5 Register (read only)                                           | XXXX <sub>H</sub> |  |  |  |

| <b>°</b> 6                                      | b | FFCC <sub>H</sub>   | E6 <sub>H</sub> | Port 6 Register (8 bits)                                              | 00 <sub>H</sub>   |  |  |  |

| PECC0                                           |   | FEC0 <sub>H</sub>   | 60 <sub>H</sub> | PEC Channel 0 Control Register                                        | 0000 <sub>H</sub> |  |  |  |

| PECC1                                           |   | FEC2 <sub>H</sub>   | 61 <sub>H</sub> | PEC Channel 1 Control Register                                        | 0000 <sub>H</sub> |  |  |  |

| PECC2                                           |   | FEC4 <sub>H</sub>   | 62 <sub>H</sub> | PEC Channel 2 Control Register                                        | 0000 <sub>H</sub> |  |  |  |

| PECC3                                           |   | FEC6 <sub>H</sub>   | 63 <sub>H</sub> | PEC Channel 3 Control Register                                        | 0000 <sub>H</sub> |  |  |  |

| PECC4                                           |   | FEC8 <sub>H</sub>   | 64 <sub>H</sub> |                                                                       |                   |  |  |  |

| PECC5                                           |   | FECA <sub>H</sub>   | 65 <sub>H</sub> | PEC Channel 5 Control Register                                        | 0000 <sub>H</sub> |  |  |  |

| PECC6                                           |   | FECC <sub>H</sub>   | 66 <sub>H</sub> | PEC Channel 6 Control Register                                        | 0000 <sub>H</sub> |  |  |  |

| PECC7                                           |   | FECE <sub>H</sub>   | 67 <sub>H</sub> | PEC Channel 7 Control Register                                        | 0000 <sub>H</sub> |  |  |  |

| PSW                                             | b | FF10 <sub>H</sub>   | 88 <sub>H</sub> | CPU Program Status Word                                               | 0000 <sub>H</sub> |  |  |  |

| RP0H                                            | b | F108 <sub>H</sub> E | 84 <sub>H</sub> | System Startup Config. Reg. (Rd. only)                                | XX <sub>H</sub>   |  |  |  |

| 60BG                                            |   | FEB4 <sub>H</sub>   | 5A <sub>H</sub> | Serial Channel 0 Baud Rate Generator Reload Register                  | 0000 <sub>H</sub> |  |  |  |

| 50CON                                           | b | FFB0 <sub>H</sub>   | D8 <sub>H</sub> | Serial Channel 0 Control Register                                     | 0000 <sub>H</sub> |  |  |  |

| SOEIC                                           | b | FF70 <sub>H</sub>   | B8 <sub>H</sub> | Serial Channel 0 Error Interrupt Ctrl. Reg                            | 0000 <sub>H</sub> |  |  |  |

| ORBUF                                           |   | FEB2 <sub>H</sub>   | 59 <sub>H</sub> | Serial Channel 0 Receive Buffer Reg.<br>(read only)                   | XX <sub>H</sub>   |  |  |  |

| SORIC                                           | b | FF6E <sub>H</sub>   | B7 <sub>H</sub> | 7 <sub>H</sub> Serial Channel 0 Receive Interrupt<br>Control Register |                   |  |  |  |

| <b>OTBIC</b>                                    | b | F19C <sub>H</sub> E | CEH             | Serial Channel 0 Transmit Buffer<br>Interrupt Control Register        | 0000 <sub>H</sub> |  |  |  |

| OTBUF                                           |   | FEB0 <sub>H</sub>   | 58 <sub>H</sub> | Serial Channel 0 Transmit Buffer<br>Register (write only)             | 00 <sub>H</sub>   |  |  |  |

| SOTIC                                           | b | FF6C <sub>H</sub>   | B6 <sub>H</sub> | Serial Channel 0 Transmit Interrupt<br>Control Register               | 0000 <sub>H</sub> |  |  |  |

|                                                 | b |                     |                 | Register (write only)<br>Serial Channel 0 Transmit Interrupt          |                   |  |  |  |

| ame (cont'd) |

|--------------|

|              |

| Name Physical<br>Address |   |                                             |                                                               | 8-Bit<br>Addr.  | Description                                   | Reset<br>Value                  |                                         |                   |

|--------------------------|---|---------------------------------------------|---------------------------------------------------------------|-----------------|-----------------------------------------------|---------------------------------|-----------------------------------------|-------------------|

| SP                       |   | FE12 <sub>H</sub>                           |                                                               | 09 <sub>H</sub> | CPU System Stack Pointer Register             | FC00 <sub>H</sub>               |                                         |                   |

| SSCBR                    |   | F0B4 <sub>H</sub>                           | Ε                                                             | 5A <sub>H</sub> | SSC Baudrate Register                         | 0000 <sub>H</sub>               |                                         |                   |

| SSCCON                   | b | FFB2 <sub>H</sub>                           |                                                               | D9 <sub>H</sub> | SSC Control Register                          | 0000 <sub>H</sub>               |                                         |                   |

| SSCEIC                   | b | FF76 <sub>H</sub>                           |                                                               | BB <sub>H</sub> | SSC Error Interrupt Control Register          | 0000 <sub>H</sub>               |                                         |                   |

| SSCRB                    |   | F0B2 <sub>H</sub>                           | Ε                                                             | 59 <sub>H</sub> | SSC Receive Buffer                            | XXXX <sub>H</sub>               |                                         |                   |

| SSCRIC                   | b | FF74 <sub>H</sub>                           |                                                               | BA <sub>H</sub> | SSC Receive Interrupt Control Register        | 0000 <sub>H</sub>               |                                         |                   |

| SSCTB                    |   | F0B0 <sub>H</sub>                           | Ε                                                             | 58 <sub>H</sub> | SSC Transmit Buffer                           | 0000 <sub>H</sub>               |                                         |                   |

| SSCTIC                   | b | FF72 <sub>H</sub>                           |                                                               | B9 <sub>H</sub> | SSC Transmit Interrupt Control Register       | 0000 <sub>H</sub>               |                                         |                   |

| STKOV                    |   | FE14 <sub>H</sub>                           |                                                               | 0A <sub>H</sub> | CPU Stack Overflow Pointer Register           | FA00 <sub>H</sub>               |                                         |                   |

| STKUN                    |   | FE16 <sub>H</sub>                           |                                                               | 0B <sub>H</sub> | CPU Stack Underflow Pointer Register          | FC00 <sub>H</sub>               |                                         |                   |

| SYSCON                   | b | FF12 <sub>H</sub>                           |                                                               | 89 <sub>H</sub> | CPU System Configuration Register             | <sup>1)</sup> 0XX0 <sub>H</sub> |                                         |                   |

| T2                       |   | FE40 <sub>H</sub>                           |                                                               | 20 <sub>H</sub> | GPT1 Timer 2 Register                         | 0000 <sub>H</sub>               |                                         |                   |

| T2CON                    | b | FF40 <sub>H</sub>                           | A0 <sub>H</sub> A0 <sub>H</sub> GPT1 Timer 2 Control Register |                 |                                               |                                 |                                         |                   |

| T2IC                     | b | FF60 <sub>H</sub> B0 <sub>H</sub> GPT1 Time |                                                               |                 | GPT1 Timer 2 Interrupt Control Register       | 0000 <sub>H</sub>               |                                         |                   |

| Т3                       |   | FE42 <sub>H</sub>                           |                                                               | 21 <sub>H</sub> | GPT1 Timer 3 Register                         | 0000 <sub>H</sub>               |                                         |                   |

| T3CON                    | b | FF42 <sub>H</sub>                           |                                                               | A1 <sub>H</sub> | GPT1 Timer 3 Control Register                 | 0000 <sub>H</sub>               |                                         |                   |

| T3IC                     | b | FF62 <sub>H</sub>                           | B1 <sub>H</sub>                                               |                 | F62 <sub>H</sub> B1 <sub>H</sub> GPT1 Timer : |                                 | GPT1 Timer 3 Interrupt Control Register | 0000 <sub>H</sub> |

| T4                       |   | FE44 <sub>H</sub>                           |                                                               | 22 <sub>H</sub> | GPT1 Timer 4 Register                         | 0000 <sub>H</sub>               |                                         |                   |

| T4CON                    | b | FF44 <sub>H</sub>                           |                                                               | A2 <sub>H</sub> | GPT1 Timer 4 Control Register                 | 0000 <sub>H</sub>               |                                         |                   |

| T4IC                     | b | FF64 <sub>H</sub>                           |                                                               | B2 <sub>H</sub> | GPT1 Timer 4 Interrupt Control Register       | 0000 <sub>H</sub>               |                                         |                   |

| Т5                       |   | FE46 <sub>H</sub>                           |                                                               | 23 <sub>H</sub> | GPT2 Timer 5 Register                         | 0000 <sub>H</sub>               |                                         |                   |

| T5CON                    | b | FF46 <sub>H</sub>                           |                                                               | A3 <sub>H</sub> | GPT2 Timer 5 Control Register                 | 0000 <sub>H</sub>               |                                         |                   |

| T5IC                     | b | FF66 <sub>H</sub>                           |                                                               | B3 <sub>H</sub> | GPT2 Timer 5 Interrupt Control Register       | 0000 <sub>H</sub>               |                                         |                   |

| Т6                       |   | FE48 <sub>H</sub>                           |                                                               | 24 <sub>H</sub> | GPT2 Timer 6 Register                         | 0000 <sub>H</sub>               |                                         |                   |

| T6CON                    | b | FF48 <sub>H</sub>                           |                                                               | A4 <sub>H</sub> | GPT2 Timer 6 Control Register                 | 0000 <sub>H</sub>               |                                         |                   |

| T6IC                     | b | FF68 <sub>H</sub>                           |                                                               | B4 <sub>H</sub> | GPT2 Timer 6 Interrupt Control Register       | 0000 <sub>H</sub>               |                                         |                   |

| TFR                      | b | FFAC <sub>H</sub>                           |                                                               | D6 <sub>H</sub> | Trap Flag Register                            | 0000 <sub>H</sub>               |                                         |                   |

| WDT                      |   | FEAE <sub>H</sub>                           |                                                               | 57 <sub>H</sub> | Watchdog Timer Register (read only)           | 0000 <sub>H</sub>               |                                         |                   |

| WDTCON                   | b | FFAE <sub>H</sub>                           |                                                               | D7 <sub>H</sub> | Watchdog Timer Control Register               | <sup>2)</sup> 00XX <sub>H</sub> |                                         |                   |

| XP0IC                    | b | F186 <sub>H</sub>                           | Е                                                             | C3 <sub>H</sub> | Software Interrupt Control Register           | 0000 <sub>H</sub>               |                                         |                   |

## **Absolute Maximum Ratings**

| Parameter                                                                  | Symbol            | Limit | Values                | Unit | Notes      |

|----------------------------------------------------------------------------|-------------------|-------|-----------------------|------|------------|

|                                                                            |                   | min.  | max.                  |      |            |

| Storage temperature                                                        | T <sub>ST</sub>   | - 65  | 150                   | °C   | -          |

| Junction temperature                                                       | TJ                | - 40  | 150                   | °C   | under bias |

| Voltage on $V_{\text{DD}}$ pins with respect to ground ( $V_{\text{SS}}$ ) | V <sub>DD</sub>   | - 0.5 | 6.5                   | V    | _          |

| Voltage on any pin with respect to ground $(V_{SS})$                       | V <sub>IN</sub>   | - 0.5 | V <sub>DD</sub> + 0.5 | V    | _          |

| Input current on any pin during overload condition                         | -                 | - 10  | 10                    | mA   | _          |

| Absolute sum of all input<br>currents during overload<br>condition         | -                 | -     | 100                   | mA   | -          |

| Power dissipation                                                          | P <sub>DISS</sub> | -     | 1.5                   | W    | -          |

#### Table 7 Absolute Maximum Rating Parameters

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DD}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DD}$  pins with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

#### **Operating Conditions**

The following operating conditions must not be exceeded in order to ensure correct operation of the C165. All parameters specified in the following sections refer to these operating conditions, unless otherwise noticed.

| Parameter                         | Symbol                | Limit             | Values | Unit | Notes                                         |  |

|-----------------------------------|-----------------------|-------------------|--------|------|-----------------------------------------------|--|

|                                   |                       | min.              | max.   |      |                                               |  |

| Standard digital supply voltage   | V <sub>DD</sub>       | 4.5               | 5.5    | V    | Active mode,<br>$f_{CPUmax} = 25 \text{ MHz}$ |  |

| (5 V versions)                    |                       | 2.5 <sup>1)</sup> | 5.5    | V    | PowerDown mode                                |  |

| Reduced<br>digital supply voltage | V <sub>DD</sub>       | 3.0               | 3.6    | V    | Active mode,<br>$f_{CPUmax} = 20 \text{ MHz}$ |  |

| (3 V versions)                    |                       | 2.5 <sup>1)</sup> | 3.6    | V    | PowerDown mode                                |  |

| Digital ground voltage            | V <sub>SS</sub>       |                   | 0      | V    | Reference voltage                             |  |

| Overload current                  | I <sub>OV</sub>       | _                 | ± 5    | mA   | Per pin <sup>2)3)</sup>                       |  |

| Absolute sum of overload currents | $\Sigma  I_{\rm OV} $ | _                 | 50     | mA   | 3)                                            |  |

| External Load<br>Capacitance      | CL                    | _                 | 100    | pF   | -                                             |  |

| Ambient temperature               | T <sub>A</sub>        | 0                 | 70     | °C   | SAB-C165                                      |  |

|                                   |                       | - 40              | 85     | °C   | SAF-C165                                      |  |

|                                   |                       | - 40              | 125    | °C   | SAK-C165                                      |  |

#### Table 8Operating Condition Parameters

<sup>1)</sup> Output voltages and output currents will be reduced when  $V_{\text{DD}}$  leaves the range defined for active mode.

<sup>2)</sup> Overload conditions occur if the standard operatings conditions are exceeded, i.e. the voltage on any pin exceeds the specified range (i.e. V<sub>OV</sub> > V<sub>DD</sub> + 0.5 V or V<sub>OV</sub> < V<sub>SS</sub> - 0.5 V). The absolute sum of input overload currents on all pins may not exceed **50 mA**. The supply voltage must remain within the specified limits. Proper operation is not guaranteed if overload conditions occur on functional pins such as XTAL1, RD, WR, etc.

<sup>3)</sup> Not 100% tested, guaranteed by design and characterization.

#### Parameter Interpretation

The parameters listed in the following partly represent the characteristics of the C165 and partly its demands on the system. To aid in interpreting the parameters right, when evaluating them for a design, they are marked in column "Symbol":

CC (Controller Characteristics):

The logic of the C165 will provide signals with the respective timing characteristics.

**SR** (System Requirement):

The external system must provide signals with the respective timing characteristics to the C165.

#### DC Characteristics (Standard Supply Voltage Range)

(Operating Conditions apply)<sup>1)</sup>

| Parameter                                                                                          | Symbol                          | Limit '                      | Values                       | Unit | <b>Test Condition</b>                           |  |

|----------------------------------------------------------------------------------------------------|---------------------------------|------------------------------|------------------------------|------|-------------------------------------------------|--|

|                                                                                                    |                                 | min.                         | max.                         |      |                                                 |  |

| Input low voltage (TTL,<br>all except XTAL1)                                                       | V <sub>IL</sub> SR              | - 0.5                        | 0.2 V <sub>DD</sub><br>- 0.1 | V    | -                                               |  |

| Input low voltage XTAL1                                                                            | $V_{IL2}$ SR                    | - 0.5                        | 0.3 V <sub>DD</sub>          | V    | -                                               |  |

| Input high voltage (TTL,<br>all except RSTIN and XTAL1)                                            | V <sub>IH</sub> SR              | 0.2 V <sub>DD</sub><br>+ 0.9 | V <sub>DD</sub> + 0.5        | V    | _                                               |  |

| Input high voltage RSTIN<br>(when operated as input)                                               | V <sub>IH1</sub> SR             | 0.6 V <sub>DD</sub>          | V <sub>DD</sub> + 0.5        | V    | _                                               |  |

| Input high voltage XTAL1                                                                           | V <sub>IH2</sub> SR             | 0.7 V <sub>DD</sub>          | V <sub>DD</sub> +<br>0.5     | V    | _                                               |  |

| Output low voltage<br>(PORT0, PORT1, Port 4, ALE,<br>RD, WR, BHE, RSTOUT,<br>RSTIN <sup>2)</sup> ) | V <sub>OL</sub> CC              | -                            | 0.45                         | V    | I <sub>OL</sub> = 2.4 mA                        |  |

| Output low voltage<br>(all other outputs)                                                          | V <sub>OL1</sub> CC             | _                            | 0.45                         | V    | <i>I</i> <sub>OL</sub> = 1.6 mA                 |  |

| Output high voltage <sup>3)</sup>                                                                  | V <sub>OH</sub> CC              | 2.4                          | _                            | V    | I <sub>OH</sub> = - 2.4 mA                      |  |

| (PORT0, PORT1, Port 4, ALE,<br>RD, WR, BHE, RSTOUT)                                                |                                 | 0.9 V <sub>DD</sub>          | _                            | V    | I <sub>OH</sub> = - 0.5 mA                      |  |

| Output high voltage <sup>3)</sup>                                                                  | V <sub>OH1</sub> CC             | 2.4                          | _                            | V    | I <sub>OH</sub> = - 1.6 mA                      |  |

| (all other outputs)                                                                                |                                 | 0.9 V <sub>DD</sub>          | _                            | V    | I <sub>OH</sub> = - 0.5 mA                      |  |

| Input leakage current (Port 5)                                                                     | I <sub>OZ1</sub> CC             | -                            | ± 200                        | nA   | $0 V < V_{IN} < V_{DD}$                         |  |

| Input leakage current (all other)                                                                  | I <sub>OZ2</sub> CC             | _                            | ± 500                        | nA   | $0.45 \text{ V} < V_{\text{IN}} < V_{\text{E}}$ |  |

| RSTIN inactive current <sup>4)</sup>                                                               | I <sub>RSTH</sub> <sup>5)</sup> | _                            | - 10                         | μA   | $V_{\rm IN} = V_{\rm IH1}$                      |  |

# DC Characteristics (Reduced Supply Voltage Range) (cont'd)

(Operating Conditions apply)<sup>1)</sup>

| Parameter                                                 | Symbol                                | Limit Values |      | Unit | Test Condition                      |

|-----------------------------------------------------------|---------------------------------------|--------------|------|------|-------------------------------------|

|                                                           |                                       | min.         | max. |      |                                     |

| PORT0 configuration current <sup>8)</sup>                 | I <sub>P0H</sub> <sup>5)</sup>        | _            | - 5  | μA   | $V_{\rm IN} = V_{\rm IHmin}$        |

|                                                           | <i>I</i> <sub>P0L</sub> <sup>6)</sup> | - 100        | _    | μA   | $V_{\rm IN} = V_{\rm ILmax}$        |

| XTAL1 input current                                       | I <sub>IL</sub> CC                    | _            | ± 20 | μA   | $0 V < V_{IN} < V_{DD}$             |

| Pin capacitance <sup>9)</sup><br>(digital inputs/outputs) | C <sub>IO</sub> CC                    | _            | 10   | pF   | f = 1  MHz<br>$T_A = 25 \text{ °C}$ |

<sup>1)</sup> Keeping signal levels within the levels specified in this table, ensures operation without overload conditions. For signal levels outside these specifications also refer to the specification of the overload current  $I_{OV}$ .

<sup>2)</sup> Valid in bidirectional reset mode only.

<sup>3)</sup> This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage results from the external circuitry.

- <sup>4)</sup> These parameters describe the  $\overline{\text{RSTIN}}$  pullup, which equals a resistance of ca. 50 to 250 k $\Omega$ .

- <sup>5)</sup> The maximum current may be drawn while the respective signal line remains inactive.

- <sup>6)</sup> The minimum current must be drawn in order to drive the respective signal line active.

- <sup>7)</sup> This specification is valid during Reset and during Hold-mode or Adapt-mode. During Hold-mode Port 6 pins are only affected, if they are used (configured) for CS output and the open drain function is not enabled. The READY-pullup is always active, except for Powerdown mode.

- <sup>8)</sup> This specification is valid during Reset and during Adapt-mode.

- <sup>9)</sup> Not 100% tested, guaranteed by design and characterization.

## Power Consumption C165 (Standard Supply Voltage Range)

(Operating Conditions apply)

| Parameter                                                 | Symbol            | Lim  | it Values                             | Unit | <b>Test Condition</b>                                                                     |  |

|-----------------------------------------------------------|-------------------|------|---------------------------------------|------|-------------------------------------------------------------------------------------------|--|

|                                                           |                   | min. | max.                                  |      |                                                                                           |  |

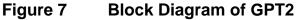

| Power supply current (active) with all peripherals active | I <sub>DD5</sub>  | -    | 15 +<br>1.8 × <i>f</i> <sub>CPU</sub> | mA   | $\overline{\text{RSTIN}} = V_{\text{IL}}$ $f_{\text{CPU}} \text{ in } [\text{MHz}]^{1)}$  |  |

| Idle mode supply current<br>with all peripherals active   | I <sub>IDX5</sub> | _    | 2 +<br>0.4 × f <sub>CPU</sub>         | mA   | $\overline{\text{RSTIN}} = V_{\text{IH1}}$ $f_{\text{CPU}} \text{ in } [\text{MHz}]^{1)}$ |  |

| Power-down mode supply current                            | I <sub>PDO5</sub> | -    | 50                                    | μA   | $V_{\rm DD} = V_{\rm DDmax}^{2)}$                                                         |  |

<sup>1)</sup> The supply current is a function of the operating frequency. This dependency is illustrated in Figure 8. These parameters are tested at V<sub>DDmax</sub> and maximum CPU clock with all outputs disconnected and all inputs at V<sub>IL</sub> or V<sub>IH</sub>.

<sup>2)</sup> This parameter is tested including leakage currents. All inputs (including pins configured as inputs) at 0 V to 0.1 V or at  $V_{DD}$  – 0.1 V to  $V_{DD}$ , all outputs (including pins configured as outputs) disconnected.

#### Power Consumption C165 (Reduced Supply Voltage Range)

(Operating Conditions apply)

| Parameter                                                 | Symbol            | Lim  | it Values                     | Unit | <b>Test Condition</b>                                                                |  |

|-----------------------------------------------------------|-------------------|------|-------------------------------|------|--------------------------------------------------------------------------------------|--|

|                                                           |                   | min. | max.                          |      |                                                                                      |  |

| Power supply current (active) with all peripherals active | I <sub>DD3</sub>  | -    | 3 +<br>1.3 × f <sub>CPU</sub> | mA   | $\overline{\text{RSTIN}} = V_{\text{IL}}$ $f_{\text{CPU}} \text{ in [MHz]}^{1)}$     |  |

| Idle mode supply current<br>with all peripherals active   | I <sub>IDX3</sub> | -    | 1 +<br>0.4 × f <sub>CPU</sub> | mA   | $\frac{\text{RSTIN} = V_{\text{IH1}}}{f_{\text{CPU}} \text{ in } [\text{MHz}]^{1)}}$ |  |

| Power-down mode supply current                            | I <sub>PDO3</sub> | -    | 30                            | μA   | $V_{\rm DD} = V_{\rm DDmax}^{2)}$                                                    |  |

<sup>1)</sup> The supply current is a function of the operating frequency. This dependency is illustrated in Figure 8. These parameters are tested at V<sub>DDmax</sub> and maximum CPU clock with all outputs disconnected and all inputs at V<sub>IL</sub> or V<sub>IH</sub>.

<sup>2)</sup> This parameter is tested including leakage currents. All inputs (including pins configured as inputs) at 0 V to 0.1 V or at  $V_{DD}$  – 0.1 V to  $V_{DD}$ , all outputs (including pins configured as outputs) disconnected.

Figure 8 Supply/Idle Current as a Function of Operating Frequency

C165

### **Testing Waveforms**

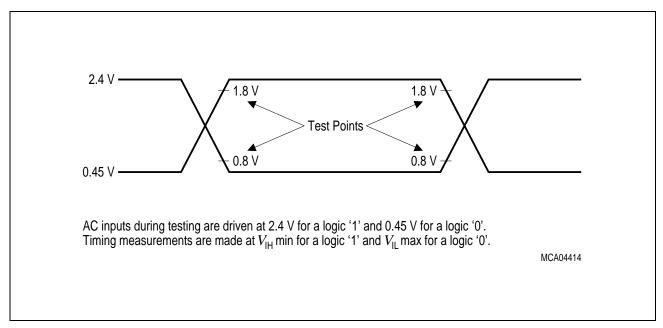

Figure 11 Input Output Waveforms

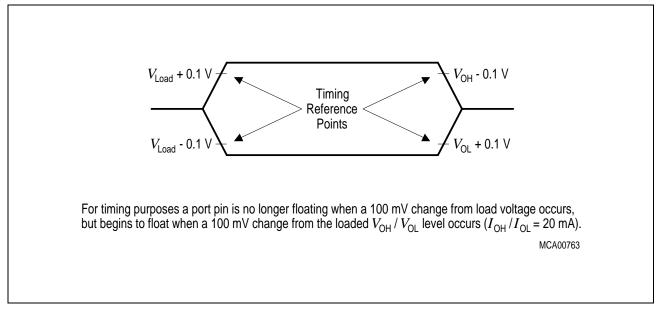

Figure 12 Float Waveforms

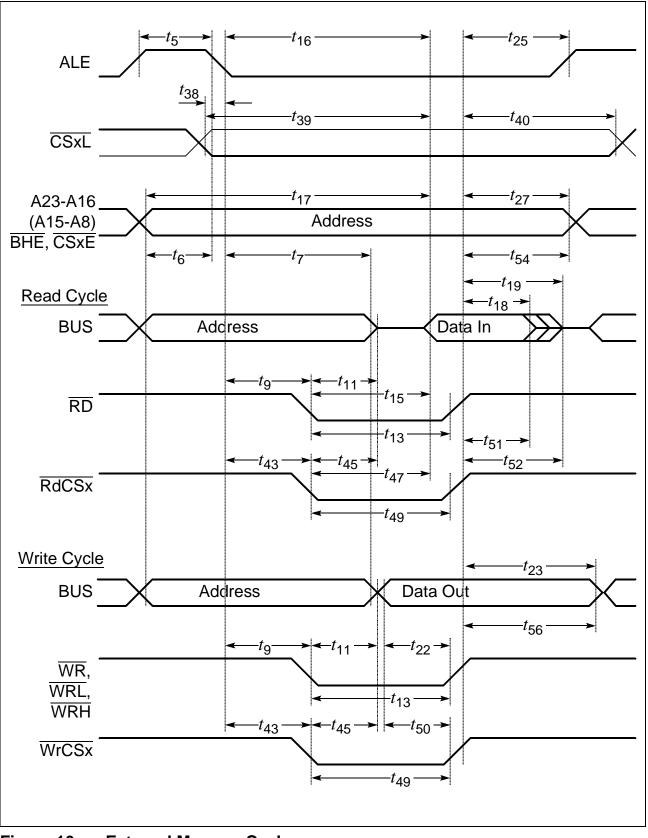

## Multiplexed Bus (Reduced Supply Voltage Range) (cont'd)

(Operating Conditions apply)

ALE cycle time = 6 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (150 ns at 20 MHz CPU clock without waitstates)

| Parameter                                                          | Symbol                 |    | Max. CPU Clock<br>= 20 MHz  |                            | Variable CPU Clock<br>1 / 2TCL = 1 to 20 MHz |                                                                | Unit |

|--------------------------------------------------------------------|------------------------|----|-----------------------------|----------------------------|----------------------------------------------|----------------------------------------------------------------|------|

|                                                                    |                        |    | min.                        | max.                       | min.                                         | max.                                                           |      |

| Data float after RD                                                | t <sub>19</sub>        | SR | _                           | $36 + t_{\rm F}$           | -                                            | 2TCL - 14<br>+ <i>t</i> <sub>F</sub>                           | ns   |

| Data valid to $\overline{WR}$                                      | t <sub>22</sub>        | CC | $24 + t_{\rm C}$            | -                          | 2TCL - 26<br>+ <i>t</i> <sub>C</sub>         | -                                                              | ns   |

| Data hold after $\overline{WR}$                                    | <i>t</i> <sub>23</sub> | CC | 36 + <i>t</i> <sub>F</sub>  | -                          | 2TCL - 14<br>+ <i>t</i> <sub>F</sub>         | -                                                              | ns   |

| ALE rising edge after $\overline{RD}$ , $\overline{WR}$            | t <sub>25</sub>        | CC | 36 + <i>t</i> <sub>F</sub>  | -                          | 2TCL - 14<br>+ <i>t</i> <sub>F</sub>         | -                                                              | ns   |

| Address hold after RD,<br>WR                                       | t <sub>27</sub>        | CC | 36 + <i>t</i> <sub>F</sub>  | -                          | 2TCL - 14<br>+ <i>t</i> <sub>F</sub>         | -                                                              | ns   |

| ALE falling edge to $\overline{\text{CS}}^{1)}$                    | t <sub>38</sub>        | CC | - 8 - <i>t</i> <sub>A</sub> | 10 - <i>t</i> <sub>A</sub> | - 8 - <i>t</i> <sub>A</sub>                  | 10 - <i>t</i> <sub>A</sub>                                     | ns   |

| CS low to Valid Data In <sup>1)</sup>                              | t <sub>39</sub>        | SR | _                           | $47 + t_{C} + 2t_{A}$      | -                                            | 3TCL - 28<br>+ <i>t</i> <sub>C</sub> + 2 <i>t</i> <sub>A</sub> | ns   |

| $\overline{CS}$ hold after $\overline{RD}$ , $\overline{WR}^{(1)}$ | <i>t</i> <sub>40</sub> | CC | 57 + <i>t</i> <sub>F</sub>  | -                          | 3TCL - 18<br>+ <i>t</i> <sub>F</sub>         | -                                                              | ns   |

| ALE fall. edge to RdCS,<br>WrCS (with RW delay)                    | <i>t</i> <sub>42</sub> | CC | 19 + <i>t</i> <sub>A</sub>  | -                          | TCL - 6<br>+ <i>t</i> <sub>A</sub>           | -                                                              | ns   |

| ALE fall. edge to RdCS,<br>WrCS (no RW delay)                      | <i>t</i> <sub>43</sub> | CC | $-6 + t_{A}$                | -                          | - 6<br>+ <i>t</i> <sub>A</sub>               | -                                                              | ns   |

| Address float after RdCS,<br>WrCS (with RW delay)                  | <i>t</i> <sub>44</sub> | CC | _                           | 0                          | -                                            | 0                                                              | ns   |

| Address float after RdCS,<br>WrCS (no RW delay)                    | t <sub>45</sub>        | CC | _                           | 25                         | -                                            | TCL                                                            | ns   |

| RdCS to Valid Data In<br>(with RW delay)                           | <i>t</i> <sub>46</sub> | SR | _                           | $20 + t_{\rm C}$           | -                                            | 2TCL - 30<br>+ <i>t</i> <sub>C</sub>                           | ns   |

| RdCS to Valid Data In (no RW delay)                                | <i>t</i> <sub>47</sub> | SR | _                           | $45 + t_{\rm C}$           | -                                            | 3TCL - 30<br>+ <i>t</i> <sub>C</sub>                           | ns   |

| RdCS, WrCS Low Time<br>(with RW delay)                             | t <sub>48</sub>        | CC | $38 + t_{\rm C}$            | -                          | 2TCL - 12<br>+ <i>t</i> <sub>C</sub>         | -                                                              | ns   |

| RdCS, WrCS Low Time<br>(no RW delay)                               | t <sub>49</sub>        | CC | $63 + t_{\rm C}$            | -                          | 3TCL - 12<br>+ <i>t</i> <sub>C</sub>         | -                                                              | ns   |

Figure 16 External Memory Cycle: Multiplexed Bus, No Read/Write Delay, Extended ALE

## Demultiplexed Bus (Standard Supply Voltage Range) (cont'd)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (80 ns at 25 MHz CPU clock without waitstates)

| Parameter                                                                              | Symbol                    | Max. CPU Clock<br>= 25 MHz   |                            | Variable CPU Clock<br>1 / 2TCL = 1 to 25 MHz |                                      | Unit |

|----------------------------------------------------------------------------------------|---------------------------|------------------------------|----------------------------|----------------------------------------------|--------------------------------------|------|

|                                                                                        |                           | min.                         | max.                       | min.                                         | max.                                 |      |

| Data valid to $\overline{WR}$                                                          | <i>t</i> <sub>22</sub> CC | $20 + t_{\rm C}$             | -                          | 2TCL - 20<br>+ <i>t</i> <sub>C</sub>         | -                                    | ns   |

| Data hold after $\overline{WR}$                                                        | <i>t</i> <sub>24</sub> CC | 10 + <i>t</i> <sub>F</sub>   | -                          | TCL - 10<br>+ <i>t</i> <sub>F</sub>          | -                                    | ns   |

| ALE rising edge after RD, WR                                                           | <i>t</i> <sub>26</sub> CC | - 10 + <i>t</i> <sub>F</sub> | _                          | - 10 + <i>t</i> <sub>F</sub>                 | _                                    | ns   |

| Address hold after $\overline{WR}^{2)}$                                                | t <sub>28</sub> CC        | $0 + t_{F}$                  | _                          | $0 + t_{F}$                                  | _                                    | ns   |

| ALE falling edge to $\overline{CS}^{3)}$                                               | t <sub>38</sub> CC        | - 4 - t <sub>A</sub>         | 10 - <i>t</i> <sub>A</sub> | - 4 - t <sub>A</sub>                         | 10 - <i>t</i> <sub>A</sub>           | ns   |

| $\overline{\text{CS}}$ low to Valid Data In <sup>3)</sup>                              | <i>t</i> <sub>39</sub> SR | -                            | $40 + t_{C} + 2t_{A}$      | -                                            | $3TCL - 20 + t_C + 2t_A$             | ns   |

| $\overline{\text{CS}}$ hold after $\overline{\text{RD}}$ , $\overline{\text{WR}}^{3)}$ | <i>t</i> <sub>41</sub> CC | $6 + t_{F}$                  | -                          | TCL - 14<br>+ <i>t</i> <sub>F</sub>          | -                                    | ns   |

| ALE falling edge to<br>RdCS, WrCS (with RW-<br>delay)                                  | t <sub>42</sub> CC        | 16 + <i>t</i> <sub>A</sub>   | -                          | TCL - 4<br>+ <i>t</i> <sub>A</sub>           | -                                    | ns   |

| ALE falling edge to<br>RdCS, WrCS (no RW-<br>delay)                                    | t <sub>43</sub> CC        | $-4 + t_{A}$                 | -                          | -4<br>+ $t_A$                                | -                                    | ns   |

| RdCS to Valid Data In (with RW-delay)                                                  | <i>t</i> <sub>46</sub> SR | -                            | 16 + <i>t</i> <sub>C</sub> | -                                            | 2TCL - 24<br>+ <i>t</i> <sub>C</sub> | ns   |

| RdCS to Valid Data In (no RW-delay)                                                    | <i>t</i> <sub>47</sub> SR | -                            | $36 + t_{\rm C}$           | _                                            | 3TCL - 24<br>+ <i>t</i> <sub>C</sub> | ns   |

| RdCS, WrCS Low Time<br>(with RW-delay)                                                 | <i>t</i> <sub>48</sub> CC | $30 + t_{\rm C}$             | -                          | 2TCL - 10<br>+ <i>t</i> <sub>C</sub>         | -                                    | ns   |

| RdCS, WrCS Low Time<br>(no RW-delay)                                                   | <i>t</i> <sub>49</sub> CC | $50 + t_{\rm C}$             | -                          | 3TCL - 10<br>+ <i>t</i> <sub>C</sub>         | -                                    | ns   |

| Data valid to $\overline{WrCS}$                                                        | <i>t</i> <sub>50</sub> CC | $26 + t_{\rm C}$             | -                          | 2TCL - 14<br>+ <i>t</i> <sub>C</sub>         | -                                    | ns   |

| Data hold after RdCS                                                                   | <i>t</i> <sub>51</sub> SR | 0                            | —                          | 0                                            | —                                    | ns   |

# Demultiplexed Bus (Standard Supply Voltage Range) (cont'd)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (80 ns at 25 MHz CPU clock without waitstates)

| Parameter                                              | Symbol                    | Max. CPU Clock<br>= 25 MHz  |                            | Variable CPU Clock<br>1 / 2TCL = 1 to 25 MHz |                                   | Unit |

|--------------------------------------------------------|---------------------------|-----------------------------|----------------------------|----------------------------------------------|-----------------------------------|------|

|                                                        |                           | min.                        | max.                       | min.                                         | max.                              |      |

| Data float after RdCS<br>(with RW-delay) <sup>1)</sup> | <i>t</i> <sub>53</sub> SR | _                           | 20 + <i>t</i> <sub>F</sub> | -                                            | 2TCL - 20<br>+ $2t_A + t_F$<br>1) | ns   |

| Data float after RdCS<br>(no RW-delay) <sup>1)</sup>   | <i>t</i> <sub>68</sub> SR | -                           | 0 + <i>t</i> <sub>F</sub>  | -                                            | TCL - 20<br>+ $2t_A + t_F$<br>1)  | ns   |

| Address hold after<br>RdCS, WrCS                       | <i>t</i> <sub>55</sub> CC | - 6 + <i>t</i> <sub>F</sub> | -                          | - 6 + <i>t</i> <sub>F</sub>                  | -                                 | ns   |

| Data hold after WrCS                                   | <i>t</i> <sub>57</sub> CC | 6 + <i>t</i> <sub>F</sub>   | _                          | TCL - 14<br>+ <i>t</i> <sub>F</sub>          | _                                 | ns   |

<sup>1)</sup> RW-delay and  $t_A$  refer to the next following bus cycle (including an access to an on-chip X-Peripheral).

2) Read data are latched with the same clock edge that triggers the address change and the rising RD edge. Therefore address changes before the end of RD have no impact on read cycles.

<sup>3)</sup> These parameters refer to the latched chip select signals (CSxL). The early chip select signals (CSxE) are specified together with the address and signal BHE (see figures below).

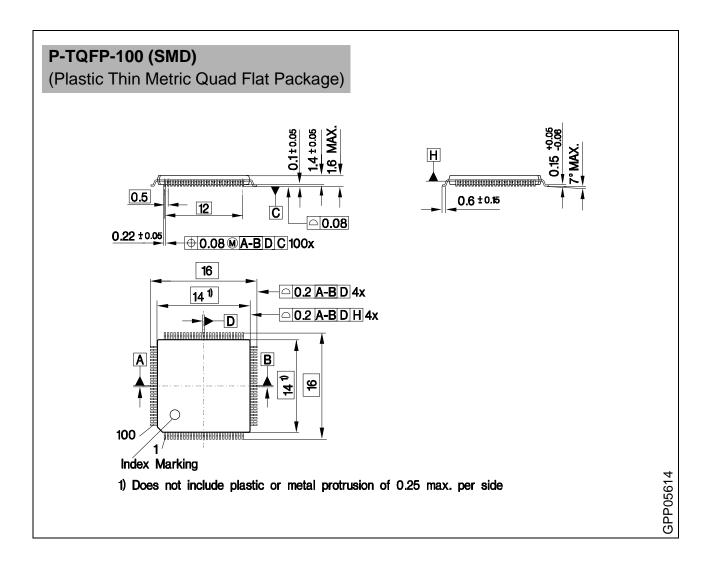

## Sorts of Packing Package outlines for tubes, trays etc. are contained in our Data Book "Package Information". SMD = Surface Mounted Device

Dimensions in mm