#### Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | C166                                                                      |

| Core Size                  | 16-Bit                                                                    |

| Speed                      | 20MHz                                                                     |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                  |

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 77                                                                        |

| Program Memory Size        | -                                                                         |

| Program Memory Type        | ROMIess                                                                   |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                               |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 100-BQFP                                                                  |

| Supplier Device Package    | P-MQFP-100                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/c165Imhafxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 16-Bit Single-Chip Microcontroller C166 Family

## C165

•

- High Performance 16-bit CPU with 4-Stage Pipeline

- 80 ns Instruction Cycle Time at 25 MHz CPU Clock

- 400 ns Multiplication (16  $\times$  16 bit), 800 ns Division (32 / 16 bit)

- Enhanced Boolean Bit Manipulation Facilities

- Additional Instructions to Support HLL and Operating Systems

- Register-Based Design with Multiple Variable Register Banks

- Single-Cycle Context Switching Support

- 16 MBytes Total Linear Address Space for Code and Data

- 1024 Bytes On-Chip Special Function Register Area

- 16-Priority-Level Interrupt System with 28 Sources, Sample-Rate down to 40 ns

- 8-Channel Interrupt-Driven Single-Cycle Data Transfer Facilities via Peripheral Event Controller (PEC)

- Clock Generation via prescaler or via direct clock input

- On-Chip Memory Modules

- 2 KBytes On-Chip Internal RAM (IRAM)

- On-Chip Peripheral Modules

- Two Multi-Functional General Purpose Timer Units with 5 Timers

- Two Serial Channels (Synchronous/Asynchronous and High-Speed-Synchronous)

- Up to 16 MBytes External Address Space for Code and Data

- Programmable External Bus Characteristics for Different Address Ranges

- Multiplexed or Demultiplexed External Address/Data Buses with 8-Bit or 16-Bit Data Bus Width

- Five Programmable Chip-Select Signals

- Hold- and Hold-Acknowledge Bus Arbitration Support

- Idle and Power Down Modes

- Programmable Watchdog Timer

- Up to 77 General Purpose I/O Lines, partly with Selectable Input Thresholds and Hysteresis

- Power Supply: the C165 can operate from a 5 V or a 3 V power supply

- Supported by a Large Range of Development Tools like C-Compilers, Macro-Assembler Packages, Emulators, Evaluation Boards, HLL-Debuggers, Simulators, Logic Analyzer Disassemblers, Programming Boards

- On-Chip Bootstrap Loader

- 100-Pin MQFP Package (0.65 mm pitch)

- 100-Pin TQFP Package (0.5 mm pitch)

C165

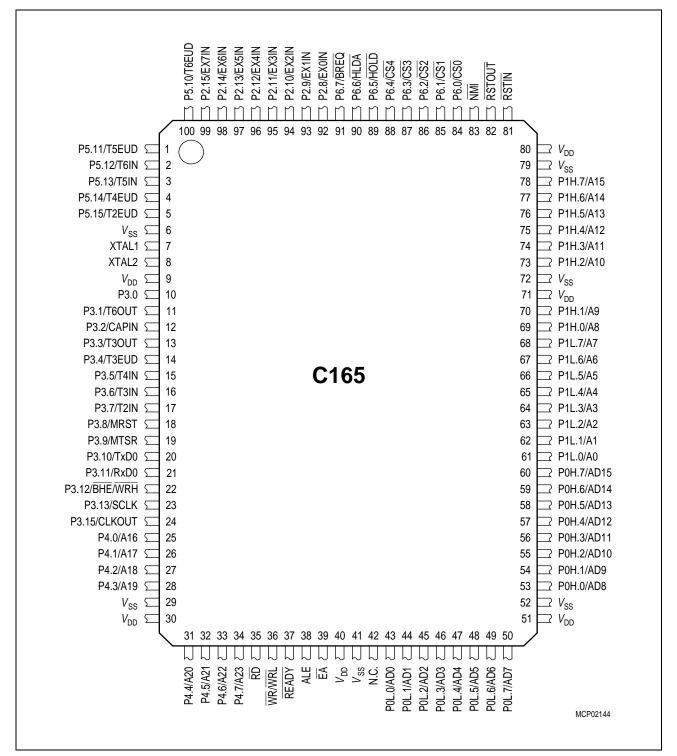

#### Pin Configuration MQFP Package

(top view)

#### Figure 3

# Table 2Pin Definitions and Functions (cont'd)

| Symbol                  | Pin Nr<br>TQFP  | Pin Nr<br>MQFP  | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    |                 |  |  |  |

|-------------------------|-----------------|-----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------|--|--|--|

| NC                      | 40              | 42              | -              | This pin is not conn<br>No connection to th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |                 |  |  |  |

| <b>PORT0</b><br>P0L.0-7 | 41-48           | 43-50           | IO             | PORT0 consists of<br>ports P0L and P0H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . It is bit-wise p | rogrammable for |  |  |  |

| P0H.0-7                 | 51-58           | 53-60           |                | input or output via direction bits. For a pin configured<br>as input, the output driver is put into high-impedance<br>state. In case of an external bus configuration,<br>PORT0 serves as the address (A) and address/data<br>(AD) bus in multiplexed bus modes and as the data<br>(D) bus in demultiplexed bus modes.<br><b>Demultiplexed bus modes:</b><br>Data Path Width: 8-bit 16-bit<br>POL.0 – POL.7: $DO - D7$ $DO - D7$<br>POH.0 – POH.7: $I/O$ $D8 - D15$<br><b>Multiplexed bus modes:</b><br>Data Path Width: 8-bit 16-bit<br>POL.0 – POL.7: $ADO - AD7$ $ADO - AD7$ |                    |                 |  |  |  |

| <b>PORT1</b><br>P1L.0-7 | 59-66           | 61-68           | 10             | PORT1 consists of the two 8-bit bidirectional I/O<br>ports P1L and P1H. It is bit-wise programmable for<br>input or output via direction bits. For a pin configured<br>as input, the output driver is put into high-impedance<br>state. PORT1 is used as the 16-bit address bus (A)<br>in demultiplexed bus modes and also after switching<br>from a demultiplexed bus mode to a multiplexed bus<br>mode.                                                                                                                                                                       |                    |                 |  |  |  |

| P1H.0-7                 | 67,68,<br>71-76 | 69-70,<br>73-78 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    |                 |  |  |  |

| Table 2 | Pin Definitions and Functions (cont'd) |

|---------|----------------------------------------|

|         |                                        |

| Symbol     | Pin Nr<br>TQFP | Pin Nr<br>MQFP | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|----------------|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSTIN      | 79             | 81             | Ι/Ο            | Reset Input with Schmitt-Trigger characteristics. A<br>low level at this pin while the oscillator is running<br>resets the C165. An internal pullup resistor permits<br>power-on reset using only a capacitor connected to<br>$V_{SS}$ . A spike filter suppresses input pulses < 10 ns.<br>Input pulses >100 ns safely pass the filter. The<br>minimum duration for a safe recognition should be<br>100 ns + 2 CPU clock cycles.<br>In bidirectional reset mode (enabled by setting bit<br>BDRSTEN in register SYSCON) the RSTIN line is<br>internally pulled low for the duration of the internal<br>reset sequence upon any reset (HW, SW, WDT).<br>See note below this table. |

|            |                |                |                | Note: To let the reset configuration of PORT0 settle a reset duration of ca. 1 ms is recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RST<br>OUT | 80             | 82             | 0              | Internal Reset Indication Output. This pin is set to a<br>low level when the part is executing either a<br>hardware-, a software- or a watchdog timer reset.<br>RSTOUT remains low until the EINIT (end of<br>initialization) instruction is executed.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| NMI        | 81             | 83             | 1              | Non-Maskable Interrupt Input. A high to low<br>transition at this pin causes the CPU to vector to the<br>NMI trap routine. When the PWRDN (power down)<br>instruction is executed, the NMI pin must be low in<br>order to force the C165 to go into power down mode.<br>If NMI is high, when PWRDN is executed, the part<br>will continue to run in normal mode.<br>If not used, pin NMI should be pulled high externally.                                                                                                                                                                                                                                                        |

| Table 2 | Pin Definitions and Functions ( | (cont'd | ) |

|---------|---------------------------------|---------|---|

|         |                                 | Comu    | / |

| Symbol                                                             | Pin Nr<br>TQFP                               | Pin Nr<br>MQFP                               | Input<br>Outp.              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P6                                                                 |                                              |                                              | IO                          | Port 6 is an 8-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits.<br>For a pin configured as input, the output driver is put<br>into high-impedance state. Port 6 outputs can be<br>configured as push/pull or open drain drivers.<br>The Port 6 pins also serve for alternate functions:                                                                                                                                                                                                                                                                                                                    |

| P6.0                                                               | 82                                           | 84                                           | 0                           | CS0 Chip Select 0 Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P6.1                                                               | 83                                           | 85                                           | 0                           | CS1 Chip Select 1 Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P6.2                                                               | 84                                           | 86                                           | 0                           | CS2 Chip Select 2 Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P6.3                                                               | 85                                           | 87                                           | 0                           | CS3 Chip Select 3 Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P6.4                                                               | 86                                           | 88                                           | 0                           | CS4 Chip Select 4 Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P6.5                                                               | 87                                           | 89                                           | 1                           | HOLD External Master Hold Request Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P6.6                                                               | 88                                           | 90                                           | I/O                         | HLDAHold Acknowledge Outp.(master mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                    |                                              |                                              |                             | or Input (slave mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P6.7                                                               | 89                                           | 91                                           | 0                           | BREQ Bus Request Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P2.8<br>P2.9<br>P2.10<br>P2.11<br>P2.12<br>P2.13<br>P2.14<br>P2.15 | 90<br>91<br>92<br>93<br>94<br>95<br>96<br>97 | 92<br>93<br>94<br>95<br>96<br>97<br>98<br>99 | IO<br>I<br>I<br>I<br>I<br>I | Port 2 is an 8-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits.For a pin configured as input, the output driver is put<br>into high-impedance state. Port 2 outputs can be<br>configured as push/pull or open drain drivers. The<br>following Port 2 pins serve for alternate functions:EX0INFast External Interrupt 0 Input<br>EX1INEX2INFast External Interrupt 1 Input<br>EX2INEX3INFast External Interrupt 2 Input<br>EX3INEX4INFast External Interrupt 3 Input<br>EX4INEX4INFast External Interrupt 4 Input<br>EX5INEX6INFast External Interrupt 5 Input<br>EX6INEX6INFast External Interrupt 6 Input |

| P5                                                                 |                                              |                                              |                             | Port 5 is a 6-bit input-only port with Schmitt-Trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P5.10                                                              | 98                                           | 100                                          |                             | char. The pins of Port 5 also serve as timer inputs:<br>T6EUD GPT2 Timer T6 Ext. Up/Down Ctrl Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P5.11                                                              | 99                                           | 1                                            |                             | T5EUD GPT2 Timer T5 Ext. Up/Down Ctrl Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| P5.12                                                              | 100                                          | 2                                            |                             | T6IN GPT2 Timer T6 Count Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| P5.13                                                              | 1                                            | 3                                            |                             | T5IN GPT2 Timer T5 Count Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| P5.14                                                              | 2                                            | 4                                            |                             | T4EUD GPT1 Timer T4 Ext. Up/Down Ctrl Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| P5.15                                                              | 3                                            | 5                                            |                             | T2EUD GPT1 Timer T2 Ext. Up/Down Ctrl Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### **Functional Description**

The architecture of the C165 combines advantages of both RISC and CISC processors and of advanced peripheral subsystems in a very well-balanced way. In addition the on-chip memory blocks allow the design of compact systems with maximum performance.

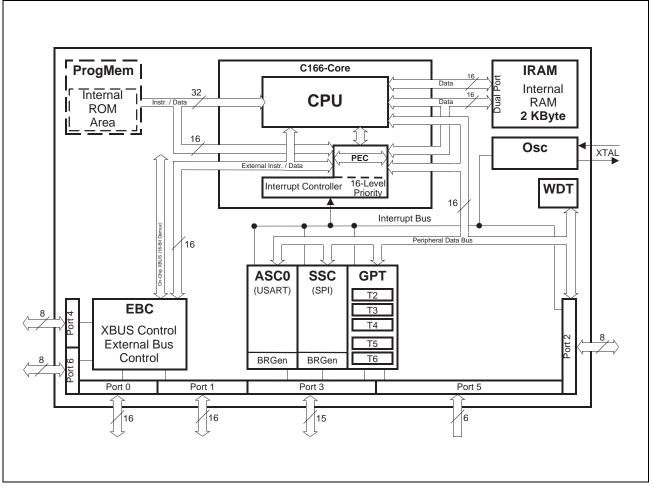

The following block diagram gives an overview of the different on-chip components and of the advanced, high bandwidth internal bus structure of the C165.

Note: All time specifications refer to a CPU clock of 25 MHz (see definition in the AC Characteristics section).

#### Figure 4 Block Diagram

The program memory, the internal RAM (IRAM) and the set of generic peripherals are connected to the CPU via separate buses. A fourth bus, the XBUS, connects external resources as well as additional on-chip resources, the X-Peripherals (see Figure 4).

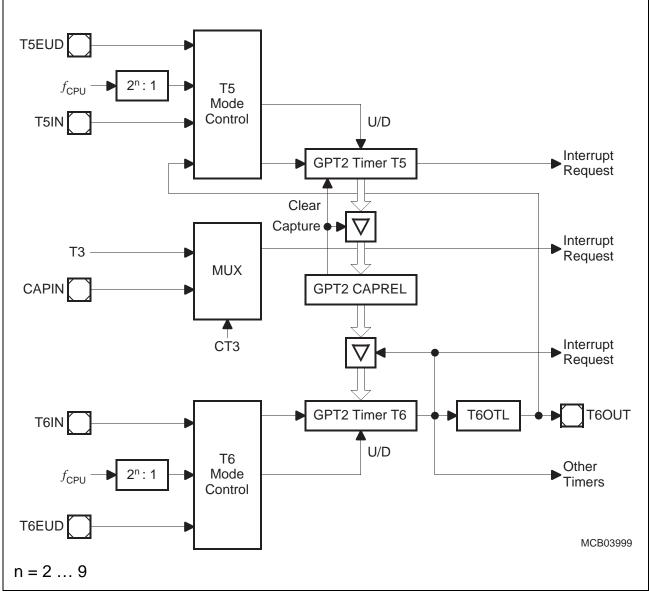

#### **General Purpose Timer (GPT) Unit**

The GPT unit represents a very flexible multifunctional timer/counter structure which may be used for many different time related tasks such as event timing and counting, pulse width and duty cycle measurements, pulse generation, or pulse multiplication.

The GPT unit incorporates five 16-bit timers which are organized in two separate modules, GPT1 and GPT2. Each timer in each module may operate independently in a number of different modes, or may be concatenated with another timer of the same module.

Each of the three timers T2, T3, T4 of **module GPT1** can be configured individually for one of four basic modes of operation, which are Timer, Gated Timer, Counter, and Incremental Interface Mode. In Timer Mode, the input clock for a timer is derived from the CPU clock, divided by a programmable prescaler, while Counter Mode allows a timer to be clocked in reference to external events.

Pulse width or duty cycle measurement is supported in Gated Timer Mode, where the operation of a timer is controlled by the 'gate' level on an external input pin. For these purposes, each timer has one associated port pin (TxIN) which serves as gate or clock input. The maximum resolution of the timers in module GPT1 is 16 TCL.

The count direction (up/down) for each timer is programmable by software or may additionally be altered dynamically by an external signal on a port pin (TxEUD) to facilitate e.g. position tracking.

In Incremental Interface Mode the GPT1 timers (T2, T3, T4) can be directly connected to the incremental position sensor signals A and B via their respective inputs TxIN and TxEUD. Direction and count signals are internally derived from these two input signals, so the contents of the respective timer Tx corresponds to the sensor position. The third position sensor signal TOP0 can be connected to an interrupt input.

Timer T3 has an output toggle latch (T3OTL) which changes its state on each timer overflow/underflow. The state of this latch may be output on pin T3OUT e.g. for time out monitoring of external hardware components, or may be used internally to clock timers T2 and T4 for measuring long time periods with high resolution.

In addition to their basic operating modes, timers T2 and T4 may be configured as reload or capture registers for timer T3. When used as capture or reload registers, timers T2 and T4 are stopped. The contents of timer T3 is captured into T2 or T4 in response to a signal at their associated input pins (TxIN). Timer T3 is reloaded with the contents of T2 or T4 triggered either by an external signal or by a selectable state transition of its toggle latch T3OTL. When both T2 and T4 are configured to alternately reload T3 on opposite state transitions of T3OTL with the low and high times of a PWM signal, this signal can be constantly generated without software intervention.

The capture trigger (timer T5 to CAPREL) may also be generated upon transitions of GPT1 timer T3's inputs T3IN and/or T3EUD. This is especially advantageous when T3 operates in Incremental Interface Mode.

#### Parameter Interpretation

The parameters listed in the following partly represent the characteristics of the C165 and partly its demands on the system. To aid in interpreting the parameters right, when evaluating them for a design, they are marked in column "Symbol":

CC (Controller Characteristics):

The logic of the C165 will provide signals with the respective timing characteristics.

**SR** (System Requirement):

The external system must provide signals with the respective timing characteristics to the C165.

#### DC Characteristics (Standard Supply Voltage Range)

(Operating Conditions apply)<sup>1)</sup>

| Parameter                                                                                          | Symbol                          | Limit '                      | Values                       | Unit | <b>Test Condition</b>                           |  |

|----------------------------------------------------------------------------------------------------|---------------------------------|------------------------------|------------------------------|------|-------------------------------------------------|--|

|                                                                                                    |                                 | min.                         | max.                         |      |                                                 |  |

| Input low voltage (TTL,<br>all except XTAL1)                                                       | V <sub>IL</sub> SR              | - 0.5                        | 0.2 V <sub>DD</sub><br>- 0.1 | V    | _                                               |  |

| Input low voltage XTAL1                                                                            | $V_{IL2}$ SR                    | - 0.5                        | 0.3 V <sub>DD</sub>          | V    | -                                               |  |

| Input high voltage (TTL,<br>all except RSTIN and XTAL1)                                            | V <sub>IH</sub> SR              | 0.2 V <sub>DD</sub><br>+ 0.9 | V <sub>DD</sub> + 0.5        | V    | _                                               |  |

| Input high voltage RSTIN<br>(when operated as input)                                               | V <sub>IH1</sub> SR             | 0.6 V <sub>DD</sub>          | V <sub>DD</sub> + 0.5        | V    | _                                               |  |

| Input high voltage XTAL1                                                                           | V <sub>IH2</sub> SR             | 0.7 V <sub>DD</sub>          | V <sub>DD</sub> +<br>0.5     | V    | _                                               |  |

| Output low voltage<br>(PORT0, PORT1, Port 4, ALE,<br>RD, WR, BHE, RSTOUT,<br>RSTIN <sup>2)</sup> ) | V <sub>OL</sub> CC              | -                            | 0.45                         | V    | I <sub>OL</sub> = 2.4 mA                        |  |

| Output low voltage<br>(all other outputs)                                                          | V <sub>OL1</sub> CC             | _                            | 0.45                         | V    | <i>I</i> <sub>OL</sub> = 1.6 mA                 |  |

| Output high voltage <sup>3)</sup>                                                                  | V <sub>OH</sub> CC              | 2.4                          | _                            | V    | I <sub>OH</sub> = - 2.4 mA                      |  |

| (PORT0, PORT1, Port 4, ALE,<br>RD, WR, BHE, RSTOUT)                                                |                                 | 0.9 V <sub>DD</sub>          | _                            | V    | I <sub>OH</sub> = - 0.5 mA                      |  |

| Output high voltage <sup>3)</sup>                                                                  | V <sub>OH1</sub> CC             | 2.4                          | _                            | V    | I <sub>OH</sub> = - 1.6 mA                      |  |

| (all other outputs)                                                                                |                                 | 0.9 V <sub>DD</sub>          | _                            | V    | I <sub>OH</sub> = - 0.5 mA                      |  |

| Input leakage current (Port 5)                                                                     | I <sub>OZ1</sub> CC             | -                            | ± 200                        | nA   | $0 V < V_{IN} < V_{DD}$                         |  |

| Input leakage current (all other)                                                                  | I <sub>OZ2</sub> CC             | _                            | ± 500                        | nA   | $0.45 \text{ V} < V_{\text{IN}} < V_{\text{E}}$ |  |

| RSTIN inactive current <sup>4)</sup>                                                               | I <sub>RSTH</sub> <sup>5)</sup> | _                            | - 10                         | μA   | $V_{\rm IN} = V_{\rm IH1}$                      |  |

# **DC Characteristics (Reduced Supply Voltage Range)** (Operating Conditions apply)<sup>1)</sup>

| Parameter                                                                                          | Symbol                          | Limit               | Values                   | Unit | Test Condition                                   |  |

|----------------------------------------------------------------------------------------------------|---------------------------------|---------------------|--------------------------|------|--------------------------------------------------|--|

|                                                                                                    |                                 | min.                | max.                     |      |                                                  |  |

| Input low voltage (TTL,<br>all except XTAL1)                                                       | V <sub>IL</sub> SR              | - 0.5               | 0.8                      | V    | -                                                |  |

| Input low voltage XTAL1                                                                            | $V_{IL2}$ SR                    | - 0.5               | 0.3 V <sub>DD</sub>      | V    | -                                                |  |

| Input high voltage (TTL, all except RSTIN and XTAL1)                                               | V <sub>IH</sub> SR              | 1.8                 | V <sub>DD</sub> + 0.5    | V    | _                                                |  |

| Input high voltage RSTIN (when operated as input)                                                  | V <sub>IH1</sub> SR             | 0.6 V <sub>DD</sub> | V <sub>DD</sub> + 0.5    | V    | _                                                |  |

| Input high voltage XTAL1                                                                           | V <sub>IH2</sub> SR             | 0.7 V <sub>DD</sub> | V <sub>DD</sub> +<br>0.5 | V    | _                                                |  |

| Output low voltage<br>(PORT0, PORT1, Port 4, ALE,<br>RD, WR, BHE, RSTOUT,<br>RSTIN <sup>2)</sup> ) | V <sub>OL</sub> CC              | -                   | 0.45                     | V    | I <sub>OL</sub> = 1.6 mA                         |  |

| Output low voltage<br>(all other outputs)                                                          | V <sub>OL1</sub> CC             | -                   | 0.45                     | V    | <i>I</i> <sub>OL</sub> = 1.0 mA                  |  |

| Output high voltage <sup>3)</sup><br>(PORT0, PORT1, Port 4, ALE,<br>RD, WR, BHE, RSTOUT)           | V <sub>OH</sub> CC              | 0.9 V <sub>DD</sub> | _                        | V    | I <sub>OH</sub> = - 0.5 mA                       |  |

| Output high voltage <sup>3)</sup><br>(all other outputs)                                           | V <sub>OH1</sub> CC             | 0.9 V <sub>DD</sub> | _                        | V    | I <sub>OH</sub> = - 0.25 mA                      |  |

| Input leakage current (Port 5)                                                                     | I <sub>OZ1</sub> CC             | -                   | ± 200                    | nA   | $0 V < V_{IN} < V_{DD}$                          |  |

| Input leakage current (all other)                                                                  | I <sub>OZ2</sub> CC             | -                   | ± 500                    | nA   | $0.45 \text{ V} < V_{\text{IN}} < V_{\text{DD}}$ |  |

| RSTIN inactive current <sup>4)</sup>                                                               | I <sub>RSTH</sub> <sup>5)</sup> | -                   | - 10                     | μA   | $V_{\rm IN} = V_{\rm IH1}$                       |  |

| RSTIN active current <sup>4)</sup>                                                                 | I <sub>RSTL</sub> <sup>6)</sup> | - 100               | -                        | μA   | $V_{\rm IN} = V_{\rm IL}$                        |  |

| READY/RD/WR inact. current <sup>7)</sup>                                                           | $I_{\rm RWH}^{5)}$              | -                   | - 10                     | μA   | $V_{OUT}$ = 2.4 V                                |  |

| READY/RD/WR active current <sup>7)</sup>                                                           |                                 | - 500               | _                        | μΑ   | $V_{OUT} = V_{OLmax}$                            |  |

| ALE inactive current <sup>7)</sup>                                                                 | $I_{ALEL}^{(5)}$                | -                   | 20                       | μA   | $V_{OUT} = V_{OLmax}$                            |  |

| ALE active current <sup>7)</sup>                                                                   | $I_{ALEH}^{6)}$                 | 500                 | _                        | μA   | $V_{\rm OUT}$ = 2.4 V                            |  |

| Port 6 inactive current <sup>7)</sup>                                                              | I <sub>P6H</sub> <sup>5)</sup>  | _                   | - 10                     | μA   | $V_{\rm OUT}$ = 2.4 V                            |  |

| Port 6 active current <sup>7)</sup>                                                                | I <sub>P6L</sub> <sup>6)</sup>  | - 500               | -                        | μA   | $V_{OUT} = V_{OL1max}$                           |  |

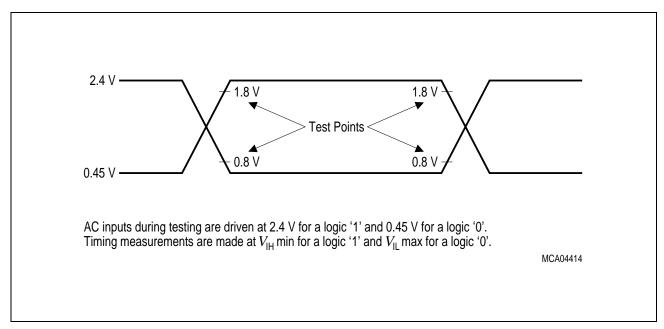

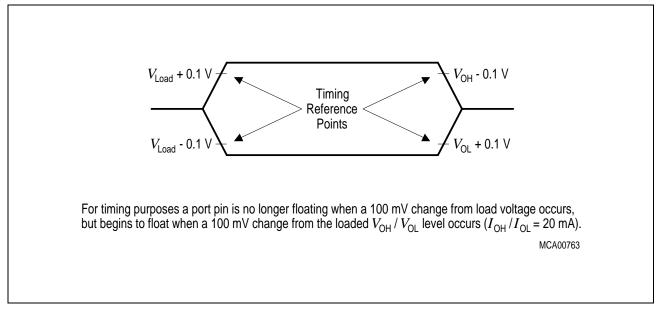

#### **Testing Waveforms**

Figure 11 Input Output Waveforms

Figure 12 Float Waveforms

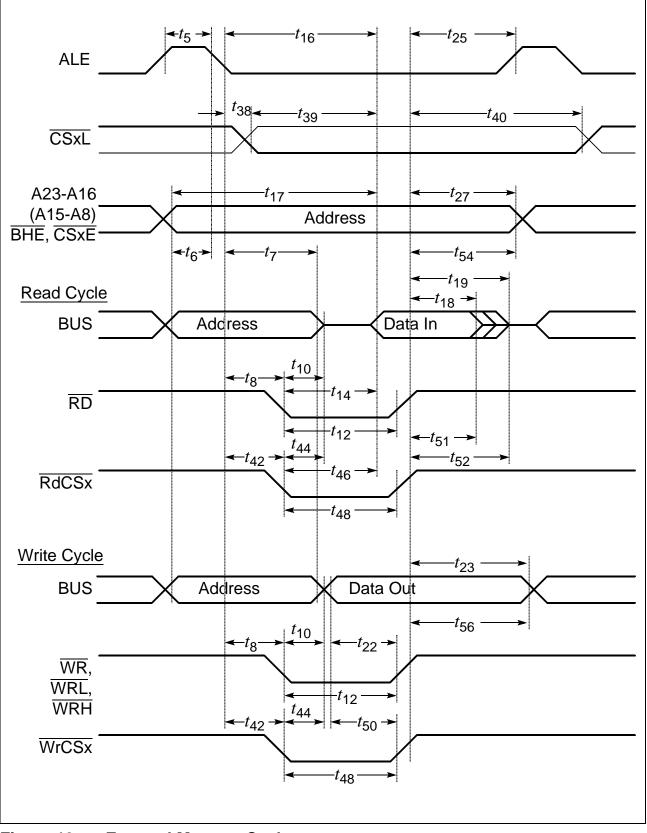

# Multiplexed Bus (Standard Supply Voltage Range) (cont'd)

(Operating Conditions apply)

ALE cycle time = 6 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (120 ns at 25 MHz CPU clock without waitstates)

| Parameter                                         | Symbol                    |                            | Max. CPU Clock<br>= 25 MHz |                                      | Variable CPU Clock<br>1 / 2TCL = 1 to 25 MHz |    |  |

|---------------------------------------------------|---------------------------|----------------------------|----------------------------|--------------------------------------|----------------------------------------------|----|--|

|                                                   |                           | min.                       | max.                       | min.                                 | max.                                         |    |  |

| Address float after RdCS,<br>WrCS (with RW delay) | <i>t</i> <sub>44</sub> CC | -                          | 0                          | -                                    | 0                                            | ns |  |

| Address float after RdCS,<br>WrCS (no RW delay)   | <i>t</i> <sub>45</sub> CC | -                          | 20                         | -                                    | TCL                                          | ns |  |

| RdCS to Valid Data In (with RW delay)             | <i>t</i> <sub>46</sub> SR | -                          | 16 + <i>t</i> <sub>C</sub> | _                                    | 2TCL - 24<br>+ <i>t</i> <sub>C</sub>         | ns |  |

| RdCS to Valid Data In (no RW delay)               | <i>t</i> <sub>47</sub> SR | -                          | $36 + t_{\rm C}$           | _                                    | 3TCL - 24<br>+ <i>t</i> <sub>C</sub>         | ns |  |

| RdCS, WrCS Low Time<br>(with RW delay)            | <i>t</i> <sub>48</sub> CC | $30 + t_{\rm C}$           | -                          | 2TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                            | ns |  |

| RdCS, WrCS Low Time<br>(no RW delay)              | <i>t</i> <sub>49</sub> CC | 50 + <i>t</i> <sub>C</sub> | -                          | 3TCL - 10<br>+ <i>t</i> <sub>C</sub> | _                                            | ns |  |

| Data valid to WrCS                                | <i>t</i> <sub>50</sub> CC | $26 + t_{\rm C}$           | -                          | 2TCL - 14<br>+ <i>t</i> <sub>C</sub> | _                                            | ns |  |

| Data hold after RdCS                              | <i>t</i> <sub>51</sub> SR | 0                          | -                          | 0                                    | -                                            | ns |  |

| Data float after RdCS                             | <i>t</i> <sub>52</sub> SR | -                          | 20 + $t_{\rm F}$           | -                                    | 2TCL - 20<br>+ <i>t</i> <sub>F</sub>         | ns |  |

| Address hold after<br>RdCS, WrCS                  | <i>t</i> <sub>54</sub> CC | 20 + <i>t</i> <sub>F</sub> | -                          | 2TCL - 20<br>+ <i>t</i> <sub>F</sub> | -                                            | ns |  |

| Data hold after WrCS                              | <i>t</i> <sub>56</sub> CC | 20 + <i>t</i> <sub>F</sub> | -                          | 2TCL - 20<br>+ <i>t</i> <sub>F</sub> | -                                            | ns |  |

<sup>1)</sup> These parameters refer to the latched chip select signals (CSxL). The early chip select signals (CSxE) are specified together with the address and signal BHE (see figures below).

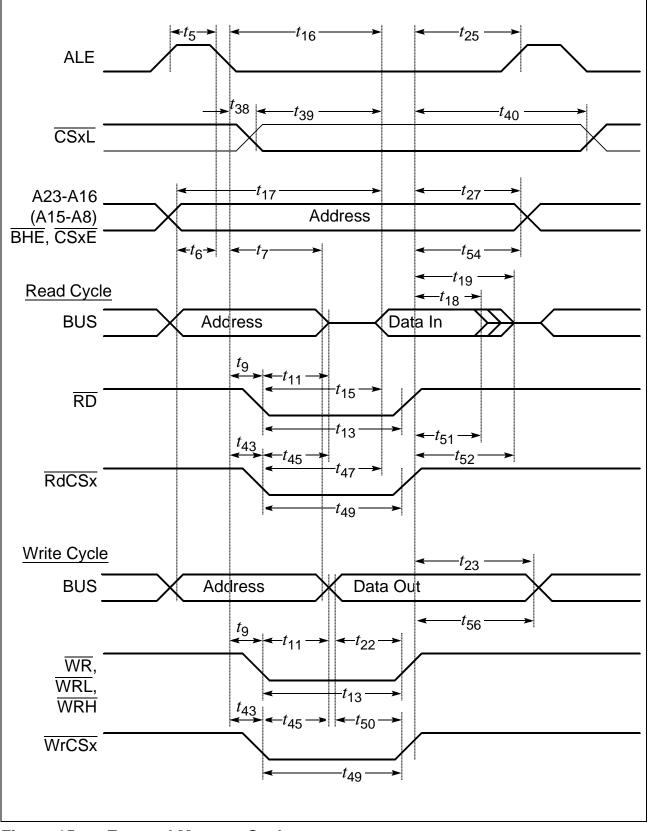

Figure 13 External Memory Cycle: Multiplexed Bus, With Read/Write Delay, Normal ALE

Figure 14 External Memory Cycle: Multiplexed Bus, With Read/Write Delay, Extended ALE

Figure 15 External Memory Cycle: Multiplexed Bus, No Read/Write Delay, Normal ALE

### **AC Characteristics**

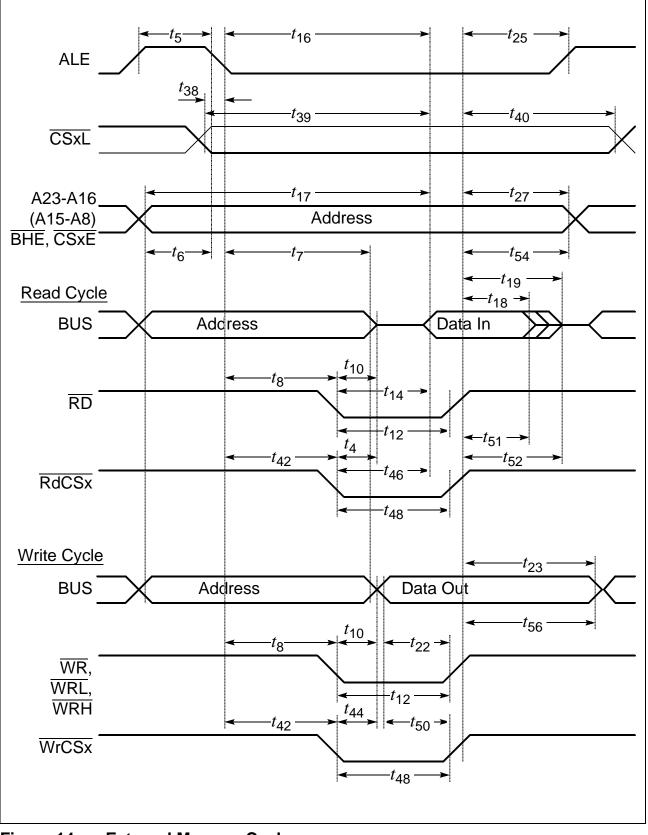

# Demultiplexed Bus (Standard Supply Voltage Range)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (80 ns at 25 MHz CPU clock without waitstates)

| Parameter                                                                   |                        | nbol |                  | Max. CPU Clock<br>= 25 MHz |                                      | Variable CPU Clock<br>1 / 2TCL = 1 to 25 MHz                 |    |  |

|-----------------------------------------------------------------------------|------------------------|------|------------------|----------------------------|--------------------------------------|--------------------------------------------------------------|----|--|

|                                                                             |                        |      | min.             | max.                       | min.                                 | max.                                                         |    |  |

| ALE high time                                                               | <i>t</i> 5             | CC   | $10 + t_{A}$     | -                          | TCL - 10<br>+ <i>t</i> <sub>A</sub>  | _                                                            | ns |  |

| Address setup to ALE                                                        | <i>t</i> <sub>6</sub>  | CC   | $4 + t_A$        | _                          | TCL - 16<br>+ <i>t</i> <sub>A</sub>  | -                                                            | ns |  |

| ALE falling edge to $\overline{RD}$ ,<br>WR (with RW-delay)                 | <i>t</i> 8             | CC   | $10 + t_{A}$     | _                          | TCL - 10<br>+ <i>t</i> <sub>A</sub>  | -                                                            | ns |  |

| ALE falling edge to $\overline{RD}$ ,<br>WR (no RW-delay)                   | t <sub>9</sub>         | CC   | $-10 + t_A$      | _                          | - 10<br>+ <i>t</i> <sub>A</sub>      | -                                                            | ns |  |

| RD, WR low time<br>(with RW-delay)                                          | t <sub>12</sub>        | CC   | $30 + t_{\rm C}$ | _                          | 2TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                                            | ns |  |

| RD, WR low time<br>(no RW-delay)                                            | t <sub>13</sub>        | CC   | $50 + t_{\rm C}$ | _                          | 3TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                                            | ns |  |

| RD to valid data in (with RW-delay)                                         | <i>t</i> <sub>14</sub> | SR   | _                | $20 + t_{\rm C}$           | -                                    | 2TCL - 20<br>+ <i>t</i> <sub>C</sub>                         | ns |  |

| RD to valid data in (no RW-delay)                                           | t <sub>15</sub>        | SR   | _                | $40 + t_{\rm C}$           | _                                    | 3TCL - 20<br>+ <i>t</i> <sub>C</sub>                         | ns |  |

| ALE low to valid data in                                                    | t <sub>16</sub>        | SR   | _                | $40 + t_{A} + t_{C}$       | _                                    | 3TCL - 20<br>+ <i>t</i> <sub>A</sub> + <i>t</i> <sub>C</sub> | ns |  |

| Address to valid data in                                                    | t <sub>17</sub>        | SR   | _                | $50 + 2t_A + t_C$          | _                                    | $4TCL - 30 + 2t_A + t_C$                                     | ns |  |

| Data hold after RD rising edge                                              | t <sub>18</sub>        | SR   | 0                | _                          | 0                                    | -                                                            | ns |  |

| Data float after $\overline{RD}$ rising edge (with RW-delay <sup>1)</sup> ) | <i>t</i> <sub>20</sub> | SR   | -                | $26 + 2t_A + t_F^{(1)}$    | -                                    | 2TCL - 14<br>+ $22t_A$<br>+ $t_F^{(1)}$                      | ns |  |

| Data float after RD rising edge (no RW-delay <sup>1)</sup> )                | t <sub>21</sub>        | SR   | -                | $10 + 2t_A + t_F^{(1)}$    | -                                    | TCL - 10<br>+ $22t_A$<br>+ $t_F^{(1)}$                       | ns |  |

### **AC Characteristics**

#### Demultiplexed Bus (Reduced Supply Voltage Range)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (100 ns at 20 MHz CPU clock without waitstates)

| Parameter                                                                   |                        | nbol | Max. CPU Clock<br>= 20 MHz   |                            | Variable (<br>1 / 2TCL =             | Unit                                                                             |    |

|-----------------------------------------------------------------------------|------------------------|------|------------------------------|----------------------------|--------------------------------------|----------------------------------------------------------------------------------|----|

|                                                                             |                        |      | min.                         | max.                       | min.                                 | max.                                                                             |    |

| ALE high time                                                               | <i>t</i> <sub>5</sub>  | CC   | $11 + t_A$                   | -                          | TCL - 14<br>+ <i>t</i> <sub>A</sub>  | _                                                                                | ns |

| Address setup to ALE                                                        | <i>t</i> <sub>6</sub>  | CC   | $5 + t_{A}$                  | _                          | TCL - 20<br>+ <i>t</i> <sub>A</sub>  | -                                                                                | ns |

| ALE falling edge to $\overline{RD}$ ,<br>WR (with RW-delay)                 | <i>t</i> 8             | CC   | $15 + t_{A}$                 | _                          | TCL - 10<br>+ <i>t</i> <sub>A</sub>  | -                                                                                | ns |

| ALE falling edge to RD,<br>WR (no RW-delay)                                 | t <sub>9</sub>         | CC   | - 10 + <i>t</i> <sub>A</sub> | _                          | - 10<br>+ <i>t</i> <sub>A</sub>      | -                                                                                | ns |

| RD, WR low time<br>(with RW-delay)                                          | <i>t</i> <sub>12</sub> | CC   | $34 + t_{\rm C}$             | _                          | 2TCL - 16<br>+ <i>t</i> <sub>C</sub> | -                                                                                | ns |

| RD, WR low time<br>(no RW-delay)                                            | <i>t</i> <sub>13</sub> | CC   | 59 + t <sub>C</sub>          | -                          | 3TCL - 16<br>+ <i>t</i> <sub>C</sub> | -                                                                                | ns |

| RD to valid data in (with RW-delay)                                         | <i>t</i> <sub>14</sub> | SR   | _                            | 22 + t <sub>C</sub>        | -                                    | 2TCL - 28<br>+ <i>t</i> <sub>C</sub>                                             | ns |

| RD to valid data in (no RW-delay)                                           | t <sub>15</sub>        | SR   | _                            | 47 + <i>t</i> <sub>C</sub> | _                                    | 3TCL - 28<br>+ <i>t</i> <sub>C</sub>                                             | ns |

| ALE low to valid data in                                                    | <i>t</i> <sub>16</sub> | SR   | _                            | $45 + t_A + t_C$           | _                                    | $\begin{array}{c} \text{3TCL} - 30 \\ + t_{\text{A}} + t_{\text{C}} \end{array}$ | ns |

| Address to valid data in                                                    | <i>t</i> <sub>17</sub> | SR   | _                            | 57 + $2t_{A} + t_{C}$      | _                                    | $4TCL - 43 + 2t_A + t_C$                                                         | ns |

| Data hold after RD rising edge                                              | t <sub>18</sub>        | SR   | 0                            | _                          | 0                                    | -                                                                                | ns |

| Data float after $\overline{RD}$ rising edge (with RW-delay <sup>1)</sup> ) | <i>t</i> <sub>20</sub> | SR   | _                            | $36 + 2t_A + t_F^{(1)}$    | -                                    | 2TCL - 14<br>+ $22t_A$<br>+ $t_F^{(1)}$                                          | ns |

| Data float after RD rising edge (no RW-delay <sup>1)</sup> )                | <i>t</i> <sub>21</sub> | SR   | _                            | $15 + 2t_A + t_F^{(1)}$    | -                                    | TCL - 10<br>+ $22t_A$<br>+ $t_F^{(1)}$                                           | ns |

# Demultiplexed Bus (Reduced Supply Voltage Range) (cont'd)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (100 ns at 20 MHz CPU clock without waitstates)

| Parameter                                              | Symbol                 |    |                              | PU Clock<br>) MHz         | Variable (<br>1 / 2TCL =            | Unit                              |    |

|--------------------------------------------------------|------------------------|----|------------------------------|---------------------------|-------------------------------------|-----------------------------------|----|

|                                                        |                        |    | min.                         | max.                      | min.                                | max.                              |    |

| Data float after RdCS<br>(with RW-delay) <sup>1)</sup> | t <sub>53</sub>        | SR | _                            | $30 + t_{\rm F}$          | -                                   | 2TCL - 20<br>+ $2t_A + t_F$<br>1) | ns |

| Data float after RdCS<br>(no RW-delay) <sup>1)</sup>   | t <sub>68</sub>        | SR | -                            | 5 + <i>t</i> <sub>F</sub> | -                                   | TCL - 20<br>+ $2t_A + t_F$<br>1)  | ns |

| Address hold after<br>RdCS, WrCS                       | <i>t</i> <sub>55</sub> | CC | - 16 + <i>t</i> <sub>F</sub> | -                         | - 16 + <i>t</i> <sub>F</sub>        | -                                 | ns |

| Data hold after WrCS                                   | t <sub>57</sub>        | CC | 9 + <i>t</i> <sub>F</sub>    | _                         | TCL - 16<br>+ <i>t</i> <sub>F</sub> | _                                 | ns |

<sup>1)</sup> RW-delay and  $t_A$  refer to the next following bus cycle (including an access to an on-chip X-Peripheral).

<sup>2)</sup> Read data are latched with the same clock edge that triggers the address change and the rising RD edge. Therefore address changes before the end of RD have no impact on read cycles.

<sup>3)</sup> These parameters refer to the latched chip select signals (CSxL). The early chip select signals (CSxE) are specified together with the address and signal BHE (see figures below).

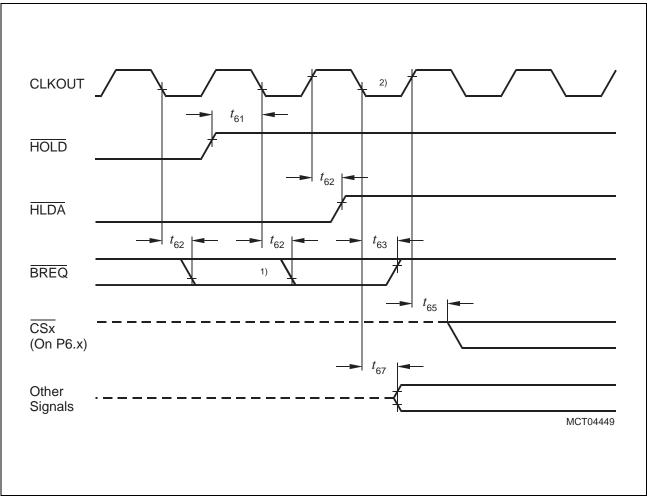

Figure 23 External Bus Arbitration, (Regaining the Bus)

#### Notes

<sup>1)</sup> This is the last chance for BREQ to trigger the indicated regain-sequence. Even if BREQ is activated earlier, the regain-sequence is initiated by HOLD going high.

Please note that HOLD may also be deactivated without the C165 requesting the bus.

<sup>2)</sup> The next C165 driven bus cycle may start here.

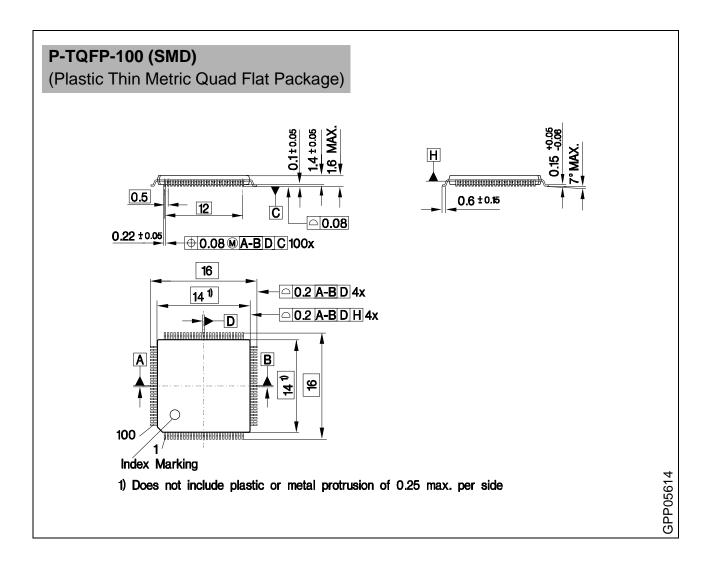

### Sorts of Packing Package outlines for tubes, trays etc. are contained in our Data Book "Package Information". SMD = Surface Mounted Device

Dimensions in mm