Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 17                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 768 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 8x16b; D/A 2x8b                                            |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 28-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 28-MLP (5x5)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f353-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| SFR Definition 22.14. TMR3RLL: Timer 3 Reload Register Low Byte  | 0 |

|------------------------------------------------------------------|---|

| SFR Definition 22.15. TMR3RLH: Timer 3 Reload Register High Byte | 0 |

| SFR Definition 22.16. TMR3L: Timer 3 Low Byte                    | 0 |

| SFR Definition 22.17. TMR3H Timer 3 High Byte 210                | 0 |

| SFR Definition 23.1. PCA0CN: PCA Control                         |   |

| SFR Definition 23.2. PCA0MD: PCA Mode                            |   |

| SFR Definition 23.3. PCA0CPMn: PCA Capture/Compare Mode          | 4 |

| SFR Definition 23.4. PCA0L: PCA Counter/Timer Low Byte           | 5 |

| SFR Definition 23.5. PCA0H: PCA Counter/Timer High Byte 225      | 5 |

| SFR Definition 23.6. PCA0CPLn: PCA Capture Module Low Byte       | 6 |

| SFR Definition 23.7. PCA0CPHn: PCA Capture Module High Byte      | 6 |

| C2 Register Definition 25.1. C2ADD: C2 Address                   | 9 |

| C2 Register Definition 25.2. DEVICEID: C2 Device ID              | 9 |

| C2 Register Definition 25.3. REVID: C2 Revision ID               | 0 |

| C2 Register Definition 25.4. FPCTL: C2 Flash Programming Control | 0 |

| C2 Register Definition 25.5. FPDAT: C2 Flash Programming Data    | 0 |

|                                                                  |   |

#### 3. **Global DC Electrical Characteristics**

#### **Table 3.1. Global DC Electrical Characteristics**

-40 to +85 °C, 25 MHz System Clock unless otherwise specified.

| Parameter                                                      | Conditions                                                                                                                                                                                                                                       | Min | Тур                         | Max                          | Units                |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------|------------------------------|----------------------|

| Analog Supply Voltage <sup>1</sup>                             |                                                                                                                                                                                                                                                  | 2.7 | 3.0                         | 3.6                          | V                    |

| Analog Supply Current                                          | Internal REF, ADC, IDACs,<br>Comparators all active                                                                                                                                                                                              |     | 0.75                        | 1.3                          | mA                   |

| Analog Supply Current with analog<br>sub-systems inactive      | Internal REF, ADC, IDACs,<br>Comparators all disabled,<br>oscillator disabled                                                                                                                                                                    | _   | < 1                         | —                            | μA                   |

| Analog-to-Digital Supply Delta<br>( V <sub>DD</sub> – AV+ )    |                                                                                                                                                                                                                                                  |     | —                           | 0.5                          | V                    |

| Digital Supply Voltage                                         |                                                                                                                                                                                                                                                  | 2.7 | 3.0                         | 3.6                          | V                    |

| Digital Supply Current with CPU active                         | $V_{DD} = 2.7 \text{ V}; \text{ SYSCLK} = 25 \text{ MHz}$<br>$V_{DD} = 2.7 \text{ V}; \text{ SYSCLK} = 50 \text{ MHz}$<br>$V_{DD} = 3.3 \text{ V}; \text{ SYSCLK} = 25 \text{ MHz}$<br>$V_{DD} = 3.3 \text{ V}; \text{ SYSCLK} = 50 \text{ MHz}$ |     | 9.9<br>17.8<br>13.6<br>24.9 | 11.3<br>20.0<br>15.5<br>27.1 | mA<br>mA<br>mA<br>mA |

| Digital Supply Current with CPU inactive (not accessing Flash) | $V_{DD} = 2.7 \text{ V}; \text{ SYSCLK} = 25 \text{ MHz}$<br>$V_{DD} = 2.7 \text{ V}; \text{ SYSCLK} = 50 \text{ MHz}$<br>$V_{DD} = 3.3 \text{ V}; \text{ SYSCLK} = 25 \text{ MHz}$<br>$V_{DD} = 3.3 \text{ V}; \text{ SYSCLK} = 50 \text{ MHz}$ |     | 5.7<br>11.1<br>7.5<br>15.0  | 6.6<br>12.7<br>8.5<br>16.5   | mA<br>mA<br>mA<br>mA |

| Digital Supply Current (shutdown)                              | Oscillator not running                                                                                                                                                                                                                           |     | < 0.1                       |                              | μA                   |

| Digital Supply RAM Data Retention<br>Voltage                   |                                                                                                                                                                                                                                                  | _   | 1.5                         | _                            | V                    |

| SYSCLK (System Clock) 2,3                                      |                                                                                                                                                                                                                                                  | 0   | _                           | 50                           | MHz                  |

| Specified Operating Temperature<br>Range                       |                                                                                                                                                                                                                                                  | -40 | —                           | +85                          | °C                   |

Notes:

Analog Supply AV+ must be greater than 1 V for V<sub>DD</sub> monitor to operate.

SYSCLK is the internal device clock. For operational speeds in excess of 25 MHz, SYSCLK must be derived from the internal clock multiplier.

3. SYSCLK must be at least 32 kHz to enable debugging.

### SFR Definition 5.1. ADC0CN: ADC0 Control

| R        | R                        | R          | R/W        | R/W          | R/W   | R/W   | R/W         | Reset Value |

|----------|--------------------------|------------|------------|--------------|-------|-------|-------------|-------------|

| _        |                          | _          | AD0POL     | AD0BCE       |       | ADOGN |             | 00010000    |

| Bit7     | Bit6                     | Bit5       | Bit4       | Bit3         | Bit2  | Bit1  | Bit0        |             |

|          |                          |            |            |              |       |       | SFR Address | :: 0xF4     |

|          |                          |            |            |              |       |       |             |             |

|          | Unused: Rea              |            |            | 't care.     |       |       |             |             |

| Bit 4:   | AD0POL: AD               |            | •          |              |       |       |             |             |

|          | 0: ADC ope               |            |            |              |       |       |             |             |

|          | 1: ADC ope               |            |            | · ·          | ,     |       |             |             |

| Bit 3:   | ADOBCE: AI               |            |            |              | le.   |       |             |             |

|          | 0: ADC Bur               |            |            |              |       |       |             |             |

| D:4+ 0-0 | 1: ADC Bur               |            |            |              |       |       |             |             |

| Bits 2:0 | AD0GN: AD0<br>000: PGA G | •          | nmable Gal | n Setting.   |       |       |             |             |

|          | 000. PGA G               |            |            |              |       |       |             |             |

|          | 010: PGA G               |            |            |              |       |       |             |             |

|          | 011: PGA G               |            |            |              |       |       |             |             |

|          | 100: PGA G               | •••••      |            |              |       |       |             |             |

|          | 101: PGA G               |            |            |              |       |       |             |             |

|          | 110: PGA G               | ain = 64.  |            |              |       |       |             |             |

|          | 111: PGA G               | ain = 128. |            |              |       |       |             |             |

|          |                          |            |            |              |       |       |             |             |

| This SFR | can only be              | modified   | when ADC   | 0 is in IDLE | mode. |       |             |             |

|          |                          |            |            |              |       |       |             |             |

|          |                          |            |            |              |       |       |             |             |

#### SFR Definition 5.19. ADC0FH: ADC0 Conversion Register (Fast Filter) High Byte

| R/W      | R/W                                                 | R/W          | R/W<br>ADC   | R/W          | R/W          | R/W         | R/W        | Reset Value |

|----------|-----------------------------------------------------|--------------|--------------|--------------|--------------|-------------|------------|-------------|

| Bit7     | Bit6                                                | Bit5         | Bit4         | Bit3         | Bit2         | Bit1        | Bit0       |             |

|          |                                                     |              |              |              |              |             | SFR Addres | s: 0xFE     |

| Bits 7–0 | : ADC0FH: AI<br>C8051F350/<br>result.<br>C8051F352/ | 1: This regi | ster contain | is bits 23–1 | 6 of the 24- | bit ADC fas |            |             |

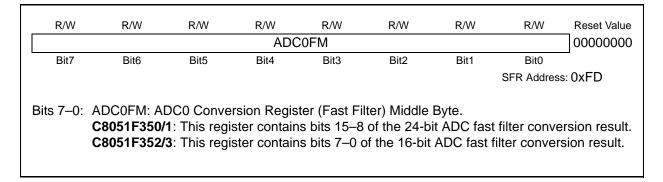

#### SFR Definition 5.20. ADC0FM: ADC0 Conversion Register (Fast Filter) Middle Byte

#### SFR Definition 5.21. ADC0FL: ADC0 Conversion Register (Fast Filter) Low Byte

|     | R/W  | R/W                                    | R/W          | R/W          | R/W           | R/W           | R/W         | R/W         | Reset Value   |

|-----|------|----------------------------------------|--------------|--------------|---------------|---------------|-------------|-------------|---------------|

|     |      | ADC0FL                                 |              |              |               |               |             |             |               |

|     | Bit7 | Bit6                                   | Bit5         | Bit4         | Bit3          | Bit2          | Bit1        | Bit0        |               |

|     |      |                                        |              |              |               |               |             | SFR Addres  | s: 0xFC       |

| Bit | C    | ADC0FL: AD<br>C8051F350/<br>C8051F352/ | 1: This regi | ster contair | ns bits 7–0 c | of the 24-bit | ADC fast fi | lter convei | rsion result. |

| Decimation | Output Word       | PGA Gain Setting |       |       |       |       |       |       |       |  |

|------------|-------------------|------------------|-------|-------|-------|-------|-------|-------|-------|--|

| Ratio      | Rate <sup>2</sup> | 1                | 2     | 4     | 8     | 16    | 32    | 64    | 128   |  |

| 1920       | 10 Hz             | 16.26            | 16.11 | 15.90 | 15.49 | 14.95 | 14.24 | 13.37 | 12.32 |  |

| 768        | 25 Hz             | 14.37            | 14.24 | 13.98 | 13.64 | 13.05 | 12.24 | 11.34 | 10.39 |  |

| 640        | 30 Hz             | 13.63            | 13.64 | 13.57 | 13.10 | 12.57 | 11.82 | 10.86 | 9.93  |  |

| 384        | 50 Hz             | 11.83            | 11.93 | 11.85 | 11.72 | 11.32 | 10.69 | 9.84  | 8.93  |  |

| 320        | 60 Hz             | 11.11            | 11.04 | 11.11 | 11.00 | 10.74 | 10.16 | 9.36  | 8.44  |  |

| 192        | 100 Hz            | 9.43             | 9.28  | 9.40  | 9.34  | 9.17  | 8.86  | 8.21  | 7.39  |  |

#### Table 5.9. ADC0 Fast Filter Flicker-Free (Noise-Free) Resolution<sup>1</sup> in Unipolar Mode (bits)

Notes:

**1.** Flicker-free (Noise-free) Resolution =  $\log_2\left(\frac{FullInputRange(V)}{6.6 \times RMS \ Noise(V)}\right)$

where *Full Input Range* =  $\frac{V_{REF}}{PGA Gain}$  in Unipolar mode and *RMS Noise* is obtained from Table 5.7.

**2.** Output Word Rate assuming Modular Clock frequency = 2.4576 MHz (sampling clock frequency = 19.2 kHz)

NOTES:

Figure 8.2. Single Channel Transfer Function

Figure 8.3. Differential Transfer Function

## 13. Prefetch Engine

The C8051F350/1/2/3 family of devices incorporate a 2-byte prefetch engine. Because the access time of the Flash memory is 40 ns, and the minimum instruction time is 20 ns, the prefetch engine is necessary for full-speed code execution. Instructions are read from Flash memory two bytes at a time by the prefetch engine, and given to the CIP-51 processor core to execute. When running linear code (code without any jumps or branches), the prefetch engine allows instructions to be executed at full speed. When a code branch occurs, the processor may be stalled for up to two clock cycles while the next set of code bytes is retrieved from Flash memory. The FLRT bit (FLSCL.4) determines how many clock cycles are used to read each set of two code bytes from Flash. When operating from a system clock of 25 MHz or less, the FLRT bit should be set to '0' so that the prefetch engine takes only one clock cycle for each read. When operating with a system clock of greater than 25 MHz (up to 50 MHz), the FLRT bit should be set to '1', so that each prefetch code read lasts for two clock cycles.

| R                             | R                                                                                                                                                              | R/W                                                                                                                     | R                                                                                    | R                                                 | R    | R    | R/W          | Reset Value |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------|------|------|--------------|-------------|

|                               |                                                                                                                                                                | PFEN                                                                                                                    |                                                                                      |                                                   |      |      | FLBWE        | 00100000    |

| Bit7                          | Bit6                                                                                                                                                           | Bit5                                                                                                                    | Bit4                                                                                 | Bit3                                              | Bit2 | Bit1 | Bit0         | -           |

|                               |                                                                                                                                                                |                                                                                                                         |                                                                                      |                                                   |      |      | SFR Address: | 0xE3        |

| Bit 5:<br>Bits 4–1:<br>Bit 0: | Unused. Rea<br>PFEN: Prefe<br>This bit enab<br>0: Prefetch e<br>1: Prefetch e<br>Unused. Rea<br>FLBWE: Flas<br>This bit allow<br>0: Each byte<br>1: Flash byte | tch Enable<br>oles the pre-<br>engine is dis<br>ongine is en<br>ad = 0000b<br>sh Block W<br>vs block wri<br>of a softwa | fetch enging<br>abled.<br>Write = Dc<br>rite Enable.<br>tes to Flash<br>are Flash wi | e.<br>on't Care<br>n memory fr<br>rite is writter |      |      |              |             |

### SFR Definition 13.1. PFE0CN: Prefetch Engine Control

#### SFR Definition 14.2. RSTSRC: Reset Source

| R     | R                           | R/W                                                                                | R/W         | R            | R/W                  | R/W           | R              | Reset Value         |  |  |

|-------|-----------------------------|------------------------------------------------------------------------------------|-------------|--------------|----------------------|---------------|----------------|---------------------|--|--|

| —     | FERROR                      | CORSEF                                                                             | SWRSF       | WDTRSF       | MCDRSF               | PORSF         | PINRSF         | Variable            |  |  |

| Bit7  | Bit6                        | Bit5                                                                               | Bit4        | Bit3         | Bit2                 | Bit1          | Bit0           | _                   |  |  |

|       |                             | SFR Address: 0xEF                                                                  |             |              |                      |               |                |                     |  |  |

|       |                             |                                                                                    |             |              |                      |               |                |                     |  |  |

| Bit7: | UNUSED. R                   |                                                                                    |             | care.        |                      |               |                |                     |  |  |

| Bit6: | FERROR: F                   |                                                                                    |             | ,            | •• •                 |               |                |                     |  |  |

|       | 0: Source of                |                                                                                    |             |              |                      | ror.          |                |                     |  |  |

| Ditc  | 1: Source of                |                                                                                    |             |              |                      |               |                |                     |  |  |

| Bit5: | CORSEF: Co<br>0: Read: So   |                                                                                    |             |              |                      | . Compara     | tor() is not a | rosot               |  |  |

|       | source.                     |                                                                                    | IESEL WAS   | not Compan   |                      | . Compara     |                | Teset               |  |  |

|       | 1: <b>Read:</b> So          | urce of last                                                                       | reset was   | Comparator   | 0. Write: Co         | omparator0    | is a reset s   | source              |  |  |

|       | (active-low).               |                                                                                    | looot hao   | oomparator   |                      | Inparatoro    |                |                     |  |  |

| Bit4: | SWRSF: So                   | ftware Rese                                                                        | et Force an | d Flag.      |                      |               |                |                     |  |  |

|       | 0: <b>Read:</b> So          |                                                                                    |             |              | o the SWRS           | SF bit. Write | e: No Effect   | t.                  |  |  |

|       | 1: Read: So                 | urce of last                                                                       | was a write | e to the SWI | RSF bit. <b>Wr</b> i | ite: Forces   | a system re    | eset.               |  |  |

| Bit3: | WDTRSF: W                   |                                                                                    |             |              |                      |               |                |                     |  |  |

|       | 0: Source of                |                                                                                    |             |              |                      |               |                |                     |  |  |

|       | 1: Source of                |                                                                                    |             |              |                      |               |                |                     |  |  |

| Bit2: | MCDRSF: M                   | -                                                                                  |             | -            |                      |               | ( )            |                     |  |  |

|       | 0: Read: So<br>Clock Detect |                                                                                    |             | not a missin | g Clock Det          | ector timed   | out. Write: M  | viissing            |  |  |

|       | 1: Read: So                 |                                                                                    |             | a Missina C  | lock Dotoct          | or timeout    | Write: Mice    | ing Clock           |  |  |

|       | Detector ena                |                                                                                    |             | •            |                      |               |                | Ing Clock           |  |  |

| Bit1: | PORSF: Pov                  |                                                                                    |             | -            |                      |               |                |                     |  |  |

|       | This bit is se              |                                                                                    |             | •            | s. Writing thi       | s bit enable  | es/disables    | the V <sub>DD</sub> |  |  |

|       | monitor as a                | •                                                                                  | •           |              | -                    |               |                |                     |  |  |

|       | and stabiliz                |                                                                                    |             | -            |                      | -             |                |                     |  |  |

|       | 0: Read: Las                |                                                                                    |             |              |                      |               |                |                     |  |  |

|       | reset source                |                                                                                    |             |              | J                    |               |                |                     |  |  |

|       | 1: Read: Las                |                                                                                    | a power-o   | n or Voo mo  | nitor reset: a       | all other res | et flags ind   | eterminate.         |  |  |

|       | Write: V <sub>DD</sub> r    |                                                                                    |             |              | ,                    |               | 0              |                     |  |  |

| Bit0: | PINRSF: HV                  |                                                                                    |             |              |                      |               |                |                     |  |  |

| 2.10. |                             |                                                                                    | 0           | ST pin.      |                      |               |                |                     |  |  |

|       |                             | 0: Source of last reset was not /RST pin.<br>1: Source of last reset was /RST pin. |             |              |                      |               |                |                     |  |  |

|       |                             |                                                                                    | •           |              |                      |               |                |                     |  |  |

|       |                             |                                                                                    |             |              |                      |               |                |                     |  |  |

#### 11.2. Data Memory

The C8051F350/1/2/3 includes 256 bytes of internal RAM mapped into the data memory space from 0x00 through 0xFF. The lower 128 bytes of data memory are used for general purpose registers and scratch pad memory. Either direct or indirect addressing may be used to access the lower 128 bytes of data memory. Locations 0x00 through 0x1F are addressable as four banks of general purpose registers, each bank consisting of eight byte-wide registers. The next 16 bytes, locations 0x20 through 0x2F, may either be addressed as bytes or as 128 bit locations accessible with the direct addressing mode.

The upper 128 bytes of data memory are accessible only by indirect addressing. This region occupies the same address space as the Special Function Registers (SFRs) but is physically separate from the SFR space. The addressing mode used by an instruction when accessing locations above 0x7F determines whether the CPU accesses the upper 128 bytes of data memory space or the SFRs. Instructions that use direct addressing will access the SFR space. Instructions using indirect addressing above 0x7F access the upper 128 bytes of data memory organization of the C8051F350/1/2/3.

The C8051F35x family also includes 512 bytes of on-chip RAM mapped into the external memory (XDATA) space. This RAM can be accessed using the CIP-51 core's MOVX instruction. More information on the XRAM memory can be found in Section "16. External RAM' on page 127.

#### 11.3. General Purpose Registers

The lower 32 bytes of data memory (locations 0x00 through 0x1F) may be addressed as four banks of general-purpose registers. Each bank consists of eight byte-wide registers designated R0 through R7. Only one of these banks may be enabled at a time. Two bits in the program status word, RS0 (PSW.3) and RS1 (PSW.4), select the active register bank (see description of the PSW in SFR Definition 10.4). This allows fast context switching when entering subroutines and interrupt service routines. Indirect addressing modes use registers R0 and R1 as index registers.

#### 11.4. Bit Addressable Locations

In addition to direct access to data memory organized as bytes, the sixteen data memory locations at 0x20 through 0x2F are also accessible as 128 individually addressable bits. Each bit has a bit address from 0x00 to 0x7F. Bit 0 of the byte at 0x20 has bit address 0x00 while bit 7 of the byte at 0x20 has bit address 0x07. Bit 7 of the byte at 0x2F has bit address 0x7F. A bit access is distinguished from a full byte access by the type of instruction used (bit source or destination operands as opposed to a byte source or destination).

The MCS-51<sup>™</sup> assembly language allows an alternate notation for bit addressing of the form XX.B where XX is the byte address and B is the bit position within the byte. For example, the instruction:

MOV C, 22.3h

moves the Boolean value at 0x13 (bit 3 of the byte at location 0x22) into the Carry flag.

#### 11.5. Stack

A programmer's stack can be located anywhere in the 256-byte data memory. The stack area is designated using the Stack Pointer (SP, 0x81) SFR. The SP will point to the last location used. The next value pushed on the stack is placed at SP+1 and then SP is incremented. A reset initializes the stack pointer to location 0x07. Therefore, the first value pushed on the stack is placed at location 0x08, which is also the first register (R0) of register bank 1. Thus, if more than one register bank is to be used, the SP should be initialized to a location in the data memory not being used for data storage. The stack depth can extend up to 256 bytes.

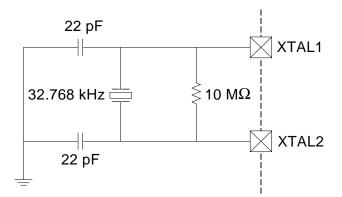

The capacitors shown in the external crystal configuration provide the load capacitance required by the crystal for correct oscillation. These capacitors are "in series" as seen by the crystal and "in parallel" with the stray capacitance of the XTAL1 and XTAL2 pins.

Note: The load capacitance depends upon the crystal and the manufacturer. Please refer to the crystal datasheet when completing these calculations.

For example, a tuning-fork crystal of 32.768 kHz with a recommended load capacitance of 12.5 pF should use the configuration shown in Figure 17.1, Option 1. The total value of the capacitors and the stray capacitance of the XTAL pins should equal 25 pF. With a stray capacitance of 3 pF per pin, the 22 pF capacitors yield an equivalent capacitance of 12.5 pF across the crystal, as shown in Figure 17.2.

Figure 17.2. 32.768 kHz External Crystal Example

**Important note on external crystals:** Crystal oscillator circuits are quite sensitive to PCB layout. The crystal should be placed as close as possible to the XTAL pins on the device. The traces should be as short as possible and shielded with ground plane from any other traces which could introduce noise or interference.

| SFR Definition 18.1. XBR0: Port I/O | Crossbar Register 0 |

|-------------------------------------|---------------------|

|-------------------------------------|---------------------|

| R        | R                                    | R/W                                                 | R/W         | R/W           | R/W          | R/W         | R/W           | Reset Value |

|----------|--------------------------------------|-----------------------------------------------------|-------------|---------------|--------------|-------------|---------------|-------------|

|          |                                      | CPOAE                                               | CP0E        | SYSCKE        | SMB0E        | SPI0E       | URTOE         | 00000000    |

| Bit7     | Bit6                                 | Bit5                                                | Bit4        | Bit3          | Bit2         | Bit1        | Bit0          |             |

| Biti     | Bito                                 | Bito                                                | BIT         | Bito          | DILL         | BRI         | SFR Address   | 0vF1        |

|          |                                      |                                                     |             |               |              |             | OF IN Address |             |

| Bits7–6: | UNUSED. R                            | ead = 00b.                                          | Write = dor | n't care.     |              |             |               |             |

| Bit5:    | CP0AE: Cor                           |                                                     |             |               | nable        |             |               |             |

|          | 0: Asynchror                         | •                                                   | •           | •             |              |             |               |             |

|          | 1: Asynchror                         |                                                     |             |               |              |             |               |             |

| Bit4:    | CP0E: Com                            | parator0 Ou                                         | tput Enable | e             |              |             |               |             |

|          | 0: CP0 unav                          | ailable at P                                        | ort pin.    |               |              |             |               |             |

|          | 1: CP0 route                         | ed to Port pi                                       | n P1.5.     |               |              |             |               |             |

| Bit3:    | SYSCKE: /S                           |                                                     |             |               |              |             |               |             |

|          | 0: /SYSCLK                           |                                                     |             |               |              |             |               |             |

|          | 1: /SYSCLK                           |                                                     |             | pin.          |              |             |               |             |

| Bit2:    | SMB0E: SM                            |                                                     |             |               |              |             |               |             |

|          | 0: SMBus I/C                         |                                                     |             | ins.          |              |             |               |             |

|          | 1: SMBus I/C                         |                                                     | Port pins.  |               |              |             |               |             |

| Bit1:    | SPIOE: SPI I                         |                                                     |             |               |              |             |               |             |

|          | 0: SPI I/O ur                        |                                                     | •           |               |              |             |               |             |

| Dito     | 1: SPI I/O ro                        |                                                     | •           | e that the SP | 'I can be as | signed eith | er 3 or 4 Gi  | PIO pins.   |

| Bit0:    |                                      | URT0E: UART I/O Output Enable                       |             |               |              |             |               |             |

|          | 0: UART I/O unavailable at Port pin. |                                                     |             |               |              |             |               |             |

|          | I. UART IA                           | 1: UART TX0, RX0 routed to Port pins P0.4 and P0.5. |             |               |              |             |               |             |

|          |                                      |                                                     |             |               |              |             |               |             |

#### 19.4. Using the SMBus

The SMBus can operate in both Master and Slave modes. The interface provides timing and shifting control for serial transfers; higher level protocol is determined by user software. The SMBus interface provides the following application-independent features:

- Byte-wise serial data transfers

- Clock signal generation on SCL (Master Mode only) and SDA data synchronization

- Timeout/bus error recognition, as defined by the SMB0CF configuration register

- START/STOP timing, detection, and generation

- Bus arbitration

- Interrupt generation

- Status information

SMBus interrupts are generated for each data byte or slave address that is transferred. When transmitting, this interrupt is generated after the ACK cycle so that software may read the received ACK value; when receiving data, this interrupt is generated before the ACK cycle so that software may define the outgoing ACK value. See Section "19.5. SMBus Transfer Modes' on page 163 for more details on transmission sequences.

Interrupts are also generated to indicate the beginning of a transfer when a master (START generated), or the end of a transfer when a slave (STOP detected). Software should read the SMB0CN (SMBus Control register) to find the cause of the SMBus interrupt. The SMB0CN register is described in Section "19.4.2. SMB0CN Control Register' on page 159; Table 19.4 provides a quick SMB0CN decoding reference.

SMBus configuration options include:

- Timeout detection (SCL Low Timeout and/or Bus Free Timeout)

- SDA setup and hold time extensions

- Slave event enable/disable

- Clock source selection

These options are selected in the SMB0CF register, as described in Section "19.4.1. SMBus Configuration Register' on page 156.

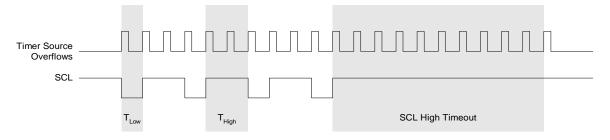

Figure 19.4 shows the typical SCL generation described by Equation 19.2. Notice that  $T_{HIGH}$  is typically twice as large as  $T_{LOW}$ . The actual SCL output may vary due to other devices on the bus (SCL may be extended low by slower slave devices, or driven low by contending master devices). The bit rate when operating as a master will never exceed the limits defined by equation Equation 19.1.

Figure 19.4. Typical SMBus SCL Generation

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable after SCL transitions from high-to-low. EXTHOLD should be set so that the minimum setup and hold times meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 19.2 shows the minimum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary when SYSCLK is above 10 MHz.

| EXTHOLD                                                                                                                                                                                                                                                                              | Minimum SDA Setup Time             | Minimum SDA Hold Time |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------|--|--|--|--|--|

|                                                                                                                                                                                                                                                                                      | T <sub>low</sub> – 4 system clocks |                       |  |  |  |  |  |

| 0                                                                                                                                                                                                                                                                                    | OR                                 | 3 system clocks       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                      | 1 system clock + s/w delay*        |                       |  |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                    | 11 system clocks                   | 12 system clocks      |  |  |  |  |  |

| *Note: Setup Time for ACK bit transmissions and the MSB of all data transfers. The s/w<br>delay occurs between the time SMB0DAT or ACK is written and when SI is cleared.<br>Note that if SI is cleared in the same write that defines the outgoing ACK value, s/w<br>delay is zero. |                                    |                       |  |  |  |  |  |

Table 19.2. Minimum SDA Setup and Hold Times

With the SMBTOE bit set, Timer 3 should be configured to overflow after 25 ms in order to detect SCL low timeouts (see Section "19.3.3. SCL Low Timeout' on page 154). The SMBus interface will force Timer 3 to reload while SCL is high, and allow Timer 3 to count when SCL is low. The Timer 3 interrupt service routine should be used to reset SMBus communication by disabling and re-enabling the SMBus.

SMBus Free Timeout detection can be enabled by setting the SMBFTE bit. When this bit is set, the bus will be considered free if SDA and SCL remain high for more than 10 SMBus clock source periods (see Figure 19.4). When a Free Timeout is detected, the interface will respond as if a STOP was detected (an interrupt will be generated, and STO will be set).

|                              | Frequency: 24.5 MHz          |                      |                                  |                       |                                     |      |                                  |  |  |  |

|------------------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------|------|----------------------------------|--|--|--|

|                              | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select)* | T1M* | Timer 1<br>Reload<br>Value (hex) |  |  |  |

|                              | 230400                       | -0.32%               | 106                              | SYSCLK                | XX                                  | 1    | 0xCB                             |  |  |  |

| SYSCLK from<br>Internal Osc. | 115200                       | -0.32%               | 212                              | SYSCLK                | XX                                  | 1    | 0x96                             |  |  |  |

|                              | 57600                        | 0.15%                | 426                              | SYSCLK                | XX                                  | 1    | 0x2B                             |  |  |  |

|                              | 28800                        | -0.32%               | 848                              | SYSCLK/4              | 01                                  | 0    | 0x96                             |  |  |  |

|                              | 14400                        | 0.15%                | 1704                             | SYSCLK / 12           | 00                                  | 0    | 0xB9                             |  |  |  |

|                              | 9600                         | -0.32%               | 2544                             | SYSCLK / 12           | 00                                  | 0    | 0x96                             |  |  |  |

|                              | 2400                         | -0.32%               | 10176                            | SYSCLK / 48           | 10                                  | 0    | 0x96                             |  |  |  |

| SY<br>Int                    | 1200                         | 0.15%                | 20448                            | SYSCLK / 48           | 10                                  | 0    | 0x2B                             |  |  |  |

# Table 20.1. Timer Settings for Standard Baud RatesUsing the Internal Oscillator

X = Don't care

\*Note: SCA1–SCA0 and T1M bit definitions can be found in Section 22.1.

# Table 20.2. Timer Settings for Standard Baud RatesUsing an External 25.0 MHz Oscillator

|                      | Frequency: 25.0 MHz          |                      |                                  |                       |                                     |      |                                  |  |  |  |

|----------------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------|------|----------------------------------|--|--|--|

|                      | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select)* | T1M* | Timer 1<br>Reload<br>Value (hex) |  |  |  |

|                      | 230400                       | -0.47%               | 108                              | SYSCLK                | XX                                  | 1    | 0xCA                             |  |  |  |

|                      | 115200                       | 0.45%                | 218                              | SYSCLK                | XX                                  | 1    | 0x93                             |  |  |  |

|                      | 57600                        | -0.01%               | 434                              | SYSCLK                | XX                                  | 1    | 0x27                             |  |  |  |

| from<br>Osc.         | 28800                        | 0.45%                | 872                              | SYSCLK / 4            | 01                                  | 0    | 0x93                             |  |  |  |

| $\sim$               | 14400                        | -0.01%               | 1736                             | SYSCLK/4              | 01                                  | 0    | 0x27                             |  |  |  |

| SYSCLK<br>External ( | 9600                         | 0.15%                | 2608                             | EXTCLK / 8            | 11                                  | 0    | 0x5D                             |  |  |  |

| SC<br>teri           | 2400                         | 0.45%                | 10464                            | SYSCLK / 48           | 10                                  | 0    | 0x93                             |  |  |  |

| SY<br>Ext            | 1200                         | -0.01%               | 20832                            | SYSCLK / 48           | 10                                  | 0    | 0x27                             |  |  |  |

| F                    | 57600                        | -0.47%               | 432                              | EXTCLK / 8            | 11                                  | 0    | 0xE5                             |  |  |  |

| -K from<br>I Osc.    | 28800                        | -0.47%               | 864                              | EXTCLK / 8            | 11                                  | 0    | 0xCA                             |  |  |  |

|                      | 14400                        | 0.45%                | 1744                             | EXTCLK / 8            | 11                                  | 0    | 0x93                             |  |  |  |

| SYSCLK<br>Internal C | 9600                         | 0.15%                | 2608                             | EXTCLK / 8            | 11                                  | 0    | 0x5D                             |  |  |  |

X = Don't care

\*Note: SCA1–SCA0 and T1M bit definitions can be found in Section 22.1.

#### 21.5. Serial Clock Timing

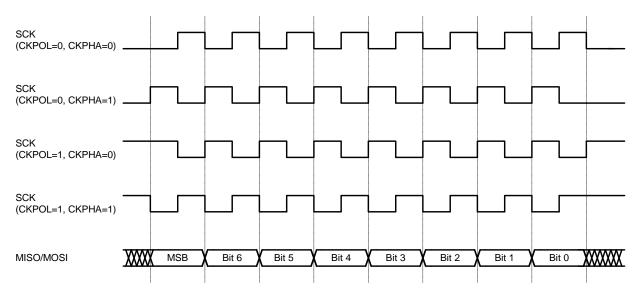

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.5) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.4) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0 should be disabled (by clearing the SPIEN bit, SPI0CN.0) when changing the clock phase or polarity. The clock and data line relationships are shown in Figure 21.5.

The SPI0 Clock Rate Register (SPI0CKR) as shown in SFR Definition 21.3 controls the master mode serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz, whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-wire slave mode), and the serial input data synchronously with the slave's system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less than 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency.

#### 21.6. SPI Special Function Registers

SPI0 is accessed and controlled through four special function registers in the system controller: SPI0CN Control Register, SPI0DAT Data Register, SPI0CFG Configuration Register, and SPI0CKR Clock Rate Register. The four special function registers related to the operation of the SPI0 Bus are described in the following figures.

### SFR Definition 21.1. SPI0CFG: SPI0 Configuration

| R<br>SPIBSY  | R/W<br>MSTEN                                                                                                                                                                                | R/W<br>CKPHA | R/W<br>CKPOL | R<br>SLVSEL   | R<br>NSSIN    | R<br>SRMT     | R<br>RXBMT          | Reset Value |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|---------------|---------------|---------------|---------------------|-------------|--|--|--|--|

|              |                                                                                                                                                                                             |              |              |               |               |               |                     |             |  |  |  |  |

| Bit7         | Bit6                                                                                                                                                                                        | Bit5         | Bit4         | Bit3          | Bit2          | Bit1          | Bit0<br>SFR Address | ΟχΔ1        |  |  |  |  |

|              |                                                                                                                                                                                             |              |              |               |               |               | SFR Auuress         |             |  |  |  |  |

| Bit 7:       | SPIBSY: SP                                                                                                                                                                                  | l Busv (read | d only).     |               |               |               |                     |             |  |  |  |  |

|              | This bit is se                                                                                                                                                                              | •            | • /          | l transfer is | in progress   | (Master or    | Slave Mode          | e).         |  |  |  |  |

| Bit 6:       | MSTEN: Ma                                                                                                                                                                                   |              |              |               | 1 3 3 3 3     | (             |                     |             |  |  |  |  |

|              | 0: Disable m                                                                                                                                                                                | aster mode   | . Operate i  | n slave mod   | e.            |               |                     |             |  |  |  |  |

|              | 1: Enable ma                                                                                                                                                                                | aster mode   | Operate a    | s a master.   |               |               |                     |             |  |  |  |  |

| Bit 5:       | CKPHA: SPI                                                                                                                                                                                  | 0 Clock Ph   | ase.         |               |               |               |                     |             |  |  |  |  |

|              | This bit cont                                                                                                                                                                               |              |              |               |               |               |                     |             |  |  |  |  |

|              | 0: Data cent                                                                                                                                                                                |              |              |               |               |               |                     |             |  |  |  |  |

|              | 1: Data cent                                                                                                                                                                                |              |              | of SCK perio  | od.*          |               |                     |             |  |  |  |  |

| Bit 4:       | CKPOL: SPI                                                                                                                                                                                  |              |              | _             |               |               |                     |             |  |  |  |  |

|              | This bit cont                                                                                                                                                                               |              |              | arity.        |               |               |                     |             |  |  |  |  |

|              | 0: SCK line I                                                                                                                                                                               |              |              |               |               |               |                     |             |  |  |  |  |

| N'1 O        | 1: SCK line high in idle state.                                                                                                                                                             |              |              |               |               |               |                     |             |  |  |  |  |

| Bit 3:       | SLVSEL: Slave Selected Flag (read only).                                                                                                                                                    |              |              |               |               |               |                     |             |  |  |  |  |

|              | This bit is set to logic 1 whenever the NSS pin is low indicating SPI0 is the selected slave. I                                                                                             |              |              |               |               |               |                     |             |  |  |  |  |

|              | is cleared to logic 0 when NSS is high (slave not selected). This bit does not indicate the instantaneous value at the NSS pin, but rather a de-glitched version of the pin input.          |              |              |               |               |               |                     |             |  |  |  |  |

| Bit 2:       |                                                                                                                                                                                             |              |              |               | •             |               |                     | pui.        |  |  |  |  |

| μ <u>2</u> . | NSSIN: NSS Instantaneous Pin Input (read only).<br>This bit mimics the instantaneous value that is present on the NSS port pin at the time that                                             |              |              |               |               |               |                     |             |  |  |  |  |

|              | the register is read. This input is not de-glitched.                                                                                                                                        |              |              |               |               |               |                     |             |  |  |  |  |

| Bit 1:       | SRMT: Shift                                                                                                                                                                                 |              | •            | •             |               | nlv).         |                     |             |  |  |  |  |

|              |                                                                                                                                                                                             |              |              |               |               |               | t of the shift      | reaister.   |  |  |  |  |

|              | This bit will be set to logic 1 when all data has been transferred in/out of the shift register, and there is no new information available to read from the transmit buffer or write to the |              |              |               |               |               |                     |             |  |  |  |  |

|              | receive buffer. It returns to logic 0 when a data byte is transferred to the shift register from                                                                                            |              |              |               |               |               |                     |             |  |  |  |  |

|              | the transmit buffer or by a transition on SCK.                                                                                                                                              |              |              |               |               |               |                     |             |  |  |  |  |

|              | NOTE: SRM                                                                                                                                                                                   | T = 1 when   | in Master I  | Mode.         |               |               |                     |             |  |  |  |  |

| Bit O:       | RXBMT: Red                                                                                                                                                                                  |              |              |               |               |               |                     |             |  |  |  |  |

|              | This bit will b                                                                                                                                                                             |              |              |               |               |               |                     |             |  |  |  |  |

|              | information.                                                                                                                                                                                |              |              | ion availabl  | e in the rece | eive buffer t | hat has not         | been read   |  |  |  |  |

|              | this bit will re                                                                                                                                                                            |              |              |               |               |               |                     |             |  |  |  |  |

|              | NOTE: RXB                                                                                                                                                                                   | MT = 1 whe   | en in Master | r Mode.       |               |               |                     |             |  |  |  |  |

|              |                                                                                                                                                                                             |              |              |               |               |               |                     |             |  |  |  |  |

|              |                                                                                                                                                                                             | iming param  | -1           |               |               |               |                     |             |  |  |  |  |

#### SFR Definition 22.8. TMR2CN: Timer 2 Control

| R/W   | R/W                                                                                                                                                                                             | R/W           | R/W        | R/W          | R/W            | R/W           | R/W          | Reset Value        |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------|--------------|----------------|---------------|--------------|--------------------|--|--|--|--|

| TF2H  | TF2L                                                                                                                                                                                            | TF2LEN        |            | T2SPLIT      | TR2            |               | T2XCLK       | 00000000           |  |  |  |  |

| Bit7  | Bit6                                                                                                                                                                                            | Bit5          | Bit4       | Bit3         | Bit2           | Bit1          | Bit0         | Bit<br>Addressable |  |  |  |  |

|       |                                                                                                                                                                                                 |               |            |              |                |               | SFR Address  | : 0xC8             |  |  |  |  |

|       |                                                                                                                                                                                                 |               |            |              |                |               |              |                    |  |  |  |  |

| Bit7: | TF2H: Timer<br>Set by hardv                                                                                                                                                                     |               |            |              | orflowe fro    | m OvEE to     | 0v00 lp 16   | hit mada           |  |  |  |  |

|       | this will occu                                                                                                                                                                                  |               |            |              |                |               |              |                    |  |  |  |  |

|       | enabled, set                                                                                                                                                                                    |               |            |              |                |               |              |                    |  |  |  |  |

|       | TF2H is not                                                                                                                                                                                     |               |            |              | and must I     | be cleared    | by software. |                    |  |  |  |  |

| Bit6: | TF2L: Timer<br>Set by hardv                                                                                                                                                                     |               |            |              | orflowe from   | m OvEE to (   |              | thic hit ic        |  |  |  |  |

|       | set, an interr                                                                                                                                                                                  |               |            |              |                |               |              |                    |  |  |  |  |

|       | will set wher                                                                                                                                                                                   |               |            |              |                |               |              |                    |  |  |  |  |

| DVE   | ically cleared                                                                                                                                                                                  |               |            |              |                |               |              |                    |  |  |  |  |

| Bit5: | TF2LEN: Tin<br>This bit enab                                                                                                                                                                    |               |            |              | arrunte If T   | F2I FN is s   | et and Time  | r 2 inter-         |  |  |  |  |

|       | rupts are ena                                                                                                                                                                                   |               |            |              |                |               |              |                    |  |  |  |  |

|       | This bit shou                                                                                                                                                                                   | uld be cleare | ed when op | erating Time |                |               |              |                    |  |  |  |  |

|       | 0: Timer 2 Lo<br>1: Timer 2 Lo                                                                                                                                                                  |               |            |              |                |               |              |                    |  |  |  |  |

| Bit4: | UNUSED. R                                                                                                                                                                                       |               |            |              |                |               |              |                    |  |  |  |  |

| Bit3: | T2SPLIT: Tir                                                                                                                                                                                    |               |            |              |                |               |              |                    |  |  |  |  |

|       | When this bi                                                                                                                                                                                    |               |            |              |                | with auto-re  | load.        |                    |  |  |  |  |

|       | 0: Timer 2 operates in 16-bit auto-reload mode.<br>1: Timer 2 operates as two 8-bit auto-reload timers.                                                                                         |               |            |              |                |               |              |                    |  |  |  |  |

| Bit2: | TR2: Timer 2 Run Control.                                                                                                                                                                       |               |            |              |                |               |              |                    |  |  |  |  |

|       | This bit enab                                                                                                                                                                                   |               |            |              | e, this bit ei | nables/disa   | bles TMR2H   | l only;            |  |  |  |  |

|       | TMR2L is always enabled in this mode.<br>0: Timer 2 disabled.                                                                                                                                   |               |            |              |                |               |              |                    |  |  |  |  |

|       | 1: Timer 2 er                                                                                                                                                                                   |               |            |              |                |               |              |                    |  |  |  |  |

| Bit1: | UNUSED. R                                                                                                                                                                                       |               |            |              |                |               |              |                    |  |  |  |  |

| Bit0: | T2XCLK: Tin                                                                                                                                                                                     |               |            |              | mar Olf Ti     | mar Q ia ia ( | 0 hitmada i  | this hit           |  |  |  |  |

|       | This bit selects the external clock source for Timer 2. If Timer 2 is in 8-bit mode, this bit selects the external oscillator clock source for both timer bytes. However, the Timer 2 Clock     |               |            |              |                |               |              |                    |  |  |  |  |

|       | Select bits (T2MH and T2ML in register CKCON) may still be used to select between the                                                                                                           |               |            |              |                |               |              |                    |  |  |  |  |

|       | external cloc                                                                                                                                                                                   |               |            |              |                |               |              |                    |  |  |  |  |

|       | <ul><li>0: Timer 2 external clock selection is the system clock divided by 12.</li><li>1: Timer 2 external clock selection is the external clock divided by 8. Note that the external</li></ul> |               |            |              |                |               |              |                    |  |  |  |  |

|       | oscillator sou                                                                                                                                                                                  |               |            |              |                |               |              |                    |  |  |  |  |