Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                          |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 50MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 17                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 768 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | A/D 8x16b; D/A 2x8b                                             |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 28-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 28-MLP (5x5)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f353-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| <b>11. Memory Organization and SFRs</b><br>Figure 11.1. Memory Map         | 99    |

|----------------------------------------------------------------------------|-------|

| 12. Interrupt Handler                                                      | 00    |

| 13. Prefetch Engine                                                        |       |

| 14. Reset Sources                                                          |       |

| Figure 14.1. Reset Sources                                                 | 115   |

| Figure 14.2. Power-On and VDD Monitor Reset Timing                         |       |

| 15. Flash Memory                                                           | . 110 |

| Figure 15.1. Flash Memory Map                                              | 122   |

| 16. External RAM                                                           | . 123 |

| 17. Oscillators                                                            |       |

| Figure 17.1. Oscillator Diagram                                            | 120   |

| Figure 17.2. 32.768 kHz External Crystal Example                           |       |

| 18. Port Input/Output                                                      | . 152 |

| Figure 18.1. Port I/O Functional Block Diagram                             | 127   |

| Figure 18.2. Port I/O Cell Block Diagram                                   | 120   |

| Figure 18.3. Crossbar Priority Decoder with No Pins Skipped                |       |

| Figure 18.4. Crossbar Priority Decoder with Crystal Pins Skipped           |       |

| 19. SMBus                                                                  | . 140 |

|                                                                            | 151   |

| Figure 19.1. SMBus Block Diagram                                           |       |

| Figure 19.2. Typical SMBus Configuration<br>Figure 19.3. SMBus Transaction | 152   |

|                                                                            |       |

| Figure 19.4. Typical SMBus SCL Generation                                  |       |

| Figure 19.5. Typical Master Transmitter Sequence                           |       |

| Figure 19.6. Typical Master Receiver Sequence                              |       |

| Figure 19.7. Typical Slave Receiver Sequence                               |       |

| Figure 19.8. Typical Slave Transmitter Sequence                            | . 100 |

|                                                                            | 474   |

| Figure 20.1. UARTO Block Diagram                                           |       |

| Figure 20.2. UARTO Baud Rate Logic                                         |       |

| Figure 20.3. UART Interconnect Diagram                                     |       |

| Figure 20.4. 8-Bit UART Timing Diagram                                     |       |

| Figure 20.5. 9-Bit UART Timing Diagram                                     |       |

| Figure 20.6. UART Multi-Processor Mode Interconnect Diagram                | . 175 |

| 21. Serial Peripheral Interface (SPI0)                                     | 101   |

| Figure 21.1. SPI Block Diagram                                             | . 101 |

| Figure 21.2. Multiple-Master Mode Connection Diagram                       |       |

| Figure 21.3. 3-Wire Single Master and Slave Mode Connection Diagram        |       |

| Figure 21.4. 4-Wire Single Master and Slave Mode Connection Diagram        |       |

| Figure 21.5. Data/Clock Timing Relationship                                |       |

| Figure 21.6. SPI Master Timing (CKPHA = 0)                                 |       |

| Figure 21.7. SPI Master Timing (CKPHA = 1)                                 | . 191 |

| Figure 21.8. SPI Slave Timing (CKPHA = 0)                                  | . 192 |

| Figure 21.9. SPI Slave Timing (CKPHA = 1)                                  | . 192 |

| SFR Definition 14.1. VDM0CN: VDD Monitor Control                 | 117 |

|------------------------------------------------------------------|-----|

| SFR Definition 14.2. RSTSRC: Reset Source                        |     |

| SFR Definition 15.1. PSCTL: Program Store R/W Control            |     |

| SFR Definition 15.2. FLKEY: Flash Lock and Key                   |     |

| SFR Definition 15.3. FLSCL: Flash Scale                          |     |

| SFR Definition 16.1. EMIOCN: External Memory Interface Control   |     |

| SFR Definition 17.1. OSCICN: Internal Oscillator Control         |     |

| SFR Definition 17.2. OSCICL: Internal Oscillator Calibration     |     |

| SFR Definition 17.2. OSCICL: Internal Oscillator Calibration     |     |

| SFR Definition 17.4. CLKMUL: Clock Multiplier Control            |     |

| •                                                                |     |

| SFR Definition 17.5. CLKSEL: Clock Select                        |     |

| SFR Definition 18.1. XBR0: Port I/O Crossbar Register 0          |     |

| SFR Definition 18.2. XBR1: Port I/O Crossbar Register 1          |     |

| SFR Definition 18.3. P0: Port0                                   |     |

| SFR Definition 18.4. POMDIN: Port0 Input Mode                    |     |

| SFR Definition 18.5. POMDOUT: Port0 Output Mode                  |     |

| SFR Definition 18.6. POSKIP: Port0 Skip                          |     |

| SFR Definition 18.7. P1: Port1                                   |     |

| SFR Definition 18.8. P1MDIN: Port1 Input Mode                    |     |

| SFR Definition 18.9. P1MDOUT: Port1 Output Mode                  |     |

| SFR Definition 18.10. P1SKIP: Port1 Skip                         |     |

| SFR Definition 18.11. P2: Port2                                  |     |

| SFR Definition 18.12. P2MDOUT: Port2 Output Mode                 |     |

| SFR Definition 19.1. SMB0CF: SMBus Clock/Configuration           |     |

| SFR Definition 19.2. SMB0CN: SMBus Control                       |     |

| SFR Definition 19.3. SMB0DAT: SMBus Data                         |     |

| SFR Definition 20.1. SCON0: Serial Port 0 Control                |     |

| SFR Definition 20.2. SBUF0: Serial (UART0) Port Data Buffer      |     |

| SFR Definition 21.1. SPI0CFG: SPI0 Configuration                 |     |

| SFR Definition 21.2. SPI0CN: SPI0 Control                        |     |

| SFR Definition 21.3. SPI0CKR: SPI0 Clock Rate                    |     |

| SFR Definition 21.4. SPI0DAT: SPI0 Data                          | 190 |

| SFR Definition 22.1. TCON: Timer Contro                          | 199 |

| SFR Definition 22.2. TMOD: Timer Mode                            | 200 |

| SFR Definition 22.3. CKCON: Clock Control                        | 201 |

| SFR Definition 22.4. TL0: Timer 0 Low Byte                       | 202 |

| SFR Definition 22.5. TL1: Timer 1 Low Byte                       | 202 |

| SFR Definition 22.6. TH0: Timer 0 High Byte                      | 202 |

| SFR Definition 22.7. TH1: Timer 1 High Byte                      | 202 |

| SFR Definition 22.8. TMR2CN: Timer 2 Control                     |     |

| SFR Definition 22.9. TMR2RLL: Timer 2 Reload Register Low Byte   | 206 |

| SFR Definition 22.10. TMR2RLH: Timer 2 Reload Register High Byte |     |

| SFR Definition 22.11. TMR2L: Timer 2 Low Byte                    |     |

| SFR Definition 22.12. TMR2H Timer 2 High Byte                    |     |

| SFR Definition 22.13. TMR3CN: Timer 3 Control                    |     |

|                                                                  |     |

### 1. System Overview

C8051F350/1/2/3 devices are fully integrated mixed-signal System-on-a-Chip MCUs. Highlighted features are listed below. Refer to Table 1.1 for specific product feature selection.

- High-speed pipelined 8051-compatible microcontroller core (up to 50 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- 24 or 16-bit single-ended/differential ADC with analog multiplexer

- Two 8-bit Current Output DACs

- Precision programmable 24.5 MHz internal oscillator

- 8 kB of on-chip Flash memory

- 768 bytes of on-chip RAM

- SMBus/I2C, Enhanced UART, and SPI serial interfaces implemented in hardware

- Four general-purpose 16-bit timers

- Programmable counter/timer array (PCA) with three capture/compare modules and watchdog timer function

- On-chip power-on reset, V<sub>DD</sub> monitor, and temperature sensor

- On-chip voltage comparator

- 17 Port I/O (5 V tolerant)

With on-chip power-on reset,  $V_{DD}$  monitor, watchdog timer, and clock oscillator, the C8051F350/1/2/3 devices are truly stand-alone System-on-a-Chip solutions. The Flash memory can be reprogrammed even in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings.

The on-chip Silicon Labs 2-Wire (C2) Development Interface allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

Each device is specified for 2.7 to 3.6 V operation over the industrial temperature range (-45 to +85 °C). The Port I/O and /RST pins are tolerant of input signals up to 5 V. The C8051F350/1/2/3 are available in 28-pin QFN (also referred to as MLP or MLF) or 32-pin LQFP packaging, as shown in Figure 1.1 through Figure 1.4.

## 2. Absolute Maximum Ratings

### Table 2.1. Absolute Maximum Ratings

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                   | Min  | Тур | Max                   | Units |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----------------------|-------|--|--|--|--|

| Ambient temperature under bias                                                                                                                                                                                                                                                                                                                                                                              | -55  | _   | 125                   | °C    |  |  |  |  |

| Storage Temperature                                                                                                                                                                                                                                                                                                                                                                                         | -65  | _   | 150                   | °C    |  |  |  |  |

| Voltage on AIN0.0–AIN0.7, VREF+, and VREF– with respect to DGND                                                                                                                                                                                                                                                                                                                                             | -0.3 |     | V <sub>DD</sub> + 0.3 | V     |  |  |  |  |

| Voltage on any Port 0, 1, or 2 Pin or /RST with respect to DGND                                                                                                                                                                                                                                                                                                                                             | -0.3 |     | 5.8                   | V     |  |  |  |  |

| Voltage on V <sub>DD</sub> with respect to DGND                                                                                                                                                                                                                                                                                                                                                             | -0.3 | _   | 4.2                   | V     |  |  |  |  |

| Voltage on AV+ with respect to AGND                                                                                                                                                                                                                                                                                                                                                                         | -0.3 | _   | 4.2                   | V     |  |  |  |  |

| Maximum output current sunk by any Port 0, 1, or 2 pin                                                                                                                                                                                                                                                                                                                                                      | —    | _   | 100                   | mA    |  |  |  |  |

| Maximum output current sunk by any other I/O pin                                                                                                                                                                                                                                                                                                                                                            | _    |     | 50                    | mA    |  |  |  |  |

| Maximum output current sourced by any Port 0, 1, or 2 pin                                                                                                                                                                                                                                                                                                                                                   | —    | _   | 100                   | mA    |  |  |  |  |

| Maximum output current sourced by any other I/O pin                                                                                                                                                                                                                                                                                                                                                         |      |     | 50                    | mA    |  |  |  |  |

| Maximum Total current through V <sub>DD</sub> , AV+, DGND, and AGND                                                                                                                                                                                                                                                                                                                                         | —    | _   | 500                   | mA    |  |  |  |  |

| Note:       Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.<br>This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. |      |     |                       |       |  |  |  |  |

|        | Pin Nu         | mbers          |                  |                                                                                     |  |

|--------|----------------|----------------|------------------|-------------------------------------------------------------------------------------|--|

| Name   | 'F350<br>'F352 | 'F351<br>'F353 | Туре             | Description                                                                         |  |

| P0.6/  | 19             | 15             | D I/O or<br>A In | Port 0.6. See Port I/O Section for a complete description.                          |  |

| CNVSTR |                |                | D In             | External Convert Start Input for IDACs (See IDAC Section for complete description). |  |

| P0.7   | 20             | 16             | D I/O or<br>A In | Port 0.7. See Port I/O Section for a complete description.                          |  |

| P1.0/  | 23             | 19             | D I/O or<br>A In | Port 1.0. See Port I/O Section for a complete description.                          |  |

| AIN0.4 |                |                | A In             | ADC0 Input Channel 4 (C8051F351/3 - See ADC0 Section for complete description).     |  |

| P1.1/  | 24             | 20             | D I/O or<br>A In | Port 1.1. See Port I/O Section for a complete description.                          |  |

| AIN0.5 |                |                | A In             | ADC0 Input Channel 5 (C8051F351/3 - See ADC0 Section for complete description).     |  |

| P1.2/  | 25             | 21             | D I/O or<br>A In | Port 1.2. See Port I/O Section for a complete description.                          |  |

| AIN0.6 |                |                | A In             | ADC0 Input Channel 6 (C8051F351/3 - See ADC0 Section for complete description).     |  |

| P1.3/  | 26             | 22             | D I/O or<br>A In | r Port 1.3. See Port I/O Section for a complete description.                        |  |

| AIN0.7 |                |                | A In             | ADC0 Input Channel 7 (C8051F351/3 - See ADC0 Section for complete description).     |  |

| P1.4   | 27             | 23             | D I/O or<br>A In | Port 1.4. See Port I/O Section for a complete description.                          |  |

| P1.5   | 28             | 24             | D I/O or<br>A In | Port 1.5. See Port I/O Section for a complete description.                          |  |

| P1.6/  | 29             | 25             | D I/O or<br>A In | Port 1.6. See Port I/O Section for a complete description.                          |  |

| IDA0   |                |                | A Out            | IDAC0 Output (See IDAC Section for complete description).                           |  |

| P1.7/  | 30             | 26             | D I/O or<br>A In | Port 1.7. See Port I/O Section for a complete description.                          |  |

| IDA1   |                |                | A Out            | IDAC1 Output (See IDAC Section for complete description).                           |  |

| Input Voltage* (AIN+ – AIN–)                                                  | 24-bit Output Word (C8051F350/1) | 16-bit Output Word (C8051F352/3) |  |  |  |  |

|-------------------------------------------------------------------------------|----------------------------------|----------------------------------|--|--|--|--|

| VREF – 1 LSB                                                                  | 0xFFFFF                          | 0xFFFF                           |  |  |  |  |

| VREF / 2                                                                      | 0x800000                         | 0x8000                           |  |  |  |  |

| +1 LSB                                                                        | 0x000001                         | 0x0001                           |  |  |  |  |

| 0                                                                             | 0x000000                         | 0x0000                           |  |  |  |  |

| *Note: Input Voltage is voltage at ADC inputs after amplification by the PGA. |                                  |                                  |  |  |  |  |

#### Table 5.1. ADC0 Unipolar Output Word Coding (AD0POL = 0)

#### Table 5.2. ADC0 Bipolar Output Word Coding (AD0POL = 1)

| Input Voltage* (AIN+ – AIN–)       | 24-bit Output Word (C8051F350/1)          | 16-bit Output Word (C8051F352/3) |

|------------------------------------|-------------------------------------------|----------------------------------|

| VREF – 1 LSB                       | 0x7FFFFF                                  | 0x7FFF                           |

| VREF / 2                           | 0x400000                                  | 0x4000                           |

| +1 LSB                             | 0x000001                                  | 0x0001                           |

| 0                                  | 0x000000                                  | 0x0000                           |

| –1 LSB                             | 0xFFFFF                                   | 0xFFFF                           |

| –VREF / 2                          | 0xC00000                                  | 0xC000                           |

| –VREF                              | 0x800000                                  | 0x8000                           |

| *Note: Input Voltage is voltage at | ADC inputs after amplification by the PGA | λ.                               |

#### 5.3.1. Error Conditions

Any errors during a conversion or calibration are indicated using bits in the ADC0STA register. The AD0S3C flag will be set to '1' if there is a SINC3 filter clip during the conversion. Likewise, the AD0FFC flag will be set to '1' if there is a Fast filter clip during the conversion. A filter clip occurs whenever an internal filter register overflows during a conversion. The AD0OVR flag will be set to '1' if an ADC overrun condition occurs. An overrun occurs if the end of a conversion is reached while the AD0INT flag is still set to '1' from the previous conversion. If the data registers have not been read, the new data values will be updated, and the previous conversion will be lost. The general AD0ERR flag indicates that an AD0S3C, AD0FFC, or AD0OVR error condition has occurred, or that a calibration resulted in a value that was beyond the limits of the offset or gain register. The data output registers are updated at the end of every conversion regardless of whether or not an error occurs.

#### 5.4. Offset DAC

An 8-bit offset DAC is included, which can be used for offset correction up to approximately  $\pm 1/2$  of the ADC's input range on any PGA gain setting. The ADC0DAC register (SFR Definition 5.7) controls the offset DAC voltage. The register is decoded as a signed binary word. The MSB (bit 7) determines the sign of the DAC magnitude (0 = positive, 1 = negative), and the remaining seven bits (bits 6–0) determine the magnitude. Each LSB of the offset DAC is equivalent to approximately 0.4% of the ADC's input span. A write to the ADC0DAC register initiates a change on the offset DAC output.

#### 5.5. Burnout Current Sources

The burnout current sources can be used to detect an open circuit or short circuit at the ADC inputs. The burnout current sources are enabled by setting the AD0BCE bit in register ADC0CN to '1' (SFR Definition 5.1). The positive-channel burnout current source sources approximately 2  $\mu$ A on AIN+, and the negative-channel burnout current sinks approximately 2  $\mu$ A on AIN–. If an open circuit exists between AIN+ and AIN– when the burnout current sources are enabled, the ADC will read a full scale positive value. If a short-circuit exists between AIN+ and AIN– when the burnout current sources should be disabled during normal ADC measurements.

#### SFR Definition 5.2. ADC0CF: ADC0 Configuration

#### SFR Definition 5.4. ADC0CLK: ADC0 Modulator Clock Divisor

| R/W         | R/W                                                                         | R/W                                                        | R/W                                                        | R/W                                                          | R/W                                    | R/W                         | R/W        | Reset Value |

|-------------|-----------------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------|-----------------------------|------------|-------------|

|             |                                                                             |                                                            | ADC                                                        | 0CLK                                                         |                                        |                             |            | 00000000    |

| Bit7        | Bit6                                                                        | Bit5                                                       | Bit4                                                       | Bit3                                                         | Bit2                                   | Bit1                        | Bit0       |             |

|             |                                                                             |                                                            |                                                            |                                                              |                                        |                             | SFR Addres | s: 0xF7     |

| (<br>F<br>נ | This register<br>SYSCLK). T<br>For optimal p<br>equal to 2.45<br>The system | The input sig<br>performanc<br>576 MHz (m<br>clock is divi | gnal is sam<br>e, the divide<br>nodulator sa<br>ded accord | pled by the<br>er should be<br>ampling rate<br>ling to the e | modulator a<br>chosen su<br>= 19.2 kHz | at a frequer<br>ch that the | ncy of MD  |             |

|             | Modulator<br>letails.                                                       | Sampling                                                   | Rate is not                                                | the ADC C                                                    | output Wor                             | d Rate. See                 | e Section  | 5.1.4 for   |

#### SFR Definition 5.5. ADC0DECH: ADC0 Decimation Ratio Register High Byte

| R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W  | R/W  | R/W  | R/W  | R/W    | R/W   | R/W          | Reset Value |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|--------|-------|--------------|-------------|

| —                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | —    | _    | _    | _    | DECI10 | DECI9 | DECI8        | 00000111    |

| Bit7                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Bit6 | Bit5 | Bit4 | Bit3 | Bit2   | Bit1  | Bit0         | -           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |      |      |      |        |       | SFR Address: | 0x9B        |

| <ul> <li>Bits 7–3: Unused: Read = 00000b, Write = don't care.</li> <li>Bits 2–0: DECI[10:8]: ADC0 Decimation Ratio Register, Bits 10–8.<br/>This register contains the high bits of the 11-bit ADC Decimation Ratio. The decimation ratio determines the output word rate of ADC0, based on the Modulator Clock (MDCLK). See the ADC0DECL register description for more information.</li> <li>This SFR can only be modified when ADC0 is in IDLE mode.</li> </ul> |      |      |      |      |        |       |              |             |

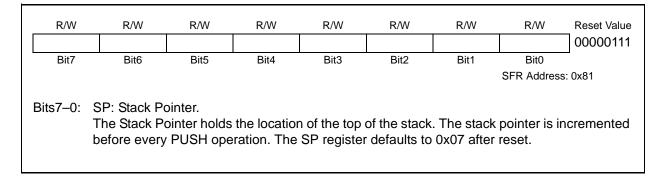

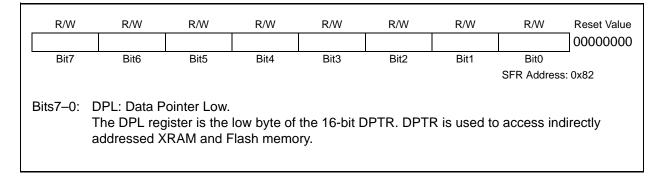

#### **10.2.** Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should not be set to logic I. Future product versions may use these bits to implement new features in which case the reset value of the bit will be logic 0, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the datasheet associated with their corresponding system function.

#### SFR Definition 10.1. SP: Stack Pointer

#### SFR Definition 10.2. DPL: Data Pointer Low Byte

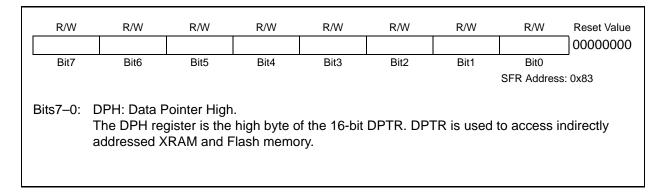

#### SFR Definition 10.3. DPH: Data Pointer High Byte

#### 11.2. Data Memory

The C8051F350/1/2/3 includes 256 bytes of internal RAM mapped into the data memory space from 0x00 through 0xFF. The lower 128 bytes of data memory are used for general purpose registers and scratch pad memory. Either direct or indirect addressing may be used to access the lower 128 bytes of data memory. Locations 0x00 through 0x1F are addressable as four banks of general purpose registers, each bank consisting of eight byte-wide registers. The next 16 bytes, locations 0x20 through 0x2F, may either be addressed as bytes or as 128 bit locations accessible with the direct addressing mode.

The upper 128 bytes of data memory are accessible only by indirect addressing. This region occupies the same address space as the Special Function Registers (SFRs) but is physically separate from the SFR space. The addressing mode used by an instruction when accessing locations above 0x7F determines whether the CPU accesses the upper 128 bytes of data memory space or the SFRs. Instructions that use direct addressing will access the SFR space. Instructions using indirect addressing above 0x7F access the upper 128 bytes of data memory organization of the C8051F350/1/2/3.

The C8051F35x family also includes 512 bytes of on-chip RAM mapped into the external memory (XDATA) space. This RAM can be accessed using the CIP-51 core's MOVX instruction. More information on the XRAM memory can be found in Section "16. External RAM' on page 127.

#### 11.3. General Purpose Registers

The lower 32 bytes of data memory (locations 0x00 through 0x1F) may be addressed as four banks of general-purpose registers. Each bank consists of eight byte-wide registers designated R0 through R7. Only one of these banks may be enabled at a time. Two bits in the program status word, RS0 (PSW.3) and RS1 (PSW.4), select the active register bank (see description of the PSW in SFR Definition 10.4). This allows fast context switching when entering subroutines and interrupt service routines. Indirect addressing modes use registers R0 and R1 as index registers.

#### 11.4. Bit Addressable Locations

In addition to direct access to data memory organized as bytes, the sixteen data memory locations at 0x20 through 0x2F are also accessible as 128 individually addressable bits. Each bit has a bit address from 0x00 to 0x7F. Bit 0 of the byte at 0x20 has bit address 0x00 while bit 7 of the byte at 0x20 has bit address 0x07. Bit 7 of the byte at 0x2F has bit address 0x7F. A bit access is distinguished from a full byte access by the type of instruction used (bit source or destination operands as opposed to a byte source or destination).

The MCS-51<sup>™</sup> assembly language allows an alternate notation for bit addressing of the form XX.B where XX is the byte address and B is the bit position within the byte. For example, the instruction:

MOV C, 22.3h

moves the Boolean value at 0x13 (bit 3 of the byte at location 0x22) into the Carry flag.

#### 11.5. Stack

A programmer's stack can be located anywhere in the 256-byte data memory. The stack area is designated using the Stack Pointer (SP, 0x81) SFR. The SP will point to the last location used. The next value pushed on the stack is placed at SP+1 and then SP is incremented. A reset initializes the stack pointer to location 0x07. Therefore, the first value pushed on the stack is placed at location 0x08, which is also the first register (R0) of register bank 1. Thus, if more than one register bank is to be used, the SP should be initialized to a location in the data memory not being used for data storage. The stack depth can extend up to 256 bytes.

|        | R/W                                                               | DAA               | DAM           | DAM            | DAM           | D 44/      | DAA        | Reset Value |  |  |  |

|--------|-------------------------------------------------------------------|-------------------|---------------|----------------|---------------|------------|------------|-------------|--|--|--|

| R      | PSPI0                                                             | R/W<br>PT2        | R/W<br>PS0    | R/W<br>PT1     | R/W<br>PX1    | R/W<br>PT0 | R/W<br>PX0 | 10000000    |  |  |  |

|        | FSFIU                                                             | FIZ               | F 30          | FII            | FAI           | FIU        | FAU        | Bit         |  |  |  |

| Bit7   | Bit6                                                              | Bit5              | Bit4          | Bit3           | Bit2          | Bit1       | Bit0       | Addressable |  |  |  |

|        |                                                                   | SFR Address: 0xB8 |               |                |               |            |            |             |  |  |  |

|        |                                                                   |                   |               |                |               |            |            |             |  |  |  |

| Bit 7: | UNUSED. Read = 1, Write = don't care.                             |                   |               |                |               |            |            |             |  |  |  |

| Bit 6: | PSPI0: Seria                                                      |                   |               |                | rupt Priority | Control.   |            |             |  |  |  |

|        | This bit sets                                                     | the priority      | of the SPI0   | interrupt.     | . ,           |            |            |             |  |  |  |

|        | 0: SPI0 inter                                                     | rupt set to       | low priority  | evel.          |               |            |            |             |  |  |  |

|        | 1: SPI0 inter                                                     | rupt set to       | high priority | level.         |               |            |            |             |  |  |  |

| Bit 5: | PT2: Timer 2                                                      | •                 |               |                |               |            |            |             |  |  |  |

|        | This bit sets                                                     |                   |               |                | t.            |            |            |             |  |  |  |

|        | 0: Timer 2 in                                                     |                   |               |                |               |            |            |             |  |  |  |

|        | 1: Timer 2 in                                                     |                   | • •           |                |               |            |            |             |  |  |  |

| Bit 4: | PS0: UARTO                                                        | •                 |               |                |               |            |            |             |  |  |  |

|        | This bit sets                                                     |                   |               |                | t.            |            |            |             |  |  |  |

|        | 0: UART0 int                                                      |                   | •             | •              |               |            |            |             |  |  |  |

| D:4 0. | 1: UART0 int                                                      | •                 | • •           |                |               |            |            |             |  |  |  |

| Bit 3: | PT1: Timer 1<br>This bit sets                                     | •                 |               |                | +             |            |            |             |  |  |  |

|        | 0: Timer 1 in                                                     |                   |               |                | ι.            |            |            |             |  |  |  |

|        | 1: Timer 1 in                                                     |                   |               |                |               |            |            |             |  |  |  |

| Bit 2: | PX1: Externa                                                      |                   | • •           |                |               |            |            |             |  |  |  |

| Dit Z. | This bit sets                                                     |                   |               |                | ot 1 interrup | t          |            |             |  |  |  |

|        | 0: External Ir                                                    |                   |               |                |               |            |            |             |  |  |  |

|        | 1: External Ir                                                    |                   |               |                |               |            |            |             |  |  |  |

| Bit 1: | PT0: Timer 0                                                      |                   | • •           |                |               |            |            |             |  |  |  |

|        | This bit sets                                                     | •                 |               |                | t.            |            |            |             |  |  |  |

|        | 0: Timer 0 in                                                     |                   |               |                |               |            |            |             |  |  |  |

|        | 1: Timer 0 interrupt set to high priority level.                  |                   |               |                |               |            |            |             |  |  |  |

| Bit 0: | PX0: Externa                                                      | al Interrupt      | 0 Priority C  | ontrol.        |               |            |            |             |  |  |  |

|        | This bit sets the priority of the External Interrupt 0 interrupt. |                   |               |                |               |            |            |             |  |  |  |

|        | 0: External Ir                                                    |                   |               |                |               |            |            |             |  |  |  |

|        | 1: External Ir                                                    | nterrupt 0 s      | et to high p  | riority level. |               |            |            |             |  |  |  |

|        |                                                                   |                   |               |                |               |            |            |             |  |  |  |

SFR Definition 12.2. IP: Interrupt Priority

| SFR Definition 12.5. IT01CF: INT0/INT1 Configuration | า |

|------------------------------------------------------|---|

|------------------------------------------------------|---|

| R/W       | R/W                                 | R/W          | R/W           | R/W            | R/W            | R/W            | R/W          | Reset Valu |

|-----------|-------------------------------------|--------------|---------------|----------------|----------------|----------------|--------------|------------|

| IN1PL     | IN1SL2                              | IN1SL1       | IN1SL0        | IN0PL          | IN0SL2         | IN0SL1         | IN0SL0       | 0000000    |

| Bit7      | Bit6                                | Bit5         | Bit4          | Bit3           | Bit2           | Bit1           | Bit0         |            |

|           |                                     |              |               |                |                |                | SFR Address  | :: 0xE4    |

| Note: Ret | fer to SFR Definit                  | tion 22.1 fc | or INT0/1 edg | ge- or level-s | ensitive inter | rupt selectior | ۱.           |            |

|           |                                     |              |               |                |                |                |              |            |

| Bit 7:    | IN1PL: /INT1 F                      | Polarity     |               |                |                |                |              |            |

|           | 0: /INT1 input i                    | is active l  | OW.           |                |                |                |              |            |

|           | 1: /INT1 input i                    |              |               |                |                |                |              |            |

| 3its 6–4: | IN1SL2-0: /IN                       |              |               |                |                |                |              |            |

|           | These bits sele                     |              |               |                |                |                |              |            |

|           | pendent of the                      |              |               |                |                |                |              |            |

|           | peripheral that                     |              |               |                |                |                |              |            |

|           | assign the Por                      |              |               |                |                | the selected   | i pin (accor | npiisnea b |

|           | setting to '1' th                   | le corresp   | onaing bit i  | n register F   | 05KIP).        |                |              |            |

|           | IN1SL2-0                            | /INT         | 1 Port Pin    |                |                |                |              |            |

|           | 000                                 |              | P0.0          |                |                |                |              |            |

|           | 001                                 |              | P0.1          |                |                |                |              |            |

|           | 010                                 |              | P0.2          |                |                |                |              |            |

|           | 011                                 |              | P0.3          |                |                |                |              |            |

|           | 100                                 |              | P0.4          |                |                |                |              |            |

|           | 101                                 |              | P0.5          |                |                |                |              |            |

|           | 110                                 |              | P0.6          |                |                |                |              |            |

|           | 111                                 |              | P0.7          |                |                |                |              |            |

|           |                                     |              |               |                |                |                |              |            |

| Bit 3:    | INOPL: /INTO F                      | Polarity     |               |                |                |                |              |            |

|           | 0: /INT0 interru                    | upt is activ | ve low.       |                |                |                |              |            |

|           | 1: /INT0 interru                    | •            | •             |                |                |                |              |            |

| 3its 2–0: | INT0SL2-0: /II                      |              |               |                |                |                |              |            |

|           | These bits sele                     |              |               |                |                |                |              |            |

|           | pendent of the                      |              |               |                |                |                |              |            |

|           | peripheral that                     |              | •             |                |                |                |              |            |

|           | assign the Por<br>setting to '1' th |              |               |                |                | ine selected   | i pin (accor | npiisned b |

|           | setting to 1 th                     | le collesp   |               | n legister r   | -03Kir).       |                |              |            |

|           | IN0SL2-0                            | /INT         | 0 Port Pin    |                |                |                |              |            |

|           | 000                                 |              | P0.0          |                |                |                |              |            |

|           | 001                                 |              | P0.1          |                |                |                |              |            |

|           | 010                                 | 1            | P0.2          |                |                |                |              |            |

|           | 011                                 |              | P0.3          |                |                |                |              |            |

|           | 100                                 |              | P0.4          |                |                |                |              |            |

|           |                                     |              |               |                |                |                |              |            |

|           | 101                                 |              | P0.5          |                |                |                |              |            |

|           | 101<br>110                          |              | P0.5<br>P0.6  |                |                |                |              |            |

### Table 18.1. Port I/O DC Electrical Characteristics

$V_{DD}$  = 2.7 to 3.6 V, –40 to +85 °C unless otherwise specified.

| Parameters            | Conditions                                                                                   | Min                                            | Тур                        | Max      | Units |

|-----------------------|----------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------|----------|-------|

| Output High Voltage   | $I_{OH} = -3 \text{ mA}$ , Port I/O push-pull                                                | V <sub>DD</sub> – 0.7<br>V <sub>DD</sub> – 0.1 | _                          |          | V     |

| Output high voltage   | I <sub>OH</sub> = −10 µA, Port I/O push-pull<br>I <sub>OH</sub> = −10 mA, Port I/O push-pull | v <sub>DD</sub> = 0.1                          | —<br>V <sub>DD</sub> – 0.8 | _        |       |

|                       | I <sub>OL</sub> = 8.5 mA                                                                     | _                                              | —                          | 0.6      |       |

| Output Low Voltage    | I <sub>OL</sub> = 10 μΑ                                                                      | —                                              | —                          | 0.1      | V     |

|                       | I <sub>OL</sub> = 25 mA                                                                      |                                                | 1.0                        |          |       |

| Input High Voltage    |                                                                                              | 2.0                                            | _                          |          | V     |

| Input Low Voltage     |                                                                                              | —                                              | _                          | 0.8      | V     |

| Input Leakage Current | Weak Pull-up Off<br>Weak Pull-up On, V <sub>IN</sub> = 0 V                                   |                                                | 25                         | ±1<br>50 | μA    |

#### 20.1. Enhanced Baud Rate Generation

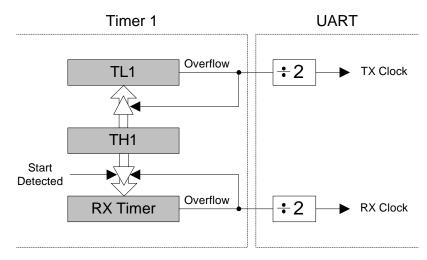

The UART0 baud rate is generated by Timer 1 in 8-bit auto-reload mode. The TX clock is generated by TL1; the RX clock is generated by a copy of TL1 (shown as RX Timer in Figure 20.2), which is not useraccessible. Both TX and RX Timer overflows are divided by two to generate the TX and RX baud rates. The RX Timer runs when Timer 1 is enabled, and uses the same reload value (TH1). However, an RX Timer reload is forced when a START condition is detected on the RX pin. This allows a receive to begin any time a START is detected, independent of the TX Timer state.

Figure 20.2. UART0 Baud Rate Logic

Timer 1 should be configured for Mode 2, 8-bit auto-reload (see Section "22.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload' on page 197). The Timer 1 reload value should be set so that overflows will occur at two times the desired UART baud rate frequency. Note that Timer 1 may be clocked by one of six sources: SYSCLK, SYSCLK / 4, SYSCLK / 12, SYSCLK / 48, the external oscillator clock / 8, or an external input T1. The UART0 baud rate is determined by Equation 20.1-A and Equation 20.1-B.

A) UartBaudRate =

$$\frac{1}{2} \times T1_Overflow_Rate$$

B) T1\_Overflow\_Rate =  $\frac{T1_{CLK}}{256 - TH1}$

#### Equation 20.1. UART0 Baud Rate

Where  $T1_{CLK}$  is the frequency of the clock supplied to Timer 1, and T1H is the high byte of Timer 1 (reload value). Timer 1 clock frequency is selected as described in Section "22. Timers' on page 195. A quick reference for typical baud rates and system clock frequencies is given in Table 20.1 through Table 20.6. Note that the internal oscillator may still generate the system clock when the external oscillator is driving Timer 1.

|                | Frequency: 11.0592 MHz       |                      |                                  |                       |                                     |      |                                  |

|----------------|------------------------------|----------------------|----------------------------------|-----------------------|-------------------------------------|------|----------------------------------|

|                | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select)* | T1M* | Timer 1<br>Reload<br>Value (hex) |

|                | 230400                       | 0.00%                | 48                               | SYSCLK                | XX                                  | 1    | 0xE8                             |

|                | 115200                       | 0.00%                | 96                               | SYSCLK                | XX                                  | 1    | 0xD0                             |

|                | 57600                        | 0.00%                | 192                              | SYSCLK                | XX                                  | 1    | 0xA0                             |

| om<br>sc.      | 28800                        | 0.00%                | 384                              | SYSCLK                | XX                                  | 1    | 0x40                             |

| ΞŐ             | 14400                        | 0.00%                | 768                              | SYSCLK / 12           | 00                                  | 0    | 0xE0                             |

| CLK<br>rnal    | 9600                         | 0.00%                | 1152                             | SYSCLK / 12           | 00                                  | 0    | 0xD0                             |

| SYS(<br>Exter  | 2400                         | 0.00%                | 4608                             | SYSCLK / 12           | 00                                  | 0    | 0x40                             |

| у<br>М         | 1200                         | 0.00%                | 9216                             | SYSCLK / 48           | 10                                  | 0    | 0xA0                             |

|                | 230400                       | 0.00%                | 48                               | EXTCLK / 8            | 11                                  | 0    | 0xFD                             |

| from<br>Jsc.   | 115200                       | 0.00%                | 96                               | EXTCLK / 8            | 11                                  | 0    | 0xFA                             |

|                | 57600                        | 0.00%                | 192                              | EXTCLK / 8            | 11                                  | 0    | 0xF4                             |

| SCLK<br>rnal ( | 28800                        | 0.00%                | 384                              | EXTCLK / 8            | 11                                  | 0    | 0xE8                             |

| 0 0            | 14400                        | 0.00%                | 768                              | EXTCLK / 8            | 11                                  | 0    | 0xD0                             |

| SY<br>Inte     | 9600                         | 0.00%                | 1152                             | EXTCLK / 8            | 11                                  | 0    | 0xB8                             |

# Table 20.5. Timer Settings for Standard Baud RatesUsing an External 11.0592 MHz Oscillator

X = Don't care

\*Note: SCA1–SCA0 and T1M bit definitions can be found in Section 22.1.

# Table 20.6. Timer Settings for Standard Baud RatesUsing an External 3.6864 MHz Oscillator

|                                | Frequency: 3.6864 MHz        |                        |                                  |                        |                                     |      |                                  |

|--------------------------------|------------------------------|------------------------|----------------------------------|------------------------|-------------------------------------|------|----------------------------------|

|                                | Target<br>Baud Rate<br>(bps) | Baud<br>Rate%<br>Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source  | SCA1–SCA0<br>(pre-scale<br>select)* | T1M* | Timer 1<br>Reload<br>Value (hex) |

|                                | 230400                       | 0.00%                  | 16                               | SYSCLK                 | XX                                  | 1    | 0xF8                             |

|                                | 115200                       | 0.00%                  | 32                               | SYSCLK                 | XX                                  | 1    | 0xF0                             |

|                                | 57600                        | 0.00%                  | 64                               | SYSCLK                 | XX                                  | 1    | 0xE0                             |

| from<br>Osc.                   | 28800                        | 0.00%                  | 128                              | SYSCLK                 | XX                                  | 1    | 0xC0                             |

|                                | 14400                        | 0.00%                  | 256                              | SYSCLK                 | XX                                  | 1    | 0x80                             |

| SYSCLK<br>External             | 9600                         | 0.00%                  | 384                              | SYSCLK                 | XX                                  | 1    | 0x40                             |

| SYSCL <sup>k</sup><br>External | 2400                         | 0.00%                  | 1536                             | SYSCLK / 12            | 00                                  | 0    | 0xC0                             |

| Ϋ́́                            | 1200                         | 0.00%                  | 3072                             | SYSCLK / 12            | 00                                  | 0    | 0x80                             |

|                                | 230400                       | 0.00%                  | 16                               | EXTCLK / 8             | 11                                  | 0    | 0xFF                             |

| E .;                           | 115200                       | 0.00%                  | 32                               | EXTCLK / 8             | 11                                  | 0    | 0xFE                             |

| < froi<br>Osc.                 | 57600                        | 0.00%                  | 64                               | EXTCLK / 8             | 11                                  | 0    | 0xFC                             |

| al e                           | 28800                        | 0.00%                  | 128                              | EXTCLK / 8             | 11                                  | 0    | 0xF8                             |

| SYSCLK from<br>Internal Osc.   | 14400                        | 0.00%                  | 256                              | EXTCLK / 8             | 11                                  | 0    | 0xF0                             |

| SY<br>Int                      | 9600                         | 0.00%                  | 384                              | EXTCLK / 8             | 11                                  | 0    | 0xE8                             |

| SΥ<br>Int                      | 9600                         | 0.00%                  | 384                              | EXTCLK / 8<br>X = Don' |                                     | 0    |                                  |

X = Don't care

\*Note: SCA1–SCA0 and T1M bit definitions can be found in Section 22.1.

#### 22.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

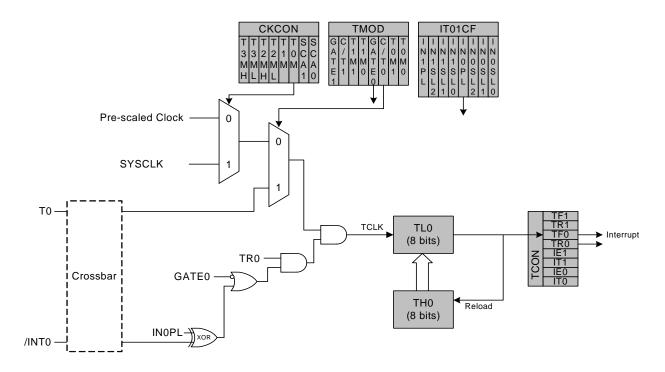

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 (TCON.5) is set and the counter in TL0 is reloaded from TH0. If Timer 0 interrupts are enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0.

Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0. Setting the TR0 bit (TCON.4) enables the timer when either GATE0 (TMOD.3) is logic 0 or when the input signal /INT0 is active as defined by bit IN0PL in register IT01CF (see Section "12.5. External Interrupts' on page 111 for details on the external input signals /INT0 and /INT1).

Figure 22.2. T0 Mode 2 Block Diagram

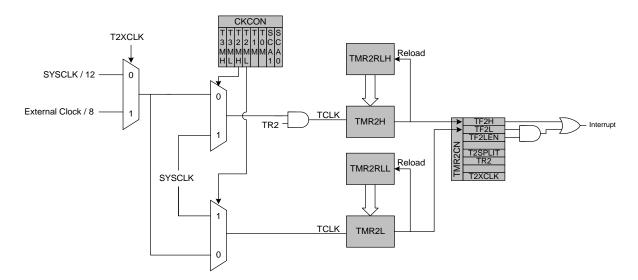

#### 22.2.2. 8-bit Timers with Auto-Reload

When T2SPLIT is set, Timer 2 operates as two 8-bit timers (TMR2H and TMR2L). Both 8-bit timers operate in auto-reload mode as shown in Figure 22.5. TMR2RLL holds the reload value for TMR2L; TMR2RLH holds the reload value for TMR2H. The TR2 bit in TMR2CN handles the run control for TMR2H. TMR2L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 2 Clock Select bits (T2MH and T2ML in CKCON) select either SYSCLK or the clock defined by the Timer 2 External Clock Select bit (T2XCLK in TMR2CN), as follows:

| T2MH | T2XCLK | TMR2H Clock        |

|------|--------|--------------------|

|      |        | Source             |

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

| T2ML | T2XCLK | TMR2L Clock<br>Source |

|------|--------|-----------------------|

| 0    | 0      | SYSCLK / 12           |

| 0    | 1      | External Clock / 8    |

| 1    | Х      | SYSCLK                |

The TF2H bit is set when TMR2H overflows from 0xFF to 0x00; the TF2L bit is set when TMR2L overflows from 0xFF to 0x00. When Timer 2 interrupts are enabled (IE.5), an interrupt is generated each time TMR2H overflows. If Timer 2 interrupts are enabled and TF2LEN (TMR2CN.5) is set, an interrupt is generated each time either TMR2L or TMR2H overflows. When TF2LEN is enabled, software must check the TF2H and TF2L flags to determine the source of the Timer 2 interrupt. The TF2H and TF2L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 22.5. Timer 2 8-Bit Mode Block Diagram

#### 22.3. Timer 3

Timer 3 is a 16-bit timer formed by two 8-bit SFRs: TMR3L (low byte) and TMR3H (high byte). Timer 3 may operate in 16-bit auto-reload mode or (split) 8-bit auto-reload mode. The T3SPLIT bit (TMR3CN.3) defines the Timer 3 operation mode.

Timer 3 may be clocked by the system clock, the system clock divided by 12, or the external oscillator source divided by 8. The external clock mode is ideal for real-time clock (RTC) functionality, where the internal oscillator drives the system clock while Timer 3 (and/or the PCA) is clocked by an external precision oscillator. Note that the external oscillator source divided by 8 is synchronized with the system clock.

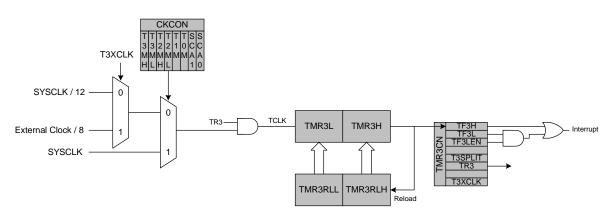

#### 22.3.1. 16-bit Timer with Auto-Reload

When T3SPLIT (TMR3CN.3) is zero, Timer 3 operates as a 16-bit timer with auto-reload. Timer 3 can be clocked by SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 3 reload registers (TMR3RLH and TM3RLL) is loaded into the Timer 3 register as shown in Figure 22.6, and the Timer 3 High Byte Overflow Flag (TMR3CN.7) is set. If Timer 3 interrupts are enabled, an interrupt will be generated each Timer 3 overflow. Additionally, if Timer 3 interrupts are enabled and the TF3LEN bit is set (TMR3CN.5), an interrupt will be generated each time the lower 8 bits (TMR3L) overflow from 0xFF to 0x00.

Figure 22.6. Timer 3 16-Bit Mode Block Diagram

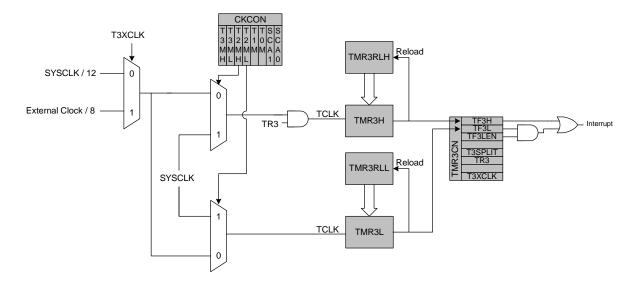

#### 22.3.2. 8-bit Timers with Auto-Reload

When T3SPLIT is set, Timer 3 operates as two 8-bit timers (TMR3H and TMR3L). Both 8-bit timers operate in auto-reload mode as shown in Figure 22.7. TMR3RLL holds the reload value for TMR3L; TMR3RLH holds the reload value for TMR3H. The TR3 bit in TMR3CN handles the run control for TMR3H. TMR3L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 3 Clock Select bits (T3MH and T3ML in CKCON) select either SYSCLK or the clock defined by the Timer 3 External Clock Select bit (T3XCLK in TMR3CN), as follows:

| T3MH | T3XCLK | TMR3H Clock        |

|------|--------|--------------------|

|      |        | Source             |

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

| T3ML | T3XCLK | TMR3L Clock<br>Source |

|------|--------|-----------------------|

| 0    | 0      | SYSCLK / 12           |

| 0    | 1      | External Clock / 8    |

| 1    | Х      | SYSCLK                |

The TF3H bit is set when TMR3H overflows from 0xFF to 0x00; the TF3L bit is set when TMR3L overflows from 0xFF to 0x00. When Timer 3 interrupts are enabled (IE.5), an interrupt is generated each time TMR3H overflows. If Timer 3 interrupts are enabled and TF3LEN (TMR3CN.5) is set, an interrupt is generated each time either TMR3L or TMR3H overflows. When TF3LEN is enabled, software must check the TF3H and TF3L flags to determine the source of the Timer 3 interrupt. The TF3H and TF3L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 22.7. Timer 3 8-Bit Mode Block Diagram

# C8051F350/1/2/3

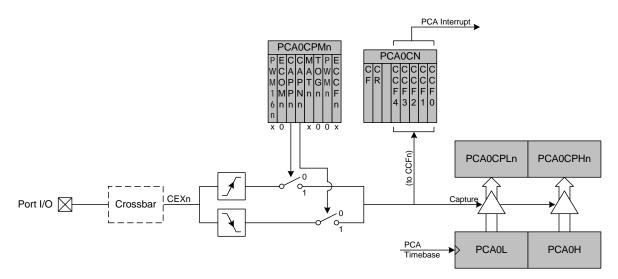

#### 23.2.1. Edge-triggered Capture Mode

In this mode, a valid transition on the CEXn pin causes the PCA to capture the value of the PCA counter/timer and load it into the corresponding module's 16-bit capture/compare register (PCA0CPLn and PCA0CPHn). The CAPPn and CAPNn bits in the PCA0CPMn register are used to select the type of transition that triggers the capture: low-to-high transition (positive edge), high-to-low transition (negative edge), or either transition (positive or negative edge). When a capture occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1 and an interrupt request is generated if CCF interrupts are enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. If both CAPPn and CAPNn bits are set to logic 1, then the state of the Port pin associated with CEXn can be read directly to determine whether a rising-edge or falling-edge caused the capture.

Figure 23.4. PCA Capture Mode Diagram

Note: The CEXn input signal must remain high or low for at least 2 system clock cycles to be recognized by the hardware.