# E. Keniconductor Corporation - LAMX01200E-3FTN256E Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - CPLDs (Complex</u> <u>Programmable Logic Devices)</u>

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixedfunction ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### Applications of Embedded - CPLDs

#### Details

| Product Status                  | Active                                                                         |

|---------------------------------|--------------------------------------------------------------------------------|

| Programmable Type               | In System Programmable                                                         |

| Delay Time tpd(1) Max           | 5.1 ns                                                                         |

| Voltage Supply - Internal       | 1.14V ~ 1.26V                                                                  |

| Number of Logic Elements/Blocks | -                                                                              |

| Number of Macrocells            | 600                                                                            |

| Number of Gates                 | -                                                                              |

| Number of I/O                   | 211                                                                            |

| Operating Temperature           | -40°C ~ 125°C (TA)                                                             |

| Mounting Type                   | Surface Mount                                                                  |

| Package / Case                  | 256-LBGA                                                                       |

| Supplier Device Package         | 256-FTBGA (17x17)                                                              |

| Purchase URL                    | https://www.e-xfl.com/product-detail/lattice-semiconductor/lamxo1200e-3ftn256e |

|                                 |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Modes of Operation**

Each Slice is capable of four modes of operation: Logic, Ripple, RAM, and ROM. The Slice in the PFF is capable of all modes except RAM. Table 2-2 lists the modes and the capability of the Slice blocks.

#### Table 2-2. Slice Modes

|           | Logic              | Ripple                | RAM     | ROM          |

|-----------|--------------------|-----------------------|---------|--------------|

| PFU Slice | LUT 4x2 or LUT 5x1 | 2-bit Arithmetic Unit | SP 16x2 | ROM 16x1 x 2 |

| PFF Slice | LUT 4x2 or LUT 5x1 | 2-bit Arithmetic Unit | N/A     | ROM 16x1 x 2 |

**Logic Mode:** In this mode, the LUTs in each Slice are configured as 4-input combinatorial lookup tables (LUT4). A LUT4 can have 16 possible input combinations. Any logic function with four inputs can be generated by programming this lookup table. Since there are two LUT4s per Slice, a LUT5 can be constructed within one Slice. Larger lookup tables such as LUT6, LUT7, and LUT8 can be constructed by concatenating other Slices.

**Ripple Mode:** Ripple mode allows the efficient implementation of small arithmetic functions. In ripple mode, the following functions can be implemented by each Slice:

- Addition 2-bit

- Subtraction 2-bit

- Add/Subtract 2-bit using dynamic control

- Up counter 2-bit

- Down counter 2-bit

- Ripple mode multiplier building block

- Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Two additional signals, Carry Generate and Carry Propagate, are generated per Slice in this mode, allowing fast arithmetic functions to be constructed by concatenating Slices.

**RAM Mode:** In this mode, distributed RAM can be constructed using each LUT block as a 16x2-bit memory. Through the combination of LUTs and Slices, a variety of different memories can be constructed.

The ispLEVER design tool supports the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2-3 shows the number of Slices required to implement different distributed RAM primitives. Figure 2-6 shows the distributed memory primitive block diagrams. Dual port memories involve the pairing of two Slices. One Slice functions as the read-write port, while the other companion Slice supports the read-only port. For more information on RAM mode in LA-MachXO devices, please see details of additional technical documentation at the end of this data sheet.

#### Table 2-3. Number of Slices Required For Implementing Distributed RAM

|                  | SPR16x2 | DPR16x2 |

|------------------|---------|---------|

| Number of Slices | 1       | 2       |

Note: SPR = Single Port RAM, DPR = Dual Port RAM

The ispLEVER design tool takes the output of the synthesis tool and places and routes the design. Generally, the place and route tool is completely automatic, although an interactive routing editor is available to optimize the design.

## **Clock/Control Distribution Network**

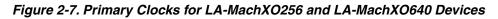

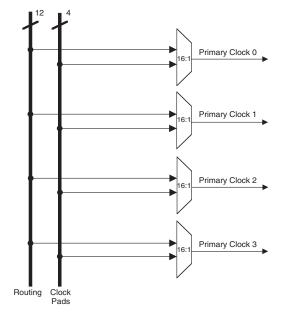

The LA-MachXO automotive family of devices provides global signals that are available to all PFUs. These signals consist of four primary clocks and four secondary clocks. Primary clock signals are generated from four 16:1 muxes as shown in Figure 2-7 and Figure 2-8. The available clock sources for the LA-MachXO256 and LA-MachXO640 devices are four dual function clock pins and 12 internal routing signals. The available clock sources for the LA-MachXO2280 devices are four dual function clock pins, up to nine internal routing signals and up to six PLL outputs.

Primary Clock 0 Primary Clock 1 16:1 Primary Clock 1 16:1 Primary Clock 2 16:1 Primary Clock 3 Bouting Clock PLL Pads Outputs

Figure 2-8. Primary Clocks for LA-MachXO1200 and LA-MachXO2280 Devices

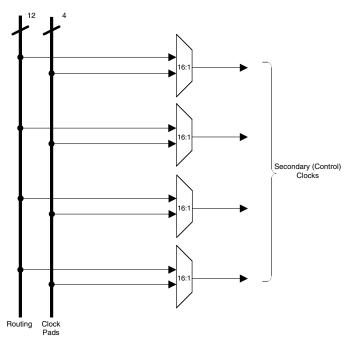

Four secondary clocks are generated from four 16:1 muxes as shown in Figure 2-9. Four of the secondary clock sources come from dual function clock pins and 12 come from internal routing.

Figure 2-9. Secondary Clocks for LA-MachXO Devices

| Signal       | I/O | Description                                                                                                 |

|--------------|-----|-------------------------------------------------------------------------------------------------------------|

| CLKI         | I   | Clock input from external pin or routing                                                                    |

| CLKFB        | I   | PLL feedback input from PLL output, clock net, routing/external pin or internal feedback from CLKINTFB port |

| RST          | I   | "1" to reset the input clock divider                                                                        |

| CLKOS        | 0   | PLL output clock to clock tree (phase shifted/duty cycle changed)                                           |

| CLKOP        | 0   | PLL output clock to clock tree (No phase shift)                                                             |

| CLKOK        | 0   | PLL output to clock tree through secondary clock divider                                                    |

| LOCK         | 0   | "1" indicates PLL LOCK to CLKI                                                                              |

| CLKINTFB     | 0   | Internal feedback source, CLKOP divider output before CLOCKTREE                                             |

| DDAMODE      | I   | Dynamic Delay Enable. "1": Pin control (dynamic), "0": Fuse Control (static)                                |

| DDAIZR       | I   | Dynamic Delay Zero. "1": delay = 0, "0": delay = on                                                         |

| DDAILAG      | 1   | Dynamic Delay Lag/Lead. "1": Lag, "0": Lead                                                                 |

| DDAIDEL[2:0] |     | Dynamic Delay Input                                                                                         |

#### Table 2-5. PLL Signal Descriptions

For more information on the PLL, please see details of additional technical documentation at the end of this data sheet.

### sysMEM Memory

The LA-MachXO1200 and LA-MachXO2280 devices contain sysMEM Embedded Block RAMs (EBRs). The EBR consists of a 9-Kbit RAM, with dedicated input and output registers.

#### sysMEM Memory Block

The sysMEM block can implement single port, dual port, pseudo dual port, or FIFO memories. Each block can be used in a variety of depths and widths as shown in Table 2-6.

#### Table 2-6. sysMEM Block Configurations

| Memory Mode      | Configurations |  |  |  |

|------------------|----------------|--|--|--|

|                  | 8,192 x 1      |  |  |  |

|                  | 4,096 x 2      |  |  |  |

| Single Port      | 2,048 x 4      |  |  |  |

|                  | 1,024 x 9      |  |  |  |

|                  | 512 x 18       |  |  |  |

|                  | 256 x 36       |  |  |  |

|                  | 8,192 x 1      |  |  |  |

| True Dual Port   | 4,096 x 2      |  |  |  |

|                  | 2,048 x 4      |  |  |  |

|                  | 1,024 x 9      |  |  |  |

|                  | 512 x 18       |  |  |  |

|                  | 8,192 x 1      |  |  |  |

|                  | 4,096 x 2      |  |  |  |

| Pseudo Dual Port | 2,048 x 4      |  |  |  |

|                  | 1,024 x 9      |  |  |  |

|                  | 512 x 18       |  |  |  |

|                  | 256 x 36       |  |  |  |

|                  | 8,192 x 1      |  |  |  |

|                  | 4,096 x 2      |  |  |  |

| FIFO             | 2,048 x 4      |  |  |  |

|                  | 1,024 x 9      |  |  |  |

|                  | 512 x 18       |  |  |  |

|                  | 256 x 36       |  |  |  |

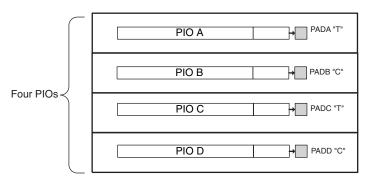

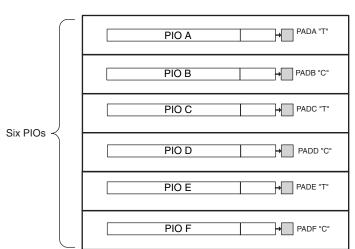

## **PIO Groups**

On the LA-MachXO devices, PIO cells are assembled into two different types of PIO groups, those with four PIO cells and those with six PIO cells. PIO groups with four IOs are placed on the left and right sides of the device while PIO groups with six IOs are placed on the top and bottom. The individual PIO cells are connected to their respective sysIO buffers and PADs.

On all LA-MachXO devices, two adjacent PIOs can be joined to provide a complementary Output driver pair. The I/ O pin pairs are labeled as "T" and "C" to distinguish between the true and complement pins.

The LA-MachXO1200 and LA-MachXO2280 devices contain enhanced I/O capability. All PIO pairs on these larger devices can implement differential receivers. In addition, half of the PIO pairs on the left and right sides of these devices can be configured as LVDS transmit/receive pairs. PIOs on the top of these larger devices also provide PCI support.

#### Figure 2-15. Group of Four Programmable I/O Cells

This structure is used on the left and right of MachXO devices

Figure 2-16. Group of Six Programmable I/O Cells

This structure is used on the top and bottom of MachXO devices

## PIO

The PIO blocks provide the interface between the sysIO buffers and the internal PFU array blocks. These blocks receive output data from the PFU array and a fast output data signal from adjacent PFUs. The output data and fast

### Table 2-8. I/O Support Device by Device

|                                             | LA-MachXO256                                                          | LA-MachXO640                                                          | LA-MachXO1200                                                                  | LA-MachXO2280                                                                  |

|---------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Number of I/O Banks                         | 2                                                                     | 4                                                                     | 8                                                                              | 8                                                                              |

| Type of Input Buffers                       | Single-ended<br>(all I/O Banks)                                       | Single-ended<br>(all I/O Banks)                                       | Single-ended<br>(all I/O Banks)                                                | Single-ended<br>(all I/O Banks)                                                |

|                                             |                                                                       |                                                                       | Differential Receivers<br>(all I/O Banks)                                      | Differential Receivers<br>(all I/O Banks)                                      |

| Types of Output Buffers                     | Single-ended buffers<br>with complementary<br>outputs (all I/O Banks) | Single-ended buffers<br>with complementary<br>outputs (all I/O Banks) | Single-ended buffers<br>with complementary<br>outputs (all I/O Banks)          | Single-ended buffers<br>with complementary<br>outputs (all I/O Banks)          |

|                                             |                                                                       |                                                                       | Differential buffers with<br>true LVDS outputs (50%<br>on left and right side) | Differential buffers with<br>true LVDS outputs (50%<br>on left and right side) |

| Differential Output<br>Emulation Capability | All I/O Banks                                                         | All I/O Banks                                                         | All I/O Banks                                                                  | All I/O Banks                                                                  |

| PCI Support                                 | No                                                                    | No                                                                    | Top side only                                                                  | Top side only                                                                  |

#### Table 2-9. Supported Input Standards

|                                                                                  | VCCIO (Typ.) |              |              |              |              |  |

|----------------------------------------------------------------------------------|--------------|--------------|--------------|--------------|--------------|--|

| Input Standard                                                                   | 3.3V         | 2.5V         | 1.8V         | 1.5V         | 1.2V         |  |

| Single Ended Interfaces                                                          |              | •            |              | •            |              |  |

| LVTTL                                                                            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |

| LVCMOS33                                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |

| LVCMOS25                                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |

| LVCMOS18                                                                         |              |              | $\checkmark$ |              |              |  |

| LVCMOS15                                                                         |              |              |              | $\checkmark$ |              |  |

| LVCMOS12                                                                         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |

| PCI <sup>1</sup>                                                                 | $\checkmark$ |              |              |              |              |  |

| Differential Interfaces                                                          |              |              |              |              |              |  |

| BLVDS <sup>2</sup> , LVDS <sup>2</sup> , LVPECL <sup>2</sup> , RSDS <sup>2</sup> | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |

1. Top Banks of LA-MachXO1200 and LA-MachXO2280 devices only.

2. LA-MachXO1200 and LA-MachXO2280 devices only.

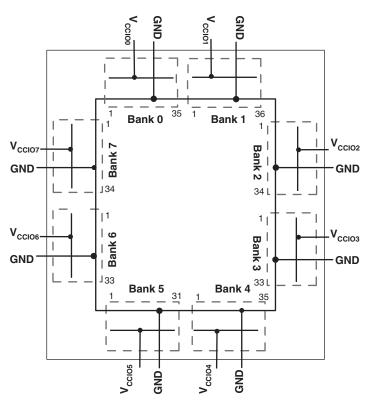

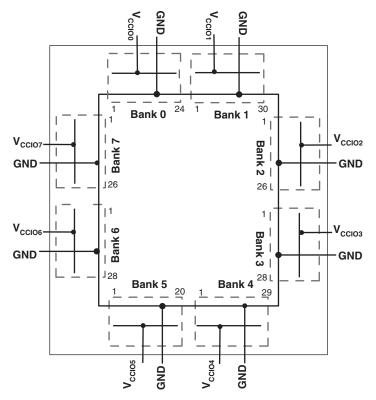

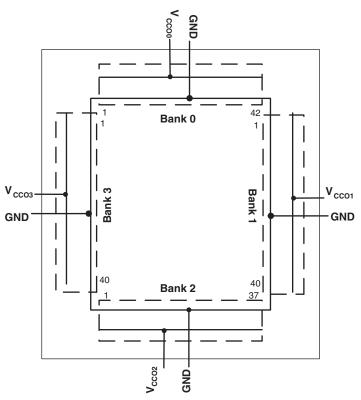

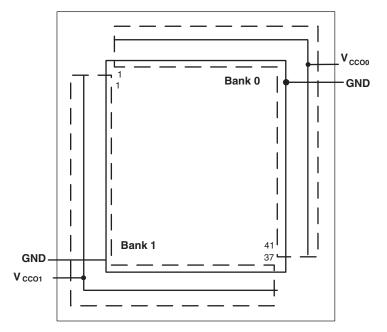

#### Figure 2-18. LA-MachXO2280 Banks

Figure 2-19. LA-MachXO1200 Banks

#### Figure 2-20. LA-MachXO640 Banks

Figure 2-21. LA-MachXO256 Banks

## **Hot Socketing**

The LA-MachXO automotive devices have been carefully designed to ensure predictable behavior during powerup and power-down. Leakage into I/O pins is controlled to within specified limits. This allows for easy integration with the rest of the system. These capabilities make the LA-MachXO ideal for many multiple power supply and hot-swap applications.

## Sleep Mode

The LA-MachXO "C" devices ( $V_{CC} = 1.8/2.5/3.3V$ ) have a sleep mode that allows standby current to be reduced dramatically during periods of system inactivity. Entry and exit to Sleep mode is controlled by the SLEEPN pin.

During Sleep mode, the logic is non-operational, registers and EBR contents are not maintained, and I/Os are tristated. Do not enter Sleep mode during device programming or configuration operation. In Sleep mode, power supplies are in their normal operating range, eliminating the need for external switching of power supplies. Table 2-11 compares the characteristics of Normal, Off and Sleep modes.

| Characteristic                  | Normal        | Off             | Sleep           |

|---------------------------------|---------------|-----------------|-----------------|

| SLEEPN Pin                      | High          | —               | Low             |

| Static Icc                      | Typical <10mA | 0               | Typical <100uA  |

| I/O Leakage                     | <10µA         | <1mA            | <10µA           |

| Power Supplies VCC/VCCIO/VCCAUX | Normal Range  | 0               | Normal Range    |

| Logic Operation                 | User Defined  | Non Operational | Non operational |

| I/O Operation                   | User Defined  | Tri-state       | Tri-state       |

| JTAG and Programming circuitry  | Operational   | Non-operational | Non-operational |

| EBR Contents and Registers      | Maintained    | Non-maintained  | Non-maintained  |

Table 2-11. Characteristics of Normal, Off and Sleep Modes

## **SLEEPN Pin Characteristics**

The SLEEPN pin behaves as an LVCMOS input with the voltage standard appropriate to the VCC supply for the device. This pin also has a weak pull-up, along with a Schmidt trigger and glitch filter to prevent false triggering. An external pull-up to VCC is recommended when Sleep Mode is not used to ensure the device stays in normal operation mode. Typically, the device enters sleep mode several hundred nanoseconds after SLEEPN is held at a valid low and restarts normal operation as specified in the Sleep Mode Timing table. The AC and DC specifications portion of this data sheet shows a detailed timing diagram.

## Oscillator

Every LA-MachXO device has an internal CMOS oscillator. The oscillator can be routed as an input clock to the clock tree or to general routing resources. The oscillator frequency can be divided by internal logic. There is a dedicated programming bit to enable/disable the oscillator. The oscillator frequency ranges from 16MHz to 26MHz.

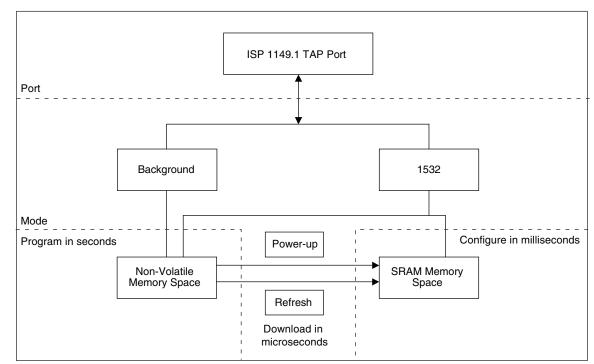

## **Configuration and Testing**

The following section describes the configuration and testing features of the LA-MachXO automotive family of devices.

## IEEE 1149.1-Compliant Boundary Scan Testability

All LA-MachXO devices have boundary scan cells that are accessed through an IEEE 1149.1 compliant test access port (TAP). This allows functional testing of the circuit board, on which the device is mounted, through a serial scan path that can access all critical logic nodes. Internal registers are linked internally, allowing test data to be shifted in and loaded directly onto test nodes, or test data to be captured and shifted out for verification. The test access port consists of dedicated I/Os: TDI, TDO, TCK and TMS. The test access port shares its power supply with one of the VCCIO Banks (LA-MachXO256:  $V_{CCIO1}$ ; LA-MachXO640:  $V_{CCIO2}$ ; LA-MachXO1200 and LA-MachXO2280:  $V_{CCIO5}$ ) and can operate with LVCMOS3.3, 2.5, 1.8, 1.5, and 1.2 standards.

For more details on boundary scan test, please see information regarding additional technical documentation at the end of this data sheet.

Figure 2-22. LA-MachXO Configuration and Programming

# **Density Shifting**

The LA-MachXO family has been designed to enable density migration in the same package. Furthermore, the architecture ensures a high success rate when performing design migration from lower density parts to higher density parts. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likely success in each case.

# sysIO Recommended Operating Conditions

|                      | V <sub>CCIO</sub> (V) |      |       |  |  |

|----------------------|-----------------------|------|-------|--|--|

| Standard             | Min.                  | Тур. | Max.  |  |  |

| LVCMOS 3.3           | 3.135                 | 3.3  | 3.465 |  |  |

| LVCMOS 2.5           | 2.375                 | 2.5  | 2.625 |  |  |

| LVCMOS 1.8           | 1.71                  | 1.8  | 1.89  |  |  |

| LVCMOS 1.5           | 1.425                 | 1.5  | 1.575 |  |  |

| LVCMOS 1.2           | 1.14                  | 1.2  | 1.26  |  |  |

| LVTTL                | 3.135                 | 3.3  | 3.465 |  |  |

| PCl <sup>3</sup>     | 3.135                 | 3.3  | 3.465 |  |  |

| LVDS <sup>1, 2</sup> | 2.375                 | 2.5  | 2.625 |  |  |

| LVPECL <sup>1</sup>  | 3.135                 | 3.3  | 3.465 |  |  |

| BLVDS <sup>1</sup>   | 2.375                 | 2.5  | 2.625 |  |  |

| RSDS <sup>1</sup>    | 2.375                 | 2.5  | 2.625 |  |  |

1. Inputs on chip. Outputs are implemented with the addition of external resistors.

2. MachXO1200 and MachXO2280 devices have dedicated LVDS buffers

3. Input on the top bank of the MachXO1200 and MachXO2280 only.

## **Typical Building Block Function Performance**<sup>1</sup>

## Pin-to-Pin Performance (LVCMOS25 12mA Drive)

| Function        | -3 Timing | Units |

|-----------------|-----------|-------|

| Basic Functions |           |       |

| 16-bit decoder  | 9.4       | ns    |

| 4:1 MUX         | 6.3       | ns    |

| 16:1 MUX        | 7.1       | ns    |

### **Register-to-Register Performance**

| Function                        | -3 Timing              | Units |

|---------------------------------|------------------------|-------|

| Basic Functions                 |                        |       |

| 16:1 MUX                        | 348                    | MHz   |

| 16-bit adder                    | 209                    | MHz   |

| 16-bit counter                  | 277                    | MHz   |

| 64-bit counter                  | 143                    | MHz   |

| Embedded Memory Functions (1200 | and 2280 Devices Only) |       |

| 256x36 Single Port RAM          | 203                    | MHz   |

| 512x18 True-Dual Port RAM       | 203                    | MHz   |

| Distributed Memory Functions    | •                      |       |

| 16x2 Single Port RAM            | 310                    | MHz   |

| 64x2 Single Port RAM            | 229                    | MHz   |

| 128x4 Single Port RAM           | 186                    | MHz   |

| 32x2 Pseudo-Dual Port RAM       | 224                    | MHz   |

| 64x4 Pseudo-Dual Port RAM       | 194                    | MHz   |

The above timing numbers are generated using the ispLEVER design tool. Exact performance may vary with device and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

Rev. A 0.19

# **Derating Logic Timing**

Logic Timing provided in the following sections of the data sheet and the ispLEVER design tools are worst case numbers in the operating range. Actual delays may be much faster. The ispLEVER design tool from Lattice can provide logic timing numbers at a particular temperature and voltage.

# LA-MachXO1200 and LA-MachXO2280 Logic Signal Connections: 100 TQFP

|               |                  |      | LAMXO1200        | D1200 LAMXO2280 |                  |      | LAMXO2280        |              |  |

|---------------|------------------|------|------------------|-----------------|------------------|------|------------------|--------------|--|

| Pin<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential    | Ball<br>Function | Bank | Dual<br>Function | Differential |  |

| 1             | PL2A             | 7    |                  | Т               | PL2A             | 7    | LUM0_PLLT_FB_A   | Т            |  |

| 2             | PL2B             | 7    |                  | С               | PL2B             | 7    | LUM0_PLLC_FB_A   | С            |  |

| 3             | PL3C             | 7    |                  | Т               | PL3C             | 7    | LUM0_PLLT_IN_A   | Т            |  |

| 4             | PL3D             | 7    |                  | С               | PL3D             | 7    | LUM0_PLLC_IN_A   | С            |  |

| 5             | PL4B             | 7    |                  |                 | PL4B             | 7    |                  |              |  |

| 6             | VCCI07           | 7    |                  |                 | VCCI07           | 7    |                  |              |  |

| 7             | PL6A             | 7    |                  | Τ*              | PL7A             | 7    |                  | T*           |  |

| 8             | PL6B             | 7    | GSRN             | C*              | PL7B             | 7    | GSRN             | C*           |  |

| 9             | GND              | -    |                  |                 | GND              | -    |                  |              |  |

| 10            | PL7C             | 7    |                  | Т               | PL9C             | 7    |                  | Т            |  |

| 11            | PL7D             | 7    |                  | С               | PL9D             | 7    |                  | С            |  |

| 12            | PL8C             | 7    |                  | Т               | PL10C            | 7    |                  | Т            |  |

| 13            | PL8D             | 7    |                  | С               | PL10D            | 7    |                  | С            |  |

| 14            | PL9C             | 6    |                  |                 | PL11C            | 6    |                  |              |  |

| 15            | PL10A            | 6    |                  | T*              | PL13A            | 6    |                  | T*           |  |

| 16            | PL10B            | 6    |                  | C*              | PL13B            | 6    |                  | C*           |  |

| 17            | VCC              | -    |                  |                 | VCC              | -    |                  |              |  |

| 18            | PL11B            | 6    |                  |                 | PL14D            | 6    |                  | С            |  |

| 19            | PL11C            | 6    | TSALL            |                 | PL14C            | 6    | TSALL            | Т            |  |

| 20            | VCCIO6           | 6    |                  |                 | VCCIO6           | 6    |                  |              |  |

| 21            | PL13C            | 6    |                  |                 | PL16C            | 6    |                  |              |  |

| 22            | PL14A            | 6    | LLM0_PLLT_FB_A   | T*              | PL17A            | 6    | LLM0_PLLT_FB_A   | T*           |  |

| 23            | PL14B            | 6    | LLM0_PLLC_FB_A   | C*              | PL17B            | 6    | LLM0_PLLC_FB_A   | C*           |  |

| 24            | PL15A            | 6    | LLM0_PLLT_IN_A   | T*              | PL18A            | 6    | LLM0_PLLT_IN_A   | T*           |  |

| 25            | PL15B            | 6    | LLM0_PLLC_IN_A   | C*              | PL18B            | 6    | LLM0_PLLC_IN_A   | C*           |  |

| 26**          | GNDIO6<br>GNDIO5 | -    |                  |                 | GNDIO6<br>GNDIO5 | -    |                  |              |  |

| 27            | VCCIO5           | 5    |                  |                 | VCCIO5           | 5    |                  |              |  |

| 28            | TMS              | 5    | TMS              |                 | TMS              | 5    | TMS              |              |  |

| 29            | TCK              | 5    | ТСК              |                 | TCK              | 5    | ТСК              |              |  |

| 30            | PB3B             | 5    |                  |                 | PB3B             | 5    |                  |              |  |

| 31            | PB4A             | 5    |                  | Т               | PB4A             | 5    |                  | Т            |  |

| 32            | PB4B             | 5    |                  | С               | PB4B             | 5    |                  | С            |  |

| 33            | TDO              | 5    | TDO              |                 | TDO              | 5    | TDO              |              |  |

| 34            | TDI              | 5    | TDI              |                 | TDI              | 5    | TDI              |              |  |

| 35            | VCC              | -    |                  |                 | VCC              | -    |                  |              |  |

| 36            | VCCAUX           | -    |                  |                 | VCCAUX           | -    |                  |              |  |

| 37            | PB6E             | 5    |                  | Т               | PB8E             | 5    |                  | Т            |  |

| 38            | PB6F             | 5    |                  | С               | PB8F             | 5    |                  | С            |  |

| 39            | PB7B             | 4    | PCLK4_1***       |                 | PB10F            | 4    | PCLK4_1***       |              |  |

| 40            | PB7F             | 4    | PCLK4_0***       |                 | PB10B            | 4    | PCLK4_0***       |              |  |

# LA-MachXO1200 and LA-MachXO2280 Logic Signal Connections: 100 TQFP (Cont.)

|               |                  | l    | AMXO1200         |              | LAMXO2280        |      |                  |              |  |

|---------------|------------------|------|------------------|--------------|------------------|------|------------------|--------------|--|

| Pin<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Function | Bank | Dual<br>Function | Differential |  |

| 80            | VCCIO1           | 1    |                  |              | VCCIO1           | 1    |                  |              |  |

| 81            | PT9E             | 1    |                  |              | PT12D            | 1    |                  | С            |  |

| 82            | PT9A             | 1    |                  |              | PT12C            | 1    |                  | Т            |  |

| 83            | GND              | -    |                  |              | GND              | -    |                  |              |  |

| 84            | PT8B             | 1    |                  | С            | PT11B            | 1    |                  | С            |  |

| 85            | PT8A             | 1    |                  | Т            | PT11A            | 1    |                  | Т            |  |

| 86            | PT7D             | 1    | PCLK1_1***       |              | PT10B            | 1    | PCLK1_1***       |              |  |

| 87            | PT6F             | 0    | PCLK1_0***       |              | PT9B             | 1    | PCLK1_0***       |              |  |

| 88            | PT6D             | 0    |                  | С            | PT8F             | 0    |                  | С            |  |

| 89            | PT6C             | 0    |                  | Т            | PT8E             | 0    |                  | Т            |  |

| 90            | VCCAUX           | -    |                  |              | VCCAUX           | -    |                  |              |  |

| 91            | VCC              | -    |                  |              | VCC              | -    |                  |              |  |

| 92            | PT5B             | 0    |                  |              | PT6D             | 0    |                  |              |  |

| 93            | PT4B             | 0    |                  |              | PT6F             | 0    |                  |              |  |

| 94            | VCCIO0           | 0    |                  |              | VCCIO0           | 0    |                  |              |  |

| 95            | PT3D             | 0    |                  | С            | PT4B             | 0    |                  | С            |  |

| 96            | PT3C             | 0    |                  | Т            | PT4A             | 0    |                  | Т            |  |

| 97            | PT3B             | 0    |                  |              | PT3B             | 0    |                  |              |  |

| 98            | PT2B             | 0    |                  | С            | PT2B             | 0    |                  | С            |  |

| 99            | PT2A             | 0    |                  | Т            | PT2A             | 0    |                  | Т            |  |

| 100**         | GNDIO0<br>GNDIO7 | -    |                  |              | GNDIO0<br>GNDIO7 | -    |                  |              |  |

\*Supports true LVDS outputs.

\*\*Double bonded to the pin.

\*\*\* Primary clock inputs are single-ended.

## LA-MachXO640, LA-MachXO1200 and LA-MachXO2280 Logic Signal Connections: 144 TQFP (Cont.)

|               |                  | L    | AMXO640          |              | LAMXO1200        |      |                  |              | LAMXO2280        |      |                  |              |

|---------------|------------------|------|------------------|--------------|------------------|------|------------------|--------------|------------------|------|------------------|--------------|

| Pin<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Function | Bank | Dual<br>Function | Differential |

| 101           | PR3D             | 1    |                  | С            | PR4B             | 2    |                  | C*           | PR5B             | 2    |                  | C*           |

| 102           | PR3C             | 1    |                  | Т            | PR4A             | 2    |                  | T*           | PR5A             | 2    |                  | T*           |

| 103           | PR3B             | 1    |                  | С            | PR3D             | 2    |                  | C            | PR4D             | 2    |                  | С            |

| 104           | PR2D             | 1    |                  | С            | PR3C             | 2    |                  | Т            | PR4C             | 2    |                  | Т            |

| 105           | PR3A             | 1    |                  | Т            | PR3B             | 2    |                  | C*           | PR4B             | 2    |                  | C*           |

| 106           | PR2B             | 1    |                  | С            | PR3A             | 2    |                  | T*           | PR4A             | 2    |                  | T*           |

| 107           | PR2C             | 1    |                  | Т            | PR2B             | 2    |                  | С            | PR3B             | 2    |                  | C*           |

| 108           | PR2A             | 1    |                  | Т            | PR2A             | 2    |                  | Т            | PR3A             | 2    |                  | T*           |

| 109           | PT9F             | 0    |                  | С            | PT11D            | 1    |                  | C            | PT16D            | 1    |                  | С            |

| 110           | PT9D             | 0    |                  | С            | PT11C            | 1    |                  | Т            | PT16C            | 1    |                  | Т            |

| 111           | PT9E             | 0    |                  | Т            | PT11B            | 1    |                  | C            | PT16B            | 1    |                  | С            |

| 112           | PT9B             | 0    |                  | С            | PT11A            | 1    |                  | Т            | PT16A            | 1    |                  | Т            |

| 113           | PT9C             | 0    |                  | Т            | PT10F            | 1    |                  | С            | PT15D            | 1    |                  | С            |

| 114           | PT9A             | 0    |                  | Т            | PT10E            | 1    |                  | Т            | PT15C            | 1    |                  | Т            |

| 115           | PT8C             | 0    |                  |              | PT10D            | 1    |                  | C            | PT14B            | 1    |                  | С            |

| 116           | PT8B             | 0    |                  | С            | PT10C            | 1    |                  | Т            | PT14A            | 1    |                  | Т            |

| 117           | VCCIO0           | 0    |                  |              | VCCIO1           | 1    |                  |              | VCCIO1           | 1    |                  |              |

| 118           | GNDIO0           | 0    |                  |              | GNDIO1           | 1    |                  |              | GNDIO1           | 1    |                  |              |

| 119           | PT8A             | 0    |                  | Т            | PT9F             | 1    |                  | C            | PT12F            | 1    |                  | С            |

| 120           | PT7E             | 0    |                  |              | PT9E             | 1    |                  | Т            | PT12E            | 1    |                  | Т            |

| 121           | PT7C             | 0    |                  |              | PT9B             | 1    |                  | С            | PT12D            | 1    |                  | С            |

| 122           | PT7A             | 0    |                  |              | PT9A             | 1    |                  | Т            | PT12C            | 1    |                  | Т            |

| 123           | GND              | -    |                  |              | GND              | -    |                  |              | GND              | -    |                  |              |

| 124           | PT6B             | 0    | PCLK0_1***       | С            | PT7D             | 1    | PCLK1_1***       |              | PT10B            | 1    | PCLK1_1***       |              |

| 125           | PT6A             | 0    |                  | Т            | PT7B             | 1    |                  | C            | PT9D             | 1    |                  | С            |

| 126           | PT5C             | 0    |                  |              | PT7A             | 1    |                  | Т            | PT9C             | 1    |                  | Т            |

| 127           | PT5B             | 0    | PCLK0_0***       |              | PT6F             | 0    | PCLK1_0***       |              | PT9B             | 1    | PCLK1_0***       |              |

| 128           | VCCAUX           | -    |                  |              | VCCAUX           | -    |                  |              | VCCAUX           | -    |                  |              |

| 129           | VCC              | -    |                  |              | VCC              | -    |                  |              | VCC              | -    |                  |              |

| 130           | PT4D             | 0    |                  |              | PT5D             | 0    |                  | C            | PT7B             | 0    |                  | С            |

| 131           | PT4B             | 0    |                  | С            | PT5C             | 0    |                  | Т            | PT7A             | 0    |                  | Т            |

| 132           | PT4A             | 0    |                  | Т            | PT5B             | 0    |                  | C            | PT6D             | 0    |                  |              |

| 133           | PT3F             | 0    |                  |              | PT5A             | 0    |                  | Т            | PT6E             | 0    |                  | Т            |

| 134           | PT3D             | 0    |                  |              | PT4B             | 0    |                  |              | PT6F             | 0    |                  | С            |

| 135           | VCCIO0           | 0    |                  |              | VCCIO0           | 0    |                  |              | VCCIO0           | 0    |                  |              |

| 136           | GNDIO0           | 0    |                  |              | GNDIO0           | 0    |                  |              | GNDIO0           | 0    |                  |              |

| 137           | PT3B             | 0    |                  | С            | PT3D             | 0    |                  | С            | PT4B             | 0    |                  | Т            |

| 138           | PT2F             | 0    |                  | С            | PT3C             | 0    |                  | Т            | PT4A             | 0    |                  | С            |

| 139           | PT3A             | 0    |                  | Т            | PT3B             | 0    |                  | C            | PT3B             | 0    |                  | С            |

| 140           | PT2D             | 0    |                  | С            | PT3A             | 0    |                  | Т            | PT3A             | 0    |                  | Т            |

| 141           | PT2E             | 0    |                  | Т            | PT2D             | 0    |                  | С            | PT2D             | 0    |                  | С            |

| 142           | PT2B             | 0    |                  | С            | PT2C             | 0    |                  | Т            | PT2C             | 0    |                  | Т            |

| 143           | PT2C             | 0    |                  | Т            | PT2B             | 0    |                  | C            | PT2B             | 0    |                  | С            |

| 144           | PT2A             | 0    |                  | Т            | PT2A             | 0    |                  | Т            | PT2A             | 0    |                  | Т            |

\*Supports true LVDS outputs.

\*\*NC for "E" devices. \*\*\*Primary clock inputs arer single-ended.

## LA-MachXO640, LA-MachXO1200 and LA-MachXO2280 Logic Signal Connections: 256 ftBGA (Cont.)

|                |                  | LAMX | 0640             |              | LAMXO1200      |                  |      |                  |              | LAMXO2280      |                  |      |                  |              |

|----------------|------------------|------|------------------|--------------|----------------|------------------|------|------------------|--------------|----------------|------------------|------|------------------|--------------|

| Ball<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential |

| A3             | PT2B             | 0    |                  | С            | A3             | PT3B             | 0    |                  | С            | A3             | PT3B             | 0    |                  | С            |

| A2             | PT2A             | 0    |                  | т            | A2             | PT3A             | 0    |                  | Т            | A2             | PT3A             | 0    |                  | Т            |

| B3             | NC               |      |                  |              | B3             | PT2B             | 0    |                  | С            | B3             | PT2D             | 0    |                  | С            |

| B2             | NC               |      |                  |              | B2             | PT2A             | 0    |                  | Т            | B2             | PT2C             | 0    |                  | т            |

| VCCIO0         | VCCIO0           | 0    |                  |              | VCCIO0         | VCCIO0           | 0    |                  |              | VCCI00         | VCCIO0           | 0    |                  |              |

| GND            | GNDIO0           | 0    |                  |              | GND            | GNDIO0           | 0    |                  |              | GND            | GNDIO0           | 0    |                  |              |

| A1             | GND              | -    |                  |              | A1             | GND              | -    |                  |              | A1             | GND              | -    |                  |              |

| A16            | GND              | -    |                  |              | A16            | GND              | -    |                  |              | A16            | GND              | -    |                  |              |

| F11            | GND              | -    |                  |              | F11            | GND              | -    |                  |              | F11            | GND              | -    |                  |              |

| G8             | GND              | -    |                  |              | G8             | GND              | -    |                  |              | G8             | GND              | -    |                  |              |

| G9             | GND              | -    |                  |              | G9             | GND              | -    |                  |              | G9             | GND              | -    |                  |              |

| H7             | GND              | -    |                  |              | H7             | GND              | -    |                  |              | H7             | GND              | -    |                  |              |

| H8             | GND              | -    |                  |              | H8             | GND              | -    |                  |              | H8             | GND              | -    |                  |              |

| H9             | GND              | -    |                  |              | H9             | GND              | -    |                  |              | H9             | GND              | -    |                  |              |

| H10            | GND              | -    |                  |              | H10            | GND              | -    |                  |              | H10            | GND              | -    |                  |              |

| J7             | GND              | -    |                  |              | J7             | GND              | -    |                  |              | J7             | GND              | -    |                  |              |

| J8             | GND              | -    |                  |              | J8             | GND              | -    |                  |              | J8             | GND              | -    |                  |              |

| J9             | GND              | -    |                  |              | J9             | GND              | -    |                  |              | J9             | GND              | -    |                  |              |

| J10            | GND              | -    |                  |              | J10            | GND              | -    |                  |              | J10            | GND              | -    |                  |              |

| K8             | GND              | -    |                  |              | K8             | GND              | -    |                  |              | K8             | GND              | -    |                  |              |

| K9             | GND              | -    |                  |              | K9             | GND              | -    |                  |              | K9             | GND              | -    |                  |              |

| L6             | GND              | -    |                  |              | L6             | GND              | -    |                  |              | L6             | GND              | -    |                  |              |

| T1             | GND              | -    |                  |              | T1             | GND              | -    |                  |              | T1             | GND              | -    |                  |              |

| T16            | GND              | -    |                  |              | T16            | GND              | -    |                  |              | T16            | GND              | -    |                  |              |

| G7             | VCC              | -    |                  |              | G7             | VCC              | -    |                  |              | G7             | VCC              | -    |                  |              |

| G10            | VCC              | -    |                  |              | G10            | VCC              | -    |                  |              | G10            | VCC              | -    |                  |              |

| K7             | VCC              | -    |                  |              | K7             | VCC              | -    |                  |              | K7             | VCC              | -    |                  |              |

| K10            | VCC              | -    |                  |              | K10            | VCC              | -    |                  |              | K10            | VCC              | -    |                  |              |

| H6             | VCCIO3           | 3    |                  |              | H6             | VCCI07           | 7    |                  |              | H6             | VCCI07           | 7    |                  |              |

| G6             | VCCIO3           | 3    |                  |              | G6             | VCCI07           | 7    |                  |              | G6             | VCCI07           | 7    |                  |              |

| K6             | VCCIO3           | 3    |                  |              | K6             | VCCIO6           | 6    |                  |              | K6             | VCCIO6           | 6    |                  |              |

| J6             | VCCIO3           | 3    |                  |              | J6             | VCCIO6           | 6    |                  |              | J6             | VCCIO6           | 6    |                  |              |

| L8             | VCCIO2           | 2    |                  |              | L8             | VCCIO5           | 5    |                  |              | L8             | VCCIO5           | 5    |                  |              |

| L7             | VCCIO2           | 2    |                  |              | L7             | VCCIO5           | 5    |                  |              | L7             | VCCI05           | 5    |                  |              |

| L9             | VCCIO2           | 2    |                  |              | L9             | VCCIO4           | 4    |                  |              | L9             | VCCIO4           | 4    |                  |              |

| L10            | VCCIO2           | 2    |                  |              | L10            | VCCIO4           | 4    |                  |              | L10            | VCCIO4           | 4    |                  |              |

| K11            | VCCIO1           | 1    |                  |              | K11            | VCCIO3           | 3    |                  |              | K11            | VCCIO3           | 3    |                  |              |

| J11            | VCCIO1           | 1    |                  |              | J11            | VCCIO3           | 3    |                  |              | J11            | VCCIO3           | 3    |                  |              |

| H11            | VCCIO1           | 1    |                  |              | H11            | VCCIO2           | 2    |                  |              | H11            | VCCIO2           | 2    |                  |              |

| G11            | VCCIO1           | 1    |                  |              | G11            | VCCIO2           | 2    |                  |              | G11            | VCCIO2           | 2    |                  |              |

| F9             | VCCIO0           | 0    |                  |              | F9             | VCCIO1           | 1    |                  |              | F9             | VCCIO1           | 1    |                  |              |

| F10            | VCCIO0           | 0    |                  |              | F10            | VCCIO1           | 1    |                  |              | F10            | VCCIO1           | 1    |                  |              |

| F8             | VCCIO0           | 0    |                  |              | F8             | VCCIO0           | 0    |                  |              | F8             | VCCIO0           | 0    |                  |              |

| F7             | VCCIO0           | 0    |                  |              | F7             | VCCIO0           | 0    |                  |              | F7             | VCCIO0           | 0    |                  |              |

\* LCMXO640 only. \*\* Supports true LVDS outputs. \*\*\* NC for "E" devices. \*\*\*\* Primary clock inputs are single-ended.

# LA-MachXO2280 Logic Signal Connections: 324 ftBGA

| LAMXO2280 Roll Eurotion Ronk Dual Eurotion Differential |               |      |                |             |  |  |  |

|---------------------------------------------------------|---------------|------|----------------|-------------|--|--|--|

| Ball Number                                             | Ball Function | Bank | Dual Function  | Differentia |  |  |  |

| GND                                                     | GNDIO7        | 7    |                |             |  |  |  |

| VCCIO7                                                  | VCCI07        | 7    |                |             |  |  |  |

| D4                                                      | PL2A          | 7    | LUM0_PLLT_FB_A | Т           |  |  |  |

| F5                                                      | PL2B          | 7    | LUM0_PLLC_FB_A | С           |  |  |  |

| B3                                                      | PL3A          | 7    |                | Τ*          |  |  |  |

| C3                                                      | PL3B          | 7    |                | C*          |  |  |  |

| E4                                                      | PL3C          | 7    | LUM0_PLLT_IN_A | Т           |  |  |  |

| G6                                                      | PL3D          | 7    | LUM0_PLLC_IN_A | С           |  |  |  |

| A1                                                      | PL4A          | 7    |                | T*          |  |  |  |

| B1                                                      | PL4B          | 7    |                | C*          |  |  |  |

| F4                                                      | PL4C          | 7    |                | Т           |  |  |  |

| VCC                                                     | VCC           | -    |                |             |  |  |  |

| E3                                                      | PL4D          | 7    |                | С           |  |  |  |

| D2                                                      | PL5A          | 7    |                | T*          |  |  |  |

| D3                                                      | PL5B          | 7    |                | C*          |  |  |  |

| G5                                                      | PL5C          | 7    |                | Т           |  |  |  |

| F3                                                      | PL5D          | 7    |                | С           |  |  |  |

| C2                                                      | PL6A          | 7    |                | T*          |  |  |  |

| VCCIO7                                                  | VCCIO7        | 7    |                |             |  |  |  |

| GND                                                     | GNDIO7        | 7    |                |             |  |  |  |

| C1                                                      | PL6B          | 7    |                | C*          |  |  |  |

| H5                                                      | PL6C          | 7    |                | Т           |  |  |  |

| G4                                                      | PL6D          | 7    |                | С           |  |  |  |

| E2                                                      | PL7A          | 7    |                | T*          |  |  |  |

| D1                                                      | PL7B          | 7    | GSRN           | C*          |  |  |  |

| J6                                                      | PL7C          | 7    |                | Т           |  |  |  |

| H4                                                      | PL7D          | 7    |                | С           |  |  |  |

| F2                                                      | PL8A          | 7    |                | T*          |  |  |  |

| E1                                                      | PL8B          | 7    |                | C*          |  |  |  |

| GND                                                     | GND           | -    |                |             |  |  |  |

| J3                                                      | PL8C          | 7    |                | Т           |  |  |  |

| J5                                                      | PL8D          | 7    |                | С           |  |  |  |

| G3                                                      | PL9A          | 7    |                | T*          |  |  |  |

| H3                                                      | PL9B          | 7    |                | C*          |  |  |  |

| K3                                                      | PL9C          | 7    |                | Т           |  |  |  |

| K5                                                      | PL9D          | 7    |                | С           |  |  |  |

| F1                                                      | PL10A         | 7    |                | T*          |  |  |  |

| VCCIO7                                                  | VCCIO7        | 7    |                | -           |  |  |  |

| GND                                                     | GNDIO7        | 7    |                |             |  |  |  |

| G1                                                      | PL10B         | 7    |                | C*          |  |  |  |

| K4                                                      | PL10C         | 7    |                | т           |  |  |  |

| K6                                                      | PL10D         | 7    |                | С           |  |  |  |

# LA-MachXO2280 Logic Signal Connections: 324 ftBGA (Cont.)

|             |               | LAMXO2280 |               | <b>B</b> 144 |

|-------------|---------------|-----------|---------------|--------------|

| Ball Number | Ball Function | Bank      | Dual Function | Differential |

| J13         | PR10C         | 2         |               | Т            |

| M18         | PR10B         | 2         |               | C*           |

| L18         | PR10A         | 2         |               | T*           |

| GND         | GNDIO2        | 2         |               |              |

| VCCIO2      | VCCIO2        | 2         |               |              |

| H16         | PR9D          | 2         |               | С            |

| H14         | PR9C          | 2         |               | Т            |

| K18         | PR9B          | 2         |               | C*           |

| J18         | PR9A          | 2         |               | Τ*           |

| J17         | PR8D          | 2         |               | С            |

| VCC         | VCC           | -         |               |              |

| H18         | PR8C          | 2         |               | Т            |

| H17         | PR8B          | 2         |               | C*           |

| G17         | PR8A          | 2         |               | T*           |

| H13         | PR7D          | 2         |               | С            |

| H15         | PR7C          | 2         |               | Т            |

| G18         | PR7B          | 2         |               | C*           |

| F18         | PR7A          | 2         |               | Τ*           |

| G14         | PR6D          | 2         |               | С            |

| G16         | PR6C          | 2         |               | Т            |

| VCCIO2      | VCCIO2        | 2         |               |              |

| GND         | GNDIO2        | 2         |               |              |

| E18         | PR6B          | 2         |               | C*           |

| F17         | PR6A          | 2         |               | T*           |

| G13         | PR5D          | 2         |               | С            |

| G15         | PR5C          | 2         |               | Т            |

| E17         | PR5B          | 2         |               | C*           |

| E16         | PR5A          | 2         |               | T*           |

| GND         | GND           | -         |               |              |

| F15         | PR4D          | 2         |               | С            |

| E15         | PR4C          | 2         |               | Т            |

| D17         | PR4B          | 2         |               | C*           |

| D18         | PR4A          | 2         |               | T*           |

| B18         | PR3D          | 2         |               | С            |

| C18         | PR3C          | 2         |               | Т            |

| C16         | PR3B          | 2         |               | C*           |

| D16         | PR3A          | 2         |               | T*           |

| C17         | PR2B          | 2         |               | C            |

| D15         | PR2A          | 2         |               |              |

| VCCIO2      | VCCIO2        | 2         |               | •            |

| GND         | GNDIO2        | 2         |               |              |

| GND         | GNDIO1        | 1         |               |              |

| VCCIO1      | VCCIO1        | i         |               |              |

# LA-MachXO2280 Logic Signal Connections: 324 ftBGA (Cont.)

|             | LAMXO2280     |      |               |              |  |  |  |

|-------------|---------------|------|---------------|--------------|--|--|--|

| Ball Number | Ball Function | Bank | Dual Function | Differential |  |  |  |

| G8          | VCCIO0        | 0    |               |              |  |  |  |

| G7          | VCCIO0        | 0    |               |              |  |  |  |

\* Supports true LVDS outputs.

\*\* Primary clock inputs are single-ended.

# LA-MachXO Automotive Family Data Sheet Revision History **Revision History**

November 2007

Data Sheet DS1003

# **Revision History**

| Date          | Version | Section                             | Change Summary                                                                                                                                                                       |

|---------------|---------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| April 2006    | 01.0    | —                                   | Initial release.                                                                                                                                                                     |

| May 2006      | 01.1    | Pinout Information                  | Removed [LOC][0]_PLL_RST from Signal Descriptions table.                                                                                                                             |

|               |         |                                     | PCLK footnote added to appropriate pins in Logic Signal Connections tables.                                                                                                          |

| November 2006 | 01.2    | DC and Switching<br>Characteristics | Corrections to MachXO "C" Sleep Mode Timing table - value for t <sub>WSLEEPN</sub> (400ns) changed from max. to min. Value for t <sub>WAWAKE</sub> (100ns) changed from min. to max. |

|               |         |                                     | Added Flash Download Time table.                                                                                                                                                     |

| December 2006 | 01.3    | Architecture                        | EBR Asynchronous Reset section added.                                                                                                                                                |

|               |         | Pinout Information                  | Power Supply and NC table: Pin/Ball orientation footnotes added.                                                                                                                     |

| February 2007 | 01.4    | Architecture                        | Updated EBR Asynchronous Reset section.                                                                                                                                              |

| November 2007 | 01.5    | DC and Switching<br>Characteristics | Updated sysIO Single-Ended DC Electrical Characteristics table.                                                                                                                      |

|               |         |                                     | Added JTAG Port Timing Waveforms diagram.                                                                                                                                            |

|               |         | Pinout Information                  | Added Thermal Management text section.                                                                                                                                               |

|               |         | Supplemental<br>Information         | Updated title list.                                                                                                                                                                  |

© 2007 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.