Welcome to **E-XFL.COM**

**Understanding Embedded - CPLDs (Complex Programmable Logic Devices)**

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixed-function ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

| Details                         |                                                                               |

|---------------------------------|-------------------------------------------------------------------------------|

| Product Status                  | Active                                                                        |

| Programmable Type               | In System Programmable                                                        |

| Delay Time tpd(1) Max           | 5.1 ns                                                                        |

| Voltage Supply - Internal       | 1.14V ~ 1.26V                                                                 |

| Number of Logic Elements/Blocks | -                                                                             |

| Number of Macrocells            | 600                                                                           |

| Number of Gates                 | -                                                                             |

| Number of I/O                   | 113                                                                           |

| Operating Temperature           | -40°C ~ 125°C (TA)                                                            |

| Mounting Type                   | Surface Mount                                                                 |

| Package / Case                  | 144-LQFP                                                                      |

| Supplier Device Package         | 144-TQFP (20x20)                                                              |

| Purchase URL                    | https://www.e-xfl.com/product-detail/lattice-semiconductor/lamxo1200e-3tn144e |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Modes of Operation**

Each Slice is capable of four modes of operation: Logic, Ripple, RAM, and ROM. The Slice in the PFF is capable of all modes except RAM. Table 2-2 lists the modes and the capability of the Slice blocks.

Table 2-2. Slice Modes

|           | Logic              | Ripple                | RAM     | ROM          |

|-----------|--------------------|-----------------------|---------|--------------|

| PFU Slice | LUT 4x2 or LUT 5x1 | 2-bit Arithmetic Unit | SP 16x2 | ROM 16x1 x 2 |

| PFF Slice | LUT 4x2 or LUT 5x1 | 2-bit Arithmetic Unit | N/A     | ROM 16x1 x 2 |

**Logic Mode:** In this mode, the LUTs in each Slice are configured as 4-input combinatorial lookup tables (LUT4). A LUT4 can have 16 possible input combinations. Any logic function with four inputs can be generated by programming this lookup table. Since there are two LUT4s per Slice, a LUT5 can be constructed within one Slice. Larger lookup tables such as LUT6, LUT7, and LUT8 can be constructed by concatenating other Slices.

**Ripple Mode:** Ripple mode allows the efficient implementation of small arithmetic functions. In ripple mode, the following functions can be implemented by each Slice:

- Addition 2-bit

- Subtraction 2-bit

- Add/Subtract 2-bit using dynamic control

- Up counter 2-bit

- Down counter 2-bit

- Ripple mode multiplier building block

- · Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Two additional signals, Carry Generate and Carry Propagate, are generated per Slice in this mode, allowing fast arithmetic functions to be constructed by concatenating Slices.

**RAM Mode:** In this mode, distributed RAM can be constructed using each LUT block as a 16x2-bit memory. Through the combination of LUTs and Slices, a variety of different memories can be constructed.

The ispLEVER design tool supports the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2-3 shows the number of Slices required to implement different distributed RAM primitives. Figure 2-6 shows the distributed memory primitive block diagrams. Dual port memories involve the pairing of two Slices. One Slice functions as the read-write port, while the other companion Slice supports the read-only port. For more information on RAM mode in LA-MachXO devices, please see details of additional technical documentation at the end of this data sheet.

Table 2-3. Number of Slices Required For Implementing Distributed RAM

|                  | SPR16x2 | DPR16x2 |

|------------------|---------|---------|

| Number of Slices | 1       | 2       |

Note: SPR = Single Port RAM, DPR = Dual Port RAM

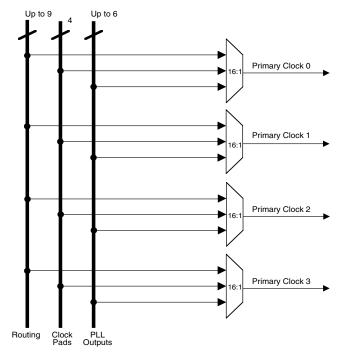

Figure 2-8. Primary Clocks for LA-MachXO1200 and LA-MachXO2280 Devices

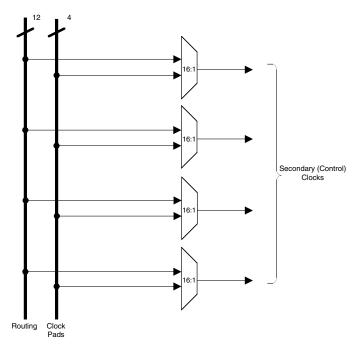

Four secondary clocks are generated from four 16:1 muxes as shown in Figure 2-9. Four of the secondary clock sources come from dual function clock pins and 12 come from internal routing.

Figure 2-9. Secondary Clocks for LA-MachXO Devices

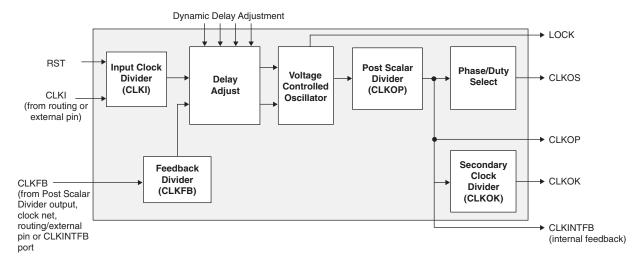

#### sysCLOCK Phase Locked Loops (PLLs)

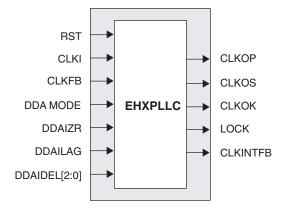

The LA-MachXO1200 and LA-MachXO2280 provide PLL support. The source of the PLL input divider can come from an external pin or from internal routing. There are four sources of feedback signals to the feedback divider: from CLKINTFB (internal feedback port), from the global clock nets, from the output of the post scalar divider, and from the routing (or from an external pin). There is a PLL\_LOCK signal to indicate that the PLL has locked on to the input clock signal. Figure 2-10 shows the sysCLOCK PLL diagram.

The setup and hold times of the device can be improved by programming a delay in the feedback or input path of the PLL which will advance or delay the output clock with reference to the input clock. This delay can be either programmed during configuration or can be adjusted dynamically. In dynamic mode, the PLL may lose lock after adjustment and not relock until the t<sub>LOCK</sub> parameter has been satisfied. Additionally, the phase and duty cycle block allows the user to adjust the phase and duty cycle of the CLKOS output.

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. Each PLL has four dividers associated with it: input clock divider, feedback divider, post scalar divider, and secondary clock divider. The input clock divider is used to divide the input clock signal, while the feedback divider is used to multiply the input clock signal. The post scalar divider allows the VCO to operate at higher frequencies than the clock output, thereby increasing the frequency range. The secondary divider is used to derive lower frequency outputs.

Figure 2-10. PLL Diagram

Figure 2-11 shows the available macros for the PLL. Table 2-5 provides signal description of the PLL Block.

Figure 2-11. PLL Primitive

of the devices also support differential input buffers. PCI clamps are available on the top Bank I/O buffers. The PCI clamp is enabled after  $V_{CC}$ ,  $V_{CCAUX}$ , and  $V_{CCIO}$  are at valid operating levels and the device has been configured.

The two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential input buffer and the comp (complementary) pad is associated with the negative side of the differential input buffer.

#### 2. Left and Right sysIO Buffer Pairs

The sysIO buffer pairs in the left and right Banks of the device consist of two single-ended output drivers and two sets of single-ended input buffers (supporting ratioed and absolute input levels). The devices also have a differential driver per output pair. The referenced input buffer can also be configured as a differential input buffer. In these Banks the two pads in the pair are described as "true" and "comp", where the true pad is associated with the positive side of the differential I/O, and the comp (complementary) pad is associated with the negative side of the differential I/O.

#### Typical I/O Behavior During Power-up

The internal power-on-reset (POR) signal is deactivated when  $V_{CC}$  and  $V_{CCAUX}$  have reached satisfactory levels. After the POR signal is deactivated, the FPGA core logic becomes active. It is the user's responsibility to ensure that all  $V_{CCIO}$  Banks are active with valid input logic levels to properly control the output logic states of all the I/O Banks that are critical to the application. The default configuration of the I/O pins in a blank device is tri-state with a weak pull-up to VCCIO. The I/O pins will maintain the blank configuration until VCC, VCCAUX and VCCIO have reached satisfactory levels at which time the I/Os will take on the user-configured settings.

The  $V_{CC}$  and  $V_{CCAUX}$  supply the power to the FPGA core fabric, whereas the  $V_{CCIO}$  supplies power to the I/O buffers. In order to simplify system design while providing consistent and predictable I/O behavior, the I/O buffers should be powered up along with the FPGA core fabric. Therefore,  $V_{CCIO}$  supplies should be powered up before or together with the  $V_{CC}$  and  $V_{CCAUX}$  supplies

#### **Supported Standards**

The LA-MachXO sysIO buffer supports both single-ended and differential standards. Single-ended standards can be further subdivided into LVCMOS and LVTTL. The buffer supports the LVTTL, LVCMOS 1.2, 1.5, 1.8, 2.5, and 3.3V standards. In the LVCMOS and LVTTL modes, the buffer has individually configurable options for drive strength, bus maintenance (weak pull-up, weak pull-down, bus-keeper latch or none) and open drain. BLVDS and LVPECL output emulation is supported on all devices. The LA-MachXO1200 and LA-MachXO2280 support on-chip LVDS output buffers on approximately 50% of the I/Os on the left and right Banks. Differential receivers for LVDS, BLVDS and LVPECL are supported on all Banks of LA-MachXO1200 and LA-MachXO2280 devices. PCI support is provided in the top Banks of the LA-MachXO1200 and LA-MachXO2280 devices. Table 2-8 summarizes the I/O characteristics of the devices in the LA-MachXO family.

Tables 2-9 and 2-10 show the I/O standards (together with their supply and reference voltages) supported by the LA-MachXO devices. For further information on utilizing the sysIO buffer to support a variety of standards please see the details of additional technical documentation at the end of this data sheet.

Table 2-10. Supported Output Standards

| Output Standard          | Drive                | V <sub>CCIO</sub> (Typ.) |

|--------------------------|----------------------|--------------------------|

| Single-ended Interfaces  |                      |                          |

| LVTTL                    | 4mA, 8mA, 12mA, 16mA | 3.3                      |

| LVCMOS33                 | 4mA, 8mA, 12mA, 14mA | 3.3                      |

| LVCMOS25                 | 4mA, 8mA, 12mA, 14mA | 2.5                      |

| LVCMOS18                 | 4mA, 8mA, 12mA, 14mA | 1.8                      |

| LVCMOS15                 | 4mA, 8mA             | 1.5                      |

| LVCMOS12                 | 2mA, 6mA             | 1.2                      |

| LVCMOS33, Open Drain     | 4mA, 8mA, 12mA, 14mA | _                        |

| LVCMOS25, Open Drain     | 4mA, 8mA, 12mA, 14mA | _                        |

| LVCMOS18, Open Drain     | 4mA, 8mA, 12mA, 14mA | _                        |

| LVCMOS15, Open Drain     | 4mA, 8mA             | _                        |

| LVCMOS12, Open Drain     | 2mA, 6mA             | _                        |

| PCI33 <sup>3</sup>       | N/A                  | 3.3                      |

| Differential Interfaces  |                      |                          |

| LVDS <sup>1, 2</sup>     | N/A                  | 2.5                      |

| BLVDS, RSDS <sup>2</sup> | N/A                  | 2.5                      |

| LVPECL <sup>2</sup>      | N/A                  | 3.3                      |

<sup>1.</sup> LA-MachXO1200 and LA-MachXO2280 devices have dedicated LVDS buffers.

#### sysIO Buffer Banks

The number of Banks vary between the devices of this family. Eight Banks surround the two larger devices, the LA-MachXO1200 and LA-MachXO2280 (two Banks per side). The LA-MachXO640 has four Banks (one Bank per side). The smallest member of this family, the LA-MachXO256, has only two Banks.

Each sysIO buffer Bank is capable of supporting multiple I/O standards. Each Bank has its own I/O supply voltage  $(V_{CCIO})$  which allows it to be completely independent from the other Banks. Figure 2-18, Figure 2-18, Figure 2-20 and Figure 2-21 shows the sysIO Banks and their associated supplies for all devices.

<sup>2.</sup> These interfaces can be emulated with external resistors in all devices.

<sup>3.</sup> Top Banks of LA-MachXO1200 and LA-MachXO2280 devices only.

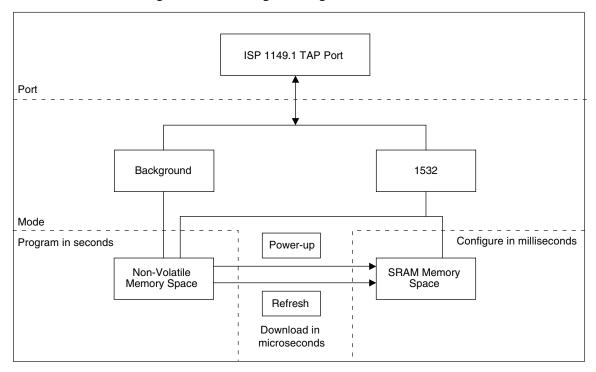

#### **Device Configuration**

All LA-MachXO devices contain a test access port that can be used for device configuration and programming.

The non-volatile memory in the LA-MachXO can be configured in two different modes:

- In IEEE 1532 mode via the IEEE 1149.1 port. In this mode, the device is off-line and I/Os are controlled by BSCAN registers.

- In background mode via the IEEE 1149.1 port. This allows the device to remain operational in user mode while reprogramming takes place.

The SRAM configuration memory can be configured in three different ways:

- At power-up via the on-chip non-volatile memory.

- After a refresh command is issued via the IEEE 1149.1 port.

- In IEEE 1532 mode via the IEEE 1149.1 port.

Figure 2-22 provides a pictorial representation of the different programming modes available in the LA-MachXO devices. On power-up, the SRAM is ready to be configured with IEEE 1149.1 serial TAP port using IEEE 1532 protocols.

#### Leave Alone I/O

When using IEEE 1532 mode for non-volatile memory programming, SRAM configuration, or issuing a refresh command, users may specify I/Os as high, low, tristated or held at current value. This provides excellent flexibility for implementing systems where reconfiguration or reprogramming occurs on-the-fly.

#### TransFR (<u>Trans</u>parent <u>Field Reconfiguration</u>)

TransFR (TFR) is a unique Lattice technology that allows users to update their logic in the field without interrupting system operation using a single ispVM command. See Lattice technical note #TN1087, *Minimizing System Interruption During Configuration Using TransFR Technology*, for details.

#### Security

The LA-MachXO automotive devices contain security bits that, when set, prevent the readback of the SRAM configuration and non-volatile memory spaces. Once set, the only way to clear the security bits is to erase the memory space.

For more information on device configuration, please see details of additional technical documentation at the end of this data sheet.

#### AEC-Q100 Tested and Qualified

The Automotive Electronics Council (AEC) consists of two committees: the Quality Systems Committee and the Component Technical Committee. These committees are composed of representatives from sustaining and other associate members. The AEC Component Technical Committee is the standardization body for establishing standards for reliable, high quality electronic components. In particular, the AEC-Q100 specification "Stress Test for Qualification for Integrated Circuits" defines qualification and re-qualification requirements for electronic components. Components meeting these specifications are suitable for use in the harsh automotive environment without additional component-level qualification testing. Lattice's LA-ispMACH 4000V and LA-MachXO devices completed and passed the requirements of the AEC-Q100 specification.

Figure 2-22. LA-MachXO Configuration and Programming

#### **Density Shifting**

The LA-MachXO family has been designed to enable density migration in the same package. Furthermore, the architecture ensures a high success rate when performing design migration from lower density parts to higher density parts. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likely success in each case.

### LA-MachXO1200 and LA-MachXO2280 Hot Socketing Specifications<sup>1, 2, 3, 4</sup>

| Symbol                                | Parameter                       | Condition                           | Min. | Тур. | Max.    | Units |

|---------------------------------------|---------------------------------|-------------------------------------|------|------|---------|-------|

| Non-LVDS G                            | Non-LVDS General Purpose syslOs |                                     |      |      |         |       |

| I <sub>DK</sub>                       | Input or I/O Leakage Current    | $0 \le V_{IN} \le V_{IH} (MAX.)$    | _    | _    | +/-1000 | μA    |

| LVDS Genera                           | al Purpose syslOs               |                                     |      |      |         |       |

| lau waa                               | Input or I/O Leakage Current    | V <sub>IN</sub> ≤ V <sub>CCIO</sub> | _    | _    | +/-1000 | μΑ    |

| IDK_LVDS Input or I/O Leakage Current |                                 | $V_{IN} > V_{CCIO}$                 | _    | 35   | _       | mA    |

- 1. Insensitive to sequence of  $V_{CC, V_{CCAUX}}$ , and  $V_{CCIO}$ . However, assumes monotonic rise/fall rates for  $V_{CC, V_{CCAUX}}$ , and  $V_{CCIO}$ . 2.  $0 \le V_{CC} \le V_{CC}$  (MAX),  $0 \le V_{CCIO} \le V_{CCIO}$  (MAX), and  $0 \le V_{CCAUX} \le V_{CCAUX}$  (MAX).

- 3.  $I_{DK}$  is additive to  $I_{PU}$ ,  $I_{PW}$  or  $I_{BH}$ .

- 4. LVCMOS and LVTTL only.

#### **DC Electrical Characteristics**

#### **Over Recommended Operating Conditions**

| Symbol                                   | Parameter                                | Condition                                                                                    | Min.                  | Тур. | Max.                  | Units |

|------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------|------|-----------------------|-------|

| I <sub>IL,</sub> I <sub>IH</sub> 1, 4, 5 | Input or I/O Leakage                     | $0 \le V_{IN} \le (V_{CCIO} - 0.2V)$                                                         | _                     | _    | 10                    | μΑ    |

| I'IL, 'IH                                | linput of 1/O Leakage                    | $(V_{CCIO} - 0.2V) < V_{IN} \le 3.6V$                                                        | _                     | _    | 40                    | μΑ    |

| I <sub>PU</sub>                          | I/O Active Pull-up Current               | $0 \le V_{IN} \le 0.7 V_{CCIO}$                                                              | -30                   | _    | -150                  | μΑ    |

| I <sub>PD</sub>                          | I/O Active Pull-down Current             | $V_{IL}$ (MAX) $\leq V_{IN} \leq V_{IH}$ (MAX)                                               | 30                    | _    | 150                   | μΑ    |

| I <sub>BHLS</sub>                        | Bus Hold Low sustaining current          | $V_{IN} = V_{IL} (MAX)$                                                                      | 30                    |      | _                     | μΑ    |

| I <sub>BHHS</sub>                        | Bus Hold High sustaining current         | $V_{IN} = 0.7V_{CCIO}$                                                                       | -30                   | _    | _                     | μΑ    |

| I <sub>BHLO</sub>                        | Bus Hold Low Overdrive current           | $0 \le V_{IN} \le V_{IH} (MAX)$                                                              | _                     | _    | 150                   | μΑ    |

| I <sub>BHHO</sub>                        | Bus Hold High Overdrive current          | $0 \le V_{IN} \le V_{IH} (MAX)$                                                              | _                     |      | -150                  | μΑ    |

| V <sub>BHT</sub> <sup>3</sup>            | Bus Hold trip Points                     | $0 \le V_{IN} \le V_{IH} (MAX)$                                                              | V <sub>IL</sub> (MAX) | _    | V <sub>IH</sub> (MIN) | V     |

| C1                                       | I/O Capacitance <sup>2</sup>             | $V_{CCIO} = 3.3V$ , 2.5V, 1.8V, 1.5V, 1.2V, $V_{CC} = Typ.$ , $V_{IO} = 0$ to $V_{IH}$ (MAX) | _                     | 8    | _                     | pf    |

| C2                                       | Dedicated Input Capacitance <sup>2</sup> | $V_{CCIO} = 3.3V, 2.5V, 1.8V, 1.5V, 1.2V, V_{CC} = Typ., V_{IO} = 0 to V_{IH} (MAX)$         | _                     | 8    | _                     | pf    |

<sup>1.</sup> Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

- 2.  $T_A$  25°C, f = 1.0MHz

- 3. Please refer to  $V_{IL}$  and  $V_{IH}$  in the sysIO Single-Ended DC Electrical Characteristics table of this document.

- 4. Not applicable to SLEEPN pin.

- 5. When VIH is higher than VCCIO, a transient current typically of 30ns in duration or less with a peak current of 6mA can occur on the high-tolow transition. For LA-MachXO1200 and LA-MachXO2280 true LVDS output pins, VIH must be less than or equal to VCIIO.

## Supply Current (Sleep Mode)<sup>1, 2</sup>

| Symbol                   | Parameter                      | Device                | Typ. <sup>3</sup> | Max. | Units |

|--------------------------|--------------------------------|-----------------------|-------------------|------|-------|

| 1                        | Cara Bawar Curah               | LCMXO256C             | 12                | 25   | μΑ    |

| I <sub>CC</sub> Core Pow | Core Power Supply              | LCMXO640C             | 12                | 25   | μΑ    |

| I <sub>CCAUX</sub>       | Auxiliary Power Supply         | LCMXO256C             | 1                 | 15   | μΑ    |

|                          |                                | LCMXO640C             | 1                 | 25   | μΑ    |

| I <sub>CCIO</sub>        | Bank Power Supply <sup>4</sup> | All LCMXO 'C' Devices | 2                 | 30   | μΑ    |

- 1. Assumes all inputs are configured as LVCMOS and held at the VCCIO or GND.

- 2. Frequency = 0MHz.

- 3.  $T_A = 25$ °C, power supplies at nominal voltage.

- 4. Per Bank.

## Supply Current (Standby)<sup>1, 2, 3, 4</sup>

#### **Over Recommended Operating Conditions**

| Symbol            | Parameter                                        | Device      | Typ.⁵ | Units |

|-------------------|--------------------------------------------------|-------------|-------|-------|

|                   |                                                  | LCMXO256C   | 7     | mA    |

|                   |                                                  | LCMXO640C   | 9     | mA    |

| 1                 | Coro Power Supply                                | LCMXO256E   | 4     | mA    |

| lcc               | Core Power Supply                                | LCMXO640E   | 6     | mA    |

|                   |                                                  | LCMXO1200E  | 10    | mA    |

|                   |                                                  | LCMXO2280E  | 12    | mA    |

|                   | Auxiliary Power Supply V <sub>CCAUX</sub> = 3.3V | LCMXO256E/C | 5     | mA    |

| 1                 |                                                  | LCMXO640E/C | 7     | mA    |

| CCAUX             |                                                  | LCMXO1200E  | 12    | mA    |

|                   |                                                  | LCMXO2280E  | 13    | mA    |

| I <sub>CCIO</sub> | Bank Power Supply <sup>6</sup>                   | All devices | 2     | mA    |

- 1. For further information on supply current, please see details of additional technical documentation at the end of this data sheet.

- 2. Assumes all outputs are tristated, all inputs are configured as LVCMOS and held at  $V_{CCIO}$  or GND.

- 3. Frequency = 0MHz.

- 4. User pattern = blank.

- 5.  $T_J = 25^{\circ}C$ , power supplies at nominal voltage.

- 6. Per Bank. V<sub>CCIO</sub> = 2.5V. Does not include pull-up/pull-down.

## sysIO Recommended Operating Conditions

|                      | V <sub>CCIO</sub> (V) |      |       |

|----------------------|-----------------------|------|-------|

| Standard             | Min.                  | Тур. | Max.  |

| LVCMOS 3.3           | 3.135                 | 3.3  | 3.465 |

| LVCMOS 2.5           | 2.375                 | 2.5  | 2.625 |

| LVCMOS 1.8           | 1.71                  | 1.8  | 1.89  |

| LVCMOS 1.5           | 1.425                 | 1.5  | 1.575 |

| LVCMOS 1.2           | 1.14                  | 1.2  | 1.26  |

| LVTTL                | 3.135                 | 3.3  | 3.465 |

| PCI <sup>3</sup>     | 3.135                 | 3.3  | 3.465 |

| LVDS <sup>1, 2</sup> | 2.375                 | 2.5  | 2.625 |

| LVPECL1              | 3.135                 | 3.3  | 3.465 |

| BLVDS <sup>1</sup>   | 2.375                 | 2.5  | 2.625 |

| RSDS <sup>1</sup>    | 2.375                 | 2.5  | 2.625 |

<sup>1.</sup> Inputs on chip. Outputs are implemented with the addition of external resistors.

<sup>2.</sup> MachXO1200 and MachXO2280 devices have dedicated LVDS buffers

<sup>3.</sup> Input on the top bank of the MachXO1200 and MachXO2280 only.

Table 3-1. LVDS DC Conditions

#### **Over Recommended Operating Conditions**

| Parameter         | Description                 | Typical | Units |

|-------------------|-----------------------------|---------|-------|

| Z <sub>OUT</sub>  | Output impedance            | 20      | Ω     |

| R <sub>S</sub>    | Driver series resistor      | 294     | Ω     |

| R <sub>P</sub>    | Driver parallel resistor    | 121     | Ω     |

| R <sub>T</sub>    | Receiver termination        | 100     | Ω     |

| V <sub>OH</sub>   | Output high voltage         | 1.43    | V     |

| V <sub>OL</sub>   | Output low voltage          | 1.07    | V     |

| V <sub>OD</sub>   | Output differential voltage | 0.35    | V     |

| V <sub>CM</sub>   | Output common mode voltage  | 1.25    | V     |

| Z <sub>BACK</sub> | Back impedance              | 100     | Ω     |

| I <sub>DC</sub>   | DC output current           | 3.66    | mA    |

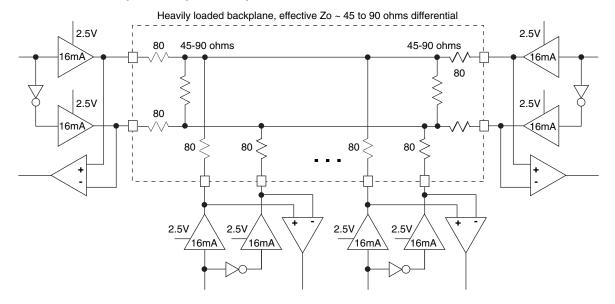

#### **BLVDS**

The LA-MachXO automotive family supports the BLVDS standard through emulation. The output is emulated using complementary LVCMOS outputs in conjunction with a parallel external resistor across the driver outputs. The input standard is supported by the LVDS differential input buffer on certain devices. BLVDS is intended for use when multi-drop and bi-directional multi-point differential signaling is required. The scheme shown in Figure 3-2 is one possible solution for bi-directional multi-point differential signals.

Figure 3-2. BLVDS Multi-point Output Example

## LA-MachXO Internal Timing Parameters<sup>1</sup>

#### **Over Recommended Operating Conditions**

|                         |                                                              | _        | 3    |       |

|-------------------------|--------------------------------------------------------------|----------|------|-------|

| Parameter               | Description                                                  | Min.     | Max. | Units |

| PFU/PFF Log             | jic Mode Timing                                              |          |      |       |

| t <sub>LUT4_PFU</sub>   | LUT4 delay (A to D inputs to F output)                       | _        | 0.39 | ns    |

| t <sub>LUT6_PFU</sub>   | LUT6 delay (A to D inputs to OFX output)                     | <b>—</b> | 0.62 | ns    |

| t <sub>LSR_PFU</sub>    | Set/Reset to output of PFU                                   | _        | 1.26 | ns    |

| t <sub>SUM_PFU</sub>    | Clock to Mux (M0,M1) input setup time                        | 0.15     | _    | ns    |

| t <sub>HM_PFU</sub>     | Clock to Mux (M0,M1) input hold time                         | -0.07    | _    | ns    |

| t <sub>SUD_PFU</sub>    | Clock to D input setup time                                  | 0.18     | _    | ns    |

| t <sub>HD_PFU</sub>     | Clock to D input hold time                                   | -0.04    | _    | ns    |

| t <sub>CK2Q_PFU</sub>   | Clock to Q delay, D-type register configuration              | _        | 0.56 | ns    |

| t <sub>LE2Q_PFU</sub>   | Clock to Q delay latch configuration                         | _        | 0.74 | ns    |

| t <sub>LD2Q_PFU</sub>   | D to Q throughput delay when latch is enabled                | _        | 0.77 | ns    |

|                         | rt Memory Mode Timing                                        |          |      |       |

| t <sub>CORAM_PFU</sub>  | Clock to Output                                              | —        | 0.56 | ns    |

| t <sub>SUDATA_PFU</sub> | Data Setup Time                                              | -0.25    | _    | ns    |

| t <sub>HDATA_PFU</sub>  | Data Hold Time                                               | 0.39     | _    | ns    |

| t <sub>SUADDR_PFU</sub> | Address Setup Time                                           | -0.65    | _    | ns    |

| t <sub>HADDR_PFU</sub>  | Address Hold Time                                            | 0.99     | _    | ns    |

| t <sub>SUWREN_PFU</sub> | Write/Read Enable Setup Time                                 | -0.30    | _    | ns    |

| t <sub>HWREN_PFU</sub>  | Write/Read Enable Hold Time                                  | 0.47     | _    | ns    |

| PIO Input/Ou            | tput Buffer Timing                                           |          |      |       |

| t <sub>IN_PIO</sub>     | Input Buffer Delay                                           | _        | 1.06 | ns    |

| t <sub>OUT_PIO</sub>    | Output Buffer Delay                                          | _        | 1.80 | ns    |

| EBR Timing (            | 1200 and 2280 Devices Only)                                  |          |      |       |

| t <sub>CO_EBR</sub>     | Clock to output from Address or Data with no output register | _        | 3.14 | ns    |

| t <sub>COO_EBR</sub>    | Clock to output from EBR output Register                     | _        | 0.75 | ns    |

| t <sub>SUDATA_EBR</sub> | Setup Data to EBR Memory                                     | -0.37    | _    | ns    |

| t <sub>HDATA_EBR</sub>  | Hold Data to EBR Memory                                      | 0.57     | _    | ns    |

| t <sub>SUADDR_EBR</sub> | Setup Address to EBR Memory                                  | -0.37    | _    | ns    |

| t <sub>HADDR_EBR</sub>  | Hold Address to EBR Memory                                   | 0.57     | _    | ns    |

| t <sub>SUWREN_EBR</sub> | Setup Write/Read Enable to EBR Memory                        | -0.23    | _    | ns    |

| t <sub>HWREN_EBR</sub>  | Hold Write/Read Enable to EBR Memory                         | 0.36     | _    | ns    |

| t <sub>SUCE_EBR</sub>   | Clock Enable Setup Time to EBR Output Register               | 0.27     | _    | ns    |

| t <sub>HCE_EBR</sub>    | Clock Enable Hold Time to EBR Output Register                | -0.18    | _    | ns    |

| t <sub>RSTO_EBR</sub>   | Reset To Output Delay Time from EBR Output Register          | _        | 1.44 | ns    |

| PLL Paramet             | ers (1200 and 2280 Devices Only)                             |          | •    | •     |

| t <sub>RSTREC</sub>     | Reset Recovery to Rising Clock                               | _        | 1.00 | ns    |

| t <sub>RSTSU</sub>      | Reset Signal Setup Time                                      | 1.00     | _    | ns    |

<sup>1.</sup> Internal parameters are characterized but not tested on every device. Rev. A 0.19

## LA-MachXO Family Timing Adders<sup>1, 2, 3</sup>

#### **Over Recommended Operating Conditions**

| Buffer Type           | Description           | -3    | Units |

|-----------------------|-----------------------|-------|-------|

| Input Adjusters       | ·                     |       |       |

| LVDS25 <sup>4</sup>   | LVDS                  | 0.61  | ns    |

| BLVDS25 <sup>4</sup>  | BLVDS                 | 0.61  | ns    |

| LVPECL33 <sup>4</sup> | LVPECL                | 0.59  | ns    |

| LVTTL33               | LVTTL                 | 0.01  | ns    |

| LVCMOS33              | LVCMOS 3.3            | 0.01  | ns    |

| LVCMOS25              | LVCMOS 2.5            | 0.00  | ns    |

| LVCMOS18              | LVCMOS 1.8            | 0.10  | ns    |

| LVCMOS15              | LVCMOS 1.5            | 0.19  | ns    |

| LVCMOS12              | LVCMOS 1.2            | 0.56  | ns    |

| PCI33 <sup>4</sup>    | PCI                   | 0.01  | ns    |

| Output Adjusters      |                       |       |       |

| LVDS25E               | LVDS 2.5 E            | -0.18 | ns    |

| LVDS25 <sup>4</sup>   | LVDS 2.5              | -0.30 | ns    |

| BLVDS25               | BLVDS 2.5             | -0.04 | ns    |

| LVPECL33              | LVPECL 3.3            | 0.05  | ns    |

| LVTTL33_4mA           | LVTTL 4mA drive       | 0.05  | ns    |

| LVTTL33_8mA           | LVTTL 8mA drive       | 0.08  | ns    |

| LVTTL33_12mA          | LVTTL 12mA drive      | -0.01 | ns    |

| LVTTL33_16mA          | LVTTL 16mA drive      | 0.70  | ns    |

| LVCMOS33_4mA          | LVCMOS 3.3 4mA drive  | 0.05  | ns    |

| LVCMOS33_8mA          | LVCMOS 3.3 8mA drive  | 0.08  | ns    |

| LVCMOS33_12mA         | LVCMOS 3.3 12mA drive | -0.01 | ns    |

| LVCMOS33_14mA         | LVCMOS 3.3 14mA drive | 0.70  | ns    |

| LVCMOS25_4mA          | LVCMOS 2.5 4mA drive  | 0.07  | ns    |

| LVCMOS25_8mA          | LVCMOS 2.5 8mA drive  | 0.13  | ns    |

| LVCMOS25_12mA         | LVCMOS 2.5 12mA drive | 0.00  | ns    |

| LVCMOS25_14mA         | LVCMOS 2.5 14mA drive | 0.47  | ns    |

| LVCMOS18_4mA          | LVCMOS 1.8 4mA drive  | 0.15  | ns    |

| LVCMOS18_8mA          | LVCMOS 1.8 8mA drive  | 0.06  | ns    |

| LVCMOS18_12mA         | LVCMOS 1.8 12mA drive | -0.08 | ns    |

| LVCMOS18_14mA         | LVCMOS 1.8 14mA drive | 0.09  | ns    |

| LVCMOS15_4mA          | LVCMOS 1.5 4mA drive  | 0.22  | ns    |

| LVCMOS15_8mA          | LVCMOS 1.5 8mA drive  | 0.07  | ns    |

| LVCMOS12_2mA          | LVCMOS 1.2 2mA drive  | 0.36  | ns    |

| LVCMOS12_6mA          | LVCMOS 1.2 6mA drive  | 0.07  | ns    |

| PCI33 <sup>4</sup>    | PCI33                 | 2.59  | ns    |

<sup>1.</sup> Timing adders are characterized but not tested on every device.

Rev. A 0.19

<sup>2.</sup> LVCMOS timing is measured with the load specified in Switching Test Conditions table.

<sup>3.</sup> All other standards tested according to the appropriate specifications.

<sup>4.</sup> I/O standard only available in LCMXO1200 and LCMXO2280 devices.

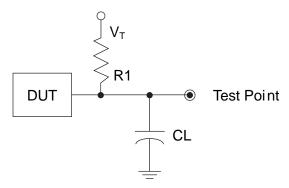

#### **Switching Test Conditions**

Figure 3-6 shows the output test load that is used for AC testing. The specific values for resistance, capacitance, voltage, and other test conditions are shown in Figure 3-5.

Figure 3-6. Output Test Load, LVTTL and LVCMOS Standards

Table 3-5. Test Fixture Required Components, Non-Terminated Interfaces

| Test Condition                             | R <sub>1</sub> | CL  | Timing Ref.                       | V <sub>T</sub>  |

|--------------------------------------------|----------------|-----|-----------------------------------|-----------------|

|                                            |                |     | LVTTL, LVCMOS 3.3 = 1.5V          | _               |

|                                            | ∞              | 0pF | LVCMOS 2.5 = V <sub>CCIO</sub> /2 | _               |

| LVTTL and LVCMOS settings (L -> H, H -> L) |                |     | LVCMOS 1.8 = V <sub>CCIO</sub> /2 | _               |

|                                            |                |     | LVCMOS 1.5 = V <sub>CCIO</sub> /2 | _               |

|                                            |                |     | LVCMOS 1.2 = V <sub>CCIO</sub> /2 | _               |

| LVTTL and LVCMOS 3.3 (Z -> H)              |                |     | 1.5                               | V <sub>OL</sub> |

| LVTTL and LVCMOS 3.3 (Z -> L)              |                |     | 1.5                               | V <sub>OH</sub> |

| Other LVCMOS (Z -> H)                      | 188            | 0pF | V <sub>CCIO</sub> /2              | V <sub>OL</sub> |

| Other LVCMOS (Z -> L)                      | 100            | Орг | V <sub>CCIO</sub> /2              | V <sub>OH</sub> |

| LVTTL + LVCMOS (H -> Z)                    |                |     | V <sub>OH</sub> - 0.15            | V <sub>OL</sub> |

| LVTTL + LVCMOS (L -> Z)                    |                |     | V <sub>OL</sub> - 0.15            | V <sub>OH</sub> |

Note: Output test conditions for all other interfaces are determined by the respective standards.

# LA-MachXO1200 and LA-MachXO2280 Logic Signal Connections: 100 TQFP

|               |                  |      | LAMXO1200        | LAMXO2280    |                  |      |                  |              |  |

|---------------|------------------|------|------------------|--------------|------------------|------|------------------|--------------|--|

| Pin<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Function | Bank | Dual<br>Function | Differential |  |

| 1             | PL2A             | 7    |                  | Т            | PL2A             | 7    | LUM0_PLLT_FB_A   | T            |  |

| 2             | PL2B             | 7    |                  | С            | PL2B             | 7    | LUM0_PLLC_FB_A   | С            |  |

| 3             | PL3C             | 7    |                  | Т            | PL3C             | 7    | LUM0_PLLT_IN_A   | Т            |  |

| 4             | PL3D             | 7    |                  | С            | PL3D             | 7    | LUM0_PLLC_IN_A   | С            |  |

| 5             | PL4B             | 7    |                  |              | PL4B             | 7    |                  |              |  |

| 6             | VCCIO7           | 7    |                  |              | VCCIO7           | 7    |                  |              |  |

| 7             | PL6A             | 7    |                  | T*           | PL7A             | 7    |                  | T*           |  |

| 8             | PL6B             | 7    | GSRN             | C*           | PL7B             | 7    | GSRN             | C*           |  |

| 9             | GND              | -    |                  |              | GND              | -    |                  |              |  |

| 10            | PL7C             | 7    |                  | Т            | PL9C             | 7    |                  | Т            |  |

| 11            | PL7D             | 7    |                  | С            | PL9D             | 7    |                  | С            |  |

| 12            | PL8C             | 7    |                  | Т            | PL10C            | 7    |                  | Т            |  |

| 13            | PL8D             | 7    |                  | С            | PL10D            | 7    |                  | С            |  |

| 14            | PL9C             | 6    |                  |              | PL11C            | 6    |                  |              |  |

| 15            | PL10A            | 6    |                  | T*           | PL13A            | 6    |                  | T*           |  |

| 16            | PL10B            | 6    |                  | C*           | PL13B            | 6    |                  | C*           |  |

| 17            | VCC              | -    |                  |              | VCC              | -    |                  |              |  |

| 18            | PL11B            | 6    |                  |              | PL14D            | 6    |                  | С            |  |

| 19            | PL11C            | 6    | TSALL            |              | PL14C            | 6    | TSALL            | T            |  |

| 20            | VCCIO6           | 6    |                  |              | VCCIO6           | 6    |                  |              |  |

| 21            | PL13C            | 6    |                  |              | PL16C            | 6    |                  |              |  |

| 22            | PL14A            | 6    | LLM0_PLLT_FB_A   | T*           | PL17A            | 6    | LLM0_PLLT_FB_A   | T*           |  |

| 23            | PL14B            | 6    | LLM0_PLLC_FB_A   | C*           | PL17B            | 6    | LLM0_PLLC_FB_A   | C*           |  |

| 24            | PL15A            | 6    | LLM0_PLLT_IN_A   | T*           | PL18A            | 6    | LLM0_PLLT_IN_A   | T*           |  |

| 25            | PL15B            | 6    | LLM0_PLLC_IN_A   | C*           | PL18B            | 6    | LLM0_PLLC_IN_A   | C*           |  |

| 26**          | GNDIO6<br>GNDIO5 | -    |                  |              | GNDIO6<br>GNDIO5 | -    |                  |              |  |

| 27            | VCCIO5           | 5    |                  |              | VCCIO5           | 5    |                  |              |  |

| 28            | TMS              | 5    | TMS              |              | TMS              | 5    | TMS              |              |  |

| 29            | TCK              | 5    | TCK              |              | TCK              | 5    | TCK              |              |  |

| 30            | PB3B             | 5    |                  |              | PB3B             | 5    |                  |              |  |

| 31            | PB4A             | 5    |                  | Т            | PB4A             | 5    |                  | Т            |  |

| 32            | PB4B             | 5    |                  | С            | PB4B             | 5    |                  | С            |  |

| 33            | TDO              | 5    | TDO              |              | TDO              | 5    | TDO              |              |  |

| 34            | TDI              | 5    | TDI              |              | TDI              | 5    | TDI              |              |  |

| 35            | VCC              | -    |                  |              | VCC              | -    |                  |              |  |

| 36            | VCCAUX           | -    |                  |              | VCCAUX           | -    |                  |              |  |

| 37            | PB6E             | 5    |                  | Т            | PB8E             | 5    |                  | Т            |  |

| 38            | PB6F             | 5    |                  | С            | PB8F             | 5    |                  | С            |  |

| 39            | PB7B             | 4    | PCLK4_1***       |              | PB10F            | 4    | PCLK4_1***       |              |  |

| 40            | PB7F             | 4    | PCLK4_0***       |              | PB10B            | 4    | PCLK4_0***       |              |  |

## LA-MachXO1200 and LA-MachXO2280 Logic Signal Connections: 100 TQFP (Cont.)

|               |                  | L    | AMXO1200         |              | LAMXO2280        |      |                  |              |  |

|---------------|------------------|------|------------------|--------------|------------------|------|------------------|--------------|--|

| Pin<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Function | Bank | Dual<br>Function | Differential |  |

| 41            | GND              | -    |                  |              | GND              | -    |                  |              |  |

| 42            | PB9A             | 4    |                  | Т            | PB12A            | 4    |                  | Т            |  |

| 43            | PB9B             | 4    |                  | С            | PB12B            | 4    |                  | С            |  |

| 44            | VCCIO4           | 4    |                  |              | VCCIO4           | 4    |                  |              |  |

| 45            | PB10A            | 4    |                  | Т            | PB13A            | 4    |                  | Т            |  |

| 46            | PB10B            | 4    |                  | С            | PB13B            | 4    |                  | С            |  |

| 47            | NC               | -    | NC               |              | NC               | -    | NC               |              |  |

| 48            | PB11A            | 4    |                  | Т            | PB16A            | 4    |                  | Т            |  |

| 49            | PB11B            | 4    |                  | С            | PB16B            | 4    |                  | С            |  |

| 50**          | GNDIO3<br>GNDIO4 | -    |                  |              | GNDIO3<br>GNDIO4 | -    |                  |              |  |

| 51            | PR16B            | 3    |                  |              | PR19B            | 3    |                  |              |  |

| 52            | PR15B            | 3    |                  | C*           | PR18B            | 3    |                  | C*           |  |

| 53            | PR15A            | 3    |                  | T*           | PR18A            | 3    |                  | T*           |  |

| 54            | PR14B            | 3    |                  | C*           | PR17B            | 3    |                  | C*           |  |

| 55            | PR14A            | 3    |                  | T*           | PR17A            | 3    |                  | T*           |  |

| 56            | VCCIO3           | 3    |                  |              | VCCIO3           | 3    |                  |              |  |

| 57            | PR12B            | 3    |                  | C*           | PR15B            | 3    |                  | C*           |  |

| 58            | PR12A            | 3    |                  | T*           | PR15A            | 3    |                  | T*           |  |

| 59            | GND              | -    |                  |              | GND              | -    |                  |              |  |

| 60            | PR10B            | 3    |                  | C*           | PR13B            | 3    |                  | C*           |  |

| 61            | PR10A            | 3    |                  | T*           | PR13A            | 3    |                  | T*           |  |

| 62            | PR9B             | 3    |                  | C*           | PR11B            | 3    |                  | C*           |  |

| 63            | PR9A             | 3    |                  | T*           | PR11A            | 3    |                  | T*           |  |

| 64            | PR8B             | 2    |                  | C*           | PR10B            | 2    |                  | C*           |  |

| 65            | PR8A             | 2    |                  | T*           | PR10A            | 2    |                  | T*           |  |

| 66            | VCC              | -    |                  |              | VCC              | -    |                  |              |  |

| 67            | PR6C             | 2    |                  |              | PR8C             | 2    |                  |              |  |

| 68            | PR6B             | 2    |                  | C*           | PR8B             | 2    |                  | C*           |  |

| 69            | PR6A             | 2    |                  | T*           | PR8A             | 2    |                  | T*           |  |

| 70            | VCCIO2           | 2    |                  |              | VCCIO2           | 2    |                  |              |  |

| 71            | PR4D             | 2    |                  |              | PR5D             | 2    |                  |              |  |

| 72            | PR4B             | 2    |                  | C*           | PR5B             | 2    |                  | C*           |  |

| 73            | PR4A             | 2    |                  | T*           | PR5A             | 2    |                  | T*           |  |

| 74            | PR2B             | 2    |                  | С            | PR3B             | 2    |                  | C*           |  |

| 75            | PR2A             | 2    |                  | Т            | PR3A             | 2    |                  | T*           |  |

| 76**          | GNDIO1<br>GNDIO2 | -    |                  |              | GNDIO1<br>GNDIO2 | -    |                  |              |  |

| 77            | PT11C            | 1    |                  |              | PT15C            | 1    |                  |              |  |

| 78            | PT11B            | 1    |                  | С            | PT14B            | 1    |                  | С            |  |

| 79            | PT11A            | 1    |                  | Т            | PT14A            | 1    |                  | Т            |  |

## LA-MachXO640, LA-MachXO1200 and LA-MachXO2280 Logic Signal Connections: 256 ftBGA (Cont.)

| R2 - K5 K4 L5 L4 M5 M4 N4 N3 VCCIO3       | Ball Function PL8A PL8B PL11A PL11B - NC NC PL10C PL10D NC NC PL11C PL11D | 3 3 3 - 3 3 3 3 3 | Dual<br>Function | Differential T C T C | Ball<br>Number<br>J4<br>J5<br>R1<br>R2<br>-<br>K5 | Ball<br>Function<br>PL13A<br>PL13B<br>PL13C<br>PL13D | 8ank 6 6 6 6 | Dual<br>Function | Differential  T**  C** | Ball<br>Number<br>J4 | Ball<br>Function<br>PL16A | Bank<br>6 | Dual<br>Function | Differential |

|-------------------------------------------|---------------------------------------------------------------------------|-------------------|------------------|----------------------|---------------------------------------------------|------------------------------------------------------|--------------|------------------|------------------------|----------------------|---------------------------|-----------|------------------|--------------|

| J5 R1 R2 - K5 K4 L5 L4 M5 M4 N4 N3 VCCIO3 | PL8B PL11A PL11B  NC NC PL10C PL10C PL10D NC NC NC PL10D NC NC PL11C      | 3 3 -             |                  | C<br>T<br>C          | J5<br>R1<br>R2<br>-<br>K5                         | PL13B<br>PL13C<br>PL13D                              | 6            |                  | ·                      | J4                   | PL16A                     | 6         |                  | T**          |

| R1 R2 - K5 K4 L5 L4 M5 M4 N3 VCCIO3       | PL11A PL11B - NC NC PL10C PL10D NC NC PL10D PL10D NC NC PL11C             | 3 - 3             |                  | T<br>C               | R1<br>R2<br>-<br>K5                               | PL13C<br>PL13D                                       | 6            |                  | C**                    |                      |                           |           |                  | •            |

| R2 - K5 K4 L5 L4 M5 M4 N4 N3 VCCIO3       | PL11B - NC NC PL10C PL10D NC NC PC PL11D                                  | 3 -               |                  | С                    | R2<br>-<br>K5                                     | PL13D                                                | L            |                  |                        | J5                   | PL16B                     | 6         |                  | C**          |

| - K5 K4 L5 L4 M5 M4 N4 N3 VCCIO3          | PL10C NC PL10D NC NC PL10D                                                | 3                 |                  |                      | -<br>K5                                           | -                                                    | 6            |                  | Т                      | R1                   | PL16C                     | 6         |                  | T            |

| K5 K4 L5 L4 M5 M4 N4 N3 VCCIO3            | NC NC PL10C PL10D NC NC PL11C                                             | 3                 |                  | Т                    | K5                                                |                                                      |              |                  | С                      | R2                   | PL16D                     | 6         |                  | С            |

| K4 L5 L4 M5 M4 N4 N3 VCCIO3               | NC PL10C PL10D NC NC PL11C                                                |                   |                  | Т                    |                                                   |                                                      | -            |                  |                        | GND                  | GND                       | -         |                  |              |

| L5 L4 M5 M4 N4 N3 VCCIO3                  | PL10C PL10D NC NC PL11C                                                   |                   |                  | Т                    | K4                                                | PL14A                                                | 6            | LLM0_PLLT_FB_A   | T**                    | K5                   | PL17A                     | 6         | LLM0_PLLT_FB_A   | T**          |

| L4 M5 M4 N4 N3 VCCIO3 Y                   | PL10D<br>NC<br>NC<br>PL11C                                                |                   |                  | Т                    | <b></b>                                           | PL14B                                                | 6            | LLM0_PLLC_FB_A   | C**                    | K4                   | PL17B                     | 6         | LLM0_PLLC_FB_A   | C**          |

| M5<br>M4<br>N4<br>N3<br>VCCIO3            | NC<br>NC<br>PL11C                                                         | 3                 |                  |                      | L5                                                | PL14C                                                | 6            |                  | Т                      | L5                   | PL17C                     | 6         |                  | Т            |

| M4<br>N4<br>N3<br>VCCIO3                  | NC<br>PL11C                                                               |                   |                  | С                    | L4                                                | PL14D                                                | 6            |                  | С                      | L4                   | PL17D                     | 6         |                  | С            |

| N4<br>N3<br>VCCIO3                        | PL11C                                                                     |                   |                  |                      | M5                                                | PL15A                                                | 6            | LLM0_PLLT_IN_A   | T**                    | M5                   | PL18A                     | 6         | LLM0_PLLT_IN_A   | T**          |

| N3<br>VCCIO3                              |                                                                           |                   |                  |                      | M4                                                | PL15B                                                | 6            | LLM0_PLLC_IN_A   | C**                    | M4                   | PL18B                     | 6         | LLM0_PLLC_IN_A   | C**          |

| VCCIO3                                    | PL11D                                                                     | 3                 |                  | Т                    | N4                                                | PL16A                                                | 6            |                  | Т                      | N4                   | PL19A                     | 6         |                  | Т            |

|                                           |                                                                           | 3                 |                  | С                    | N3                                                | PL16B                                                | 6            |                  | С                      | N3                   | PL19B                     | 6         |                  | С            |

| GND '                                     | VCCIO3                                                                    | 3                 |                  |                      | VCCIO6                                            | VCCIO6                                               | 6            |                  |                        | VCCIO6               | VCCIO6                    | 6         |                  |              |

|                                           | GNDIO3                                                                    | 3                 |                  |                      | GND                                               | GNDIO6                                               | 6            |                  |                        | GND                  | GNDIO6                    | 6         |                  |              |

|                                           | GNDIO2                                                                    | 2                 |                  |                      | GND                                               | GNDIO5                                               | 5            |                  |                        | GND                  | GNDIO5                    | 5         |                  |              |

|                                           | VCCIO2                                                                    | 2                 |                  |                      | VCCIO5                                            | VCCIO5                                               | 5            |                  |                        | VCCIO5               | VCCIO5                    | 5         |                  |              |

| P4                                        | TMS                                                                       | 2                 | TMS              |                      | P4                                                | TMS                                                  | 5            | TMS              |                        | P4                   | TMS                       | 5         | TMS              |              |

| P2                                        | NC                                                                        |                   |                  |                      | P2                                                | PB2A                                                 | 5            |                  | Т                      | P2                   | PB2A                      | 5         |                  | Т            |

| P3                                        | NC                                                                        |                   |                  |                      | P3                                                | PB2B                                                 | 5            |                  | С                      | P3                   | PB2B                      | 5         |                  | С            |

| N5                                        | NC                                                                        |                   |                  |                      | N5                                                | PB2C                                                 | 5            |                  | Т                      | N5                   | PB2C                      | 5         |                  | Т            |

| R3                                        | TCK                                                                       | 2                 | TCK              |                      | R3                                                | TCK                                                  | 5            | TCK              |                        | R3                   | TCK                       | 5         | TCK              | <u> </u>     |

| N6                                        | NC                                                                        |                   |                  |                      | N6                                                | PB2D                                                 | 5            |                  | С                      | N6                   | PB2D                      | 5         |                  | С            |

| T2                                        | PB2A                                                                      | 2                 |                  | Т                    | T2                                                | PB3A                                                 | 5            |                  | Т                      | T2                   | PB3A                      | 5         |                  | Т            |

| T3                                        | PB2B                                                                      | 2                 |                  | С                    | Т3                                                | PB3B                                                 | 5            |                  | С                      | T3                   | PB3B                      | 5         |                  | С            |

| R4                                        | PB2C                                                                      | 2                 |                  | Т                    | R4                                                | PB3C                                                 | 5            |                  | Т                      | R4                   | PB3C                      | 5         |                  | Т            |

| R5                                        | PB2D                                                                      | 2                 |                  | С                    | R5                                                | PB3D                                                 | 5            |                  | С                      | R5                   | PB3D                      | 5         |                  | С            |

| P5                                        | PB3A                                                                      | 2                 |                  | Т                    | P5                                                | PB4A                                                 | 5            |                  | Т                      | P5                   | PB4A                      | 5         |                  | Т            |

| P6                                        | PB3B                                                                      | 2                 |                  | С                    | P6                                                | PB4B                                                 | 5            |                  | С                      | P6                   | PB4B                      | 5         |                  | С            |

| T5                                        | PB3C                                                                      | 2                 |                  | Т                    | T5                                                | PB4C                                                 | 5            |                  | Т                      | T5                   | PB4C                      | 5         |                  | Т            |

| M6                                        | TDO                                                                       | 2                 | TDO              | _                    | M6                                                | TDO                                                  | 5            | TDO              | _                      | M6                   | TDO                       | 5         | TDO              |              |

| T4                                        | PB3D                                                                      | 2                 |                  | C                    | T4                                                | PB4D                                                 | 5            |                  | C                      | T4                   | PB4D                      | 5         |                  | C            |

| R6                                        | PB4A                                                                      | 2                 |                  | Т                    | R6                                                | PB5A                                                 | 5            |                  | Т                      | R6                   | PB5A                      | 5         |                  | Т            |

|                                           | GNDIO2                                                                    | 2                 |                  |                      | GND                                               | GNDIO5                                               | 5            |                  |                        | GND                  | GNDIO5                    | 5         |                  |              |

|                                           | VCCIO2                                                                    | 2                 |                  |                      | VCCIO5                                            | VCCIO5                                               | 5            |                  |                        | VCCIO5               | VCCIO5                    | 5         |                  |              |

| T6                                        | PB4B                                                                      | 2                 | TDI              | С                    | T6                                                | PB5B                                                 | 5            | TDI              | С                      | T6                   | PB5B                      | 5<br>5    | TDI              | С            |

| N7                                        | TDI                                                                       | 2                 | וטו              | -                    | N7                                                | TDI                                                  |              | TDI              |                        | N7                   | TDI                       |           | 101              | <u> </u>     |

| T8                                        | PB4C                                                                      | 2                 |                  | Т                    | T8                                                | PB5C                                                 | 5            |                  | Т                      | T8                   | PB6A                      | 5         |                  | T            |

| T7<br>M7                                  | PB4D<br>NC                                                                | 2                 |                  | С                    | T7<br>M7                                          | PB5D<br>PB6A                                         | 5<br>5       |                  | C<br>T                 | T7<br>M7             | PB6B<br>PB7C              | 5<br>5    |                  | C<br>T       |

|                                           |                                                                           |                   |                  |                      |                                                   |                                                      | _            |                  |                        |                      |                           |           |                  |              |

| M8<br>T9 \                                | NC                                                                        | -                 |                  |                      | M8<br>T9                                          | PB6B<br>VCCAUX                                       | 5            |                  | С                      | M8<br>T9             | PB7D                      | 5         |                  | С            |

| R7                                        | VCCAUX<br>PB4E                                                            | 2                 |                  | Т                    | R7                                                | PB6C                                                 | 5            |                  | Т                      | R7                   | VCCAUX<br>PB8C            | 5         |                  | Т            |

| R8                                        | PB4F                                                                      | 2                 |                  | С                    | R8                                                | PB6D                                                 | 5            |                  | C                      | R8                   | PB8D                      | 5         |                  | C            |

| -                                         | -                                                                         |                   |                  | U                    | VCCIO5                                            | VCCIO5                                               | 5            |                  | U                      | VCCIO5               | VCCIO5                    | 5         |                  |              |

| -                                         | -                                                                         |                   |                  |                      | GND                                               | GNDIO5                                               | 5            |                  |                        | GND                  | GNDIO5                    | 5         |                  |              |

| P7                                        | PB5C                                                                      | 2                 |                  | Т                    | P7                                                | PB6E                                                 | 5            |                  | Т                      | P7                   | PB9A                      | 4         |                  | Т            |

| P8                                        | PB5D                                                                      | 2                 |                  | С                    | P8                                                | PB6F                                                 | 5            |                  | С                      | P8                   | PB9B                      | 4         |                  | С            |

| N8                                        | PB5A                                                                      | 2                 |                  | Т                    | N8                                                | PB7A                                                 | 4            |                  | T                      | N8                   | PB10E                     | 4         |                  | Т            |

| N9                                        | PB5B                                                                      | 2                 | PCLK2_1****      | С                    | N9                                                | PB7B                                                 | 4            | PCLK4_1****      | С                      | N9                   | PB10F                     | 4         | PCLK4_1****      | C            |

| P10                                       | PB7B                                                                      | 2                 | . 02142_1        | С                    | P10                                               | PB7D                                                 | 4            | I OLIVI_I        | С                      | P10                  | PB10D                     | 4         | I OLIVI_I        | C            |

| P9                                        | PB7A                                                                      | 2                 |                  | Т                    | P9                                                | PB7C                                                 | 4            |                  | T                      | P9                   | PB10C                     | 4         |                  | T            |

| M9                                        | PB6B                                                                      | 2                 | PCLK2_0****      | С                    | M9                                                | PB7F                                                 | 4            | PCLK4_0****      | С                      | M9                   | PB10B                     | 4         | PCLK4_0****      | С            |

## LA-MachXO2280 Logic Signal Connections: 324 ftBGA (Cont.)

|             |               | LAMXO2280 |               |              |

|-------------|---------------|-----------|---------------|--------------|

| Ball Number | Ball Function | Bank      | Dual Function | Differential |

| V10         | PB9B          | 4         |               | С            |

| N10         | PB9C          | 4         |               | Т            |

| R10         | PB9D          | 4         |               | С            |

| P10         | PB10F         | 4         | PCLK4_1**     | С            |

| T10         | PB10E         | 4         |               | Т            |

| U10         | PB10D         | 4         |               | С            |

| V11         | PB10C         | 4         |               | Т            |

| U11         | PB10B         | 4         | PCLK4_0**     | С            |

| VCCIO4      | VCCIO4        | 4         |               |              |

| GND         | GNDIO4        | 4         |               |              |

| T11         | PB10A         | 4         |               | T            |

| U12         | PB11A         | 4         |               | Т            |

| R11         | PB11B         | 4         |               | С            |

| GND         | GND           | -         |               |              |

| T12         | PB11C         | 4         |               | Т            |

| P11         | PB11D         | 4         |               | С            |

| V12         | PB12A         | 4         |               | Т            |

| V13         | PB12B         | 4         |               | С            |

| R12         | PB12C         | 4         |               | Т            |

| N11         | PB12D         | 4         |               | С            |

| U13         | PB12E         | 4         |               | Т            |

| VCCIO4      | VCCIO4        | 4         |               |              |

| GND         | GNDIO4        | 4         |               |              |

| V14         | PB12F         | 4         |               | С            |

| T13         | PB13A         | 4         |               | Т            |

| P12         | PB13B         | 4         |               | С            |

| R13         | PB13C         | 4         |               | Т            |

| N12         | PB13D         | 4         |               | С            |

| V15         | PB14A         | 4         |               | Т            |