Welcome to **E-XFL.COM**

**Understanding Embedded - CPLDs (Complex Programmable Logic Devices)**

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixed-function ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

| Details                         |                                                                              |

|---------------------------------|------------------------------------------------------------------------------|

| Product Status                  | Active                                                                       |

| Programmable Type               | In System Programmable                                                       |

| Delay Time tpd(1) Max           | 4.9 ns                                                                       |

| Voltage Supply - Internal       | 1.71V ~ 3.465V                                                               |

| Number of Logic Elements/Blocks | -                                                                            |

| Number of Macrocells            | 320                                                                          |

| Number of Gates                 | -                                                                            |

| Number of I/O                   | 113                                                                          |

| Operating Temperature           | -40°C ~ 125°C (TA)                                                           |

| Mounting Type                   | Surface Mount                                                                |

| Package / Case                  | 144-LQFP                                                                     |

| Supplier Device Package         | 144-TQFP (20x20)                                                             |

| Purchase URL                    | https://www.e-xfl.com/product-detail/lattice-semiconductor/lamxo640c-3tn144e |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

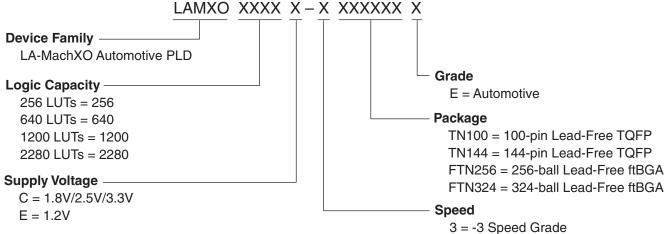

## LA-MachXO Automotive Family Data Sheet

April 2006 Data Sheet DS1003

### **Features**

## ■ Non-volatile, Infinitely Reconfigurable

- Instant-on powers up in microseconds

- Single chip, no external configuration memory required

- Excellent design security, no bit stream to intercept

- · Reconfigure SRAM based logic in milliseconds

- SRAM and non-volatile memory programmable through JTAG port

- Supports background programming of non-volatile memory

#### AEC-Q100 Tested and Qualified

## ■ Sleep Mode

Allows up to 100x static current reduction

## ■ TransFR<sup>™</sup> Reconfiguration (TFR)

· In-field logic update while system operates

## ■ High I/O to Logic Density

- 256 to 2280 LUT4s

- 73 to 271 I/Os with extensive package options

- Density migration supported

- Lead free/RoHS compliant packaging

### **■** Embedded and Distributed Memory

- Up to 27.6 Kbits sysMEM<sup>™</sup> Embedded Block RAM

- Up to 7.5 Kbits distributed RAM

- Dedicated FIFO control logic

#### **■** Flexible I/O Buffer

- Programmable sysIO<sup>™</sup> buffer supports wide range of interfaces:

- LVCMOS 3.3/2.5/1.8/1.5/1.2

- LVTTL

- PCI

- LVDS, Bus-LVDS, LVPECL, RSDS

## ■ sysCLOCK<sup>™</sup> PLLs

- · Up to two analog PLLs per device

- · Clock multiply, divide, and phase shifting

## **■** System Level Support

- IEEE Standard 1149.1 Boundary Scan

- · Onboard oscillator

- Devices operate with 3.3V, 2.5V, 1.8V or 1.2V power supply

- IEEE 1532 compliant in-system programming

#### Introduction

The LA-MachXO automotive device family is optimized to meet the requirements of applications traditionally addressed by CPLDs and low capacity FPGAs: glue logic, bus bridging, bus interfacing, power-up control, and control logic. These devices bring together the best features of CPLD and FPGA devices on a single chip in AEC-Q100 tested and qualified versions.

The devices use look-up tables (LUTs) and embedded block memories traditionally associated with FPGAs for flexible and efficient logic implementation. Through nonvolatile technology, the devices provide the single-chip,

Table 1-1. LA-MachXO Automotive Family Selection Guide

| Device                              | LAMXO256E/C      | LAMXO640E/C      | LAMXO1200E | LAMXO2280E |

|-------------------------------------|------------------|------------------|------------|------------|

| LUTs                                | 256              | 640              | 1200       | 2280       |

| Dist. RAM (Kbits)                   | 2.0              | 6.0              | 6.25       | 7.5        |

| EBR SRAM (Kbits)                    | 0                | 0                | 9.2        | 27.6       |

| Number of EBR SRAM Blocks (9 Kbits) | 0                | 0                | 1          | 3          |

| V <sub>CC</sub> Voltage             | 1.2/1.8/2.5/3.3V | 1.2/1.8/2.5/3.3V | 1.2        | 1.2        |

| Number of PLLs                      | 0                | 0                | 1          | 2          |

| Max. I/O                            | 78               | 159              | 211        | 271        |

| Packages                            |                  |                  |            |            |

| 100-pin Lead-Free TQFP (14x14 mm)   | 78               | 74               | 73         | 73         |

| 144-pin Lead-Free TQFP (20x20 mm)   |                  | 113              | 113        | 113        |

| 256-ball Lead-Free ftBGA (17x17 mm) |                  | 159              | 211        | 211        |

| 324-ball Lead-Free ftBGA (19x19 mm) |                  |                  |            | 271        |

## **Lattice Semiconductor**

high-security, instant-on capabilities traditionally associated with CPLDs. Finally, advanced process technology and careful design will provide the high pin-to-pin performance also associated with CPLDs.

The ispLEVER® design tools from Lattice allow complex designs to be efficiently implemented using the LA-MachXO automotive family of devices. Popular logic synthesis tools provide synthesis library support for LA-MachXO. The ispLEVER tools use the synthesis tool output along with the constraints from its floor planning tools to place and route the design in the LA-MachXO device. The ispLEVER tool extracts the timing from the routing and back-annotates it into the design for timing verification.

The ispLEVER design tool takes the output of the synthesis tool and places and routes the design. Generally, the place and route tool is completely automatic, although an interactive routing editor is available to optimize the design.

## **Clock/Control Distribution Network**

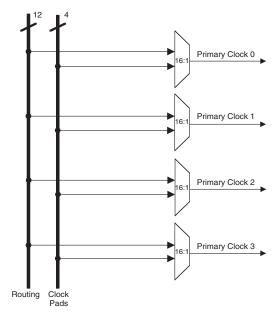

The LA-MachXO automotive family of devices provides global signals that are available to all PFUs. These signals consist of four primary clocks and four secondary clocks. Primary clock signals are generated from four 16:1 muxes as shown in Figure 2-7 and Figure 2-8. The available clock sources for the LA-MachXO256 and LA-MachXO640 devices are four dual function clock pins and 12 internal routing signals. The available clock sources for the LA-MachXO1200 and LA-MachXO2280 devices are four dual function clock pins, up to nine internal routing signals and up to six PLL outputs.

Figure 2-7. Primary Clocks for LA-MachXO256 and LA-MachXO640 Devices

## sysCLOCK Phase Locked Loops (PLLs)

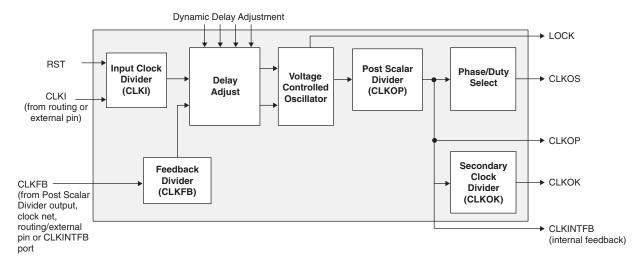

The LA-MachXO1200 and LA-MachXO2280 provide PLL support. The source of the PLL input divider can come from an external pin or from internal routing. There are four sources of feedback signals to the feedback divider: from CLKINTFB (internal feedback port), from the global clock nets, from the output of the post scalar divider, and from the routing (or from an external pin). There is a PLL\_LOCK signal to indicate that the PLL has locked on to the input clock signal. Figure 2-10 shows the sysCLOCK PLL diagram.

The setup and hold times of the device can be improved by programming a delay in the feedback or input path of the PLL which will advance or delay the output clock with reference to the input clock. This delay can be either programmed during configuration or can be adjusted dynamically. In dynamic mode, the PLL may lose lock after adjustment and not relock until the t<sub>LOCK</sub> parameter has been satisfied. Additionally, the phase and duty cycle block allows the user to adjust the phase and duty cycle of the CLKOS output.

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. Each PLL has four dividers associated with it: input clock divider, feedback divider, post scalar divider, and secondary clock divider. The input clock divider is used to divide the input clock signal, while the feedback divider is used to multiply the input clock signal. The post scalar divider allows the VCO to operate at higher frequencies than the clock output, thereby increasing the frequency range. The secondary divider is used to derive lower frequency outputs.

Figure 2-10. PLL Diagram

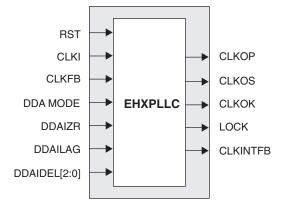

Figure 2-11 shows the available macros for the PLL. Table 2-5 provides signal description of the PLL Block.

Figure 2-11. PLL Primitive

#### **Bus Size Matching**

All of the multi-port memory modes support different widths on each of the ports. The RAM bits are mapped LSB word 0 to MSB word 0, LSB word 1 to MSB word 1 and so on. Although the word size and number of words for each port varies, this mapping scheme applies to each port.

### **RAM Initialization and ROM Operation**

If desired, the contents of the RAM can be pre-loaded during device configuration. By preloading the RAM block during the chip configuration cycle and disabling the write controls, the sysMEM block can also be utilized as a ROM.

### **Memory Cascading**

Larger and deeper blocks of RAMs can be created using EBR sysMEM Blocks. Typically, the Lattice design tools cascade memory transparently, based on specific design inputs.

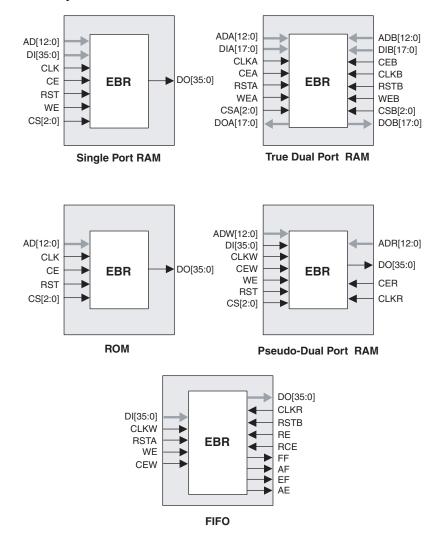

#### Single, Dual, Pseudo-Dual Port and FIFO Modes

Figure 2-12 shows the five basic memory configurations and their input/output names. In all the sysMEM RAM modes, the input data and address for the ports are registered at the input of the memory array. The output data of the memory is optionally registered at the memory array output.

Figure 2-12. sysMEM Memory Primitives

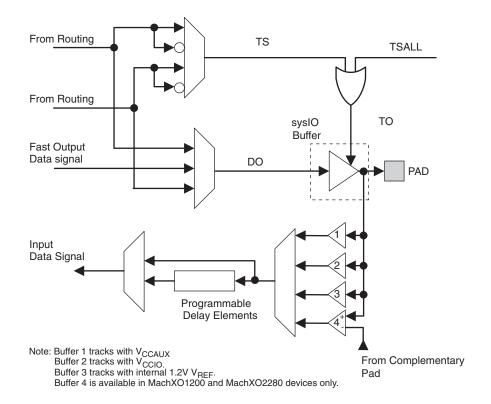

output data signals are multiplexed and provide a single signal to the I/O pin via the sysIO buffer. Figure 2-17 shows the LA-MachXO PIO logic.

The tristate control signal is multiplexed from the output data signals and their complements. In addition a global signal (TSALL) from a dedicated pad can be used to tristate the sysIO buffer.

The PIO receives an input signal from the pin via the sysIO buffer and provides this signal to the core of the device. In addition there are programmable elements that can be utilized by the design tools to avoid positive hold times.

Figure 2-17. LA-MachXO PIO Block Diagram

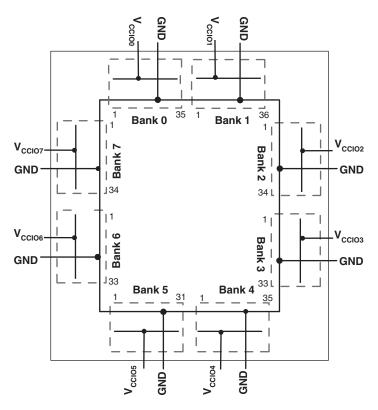

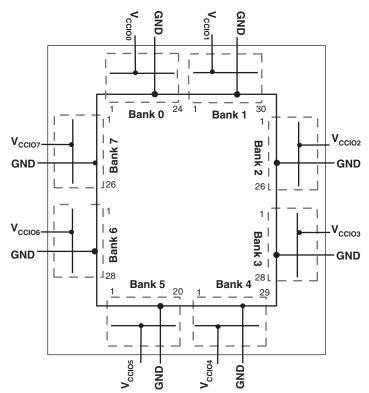

## sysIO Buffer

Each I/O is associated with a flexible buffer referred to as a sysIO buffer. These buffers are arranged around the periphery of the device in groups referred to as Banks. The sysIO buffers allow users to implement the wide variety of standards that are found in today's systems including LVCMOS, TTL, BLVDS, LVDS and LVPECL.

In the LA-MachXO devices, single-ended output buffers and ratioed input buffers (LVTTL, LVCMOS and PCI) are powered using  $V_{CCIO}$ . In addition to the Bank  $V_{CCIO}$  supplies, the LA-MachXO devices have a  $V_{CC}$  core logic power supply, and a  $V_{CCAUX}$  supply that powers up a variety of internal circuits including all the differential and referenced input buffers.

LA-MachXO256 and LA-MachXO640 devices contain single-ended input buffers and single-ended output buffers with complementary outputs on all the I/O Banks.

LA-MachXO1200 and LA-MachXO2280 devices contain two types of sysIO buffer pairs.

#### 1. Top and Bottom sysIO Buffer Pairs

The sysIO buffer pairs in the top and bottom Banks of the device consist of two single-ended output drivers and two sets of single-ended input buffers (for ratioed or absolute input levels). The I/O pairs on the top and bottom

Table 2-8. I/O Support Device by Device

|                                             | LA-MachXO256                                                          | LA-MachXO640                                                          | LA-MachXO1200                                                                  | LA-MachXO2280                                                                  |

|---------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Number of I/O Banks                         | 2                                                                     | 4                                                                     | 8                                                                              | 8                                                                              |

| Type of Input Buffers                       | Single-ended<br>(all I/O Banks)                                       | Single-ended<br>(all I/O Banks)                                       | Single-ended (all I/O Banks)  Differential Receivers                           | Single-ended<br>(all I/O Banks)<br>Differential Receivers                      |

|                                             |                                                                       |                                                                       | (all I/O Banks)                                                                | (all I/O Banks)                                                                |

| Types of Output Buffers                     | Single-ended buffers<br>with complementary<br>outputs (all I/O Banks) | Single-ended buffers<br>with complementary<br>outputs (all I/O Banks) | Single-ended buffers<br>with complementary<br>outputs (all I/O Banks)          | Single-ended buffers<br>with complementary<br>outputs (all I/O Banks)          |

|                                             |                                                                       |                                                                       | Differential buffers with<br>true LVDS outputs (50%<br>on left and right side) | Differential buffers with<br>true LVDS outputs (50%<br>on left and right side) |

| Differential Output<br>Emulation Capability | All I/O Banks                                                         | All I/O Banks                                                         | All I/O Banks                                                                  | All I/O Banks                                                                  |

| PCI Support                                 | No                                                                    | No                                                                    | Top side only                                                                  | Top side only                                                                  |

Table 2-9. Supported Input Standards

|                                                                                  | VCCIO (Typ.) |      |      |      |      |  |  |  |

|----------------------------------------------------------------------------------|--------------|------|------|------|------|--|--|--|

| Input Standard                                                                   | 3.3V         | 2.5V | 1.8V | 1.5V | 1.2V |  |  |  |

| Single Ended Interfaces                                                          |              |      |      |      |      |  |  |  |

| LVTTL                                                                            | √            | √    | √    | √    | √    |  |  |  |

| LVCMOS33                                                                         | √            | √    | √    | √    | √    |  |  |  |

| LVCMOS25                                                                         | √            | √    | √    | √    | √    |  |  |  |

| LVCMOS18                                                                         |              |      | √    |      |      |  |  |  |

| LVCMOS15                                                                         |              |      |      | √    |      |  |  |  |

| LVCMOS12                                                                         | √            | √    | √    | √    | √    |  |  |  |

| PCI <sup>1</sup>                                                                 | √            |      |      |      |      |  |  |  |

| Differential Interfaces                                                          |              |      | •    | •    |      |  |  |  |

| BLVDS <sup>2</sup> , LVDS <sup>2</sup> , LVPECL <sup>2</sup> , RSDS <sup>2</sup> | V            | V    | V    | V    | V    |  |  |  |

<sup>1.</sup> Top Banks of LA-MachXO1200 and LA-MachXO2280 devices only.

<sup>2.</sup> LA-MachXO1200 and LA-MachXO2280 devices only.

Figure 2-18. LA-MachXO2280 Banks

Figure 2-19. LA-MachXO1200 Banks

## sysIO Recommended Operating Conditions

|                      | V <sub>CCIO</sub> (V) |      |       |  |  |  |  |  |

|----------------------|-----------------------|------|-------|--|--|--|--|--|

| Standard             | Min.                  | Тур. | Max.  |  |  |  |  |  |

| LVCMOS 3.3           | 3.135                 | 3.3  | 3.465 |  |  |  |  |  |

| LVCMOS 2.5           | 2.375                 | 2.5  | 2.625 |  |  |  |  |  |

| LVCMOS 1.8           | 1.71                  | 1.8  | 1.89  |  |  |  |  |  |

| LVCMOS 1.5           | 1.425                 | 1.5  | 1.575 |  |  |  |  |  |

| LVCMOS 1.2           | 1.14                  | 1.2  | 1.26  |  |  |  |  |  |

| LVTTL                | 3.135                 | 3.3  | 3.465 |  |  |  |  |  |

| PCI <sup>3</sup>     | 3.135                 | 3.3  | 3.465 |  |  |  |  |  |

| LVDS <sup>1, 2</sup> | 2.375                 | 2.5  | 2.625 |  |  |  |  |  |

| LVPECL1              | 3.135                 | 3.3  | 3.465 |  |  |  |  |  |

| BLVDS <sup>1</sup>   | 2.375                 | 2.5  | 2.625 |  |  |  |  |  |

| RSDS <sup>1</sup>    | 2.375                 | 2.5  | 2.625 |  |  |  |  |  |

<sup>1.</sup> Inputs on chip. Outputs are implemented with the addition of external resistors.

<sup>2.</sup> MachXO1200 and MachXO2280 devices have dedicated LVDS buffers

<sup>3.</sup> Input on the top bank of the MachXO1200 and MachXO2280 only.

For further information on LVPECL, BLVDS and other differential interfaces please see details of additional technical documentation at the end of the data sheet.

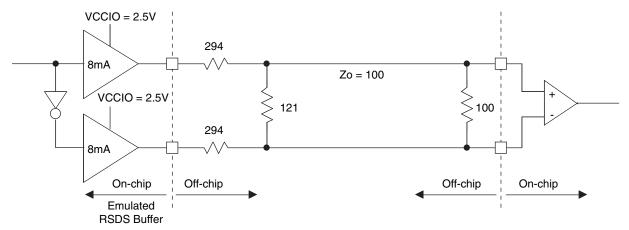

### **RSDS**

The LA-MachXO automotive family supports the differential RSDS standard. The output standard is emulated using complementary LVCMOS outputs in conjunction with a parallel resistor across the driver outputs on all the devices. The RSDS input standard is supported by the LVDS differential input buffer on certain devices. The scheme shown in Figure 3-4 is one possible solution for RSDS standard implementation. Use LVDS25E mode with suggested resistors for RSDS operation. Resistor values in Figure 3-4 are industry standard values for 1% resistors.

Figure 3-4. RSDS (Reduced Swing Differential Standard)

Table 3-4. RSDS DC Conditions

| Parameter         | Description                 | Typical | Units |

|-------------------|-----------------------------|---------|-------|

| Z <sub>OUT</sub>  | Output impedance            | 20      | ohm   |

| R <sub>S</sub>    | Driver series resistor      | 294     | ohm   |

| R <sub>P</sub>    | Driver parallel resistor    | 121     | ohm   |

| R <sub>T</sub>    | Receiver termination        | 100     | ohm   |

| V <sub>OH</sub>   | Output high voltage         | 1.35    | V     |

| V <sub>OL</sub>   | Output low voltage          | 1.15    | V     |

| V <sub>OD</sub>   | Output differential voltage | 0.20    | V     |

| V <sub>CM</sub>   | Output common mode voltage  | 1.25    | V     |

| Z <sub>BACK</sub> | Back impedance              | 101.5   | ohm   |

| I <sub>DC</sub>   | DC output current           | 3.66    | mA    |

# Lattice LA-MachXO Automotive Family Data Sheet

November 2007 **Data Sheet DS1003**

## **Signal Descriptions**

| Signal Name                                    | I/O    | Descriptions                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Purpose                                |        |                                                                                                                                                                                                                                                                                                                                                      |

|                                                |        | [Edge] indicates the edge of the device on which the pad is located. Valid edge designations are L (Left), B (Bottom), R (Right), T (Top).                                                                                                                                                                                                           |

|                                                |        | [Row/Column Number] indicates the PFU row or the column of the device on which the PIO Group exists. When Edge is T (Top) or (Bottom), only need to specify Row Number. When Edge is L (Left) or R (Right), only need to specify Column Number.                                                                                                      |

| P[Edge] [Row/Column<br>  Number] [A/B/C/D/E/F] | I/O    | [A/B/C/D/E/F] indicates the PIO within the group to which the pad is connected.                                                                                                                                                                                                                                                                      |

| , , , , , , , , , , , , , , , , , , ,          |        | Some of these user programmable pins are shared with special function pins. When not used as special function pins, these pins can be programmed as I/Os for user logic.                                                                                                                                                                             |

|                                                |        | During configuration of the user-programmable I/Os, the user has an option to tri-state the I/Os and enable an internal pull-up resistor. This option also applies to unused pins (or those not bonded to a package pin). The default during configuration is for user-programmable I/Os to be tri-stated with an internal pull-up resistor enabled. |

| GSRN                                           | I      | Global RESET signal (active low). Dedicated pad, when not in use it can be used as an I/O pin.                                                                                                                                                                                                                                                       |

| TSALL                                          | I      | TSALL is a dedicated pad for the global output enable signal. When TSALL is high all the outputs are tristated. It is a dual function pin. When not in use, it can be used as an I/O pin.                                                                                                                                                            |

| NC                                             | _      | No connect.                                                                                                                                                                                                                                                                                                                                          |

| GND                                            | _      | GND - Ground. Dedicated pins.                                                                                                                                                                                                                                                                                                                        |

| V <sub>CC</sub>                                | _      | VCC - The power supply pins for core logic. Dedicated pins.                                                                                                                                                                                                                                                                                          |

| V <sub>CCAUX</sub>                             | _      | VCCAUX - the Auxiliary power supply pin. This pin powers up a variety of internal circuits including all the differential and referenced input buffers. Dedicated pins.                                                                                                                                                                              |

| V <sub>CCIOx</sub>                             | _      | V <sub>CCIO</sub> - The power supply pins for I/O Bank x. Dedicated pins.                                                                                                                                                                                                                                                                            |

| SLEEPN <sup>1</sup>                            | I      | Sleep Mode pin - Active low sleep pin. When this pin is held high, the device operates normally. This pin has a weak internal pull-up, but when unused, an external pull-up to $V_{CC}$ is recommended. When driven low, the device moves into Sleep mode after a specified time.                                                                    |

| PLL and Clock Functions (                      | Used   | as user programmable I/O pins when not used for PLL or clock pins)                                                                                                                                                                                                                                                                                   |

| [LOC][0]_PLL[T, C]_IN                          | _      | Reference clock (PLL) input Pads: [LOC] indicates location. Valid designations are ULM (Upper PLL) and LLM (Lower PLL). T = true and C = complement.                                                                                                                                                                                                 |

| [LOC][0]_PLL[T, C]_FB                          | _      | Optional feedback (PLL) input Pads: [LOC] indicates location. Valid designations are ULM (Upper PLL) and LLM (Lower PLL). T = true and C = complement.                                                                                                                                                                                               |

| PCLK [n]_[1:0]                                 | _      | Primary Clock Pads, n per side.                                                                                                                                                                                                                                                                                                                      |

| Test and Programming (De                       | dicate | d pins)                                                                                                                                                                                                                                                                                                                                              |

| TMS                                            | I      | Test Mode Select input pin, used to control the 1149.1 state machine.                                                                                                                                                                                                                                                                                |

| TCK                                            | I      | Test Clock input pin, used to clock the 1149.1 state machine.                                                                                                                                                                                                                                                                                        |

| TDI                                            | I      | Test Data input pin, used to load data into the device using an 1149.1 state machine.                                                                                                                                                                                                                                                                |

| TDO                                            | 0      | Output pin -Test Data output pin used to shift data out of the device using 1149.1.                                                                                                                                                                                                                                                                  |

| ·                                              |        | ·                                                                                                                                                                                                                                                                                                                                                    |

<sup>1.</sup> Applies to LA-MachXO "C" devices only. NC for "E" devices.

www.latticesemi.com DS1003 Pinouts\_01.3 4-1

## Power Supply and NC (Cont.)

| Signal           | 256 ftBGA <sup>1</sup>                                                                                                                                                                                                                                                             | 324 ftBGA <sup>1</sup>                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| VCC              | G7, G10, K7, K10                                                                                                                                                                                                                                                                   | F14, G11, G9, H7, L7, M9                                                                                   |

| VCCIO0           | <b>LAMXO640</b> : F8, F7, F9, F10<br><b>LAMXO1200/2280</b> : F8, F7                                                                                                                                                                                                                | G8, G7                                                                                                     |

| VCCIO1           | <b>LAMXO640</b> : H11, G11, K11, J11<br><b>LAMXO1200/2280</b> : F9, F10                                                                                                                                                                                                            | G12, G10                                                                                                   |

| VCCIO2           | LAMXO640: L9, L10, L8, L7<br>LAMXO1200/2280: H11, G11                                                                                                                                                                                                                              | J12, H12                                                                                                   |

| VCCIO3           | <b>LAMXO640</b> : K6, J6, H6, G6<br><b>LAMXO1200/2280</b> : K11, J11                                                                                                                                                                                                               | L12, K12                                                                                                   |

| VCCIO4           | <b>LAMXO640</b> : None <b>LAMXO1200/2280</b> : L9, L10                                                                                                                                                                                                                             | M12, M11                                                                                                   |

| VCCIO5           | <b>LAMXO640</b> : None <b>LAMXO1200/2280</b> : L8, L7                                                                                                                                                                                                                              | M8, R9                                                                                                     |

| VCCIO6           | <b>LAMXO640</b> : None <b>LAMXO1200/2280</b> : K6, J6                                                                                                                                                                                                                              | M7, K7                                                                                                     |

| VCCIO7           | <b>LAMXO640</b> : None <b>LAMXO1200/2280</b> : H6, G6                                                                                                                                                                                                                              | H6, J7                                                                                                     |

| VCCAUX           | T9, A8                                                                                                                                                                                                                                                                             | M10, F9                                                                                                    |

| GND <sup>2</sup> | A1, A16, F11, G8, G9, H7, H8, H9, H10, J7, J8, J9, J10, K8, K9, L6, T1, T16                                                                                                                                                                                                        | E14, F16, H10, H11, H8, H9, J10, J11, J4, J8, J9, K10, K11, K17, K8, K9, L10, L11, L8, L9, N2, P14, P5, R7 |

| NC <sup>3</sup>  | LAMXO640: E4, E5, F5, F6, C3, C2, G4, G5, H4, H5, K5, K4, M5, M4, P2, P3, N5, N6, M7, M8, N10, N11, R15, R16, P15, P16, M11, L11, N12, N13, M13, M12, K12, J12, F12, F13, E12, E13, D13, D14, B15, A15, C14, B14, E11, E10, E7, E6, D4, D3, B3, B2 LAMXO1200: None LAMXO2280: None | _                                                                                                          |

Pin orientation A1 starts from the upper left corner of the top side view with alphabetical order ascending vertically and numerical order ascending horizontally.

All grounds must be electrically connected at the board level. For fpBGA and ftBGA packages, the total number of GND balls is less than the actual number of GND logic connections from the die to the common package GND plane.

NC pins should not be connected to any active signals, VCC or GND.

## LA-MachXO256 and LA-MachXO640 Logic Signal Connections: 100 TQFP (Cont.)

|            | (301111) |      | (O256    |              | LAMXO640 |      |          |              |  |  |

|------------|----------|------|----------|--------------|----------|------|----------|--------------|--|--|

|            | Ball     |      | Dual     |              | Ball     |      | Dual     |              |  |  |

| Pin Number | Function | Bank | Function | Differential | Function | Bank | Function | Differential |  |  |

| 42         | GNDIO1   | 1    |          |              | GNDIO2   | 2    |          |              |  |  |

| 43         | PB4A     | 1    |          | Т            | PB8B     | 2    |          |              |  |  |

| 44         | PB4B     | 1    |          | С            | PB8C     | 2    |          | Т            |  |  |

| 45         | PB4C     | 1    |          | Т            | PB8D     | 2    |          | С            |  |  |

| 46         | PB4D     | 1    |          | С            | PB9A     | 2    |          |              |  |  |

| 47         | PB5A     | 1    |          |              | PB9C     | 2    |          | Т            |  |  |

| 48*        | SLEEPN   | -    | SLEEPN   |              | SLEEPN   | -    | SLEEPN   |              |  |  |

| 49         | PB5C     | 1    |          | Т            | PB9D     | 2    |          | С            |  |  |

| 50         | PB5D     | 1    |          | С            | PB9F     | 2    |          |              |  |  |

| 51         | PR9B     | 0    |          | С            | PR11D    | 1    |          | С            |  |  |

| 52         | PR9A     | 0    |          | Т            | PR11B    | 1    |          | С            |  |  |

| 53         | PR8B     | 0    |          | С            | PR11C    | 1    |          | Т            |  |  |

| 54         | PR8A     | 0    |          | Т            | PR11A    | 1    |          | Т            |  |  |

| 55         | PR7D     | 0    |          | С            | PR10D    | 1    |          | С            |  |  |

| 56         | PR7C     | 0    |          | Т            | PR10C    | 1    |          | Т            |  |  |

| 57         | PR7B     | 0    |          | С            | PR10B    | 1    |          | С            |  |  |

| 58         | PR7A     | 0    |          | Т            | PR10A    | 1    |          | Т            |  |  |

| 59         | PR6B     | 0    |          | С            | PR9D     | 1    |          |              |  |  |

| 60         | VCCIO0   | 0    |          |              | VCCIO1   | 1    |          |              |  |  |

| 61         | PR6A     | 0    |          | Т            | PR9B     | 1    |          |              |  |  |

| 62         | GNDIO0   | 0    |          |              | GNDIO1   | 1    |          |              |  |  |

| 63         | PR5D     | 0    |          | С            | PR7B     | 1    |          |              |  |  |

| 64         | PR5C     | 0    |          | Т            | PR6C     | 1    |          |              |  |  |

| 65         | PR5B     | 0    |          | С            | PR6B     | 1    |          |              |  |  |

| 66         | PR5A     | 0    |          | Т            | PR5D     | 1    |          |              |  |  |

| 67         | PR4B     | 0    |          | С            | PR5B     | 1    |          |              |  |  |

| 68         | PR4A     | 0    |          | Т            | PR4D     | 1    |          |              |  |  |

| 69         | PR3D     | 0    |          | С            | PR4B     | 1    |          |              |  |  |

| 70         | PR3C     | 0    |          | Т            | PR3D     | 1    |          |              |  |  |

| 71         | PR3B     | 0    |          | С            | PR3B     | 1    |          |              |  |  |

| 72         | PR3A     | 0    |          | Т            | PR2D     | 1    |          |              |  |  |

| 73         | PR2B     | 0    |          | С            | PR2B     | 1    |          |              |  |  |

| 74         | VCCIO0   | 0    |          |              | VCCIO1   | 1    |          |              |  |  |

| 75         | GNDIO0   | 0    |          |              | GNDIO1   | 1    |          |              |  |  |

| 76         | PR2A     | 0    |          | Т            | PT9F     | 0    |          | С            |  |  |

| 77         | PT5C     | 0    |          |              | PT9E     | 0    |          | Т            |  |  |

| 78         | PT5B     | 0    |          | С            | PT9C     | 0    |          |              |  |  |

| 79         | PT5A     | 0    |          | Т            | PT9A     | 0    |          |              |  |  |

| 80         | PT4F     | 0    |          | С            | VCCIO0   | 0    |          |              |  |  |

| 81         | PT4E     | 0    |          | Т            | GNDIO0   | 0    |          |              |  |  |

| 82         | PT4D     | 0    |          | С            | PT7E     | 0    |          |              |  |  |

## LA-MachXO1200 and LA-MachXO2280 Logic Signal Connections: 100 TQFP (Cont.)

|               |                  | L    | AMXO1200         |              | LAMXO2280        |      |                  |              |  |

|---------------|------------------|------|------------------|--------------|------------------|------|------------------|--------------|--|

| Pin<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Function | Bank | Dual<br>Function | Differential |  |

| 41            | GND              | -    |                  |              | GND              | -    |                  |              |  |

| 42            | PB9A             | 4    |                  | Т            | PB12A            | 4    |                  | Т            |  |

| 43            | PB9B             | 4    |                  | С            | PB12B            | 4    |                  | С            |  |

| 44            | VCCIO4           | 4    |                  |              | VCCIO4           | 4    |                  |              |  |

| 45            | PB10A            | 4    |                  | Т            | PB13A            | 4    |                  | Т            |  |

| 46            | PB10B            | 4    |                  | С            | PB13B            | 4    |                  | С            |  |

| 47            | NC               | -    | NC               |              | NC               | -    | NC               |              |  |

| 48            | PB11A            | 4    |                  | Т            | PB16A            | 4    |                  | Т            |  |

| 49            | PB11B            | 4    |                  | С            | PB16B            | 4    |                  | С            |  |

| 50**          | GNDIO3<br>GNDIO4 | -    |                  |              | GNDIO3<br>GNDIO4 | -    |                  |              |  |

| 51            | PR16B            | 3    |                  |              | PR19B            | 3    |                  |              |  |

| 52            | PR15B            | 3    |                  | C*           | PR18B            | 3    |                  | C*           |  |

| 53            | PR15A            | 3    |                  | T*           | PR18A            | 3    |                  | T*           |  |

| 54            | PR14B            | 3    |                  | C*           | PR17B            | 3    |                  | C*           |  |

| 55            | PR14A            | 3    |                  | T*           | PR17A            | 3    |                  | T*           |  |

| 56            | VCCIO3           | 3    |                  |              | VCCIO3           | 3    |                  |              |  |

| 57            | PR12B            | 3    |                  | C*           | PR15B            | 3    |                  | C*           |  |

| 58            | PR12A            | 3    |                  | T*           | PR15A            | 3    |                  | T*           |  |

| 59            | GND              | -    |                  |              | GND              | -    |                  |              |  |

| 60            | PR10B            | 3    |                  | C*           | PR13B            | 3    |                  | C*           |  |

| 61            | PR10A            | 3    |                  | T*           | PR13A            | 3    |                  | T*           |  |

| 62            | PR9B             | 3    |                  | C*           | PR11B            | 3    |                  | C*           |  |

| 63            | PR9A             | 3    |                  | T*           | PR11A            | 3    |                  | T*           |  |

| 64            | PR8B             | 2    |                  | C*           | PR10B            | 2    |                  | C*           |  |

| 65            | PR8A             | 2    |                  | T*           | PR10A            | 2    |                  | T*           |  |

| 66            | VCC              | -    |                  |              | VCC              | -    |                  |              |  |

| 67            | PR6C             | 2    |                  |              | PR8C             | 2    |                  |              |  |

| 68            | PR6B             | 2    |                  | C*           | PR8B             | 2    |                  | C*           |  |

| 69            | PR6A             | 2    |                  | T*           | PR8A             | 2    |                  | T*           |  |

| 70            | VCCIO2           | 2    |                  |              | VCCIO2           | 2    |                  |              |  |

| 71            | PR4D             | 2    |                  |              | PR5D             | 2    |                  |              |  |

| 72            | PR4B             | 2    |                  | C*           | PR5B             | 2    |                  | C*           |  |

| 73            | PR4A             | 2    |                  | T*           | PR5A             | 2    |                  | T*           |  |

| 74            | PR2B             | 2    |                  | С            | PR3B             | 2    |                  | C*           |  |

| 75            | PR2A             | 2    |                  | Т            | PR3A             | 2    |                  | T*           |  |

| 76**          | GNDIO1<br>GNDIO2 | -    |                  |              | GNDIO1<br>GNDIO2 | -    |                  |              |  |

| 77            | PT11C            | 1    |                  |              | PT15C            | 1    |                  |              |  |

| 78            | PT11B            | 1    |                  | С            | PT14B            | 1    |                  | С            |  |

| 79            | PT11A            | 1    |                  | Т            | PT14A            | 1    |                  | Т            |  |

## LA-MachXO640, LA-MachXO1200 and LA-MachXO2280 Logic Signal Connections: 144 TQFP (Cont.)

|               |                  | L    | AMXO640          |              |                  |      | LAMXO1200        |              |                  |      | LAMXO2280        |              |

|---------------|------------------|------|------------------|--------------|------------------|------|------------------|--------------|------------------|------|------------------|--------------|

| Pin<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Function | Bank | Dual<br>Function | Differential |

| 51            | TDI              | 2    | TDI              |              | TDI              | 5    | TDI              |              | TDI              | 5    | TDI              |              |

| 52            | VCC              | -    |                  |              | VCC              | -    |                  |              | VCC              | -    |                  |              |

| 53            | VCCAUX           | -    |                  |              | VCCAUX           | -    |                  |              | VCCAUX           | -    |                  |              |

| 54            | PB5A             | 2    |                  | Т            | PB6F             | 5    |                  |              | PB8F             | 5    |                  |              |

| 55            | PB5B             | 2    | PCLKT2_1***      | С            | PB7B             | 4    | PCLK4_1***       |              | PB10F            | 4    | PCLK4_1***       |              |

| 56            | PB5D             | 2    |                  |              | PB7C             | 4    |                  | Т            | PB10C            | 4    |                  | Т            |

| 57            | PB6A             | 2    |                  | Т            | PB7D             | 4    |                  | С            | PB10D            | 4    |                  | C            |

| 58            | PB6B             | 2    | PCLKT2_0***      | C            | PB7F             | 4    | PCLK4 0***       |              | PB10B            | 4    | PCLK4_0***       |              |

| 59            | GND              | -    | T OLIVIZ_0       |              | GND              | -    | T OLKT_O         |              | GND              | -    | 1 021(1_0        |              |

| 60            | PB7C             | 2    |                  |              | PB9A             | 4    |                  | Т            | PB12A            | 4    |                  | Т            |

| 61            | PB7E             | 2    |                  |              | PB9B             | 4    |                  | C            | PB12B            | 4    |                  | C            |

|               | PB8A             | 2    |                  |              | PB9E             |      |                  |              | PB12E            |      |                  |              |

| 62            |                  | -    |                  |              |                  | 4    |                  |              |                  | 4    |                  |              |

| 63            | VCCIO2           | 2    |                  |              | VCCIO4           | 4    |                  |              | VCCIO4           | 4    |                  |              |

| 64            | GNDIO2           | 2    |                  | _            | GNDIO4           | 4    |                  |              | GNDIO4           | 4    |                  |              |

| 65            | PB8C             | 2    |                  | Т            | PB10A            | 4    |                  | T            | PB13A            | 4    |                  | T            |

| 66            | PB8D             | 2    |                  | С            | PB10B            | 4    |                  | С            | PB13B            | 4    |                  | С            |

| 67            | PB9A             | 2    |                  | Т            | PB10C            | 4    |                  | Т            | PB13C            | 4    |                  | T            |

| 68            | PB9C             | 2    |                  | Т            | PB10D            | 4    |                  | С            | PB13D            | 4    |                  | С            |

| 69            | PB9B             | 2    |                  | С            | PB10F            | 4    |                  |              | PB14D            | 4    |                  |              |

| 70**          | SLEEPN           | -    | SLEEPN           |              | NC               | -    |                  |              | NC               | -    |                  |              |

| 71            | PB9D             | 2    |                  | С            | PB11C            | 4    |                  | Т            | PB16C            | 4    |                  | Т            |

| 72            | PB9F             | 2    |                  |              | PB11D            | 4    |                  | С            | PB16D            | 4    |                  | С            |

| 73            | PR11D            | 1    |                  | С            | PR16B            | 3    |                  | С            | PR20B            | 3    |                  | С            |

| 74            | PR11B            | 1    |                  | С            | PR16A            | 3    |                  | Т            | PR20A            | 3    |                  | Т            |

| 75            | PR11C            | 1    |                  | Т            | PR15B            | 3    |                  | C*           | PR19B            | 3    |                  | С            |

| 76            | PR10D            | 1    |                  | С            | PR15A            | 3    |                  | T*           | PR19A            | 3    |                  | Т            |

| 77            | PR11A            | 1    |                  | Т            | PR14D            | 3    |                  | С            | PR17D            | 3    |                  | С            |

| 78            | PR10B            | 1    |                  | С            | PR14C            | 3    |                  | Т            | PR17C            | 3    |                  | Т            |

| 79            | PR10C            | 1    |                  | Т            | PR14B            | 3    |                  | C*           | PR17B            | 3    |                  | C*           |

| 80            | PR10A            | 1    |                  | Т            | PR14A            | 3    |                  | T*           | PR17A            | 3    |                  | T*           |

| 81            | PR9D             | 1    |                  |              | PR13D            | 3    |                  | ·            | PR16D            | 3    |                  | -            |

| 82            | VCCIO1           | 1    |                  |              | VCCIO3           | 3    |                  |              | VCCIO3           | 3    |                  |              |

| 83            | GNDIO1           | 1    |                  |              | GNDIO3           | 3    |                  |              | GNDIO3           | 3    |                  |              |

| 84            | PR9A             | 1    |                  |              | PR12B            | 3    |                  | C*           | PR15B            | 3    |                  | C*           |

| 85            | PR8C             | 1    |                  |              | PR12A            | 3    |                  | T*           | PR15A            | 3    |                  | T*           |

| 86            | PR8A             | 1    |                  |              |                  | 3    |                  | C*           | PR14B            | 3    |                  | C*           |

|               |                  |      |                  |              | PR11B            |      |                  | T*           |                  |      |                  | T*           |

| 87            | PR7D             | 1    |                  |              | PR11A            | 3    |                  | l"           | PR14A            | 3    |                  | 1 "          |

| 88            | GND              | -    |                  |              | GND              | -    |                  | -            | GND              | -    |                  | -            |

| 89            | PR7B             | 1    |                  | C            | PR10B            | 3    |                  | C*           | PR13B            | 3    |                  | C*           |

| 90            | PR7A             | 1    |                  | Т            | PR10A            | 3    |                  | T*           | PR13A            | 3    |                  | T*           |

| 91            | PR6D             | 1    |                  | С            | PR8B             | 2    |                  | C*           | PR10B            | 2    |                  | C*           |

| 92            | PR6C             | 1    |                  | Т            | PR8A             | 2    |                  | T*           | PR10A            | 2    |                  | T*           |

| 93            | VCC              | -    |                  |              | VCC              | -    |                  |              | VCC              | -    |                  |              |

| 94            | PR5D             | 1    |                  |              | PR6B             | 2    |                  | C*           | PR8B             | 2    |                  | C*           |

| 95            | PR5B             | 1    |                  |              | PR6A             | 2    |                  | T*           | PR8A             | 2    |                  | T*           |

| 96            | PR4D             | 1    |                  |              | PR5B             | 2    |                  | C*           | PR7B             | 2    |                  | C*           |

| 97            | PR4B             | 1    |                  | С            | PR5A             | 2    |                  | T*           | PR7A             | 2    |                  | T*           |

| 98            | VCCIO1           | 1    |                  |              | VCCIO2           | 2    |                  |              | VCCIO2           | 2    |                  |              |

| 99            | GNDIO1           | 1    |                  |              | GNDIO2           | 2    |                  |              | GNDIO2           | 2    |                  |              |

| 100           | PR4A             | 1    |                  | Т            | PR4C             | 2    |                  |              | PR5C             | 2    |                  |              |

## LA-MachXO640, LA-MachXO1200 and LA-MachXO2280 Logic Signal Connections: 256 ftBGA

|                | LAMXO640         |      |                  | LAMXO1200    |                |                  |      |                  |              | LAMXO2280      |                  |      |                  |              |

|----------------|------------------|------|------------------|--------------|----------------|------------------|------|------------------|--------------|----------------|------------------|------|------------------|--------------|

| Ball<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential |

| GND            | GNDIO3           | 3    |                  |              | GND            | GNDIO7           | 7    |                  |              | GND            | GNDIO7           | 7    |                  |              |

| VCCIO3         | VCCIO3           | 3    |                  |              | VCCIO7         | VCCIO7           | 7    |                  |              | VCCIO7         | VCCIO7           | 7    |                  |              |

| E4             | NC               |      |                  |              | E4             | PL2A             | 7    |                  | Т            | E4             | PL2A             | 7    | LUM0_PLLT_FB_A   | Т            |

| E5             | NC               |      |                  |              | E5             | PL2B             | 7    |                  | С            | E5             | PL2B             | 7    | LUM0_PLLC_FB_A   | С            |

| F5             | NC               |      |                  |              | F5             | PL3A             | 7    |                  | T**          | F5             | PL3A             | 7    |                  | T**          |

| F6             | NC               |      |                  |              | F6             | PL3B             | 7    |                  | C**          | F6             | PL3B             | 7    |                  | C**          |

| F3             | PL3A             | 3    |                  | Т            | F3             | PL3C             | 7    |                  | Т            | F3             | PL3C             | 7    | LUM0_PLLT_IN_A   | Т            |

| F4             | PL3B             | 3    |                  | С            | F4             | PL3D             | 7    |                  | С            | F4             | PL3D             | 7    | LUM0_PLLC_IN_A   | С            |

| E3             | PL2C             | 3    |                  | Т            | E3             | PL4A             | 7    |                  | T**          | E3             | PL4A             | 7    |                  | T**          |

| E2             | PL2D             | 3    |                  | С            | E2             | PL4B             | 7    |                  | C**          | E2             | PL4B             | 7    |                  | C**          |

| C3             | NC               |      |                  |              | C3             | PL4C             | 7    |                  | Т            | C3             | PL4C             | 7    |                  | Т            |

| C2             | NC               |      |                  |              | C2             | PL4D             | 7    |                  | С            | C2             | PL4D             | 7    |                  | С            |

| B1             | PL2A             | 3    |                  | Т            | B1             | PL5A             | 7    |                  | T**          | B1             | PL5A             | 7    |                  | T**          |

| C1             | PL2B             | 3    |                  | С            | C1             | PL5B             | 7    |                  | C**          | C1             | PL5B             | 7    |                  | C**          |

| VCCIO3         | VCCIO3           | 3    |                  |              | VCCIO7         | VCCIO7           | 7    |                  |              | VCCIO7         | VCCIO7           | 7    |                  |              |

| GND            | GNDIO3           | 3    |                  |              | GND            | GNDIO7           | 7    |                  |              | GND            | GNDIO7           | 7    |                  |              |

| D2             | PL3C             | 3    |                  | Т            | D2             | PL5C             | 7    |                  | Т            | D2             | PL6C             | 7    |                  | Т            |

| D1             | PL3D             | 3    |                  | С            | D1             | PL5D             | 7    |                  | С            | D1             | PL6D             | 7    |                  | С            |

| F2             | PL5A             | 3    |                  | Т            | F2             | PL6A             | 7    |                  | T**          | F2             | PL7A             | 7    |                  | T**          |

| G2             | PL5B             | 3    | GSRN             | С            | G2             | PL6B             | 7    | GSRN             | C**          | G2             | PL7B             | 7    | GSRN             | C**          |

| E1             | PL4A             | 3    |                  | Т            | E1             | PL6C             | 7    |                  | Т            | E1             | PL7C             | 7    |                  | Т            |

| F1             | PL4B             | 3    |                  | С            | F1             | PL6D             | 7    |                  | С            | F1             | PL7D             | 7    |                  | С            |

| G4             | NC               |      |                  |              | G4             | PL7A             | 7    |                  | T**          | G4             | PL8A             | 7    |                  | T**          |

| G5             | NC               |      |                  |              | G5             | PL7B             | 7    |                  | C**          | G5             | PL8B             | 7    |                  | C**          |

| GND            | GND              | -    |                  |              | GND            | GND              | -    |                  |              | GND            | GND              | -    |                  |              |

| G3             | PL4C             | 3    |                  | Т            | G3             | PL7C             | 7    |                  | Т            | G3             | PL8C             | 7    |                  | T            |

| Н3             | PL4D             | 3    |                  | С            | Н3             | PL7D             | 7    |                  | С            | НЗ             | PL8D             | 7    |                  | С            |

| H4             | NC               |      |                  |              | H4             | PL8A             | 7    |                  | T**          | H4             | PL9A             | 7    |                  | T**          |

| H5             | NC               |      |                  |              | H5             | PL8B             | 7    |                  | C**          | H5             | PL9B             | 7    |                  | C**          |

| -              | -                |      |                  |              | VCCIO7         | VCCIO7           | 7    |                  |              | VCCIO7         | VCCIO7           | 7    |                  |              |

| -              | -                |      |                  |              | GND            | GNDI07           | 7    |                  |              | GND            | GNDIO7           | 7    |                  |              |

| G1             | PL5C             | 3    |                  | Т            | G1             | PL8C             | 7    |                  | Т            | G1             | PL10C            | 7    |                  | Т            |

| H1             | PL5D             | 3    |                  | С            | H1             | PL8D             | 7    |                  | С            | H1             | PL10D            | 7    |                  | С            |

| H2             | PL6A             | 3    |                  | Т            | H2             | PL9A             | 6    |                  | T**          | H2             | PL11A            | 6    |                  | T**          |

| J2             | PL6B             | 3    |                  | С            | J2             | PL9B             | 6    |                  | C**          | J2             | PL11B            | 6    |                  | C**          |

| J3             | PL7C             | 3    |                  | Т            | J3             | PL9C             | 6    |                  | Т            | J3             | PL11C            | 6    |                  | Т            |

| K3             | PL7D             | 3    |                  | С            | K3             | PL9D             | 6    |                  | С            | K3             | PL11D            | 6    |                  | С            |

| J1             | PL6C             | 3    |                  | Т            | J1             | PL10A            | 6    |                  | T**          | J1             | PL12A            | 6    |                  | T**          |

| -              | 1                |      |                  |              | VCCIO6         | VCCIO6           | 6    |                  |              | VCCIO6         | VCCIO6           | 6    |                  |              |

| -              | -                |      |                  |              | GND            | GNDIO6           | 6    |                  |              | GND            | GNDIO6           | 6    |                  |              |

| K1             | PL6D             | 3    |                  | С            | K1             | PL10B            | 6    |                  | C**          | K1             | PL12B            | 6    |                  | C**          |

| K2             | PL9A             | 3    |                  | Т            | K2             | PL10C            | 6    |                  | Т            | K2             | PL12C            | 6    |                  | Т            |

| L2             | PL9B             | 3    |                  | С            | L2             | PL10D            | 6    |                  | С            | L2             | PL12D            | 6    |                  | С            |

| L1             | PL7A             | 3    |                  | Т            | L1             | PL11A            | 6    |                  | T**          | L1             | PL13A            | 6    |                  | T**          |

| M1             | PL7B             | 3    |                  | С            | M1             | PL11B            | 6    |                  | C**          | M1             | PL13B            | 6    |                  | C**          |

| P1             | PL8D             | 3    |                  | С            | P1             | PL11D            | 6    |                  | С            | P1             | PL14D            | 6    |                  | С            |

| N1             | PL8C             | 3    | TSALL            | Т            | N1             | PL11C            | 6    | TSALL            | Т            | N1             | PL14C            | 6    | TSALL            | T            |

| L3             | PL10A            | 3    |                  | Т            | L3             | PL12A            | 6    |                  | T**          | L3             | PL15A            | 6    |                  | T**          |

| МЗ             | PL10B            | 3    |                  | С            | МЗ             | PL12B            | 6    |                  | C**          | МЗ             | PL15B            | 6    |                  | C**          |

| M2             | PL9C             | 3    |                  | Т            | M2             | PL12C            | 6    |                  | Т            | M2             | PL15C            | 6    |                  | Т            |

| N2             | PL9D             | 3    |                  | С            | N2             | PL12D            | 6    |                  | С            | N2             | PL15D            | 6    |                  | С            |

| VCCIO3         | VCCIO3           | 3    |                  |              | VCCIO6         | VCCIO6           | 6    |                  |              | VCCIO6         | VCCIO6           | 6    |                  |              |

| GND            | GNDIO3           | 3    |                  |              | GND            | GNDIO6           | 6    |                  |              | GND            | GNDIO6           | 6    |                  |              |

## LA-MachXO640, LA-MachXO1200 and LA-MachXO2280 Logic Signal Connections: 256 ftBGA (Cont.)

| LAMXO640       |                  |      | LAMXO1200        |              |                |                  |      | LAMXO2280        |              |                |                  |      |                  |              |

|----------------|------------------|------|------------------|--------------|----------------|------------------|------|------------------|--------------|----------------|------------------|------|------------------|--------------|

| Ball<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Number | Ball<br>Function | Bank | Dual<br>Function | Differential |

| J13            | PR8C             | 1    | 1 dilotion       | Т            | J13            | PR11A            | 3    | - unotion        | T**          | J13            | PR14A            | 3    | T dilotion       | T**          |

| GND            | GND              | -    |                  |              | GND            | GND              | -    |                  |              | GND            | GND              | -    |                  | <u> </u>     |

| K14            | PR8B             | 1    |                  | С            | K14            | PR10D            | 3    |                  | С            | K14            | PR13D            | 3    |                  | С            |

| J14            | PR8A             | 1    |                  | T            | J14            | PR10C            | 3    |                  | T            | J14            | PR13C            | 3    |                  | Т            |

| K15            | PR7D             | 1    |                  | С            | K15            | PR10B            | 3    |                  | C**          | K15            | PR13B            | 3    |                  | C**          |

| J15            | PR7C             | 1    |                  | T            | J15            | PR10A            | 3    |                  | T**          | J15            | PR13A            | 3    |                  | T**          |

| -              | -                | · ·  |                  |              | GND            | GNDIO3           | 3    |                  | 1            | GND            | GNDIO3           | 3    |                  | + '          |

|                | -                |      |                  |              | VCCIO3         | VCCIO3           | 3    |                  |              | VCCIO3         | VCCIO3           | 3    |                  |              |

| K12            | NC               |      |                  |              | K12            | PR9D             | 3    |                  | С            | K12            | PR11D            | 3    |                  | С            |

| J12            | NC               |      |                  |              | J12            | PR9C             | 3    |                  | T            | J12            | PR11C            | 3    |                  | T            |

| J16            | PR7B             | 1    |                  | С            | J16            | PR9B             | 3    |                  | C**          | J16            | PR11B            | 3    |                  | C**          |

| H16            | PR7A             | 1    |                  | T            | H16            | PR9A             | 3    |                  | T**          | H16            | PR11A            | 3    |                  | T**          |

| H15            | PR6B             | 1    |                  | С            | H15            | PR8D             | 2    |                  | C            | H15            | PR10D            | 2    |                  | С            |

| G15            | PR6A             | 1    |                  | Т            | G15            | PR8C             | 2    |                  | Т            | G15            | PR10C            | 2    |                  | Т            |

| H14            | PR5D             | 1    |                  | С            | H14            | PR8B             | 2    |                  | C**          | H14            | PR10B            | 2    |                  | C**          |

| G14            | PR5C             | 1    |                  | Т            | G14            | PR8A             | 2    |                  | T**          | G14            | PR10A            | 2    |                  | T**          |