Welcome to **E-XFL.COM**

Understanding <u>Embedded - CPLDs (Complex Programmable Logic Devices)</u>

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixed-function ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

| Details                         |                                                                               |

|---------------------------------|-------------------------------------------------------------------------------|

| Product Status                  | Active                                                                        |

| Programmable Type               | In System Programmable                                                        |

| Delay Time tpd(1) Max           | 4.9 ns                                                                        |

| Voltage Supply - Internal       | 1.14V ~ 1.26V                                                                 |

| Number of Logic Elements/Blocks | -                                                                             |

| Number of Macrocells            | 320                                                                           |

| Number of Gates                 | -                                                                             |

| Number of I/O                   | 159                                                                           |

| Operating Temperature           | -40°C ~ 125°C (TA)                                                            |

| Mounting Type                   | Surface Mount                                                                 |

| Package / Case                  | 256-LBGA                                                                      |

| Supplier Device Package         | 256-FTBGA (17x17)                                                             |

| Purchase URL                    | https://www.e-xfl.com/product-detail/lattice-semiconductor/lamxo640e-3ftn256e |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

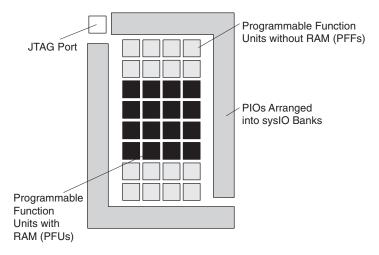

Figure 2-3. Top View of the LA-MachXO256 Device

#### **PFU Blocks**

The core of the LA-MachXO devices consists of PFU and PFF blocks. The PFUs can be programmed to perform Logic, Arithmetic, Distributed RAM, and Distributed ROM functions. PFF blocks can be programmed to perform Logic, Arithmetic, and Distributed ROM functions. Except where necessary, the remainder of this data sheet will use the term PFU to refer to both PFU and PFF blocks.

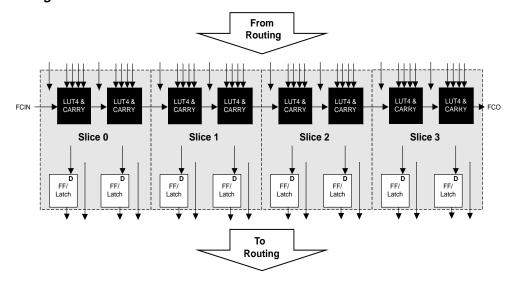

Each PFU block consists of four interconnected Slices, numbered 0-3 as shown in Figure 2-4. There are 53 inputs and 25 outputs associated with each PFU block.

Figure 2-4. PFU Diagram

#### Slice

Each Slice contains two LUT4 lookup tables feeding two registers (programmed to be in FF or Latch mode), and some associated logic that allows the LUTs to be combined to perform functions such as LUT5, LUT6, LUT7, and LUT8. There is control logic to perform set/reset functions (programmable as synchronous/asynchronous), clock select, chip-select, and wider RAM/ROM functions. Figure 2-5 shows an overview of the internal logic of the Slice. The registers in the Slice can be configured for positive/negative and edge/level clocks.

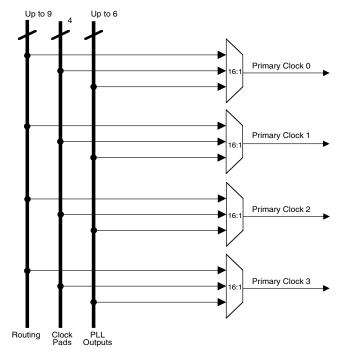

Figure 2-8. Primary Clocks for LA-MachXO1200 and LA-MachXO2280 Devices

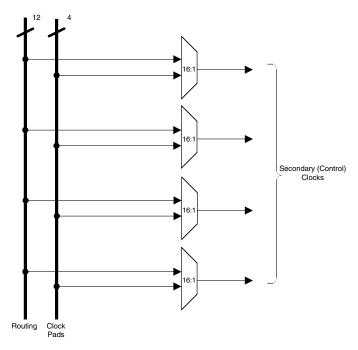

Four secondary clocks are generated from four 16:1 muxes as shown in Figure 2-9. Four of the secondary clock sources come from dual function clock pins and 12 come from internal routing.

Figure 2-9. Secondary Clocks for LA-MachXO Devices

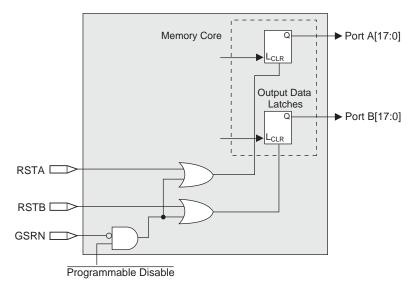

Figure 2-13. Memory Core Reset

For further information on the sysMEM EBR block, see the details of additional technical documentation at the end of this data sheet.

#### **EBR Asynchronous Reset**

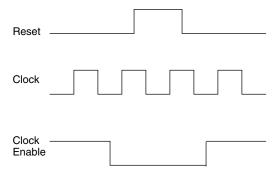

EBR asynchronous reset or GSR (if used) can only be applied if all clock enables are low for a clock cycle before the reset is applied and released a clock cycle after the reset is released, as shown in Figure 2-14. The GSR input to the EBR is always asynchronous.

Figure 2-14. EBR Asynchronous Reset (Including GSR) Timing Diagram

If all clock enables remain enabled, the EBR asynchronous reset or GSR may only be applied and released after the EBR read and write clock inputs are in a steady state condition for a minimum of 1/f<sub>MAX</sub> (EBR clock). The reset release must adhere to the EBR synchronous reset setup time before the next active read or write clock edge.

If an EBR is pre-loaded during configuration, the GSR input must be disabled or the release of the GSR during device Wake Up must occur before the release of the device I/Os becoming active.

These instructions apply to all EBR RAM, ROM and FIFO implementations. For the EBR FIFO mode, the GSR signal is always enabled and the WE and RE signals act like the clock enable signals in Figure 2-14. The reset timing rules apply to the RPReset input vs the RE input and the RST input vs. the WE and RE inputs. Both RST and RPReset are always asynchronous EBR inputs.

Note that there are no reset restrictions if the EBR synchronous reset is used and the EBR GSR input is disabled.

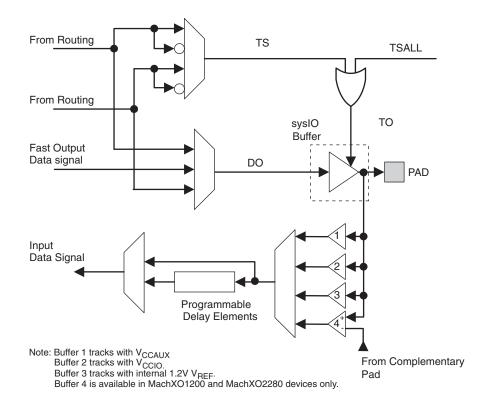

output data signals are multiplexed and provide a single signal to the I/O pin via the sysIO buffer. Figure 2-17 shows the LA-MachXO PIO logic.

The tristate control signal is multiplexed from the output data signals and their complements. In addition a global signal (TSALL) from a dedicated pad can be used to tristate the sysIO buffer.

The PIO receives an input signal from the pin via the sysIO buffer and provides this signal to the core of the device. In addition there are programmable elements that can be utilized by the design tools to avoid positive hold times.

Figure 2-17. LA-MachXO PIO Block Diagram

## sysIO Buffer

Each I/O is associated with a flexible buffer referred to as a sysIO buffer. These buffers are arranged around the periphery of the device in groups referred to as Banks. The sysIO buffers allow users to implement the wide variety of standards that are found in today's systems including LVCMOS, TTL, BLVDS, LVDS and LVPECL.

In the LA-MachXO devices, single-ended output buffers and ratioed input buffers (LVTTL, LVCMOS and PCI) are powered using  $V_{CCIO}$ . In addition to the Bank  $V_{CCIO}$  supplies, the LA-MachXO devices have a  $V_{CC}$  core logic power supply, and a  $V_{CCAUX}$  supply that powers up a variety of internal circuits including all the differential and referenced input buffers.

LA-MachXO256 and LA-MachXO640 devices contain single-ended input buffers and single-ended output buffers with complementary outputs on all the I/O Banks.

LA-MachXO1200 and LA-MachXO2280 devices contain two types of sysIO buffer pairs.

#### 1. Top and Bottom sysIO Buffer Pairs

The sysIO buffer pairs in the top and bottom Banks of the device consist of two single-ended output drivers and two sets of single-ended input buffers (for ratioed or absolute input levels). The I/O pairs on the top and bottom

Table 2-8. I/O Support Device by Device

|                                             | LA-MachXO256                                                          | LA-MachXO640                                                    | LA-MachXO1200                                                                  | LA-MachXO2280                                                                  |

|---------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Number of I/O Banks                         | 2                                                                     | 4                                                               | 8                                                                              | 8                                                                              |

| Type of Input Buffers                       | Single-ended<br>(all I/O Banks)                                       | Single-ended<br>(all I/O Banks)                                 | Single-ended (all I/O Banks)  Differential Receivers                           | Single-ended (all I/O Banks)  Differential Receivers                           |

|                                             | 0: 1 11 "                                                             | 0: 1 11 "                                                       | (all I/O Banks)                                                                | (all I/O Banks)                                                                |

| Types of Output Buffers                     | Single-ended buffers<br>with complementary<br>outputs (all I/O Banks) | Single-ended buffers with complementary outputs (all I/O Banks) | Single-ended buffers<br>with complementary<br>outputs (all I/O Banks)          | Single-ended buffers<br>with complementary<br>outputs (all I/O Banks)          |

|                                             |                                                                       |                                                                 | Differential buffers with<br>true LVDS outputs (50%<br>on left and right side) | Differential buffers with<br>true LVDS outputs (50%<br>on left and right side) |

| Differential Output<br>Emulation Capability | All I/O Banks                                                         | All I/O Banks                                                   | All I/O Banks                                                                  | All I/O Banks                                                                  |

| PCI Support                                 | No                                                                    | No                                                              | Top side only                                                                  | Top side only                                                                  |

Table 2-9. Supported Input Standards

|                                                                                  | VCCIO (Typ.) |      |      |      |      |  |

|----------------------------------------------------------------------------------|--------------|------|------|------|------|--|

| Input Standard                                                                   | 3.3V         | 2.5V | 1.8V | 1.5V | 1.2V |  |

| Single Ended Interfaces                                                          |              |      |      |      |      |  |

| LVTTL                                                                            | V            | V    | V    | √    | V    |  |

| LVCMOS33                                                                         | V            | V    | V    | √    | V    |  |

| LVCMOS25                                                                         | V            | V    | V    | √    | V    |  |

| LVCMOS18                                                                         |              |      | √    |      |      |  |

| LVCMOS15                                                                         |              |      |      | √    |      |  |

| LVCMOS12                                                                         | V            | V    | V    | √    | V    |  |

| PCI <sup>1</sup>                                                                 | √            |      |      |      |      |  |

| Differential Interfaces                                                          | •            | •    |      |      |      |  |

| BLVDS <sup>2</sup> , LVDS <sup>2</sup> , LVPECL <sup>2</sup> , RSDS <sup>2</sup> | V            | V    | V    | V    | V    |  |

<sup>1.</sup> Top Banks of LA-MachXO1200 and LA-MachXO2280 devices only.

<sup>2.</sup> LA-MachXO1200 and LA-MachXO2280 devices only.

Table 2-10. Supported Output Standards

| Output Standard          | Drive                | V <sub>CCIO</sub> (Typ.) |

|--------------------------|----------------------|--------------------------|

| Single-ended Interfaces  |                      |                          |

| LVTTL                    | 4mA, 8mA, 12mA, 16mA | 3.3                      |

| LVCMOS33                 | 4mA, 8mA, 12mA, 14mA | 3.3                      |

| LVCMOS25                 | 4mA, 8mA, 12mA, 14mA | 2.5                      |

| LVCMOS18                 | 4mA, 8mA, 12mA, 14mA | 1.8                      |

| LVCMOS15                 | 4mA, 8mA             | 1.5                      |

| LVCMOS12                 | 2mA, 6mA             | 1.2                      |

| LVCMOS33, Open Drain     | 4mA, 8mA, 12mA, 14mA | _                        |

| LVCMOS25, Open Drain     | 4mA, 8mA, 12mA, 14mA | _                        |

| LVCMOS18, Open Drain     | 4mA, 8mA, 12mA, 14mA | _                        |

| LVCMOS15, Open Drain     | 4mA, 8mA             | _                        |

| LVCMOS12, Open Drain     | 2mA, 6mA             | _                        |

| PCI33 <sup>3</sup>       | N/A                  | 3.3                      |

| Differential Interfaces  |                      |                          |

| LVDS <sup>1, 2</sup>     | N/A                  | 2.5                      |

| BLVDS, RSDS <sup>2</sup> | N/A                  | 2.5                      |

| LVPECL <sup>2</sup>      | N/A                  | 3.3                      |

<sup>1.</sup> LA-MachXO1200 and LA-MachXO2280 devices have dedicated LVDS buffers.

#### sysIO Buffer Banks

The number of Banks vary between the devices of this family. Eight Banks surround the two larger devices, the LA-MachXO1200 and LA-MachXO2280 (two Banks per side). The LA-MachXO640 has four Banks (one Bank per side). The smallest member of this family, the LA-MachXO256, has only two Banks.

Each sysIO buffer Bank is capable of supporting multiple I/O standards. Each Bank has its own I/O supply voltage  $(V_{CCIO})$  which allows it to be completely independent from the other Banks. Figure 2-18, Figure 2-18, Figure 2-20 and Figure 2-21 shows the sysIO Banks and their associated supplies for all devices.

<sup>2.</sup> These interfaces can be emulated with external resistors in all devices.

<sup>3.</sup> Top Banks of LA-MachXO1200 and LA-MachXO2280 devices only.

# LA-MachXO Automotive Family Data Sheet Onductor DC and Switching Characteristics

November 2007 Data Sheet DS1003

### Absolute Maximum Ratings<sup>1, 2, 3</sup>

|                                              | LCMXO E (1.2V) | LCMXO C (1.8V/2.5V/3.3V) |

|----------------------------------------------|----------------|--------------------------|

| Supply Voltage V <sub>CC</sub>               | 0.5 to 1.32V   | 0.5 to 3.75V             |

| Supply Voltage V <sub>CCAUX</sub>            | 0.5 to 3.75V   | 0.5 to 3.75V             |

| Output Supply Voltage $V_{CCIO}$             | 0.5 to 3.75V   | 0.5 to 3.75V             |

| I/O Tristate Voltage Applied 4               | 0.5 to 3.75V   | 0.5 to 3.75V             |

| Dedicated Input Voltage Applied <sup>4</sup> | 0.5 to 3.75V   | 0.5 to 4.25V             |

| Storage Temperature (ambient)                | 65 to 150°C    | 65 to 150°C              |

| Junction Temp. (Tj)                          | +125°C         | +125°C                   |

<sup>1.</sup> Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

## Recommended Operating Conditions<sup>1</sup>

| Symbol                          | Parameter                                           |       | Max.  | Units |

|---------------------------------|-----------------------------------------------------|-------|-------|-------|

| V                               | Core Supply Voltage for 1.2V Devices                | 1.14  | 1.26  | V     |

| V <sub>CC</sub>                 | Core Supply Voltage for 1.8V/2.5V/3.3V Devices      | 1.71  | 3.465 | V     |

| V <sub>CCAUX</sub> <sup>3</sup> | Auxiliary Supply Voltage                            | 3.135 | 3.465 | V     |

| V <sub>CCIO</sub> <sup>2</sup>  | I/O Driver Supply Voltage                           |       | 3.465 | V     |

| t <sub>JAUTO</sub>              | Junction Temperature Automotive Operation           | -40   | 125   | ç     |

| t <sub>JFLASHAUTO</sub>         | Junction Temperature, Flash Programming, Automotive | -40   | 125   | °C    |

Like power supplies must be tied together. For example, if V<sub>CCIO</sub> and V<sub>CC</sub> are both 2.5V, they must also be the same supply. 3.3V V<sub>CCIO</sub> and 1.2V V<sub>CCIO</sub> should be tied to V<sub>CCAUX</sub> or 1.2V V<sub>CC</sub> respectively.

### LA-MachXO256 and LA-MachXO640 Hot Socketing Specifications<sup>1,2,3</sup>

| Symbol          | Parameter                    | Condition                       | Min. | Тур. | Max     | Units |

|-----------------|------------------------------|---------------------------------|------|------|---------|-------|

| I <sub>DK</sub> | Input or I/O leakage Current | $0 \le V_{IN} \le V_{IH} (MAX)$ |      |      | +/-1000 | μΑ    |

<sup>1.</sup> Insensitive to sequence of  $V_{CC,}V_{CCAUX,}$  and  $V_{CCIO.}$  However, assumes monotonic rise/fall rates for  $V_{CC,}V_{CCAUX,}$  and  $V_{CCIO.}$

<sup>2.</sup> Compliance with the Lattice Thermal Management document is required.

<sup>3.</sup> All voltages referenced to GND.

<sup>4.</sup> Overshoot and undershoot of -2V to (V<sub>IHMAX</sub> + 2) volts is permitted for a duration of <20ns.

<sup>2.</sup> See recommended voltages by I/O standard in subsequent table.

<sup>3.</sup>  $V_{CC}$  must reach minimum  $V_{CC}$  value before  $V_{CCAUX}$  reaches 2.5V.

<sup>2.</sup>  $0 \le V_{CC} \le V_{CC}$  (MAX),  $0 \le V_{CCIO} \le V_{CCIO}$  (MAX) and  $0 \le V_{CCAUX} \le V_{CCAUX}$  (MAX).

<sup>3.</sup> I<sub>DK</sub> is additive to I<sub>PU</sub>, I<sub>PD</sub> or I<sub>BH</sub>.

## LA-MachXO1200 and LA-MachXO2280 Hot Socketing Specifications<sup>1, 2, 3, 4</sup>

| Symbol                          | Parameter                    | Condition                           | Min. | Тур. | Max.    | Units |

|---------------------------------|------------------------------|-------------------------------------|------|------|---------|-------|

| Non-LVDS General Purpose syslOs |                              |                                     |      |      |         |       |

| I <sub>DK</sub>                 | Input or I/O Leakage Current | $0 \le V_{IN} \le V_{IH} (MAX.)$    | _    | _    | +/-1000 | μA    |

| LVDS General Purpose syslOs     |                              |                                     |      |      |         |       |

| lau waa                         | Input or I/O Leakage Current | V <sub>IN</sub> ≤ V <sub>CCIO</sub> | _    | _    | +/-1000 | μΑ    |

| Input or I/O Leakage Current    |                              | $V_{IN} > V_{CCIO}$                 | _    | 35   | _       | mA    |

- 1. Insensitive to sequence of  $V_{CC, V_{CCAUX}}$ , and  $V_{CCIO}$ . However, assumes monotonic rise/fall rates for  $V_{CC, V_{CCAUX}}$ , and  $V_{CCIO}$ . 2.  $0 \le V_{CC} \le V_{CC}$  (MAX),  $0 \le V_{CCIO} \le V_{CCIO}$  (MAX), and  $0 \le V_{CCAUX} \le V_{CCAUX}$  (MAX).

- 3.  $I_{DK}$  is additive to  $I_{PU}$ ,  $I_{PW}$  or  $I_{BH}$ .

- 4. LVCMOS and LVTTL only.

#### **DC Electrical Characteristics**

#### **Over Recommended Operating Conditions**

| Symbol                                   | Parameter                                | Condition                                                                                    | Min.                  | Тур. | Max.                  | Units |

|------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------|------|-----------------------|-------|

| I <sub>IL,</sub> I <sub>IH</sub> 1, 4, 5 | Input or I/O Leakage                     | $0 \le V_{IN} \le (V_{CCIO} - 0.2V)$                                                         | _                     | _    | 10                    | μΑ    |

| I'IL, 'IH                                | linput of 1/O Leakage                    | $(V_{CCIO} - 0.2V) < V_{IN} \le 3.6V$                                                        | _                     | _    | 40                    | μΑ    |

| I <sub>PU</sub>                          | I/O Active Pull-up Current               | $0 \le V_{IN} \le 0.7 V_{CCIO}$                                                              | -30                   | _    | -150                  | μΑ    |

| I <sub>PD</sub>                          | I/O Active Pull-down Current             | $V_{IL}$ (MAX) $\leq V_{IN} \leq V_{IH}$ (MAX)                                               | 30                    | _    | 150                   | μΑ    |

| I <sub>BHLS</sub>                        | Bus Hold Low sustaining current          | $V_{IN} = V_{IL} (MAX)$                                                                      | 30                    |      | _                     | μΑ    |

| I <sub>BHHS</sub>                        | Bus Hold High sustaining current         | $V_{IN} = 0.7V_{CCIO}$                                                                       | -30                   | _    | _                     | μΑ    |

| I <sub>BHLO</sub>                        | Bus Hold Low Overdrive current           | $0 \le V_{IN} \le V_{IH} (MAX)$                                                              | _                     | _    | 150                   | μΑ    |

| I <sub>BHHO</sub>                        | Bus Hold High Overdrive current          | $0 \le V_{IN} \le V_{IH} (MAX)$                                                              | _                     |      | -150                  | μΑ    |

| V <sub>BHT</sub> <sup>3</sup>            | Bus Hold trip Points                     | $0 \le V_{IN} \le V_{IH} (MAX)$                                                              | V <sub>IL</sub> (MAX) | _    | V <sub>IH</sub> (MIN) | V     |

| C1                                       | I/O Capacitance <sup>2</sup>             | $V_{CCIO} = 3.3V$ , 2.5V, 1.8V, 1.5V, 1.2V, $V_{CC} = Typ.$ , $V_{IO} = 0$ to $V_{IH}$ (MAX) | _                     | 8    | _                     | pf    |

| C2                                       | Dedicated Input Capacitance <sup>2</sup> | $V_{CCIO} = 3.3V$ , 2.5V, 1.8V, 1.5V, 1.2V, $V_{CC} = Typ.$ , $V_{IO} = 0$ to $V_{IH}$ (MAX) | _                     | 8    | _                     | pf    |

<sup>1.</sup> Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

- 2.  $T_A$  25°C, f = 1.0MHz

- 3. Please refer to  $V_{IL}$  and  $V_{IH}$  in the sysIO Single-Ended DC Electrical Characteristics table of this document.

- 4. Not applicable to SLEEPN pin.

- 5. When VIH is higher than VCCIO, a transient current typically of 30ns in duration or less with a peak current of 6mA can occur on the high-tolow transition. For LA-MachXO1200 and LA-MachXO2280 true LVDS output pins, VIH must be less than or equal to VCIIO.

## sysIO Recommended Operating Conditions

|                      | V <sub>CCIO</sub> (V) |      |       |  |

|----------------------|-----------------------|------|-------|--|

| Standard             | Min.                  | Тур. | Max.  |  |

| LVCMOS 3.3           | 3.135                 | 3.3  | 3.465 |  |

| LVCMOS 2.5           | 2.375                 | 2.5  | 2.625 |  |

| LVCMOS 1.8           | 1.71                  | 1.8  | 1.89  |  |

| LVCMOS 1.5           | 1.425                 | 1.5  | 1.575 |  |

| LVCMOS 1.2           | 1.14                  | 1.2  | 1.26  |  |

| LVTTL                | 3.135                 | 3.3  | 3.465 |  |

| PCI <sup>3</sup>     | 3.135                 | 3.3  | 3.465 |  |

| LVDS <sup>1, 2</sup> | 2.375                 | 2.5  | 2.625 |  |

| LVPECL1              | 3.135                 | 3.3  | 3.465 |  |

| BLVDS <sup>1</sup>   | 2.375                 | 2.5  | 2.625 |  |

| RSDS <sup>1</sup>    | 2.375                 | 2.5  | 2.625 |  |

<sup>1.</sup> Inputs on chip. Outputs are implemented with the addition of external resistors.

<sup>2.</sup> MachXO1200 and MachXO2280 devices have dedicated LVDS buffers

<sup>3.</sup> Input on the top bank of the MachXO1200 and MachXO2280 only.

## sysIO Differential Electrical Characteristics LVDS

#### **Over Recommended Operating Conditions**

| Parameter<br>Symbol                | Parameter Description                                      | Test Conditions                                 | Min.                | Тур. | Max.  | Units |

|------------------------------------|------------------------------------------------------------|-------------------------------------------------|---------------------|------|-------|-------|

| V <sub>INP,</sub> V <sub>INM</sub> | Input Voltage                                              |                                                 | 0                   | _    | 2.4   | V     |

| $V_{THD}$                          | Differential Input Threshold                               |                                                 | +/-100              |      | _     | mV    |

|                                    |                                                            | 100mV ≤ V <sub>THD</sub>                        | V <sub>THD</sub> /2 | 1.2  | 1.8   | V     |

| $V_{CM}$                           | Input Common Mode Voltage                                  | 200mV ≤ V <sub>THD</sub>                        | V <sub>THD</sub> /2 | 1.2  | 1.9   | V     |

|                                    |                                                            | 350mV ≤ V <sub>THD</sub>                        | V <sub>THD</sub> /2 | 1.2  | 2.0   | V     |

| I <sub>IN</sub>                    | Input current                                              | Power on                                        | _                   | _    | +/-10 | μΑ    |

| V <sub>OH</sub>                    | Output high voltage for V <sub>OP</sub> or V <sub>OM</sub> | R <sub>T</sub> = 100 Ohm                        | _                   | 1.38 | 1.60  | V     |

| $V_{OL}$                           | Output low voltage for V <sub>OP</sub> or V <sub>OM</sub>  | R <sub>T</sub> = 100 Ohm                        | 0.9V                | 1.03 | _     | V     |

| V <sub>OD</sub>                    | Output voltage differential                                | $(V_{OP} - V_{OM}), R_T = 100 Ohm$              | 250                 | 350  | 450   | mV    |

| ΔV <sub>OD</sub>                   | Change in V <sub>OD</sub> between high and low             |                                                 | _                   | _    | 50    | mV    |

| V <sub>OS</sub>                    | Output voltage offset                                      | $(V_{OP} - V_{OM})/2$ , $R_T = 100 \text{ Ohm}$ | 1.125               | 1.25 | 1.375 | V     |

| ΔV <sub>OS</sub>                   | Change in V <sub>OS</sub> between H and L                  |                                                 | _                   | _    | 50    | mV    |

| I <sub>OSD</sub>                   | Output short circuit current                               | V <sub>OD</sub> = 0V Driver outputs shorted     | _                   | _    | 6     | mA    |

#### **LVDS Emulation**

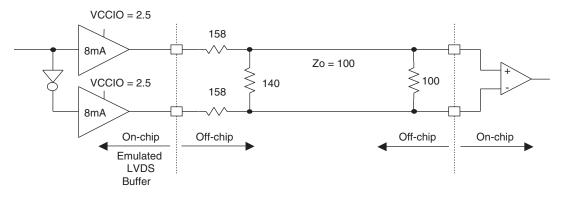

LA-MachXO automotive devices can support LVDS outputs via emulation (LVDS25E), in addition to the LVDS support that is available on-chip on certain devices. The output is emulated using complementary LVCMOS outputs in conjunction with resistors across the driver outputs on all devices. The scheme shown in Figure 3-1 is one possible solution for LVDS standard implementation. Resistor values in Figure 3-1 are industry standard values for 1% resistors.

Figure 3-1. LVDS Using External Resistors (LVDS25E)

Note: All resistors are  $\pm 1\%$ .

The LVDS differential input buffers are available on certain devices in the LA-MachXO family.

Table 3-1. LVDS DC Conditions

#### **Over Recommended Operating Conditions**

| Parameter         | Description                 | Typical | Units |

|-------------------|-----------------------------|---------|-------|

| Z <sub>OUT</sub>  | Output impedance            | 20      | Ω     |

| R <sub>S</sub>    | Driver series resistor      | 294     | Ω     |

| R <sub>P</sub>    | Driver parallel resistor    | 121     | Ω     |

| R <sub>T</sub>    | Receiver termination        | 100     | Ω     |

| V <sub>OH</sub>   | Output high voltage         | 1.43    | V     |

| V <sub>OL</sub>   | Output low voltage          | 1.07    | V     |

| V <sub>OD</sub>   | Output differential voltage | 0.35    | V     |

| V <sub>CM</sub>   | Output common mode voltage  | 1.25    | V     |

| Z <sub>BACK</sub> | Back impedance              | 100     | Ω     |

| I <sub>DC</sub>   | DC output current           | 3.66    | mA    |

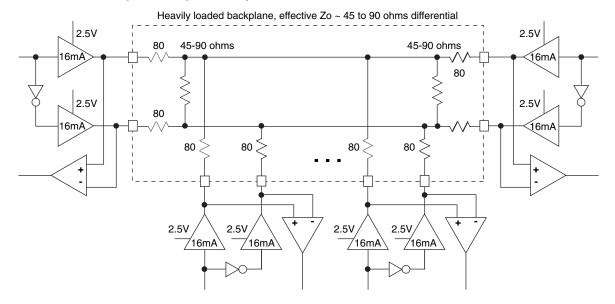

#### **BLVDS**

The LA-MachXO automotive family supports the BLVDS standard through emulation. The output is emulated using complementary LVCMOS outputs in conjunction with a parallel external resistor across the driver outputs. The input standard is supported by the LVDS differential input buffer on certain devices. BLVDS is intended for use when multi-drop and bi-directional multi-point differential signaling is required. The scheme shown in Figure 3-2 is one possible solution for bi-directional multi-point differential signals.

Figure 3-2. BLVDS Multi-point Output Example

## Typical Building Block Function Performance<sup>1</sup>

### Pin-to-Pin Performance (LVCMOS25 12mA Drive)

| Function        | -3 Timing | Units |

|-----------------|-----------|-------|

| Basic Functions |           |       |

| 16-bit decoder  | 9.4       | ns    |

| 4:1 MUX         | 6.3       | ns    |

| 16:1 MUX        | 7.1       | ns    |

#### **Register-to-Register Performance**

| Function                             | -3 Timing                 | Units |

|--------------------------------------|---------------------------|-------|

| Basic Functions                      |                           |       |

| 16:1 MUX                             | 348                       | MHz   |

| 16-bit adder                         | 209                       | MHz   |

| 16-bit counter                       | 277                       | MHz   |

| 64-bit counter                       | 143                       | MHz   |

| <b>Embedded Memory Functions (12</b> | 00 and 2280 Devices Only) |       |

| 256x36 Single Port RAM               | 203                       | MHz   |

| 512x18 True-Dual Port RAM            | 203                       | MHz   |

| Distributed Memory Functions         |                           |       |

| 16x2 Single Port RAM                 | 310                       | MHz   |

| 64x2 Single Port RAM                 | 229                       | MHz   |

| 128x4 Single Port RAM                | 186                       | MHz   |

| 32x2 Pseudo-Dual Port RAM            | 224                       | MHz   |

| 64x4 Pseudo-Dual Port RAM            | 194                       | MHz   |

The above timing numbers are generated using the ispLEVER design tool. Exact performance may vary with device and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

Rev. A 0.19

## **Derating Logic Timing**

Logic Timing provided in the following sections of the data sheet and the ispLEVER design tools are worst case numbers in the operating range. Actual delays may be much faster. The ispLEVER design tool from Lattice can provide logic timing numbers at a particular temperature and voltage.

### sysCLOCK PLL Timing

#### **Over Recommended Operating Conditions**

| Descriptions                          | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                      | Min.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Max.                                     | Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Clock Frequency (CLKI, CLKFB)   |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 420                                      | MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Output Clock Frequency (CLKOP, CLKOS) |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 420                                      | MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| K-Divider Output Frequency (CLKOK)    |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0.195                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 210                                      | MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PLL VCO Frequency                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 420                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 840                                      | MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Phase Detector Input Frequency        |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                        | MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| eristics                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Output Clock Duty Cycle               | Default duty cycle selected <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                        | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55                                       | %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Output Phase Accuracy                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0.05                                     | UI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Output Clask Pariod litter            | Fout ≥ 100MHz                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | +/-120                                   | ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Output Clock Period Jitter            | Fout < 100MHz                                                                                                                                                                                                                                                                                                                                                                                                                                   | T —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0.02                                     | UIPP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Input Clock to Output Clock Skew      | Divider ratio = integer                                                                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | +/-200                                   | ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Output Clock Pulse Width              | At 90% or 10% <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                        | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PLL Lock-in Time                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 150                                      | μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Programmable Delay Unit               |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 450                                      | ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Input Clock Period Jitter             |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | +/-200                                   | ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| External Feedback Delay               |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10                                       | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Input Clock High Time                 | 90% to 90%                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                                        | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Input Clock Low Time                  | 10% to 10%                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                                        | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RST Pulse Width                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                        | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                       | Input Clock Frequency (CLKI, CLKFB) Output Clock Frequency (CLKOP, CLKOS) K-Divider Output Frequency (CLKOK) PLL VCO Frequency Phase Detector Input Frequency Pristics Output Clock Duty Cycle Output Phase Accuracy Output Clock Period Jitter Input Clock to Output Clock Skew Output Clock Pulse Width PLL Lock-in Time Programmable Delay Unit Input Clock Period Jitter External Feedback Delay Input Clock High Time Input Clock Low Time | Input Clock Frequency (CLKI, CLKFB)  Output Clock Frequency (CLKOP, CLKOS)  K-Divider Output Frequency (CLKOK)  PLL VCO Frequency  Phase Detector Input Frequency  Pristics  Output Clock Duty Cycle  Output Phase Accuracy  Output Clock Period Jitter  Input Clock to Output Clock Skew  Divider ratio = integer  Output Clock Pulse Width  At 90% or 10%³  PLL Lock-in Time  Programmable Delay Unit  Input Clock Period Jitter  External Feedback Delay  Input Clock High Time  Po% to 90%  Input Clock Low Time | Input Clock Frequency (CLKI, CLKFB)   25 | Input Clock Frequency (CLKI, CLKFB)         25         420           Output Clock Frequency (CLKOP, CLKOS)         25         420           K-Divider Output Frequency (CLKOK)         0.195         210           PLL VCO Frequency         420         840           Phase Detector Input Frequency         25         —           ristics           Output Clock Duty Cycle         Default duty cycle selected³         45         55           Output Phase Accuracy         —         0.05           Output Clock Period Jitter         Fout ≥ 100MHz         —         +/-120           Fout < 100MHz |

- 1. Jitter sample is taken over 10,000 samples of the primary PLL output with a clean reference clock.

- 2. Output clock is valid after  $t_{LOCK}$  for PLL reset and dynamic delay adjustment.

- 3. Using LVDS output buffers.

- 4. CLKOS as compared to CLKOP output.

Rev. A 0.19

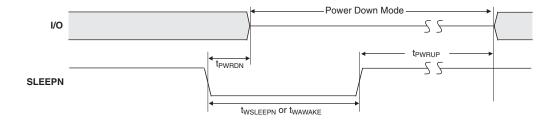

## LA-MachXO "C" Sleep Mode Timing

| Symbol                               | Parameter                 | Device   | Min. | Тур. | Max | Units |

|--------------------------------------|---------------------------|----------|------|------|-----|-------|

| t <sub>PWRDN</sub>                   | SLEEPN Low to Power Down  | All      | _    | _    | 400 | ns    |

| t <sub>PWRUP</sub> SLEEPN High to Po | SI EEDNI High to Power Up | LCMXO256 | _    | _    | 400 | μs    |

|                                      | SEEFIN High to Fower op   | LCMXO640 | _    | _    | 600 | μs    |

| t <sub>WSLEEPN</sub>                 | SLEEPN Pulse Width        | All      | 400  | _    | _   | ns    |

| twawake                              | SLEEPN Pulse Rejection    | All      | _    | _    | 100 | ns    |

Rev. A 0.19

## LA-MachXO256 and LA-MachXO640 Logic Signal Connections: 100 TQFP

|            |                  | LAM  | XO256            |              | LAMXO640         |      |                  |              |  |

|------------|------------------|------|------------------|--------------|------------------|------|------------------|--------------|--|

| Pin Number | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Function | Bank | Dual<br>Function | Differential |  |

| 1          | PL2A             | 1    |                  | Т            | PL2A             | 3    |                  | Т            |  |

| 2          | PL2B             | 1    |                  | С            | PL2C             | 3    |                  | Т            |  |

| 3          | PL3A             | 1    |                  | Т            | PL2B             | 3    |                  | С            |  |

| 4          | PL3B             | 1    |                  | С            | PL2D             | 3    |                  | С            |  |

| 5          | PL3C             | 1    |                  | Т            | PL3A             | 3    |                  | Т            |  |

| 6          | PL3D             | 1    |                  | С            | PL3B             | 3    |                  | С            |  |

| 7          | PL4A             | 1    |                  | Т            | PL3C             | 3    |                  | Т            |  |

| 8          | PL4B             | 1    |                  | С            | PL3D             | 3    |                  | С            |  |

| 9          | PL5A             | 1    |                  | Т            | PL4A             | 3    |                  |              |  |

| 10         | VCCIO1           | 1    |                  |              | VCCIO3           | 3    |                  |              |  |

| 11         | PL5B             | 1    |                  | С            | PL4C             | 3    |                  | Т            |  |

| 12         | GNDIO1           | 1    |                  |              | GNDIO3           | 3    |                  |              |  |

| 13         | PL5C             | 1    |                  | Т            | PL4D             | 3    |                  | С            |  |

| 14         | PL5D             | 1    | GSRN             | С            | PL5B             | 3    | GSRN             |              |  |

| 15         | PL6A             | 1    |                  | Т            | PL7B             | 3    |                  |              |  |

| 16         | PL6B             | 1    | TSALL            | С            | PL8C             | 3    | TSALL            | Т            |  |

| 17         | PL7A             | 1    |                  | Т            | PL8D             | 3    |                  | С            |  |

| 18         | PL7B             | 1    |                  | С            | PL9A             | 3    |                  |              |  |

| 19         | PL7C             | 1    |                  | Т            | PL9C             | 3    |                  |              |  |

| 20         | PL7D             | 1    |                  | С            | PL10A            | 3    |                  |              |  |

| 21         | PL8A             | 1    |                  | Т            | PL10C            | 3    |                  |              |  |

| 22         | PL8B             | 1    |                  | С            | PL11A            | 3    |                  |              |  |

| 23         | PL9A             | 1    |                  | Т            | PL11C            | 3    |                  |              |  |

| 24         | VCCIO1           | 1    |                  |              | VCCIO3           | 3    |                  |              |  |

| 25         | GNDIO1           | 1    |                  |              | GNDIO3           | 3    |                  |              |  |

| 26         | TMS              | 1    | TMS              |              | TMS              | 2    | TMS              |              |  |

| 27         | PL9B             | 1    |                  | С            | PB2C             | 2    |                  |              |  |

| 28         | TCK              | 1    | TCK              |              | TCK              | 2    | TCK              |              |  |

| 29         | PB2A             | 1    |                  | Т            | VCCIO2           | 2    |                  |              |  |

| 30         | PB2B             | 1    |                  | С            | GNDIO2           | 2    |                  |              |  |

| 31         | TDO              | 1    | TDO              |              | TDO              | 2    | TDO              |              |  |

| 32         | PB2C             | 1    |                  | Т            | PB4C             | 2    |                  |              |  |

| 33         | TDI              | 1    | TDI              |              | TDI              | 2    | TDI              |              |  |

| 34         | PB2D             | 1    |                  | С            | PB4E             | 2    |                  |              |  |

| 35         | VCC              | -    |                  |              | VCC              | -    |                  |              |  |

| 36         | PB3A             | 1    | PCLK1_1**        | Т            | PB5B             | 2    | PCLK2_1**        |              |  |

| 37         | PB3B             | 1    |                  | С            | PB5D             | 2    |                  |              |  |

| 38         | PB3C             | 1    | PCLK1_0**        | Т            | PB6B             | 2    | PCLK2_0**        |              |  |

| 39         | PB3D             | 1    |                  | С            | PB6C             | 2    |                  |              |  |

| 40         | GND              | -    |                  |              | GND              | -    |                  |              |  |

| 41         | VCCIO1           | 1    |                  |              | VCCIO2           | 2    |                  |              |  |

## LA-MachXO256 and LA-MachXO640 Logic Signal Connections: 100 TQFP (Cont.)

|            | LAMXO256         |      |                  |              | LAMXO640         |      |                  |              |  |

|------------|------------------|------|------------------|--------------|------------------|------|------------------|--------------|--|

| Pin Number | Ball<br>Function | Bank | Dual<br>Function | Differential | Ball<br>Function | Bank | Dual<br>Function | Differential |  |

| 83         | PT4C             | 0    |                  | Т            | PT7A             | 0    |                  |              |  |

| 84         | GND              | -    |                  |              | GND              | -    |                  |              |  |

| 85         | PT4B             | 0    | PCLK0_1**        | С            | PT6B             | 0    | PCLK0_1**        |              |  |

| 86         | PT4A             | 0    | PCLK0_0**        | T            | PT5B             | 0    | PCLK0_0**        | С            |  |

| 87         | PT3D             | 0    |                  | С            | PT5A             | 0    |                  | Т            |  |

| 88         | VCCAUX           | -    |                  |              | VCCAUX           | -    |                  |              |  |

| 89         | PT3C             | 0    |                  | T            | PT4F             | 0    |                  |              |  |

| 90         | VCC              | -    |                  |              | VCC              | -    |                  |              |  |

| 91         | PT3B             | 0    |                  | С            | PT3F             | 0    |                  |              |  |

| 92         | VCCIO0           | 0    |                  |              | VCCIO0           | 0    |                  |              |  |

| 93         | GNDIO0           | 0    |                  |              | GNDIO0           | 0    |                  |              |  |

| 94         | РТ3А             | 0    |                  | Т            | PT3B             | 0    |                  | С            |  |

| 95         | PT2F             | 0    |                  | С            | PT3A             | 0    |                  | Т            |  |

| 96         | PT2E             | 0    |                  | Т            | PT2F             | 0    |                  | С            |  |

| 97         | PT2D             | 0    |                  | С            | PT2E             | 0    |                  | Т            |  |