Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

:XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | ECANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6К х 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 8x12b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN-S (6x6)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f25k80-e-mm |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

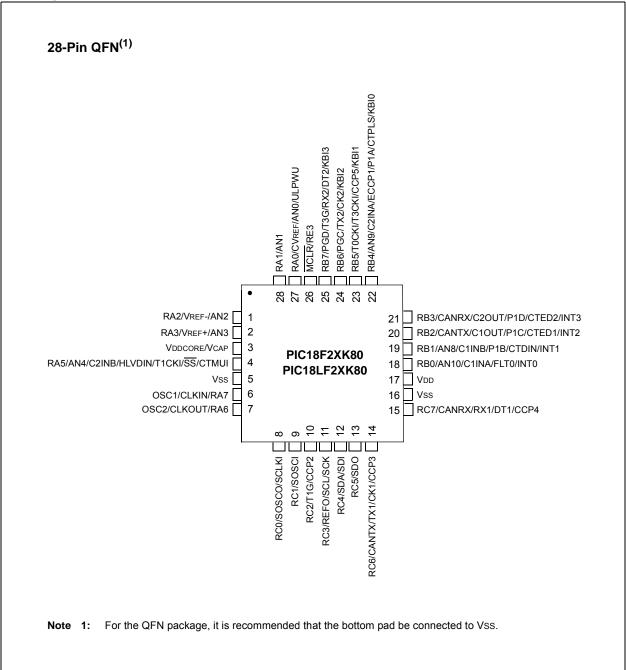

### **Pin Diagrams**

| Pin Name                                                               | Pin<br>Num  | Pin<br>Type | Buffer<br>Type | Description                                                                             |

|------------------------------------------------------------------------|-------------|-------------|----------------|-----------------------------------------------------------------------------------------|

| RD6/P1C/PSP6                                                           | 4           |             |                |                                                                                         |

| RD6                                                                    |             | I/O         | ST/<br>CMOS    | Digital I/O.                                                                            |

| P1C                                                                    |             | 0           | CMOS           | Enhanced PWM1 Output C.                                                                 |

| PSP6                                                                   |             | I/O         | ST/<br>CMOS    | Parallel Slave Port data.                                                               |

| RD7/P1D/PSP7                                                           | 5           |             |                |                                                                                         |

| RD7                                                                    |             | I/O         | ST/<br>CMOS    | Digital I/O.                                                                            |

| P1D                                                                    |             | 0           | CMOS           | Enhanced PWM1 Output D.                                                                 |

| PSP7                                                                   |             | I/O         | ST/<br>CMOS    | Parallel Slave Port data.                                                               |

| Legend: I <sup>2</sup> C™ = I <sup>2</sup> C<br>ST = Schr<br>I = Input | nitt Trigge | -           |                | CMOS = CMOS compatible input or output<br>OS levels Analog = Analog input<br>O = Output |

| TABLE 1-6: PIC18F6XK80 PINOUT I/O DESCRIPTIONS (CONTINUED | )) |

|-----------------------------------------------------------|----|

|-----------------------------------------------------------|----|

I = Input P = Power

## REGISTER 4-1: PMD2: PERIPHERAL MODULE DISABLE REGISTER 2

| U-0   | U-0 | U-0 U-0 |   | R/W-0 R/W-0          |        | R/W-0  | R/W-0  |

|-------|-----|---------|---|----------------------|--------|--------|--------|

| —     | —   | —       | — | MODMD <sup>(1)</sup> | ECANMD | CMP2MD | CMP1MD |

| bit 7 |     |         |   |                      |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-4 | Unimplemented: Read as '0'                                                                                         |

|---------|--------------------------------------------------------------------------------------------------------------------|

| bit 3   | MODMD: Modulator Output Module Disable bit <sup>(1)</sup>                                                          |

|         | 1 = The modulator output module is disabled; all Modulator Output registers are held in Reset and are not writable |

|         | 0 = The modulator output module is enabled                                                                         |

| bit 2   | ECANMD: Enhanced CAN Module Disable bit                                                                            |

|         | 1 = The Enhanced CAN module is disabled; all Enhanced CAN registers are held in Reset and are not writable         |

|         | 0 = The Enhanced CAN module is enabled                                                                             |

| bit 1   | CMP2MD: Comparator 2 Module Disable bit                                                                            |

|         | 1 = The Comparator 2 module is disabled; all Comparator 2 registers are held in Reset and are not writable         |

|         | 0 = The Comparator 2 module is enabled                                                                             |

| bit 0   | CMP1MD: Comparator 1 Module Disable bit                                                                            |

|         | 1 = The Comparator 1 module is disabled; all Comparator 1 registers are held in Reset and are not writable         |

|         | 0 = The Comparator 1 module is enabled                                                                             |

|         |                                                                                                                    |

Note 1: This bit is only implemented on devices with 64 pins (PIC18F6XK80, PIC18LF6XK80).

| Addr. | Name                       | Addr. | Name                       | Addr. | Name                       | Addr. | Name                       | Addr. | Name                     | Addr. | Name                    |

|-------|----------------------------|-------|----------------------------|-------|----------------------------|-------|----------------------------|-------|--------------------------|-------|-------------------------|

| F3Fh  | CANCON_RO0 <sup>(5)</sup>  | F0Fh  | CANCON_RO3(5)              | EDFh  | CANCON_RO4 <sup>(5)</sup>  | EAFh  | CANCON_RO7(5)              | E7Fh  | TXBIE <sup>(5)</sup>     | E4Fh  | RXF7EIDL <sup>(5)</sup> |

|       | CANSTAT_RO0 <sup>(5)</sup> |       | CANSTAT_RO3 <sup>(5)</sup> | EDEh  | CANSTAT_RO4 <sup>(5)</sup> |       | CANSTAT_RO7 <sup>(5)</sup> | E7Eh  | BIE0 <sup>(5)</sup>      | E4Eh  | RXF7EIDH <sup>(5)</sup> |

| F3Dh  | RXB1D7 <sup>(5)</sup>      | F0Dh  | TXB2D7 <sup>(5)</sup>      | EDDh  | B5D7 <sup>(5)</sup>        | EADh  | B2D7 <sup>(5)</sup>        | E7Dh  | BSEL0 <sup>(5)</sup>     | E4Dh  | RXF7SIDL <sup>(5)</sup> |

| F3Ch  | RXB1D6 <sup>(5)</sup>      | F0Ch  | TXB2D6 <sup>(5)</sup>      | EDCh  | B5D6 <sup>(5)</sup>        | EACh  | B2D6 <sup>(5)</sup>        | E7Ch  | MSEL3 <sup>(5)</sup>     | E4Ch  | RXF7SIDH <sup>(5)</sup> |

| F3Bh  | RXB1D5 <sup>(5)</sup>      | F0Bh  | TXB2D5 <sup>(5)</sup>      | EDBh  | B5D5 <sup>(5)</sup>        | EABh  | B2D5 <sup>(5)</sup>        | E7Bh  | MSEL2 <sup>(5)</sup>     | E4Bh  | RXF6EIDL <sup>(5)</sup> |

| F3Ah  | RXB1D4 <sup>(5)</sup>      | F0Ah  | TXB2D4 <sup>(5)</sup>      | EDAh  | B5D4 <sup>(5)</sup>        | EAAh  | B2D4 <sup>(5)</sup>        | E7Ah  | MSEL1 <sup>(5)</sup>     | E4Ah  | RXF6EIDH <sup>(5)</sup> |

| F39h  | RXB1D3 <sup>(5)</sup>      | F09h  | TXB2D3 <sup>(5)</sup>      | ED9h  | B5D3 <sup>(5)</sup>        | EA9h  | B2D3 <sup>(5)</sup>        | E79h  | MSEL0 <sup>(5)</sup>     | E49h  | RXF6SIDL <sup>(5)</sup> |

| F38h  | RXB1D2 <sup>(5)</sup>      | F08h  | TXB2D2 <sup>(5)</sup>      | ED8h  | B5D2 <sup>(5)</sup>        | EA8h  | B2D2 <sup>(5)</sup>        | E78h  | RXFBCON7 <sup>(5)</sup>  | E48h  | RXF6SIDH(5)             |

| F37h  | RXB1D1 <sup>(5)</sup>      | F07h  | TXB2D1 <sup>(5)</sup>      | ED7h  | B5D1 <sup>(5)</sup>        | EA7h  | B2D1 <sup>(5)</sup>        | E77h  | RXFBCON6(5)              | E47h  | RXFCON1 <sup>(5)</sup>  |

| F36h  | RXB1D0 <sup>(5)</sup>      | F06h  | TXB2D0 <sup>(5)</sup>      | ED6h  | B5D0 <sup>(5)</sup>        | EA6h  | B2D0 <sup>(5)</sup>        | E76h  | RXFBCON5(5)              | E46h  | RXFCON0 <sup>(5)</sup>  |

| F35h  | RXB1DLC <sup>(5)</sup>     | F05h  | TXB2DLC <sup>(5)</sup>     | ED5h  | B5DLC <sup>(5)</sup>       | EA5h  | B2DLC <sup>(5)</sup>       | E75h  | RXFBCON4 <sup>(5)</sup>  | E45h  | BRGCON3(5)              |

| F34h  | RXB1EIDL <sup>(5)</sup>    | F04h  | TXB2EIDL <sup>(5)</sup>    | ED4h  | B5EIDL <sup>(5)</sup>      | EA4h  | B2EIDL <sup>(5)</sup>      | E74h  | RXFBCON3(5)              | E44h  | BRGCON2 <sup>(5)</sup>  |

| F33h  | RXB1EIDH <sup>(5)</sup>    | F03h  | TXB2EIDH <sup>(5)</sup>    | ED3h  | B5EIDH <sup>(5)</sup>      | EA3h  | B2EIDH <sup>(5)</sup>      | E73h  | RXFBCON2 <sup>(5)</sup>  | E43h  | BRGCON1 <sup>(5)</sup>  |

| F32h  | RXB1SIDL <sup>(5)</sup>    | F02h  | TXB2SIDL <sup>(5)</sup>    | ED2h  | B5SIDL <sup>(5)</sup>      | EA2h  | B2SIDL <sup>(5)</sup>      | E72h  | RXFBCON1(5)              | E42h  | TXERRCNT <sup>(5)</sup> |

| F31h  | RXB1SIDH <sup>(5)</sup>    | F01h  | TXB2SIDH <sup>(5)</sup>    | ED1h  | B5SIDH <sup>(5)</sup>      | EA1h  | B2SIDH <sup>(5)</sup>      | E71h  | RXFBCON0(5)              | E41h  | RXERRCNT <sup>(5)</sup> |

| F30h  | RXB1CON <sup>(5)</sup>     | F00h  | TXB2CON <sup>(5)</sup>     | ED0h  | B5CON <sup>(5)</sup>       | EA0h  | B2CON <sup>(5)</sup>       | E70h  | SDFLC <sup>(5)</sup>     |       |                         |

| F30h  | RXB1CON <sup>(5)</sup>     | EFFh  | RXM1EIDL <sup>(5)</sup>    | ECFh  | CANCON_RO5(5)              | E9Fh  | CANCON_RO8(5)              | E6Fh  | RXF15EIDL <sup>(5)</sup> |       |                         |

| F2Fh  | CANCON_RO1(5)              | EFEh  | RXM1EIDH <sup>(5)</sup>    | ECEh  | CANSTAT_RO5(5)             | E9Eh  | CANSTAT_RO8 <sup>(5)</sup> | E6Eh  | RXF15EIDH <sup>(5)</sup> |       |                         |

| F2Eh  | CANSTAT_RO1(5)             | EFDh  | RXM1SIDL <sup>(5)</sup>    | ECDh  | B4D7 <sup>(5)</sup>        | E9Dh  | B1D7 <sup>(5)</sup>        | E6Dh  | RXF15SIDL <sup>(5)</sup> |       |                         |

| F2Dh  | TXB0D7 <sup>(5)</sup>      | EFCh  | RXM1SIDH <sup>(5)</sup>    | ECCh  | B4D6 <sup>(5)</sup>        | E9Ch  | B1D6 <sup>(5)</sup>        |       | RXF15SIDH(5)             |       |                         |

| F2Ch  | TXB0D6 <sup>(5)</sup>      | EFBh  | RXM0EIDL <sup>(5)</sup>    | ECBh  | B4D5 <sup>(5)</sup>        | E9Bh  | B1D5 <sup>(5)</sup>        |       | RXF14EIDL <sup>(5)</sup> |       |                         |

| F2Bh  | TXB0D5 <sup>(5)</sup>      | EFAh  | RXM0EIDH <sup>(5)</sup>    | ECAh  | B4D4 <sup>(5)</sup>        | E9Ah  | B1D4 <sup>(5)</sup>        | E6Ah  | RXF14EIDH <sup>(5)</sup> |       |                         |

| F2Ah  | TXB0D4 <sup>(5)</sup>      | EF9h  | RXM0SIDL <sup>(5)</sup>    | EC9h  | B4D3 <sup>(5)</sup>        | E99h  | B1D3 <sup>(5)</sup>        | E69h  | RXF14SIDL <sup>(5)</sup> |       |                         |

| F29h  | TXB0D3 <sup>(5)</sup>      | EF8h  | RXM0SIDH <sup>(5)</sup>    | EC8h  | B4D2 <sup>(5)</sup>        | E98h  | B1D2 <sup>(5)</sup>        | E68h  | RXF14SIDH(5)             |       |                         |

| F28h  | TXB0D2 <sup>(5)</sup>      | EF7h  | RXF5EIDL <sup>(5)</sup>    | EC7h  | B4D1 <sup>(5)</sup>        | E97h  | B1D1 <sup>(5)</sup>        | E67h  | RXF13EIDL <sup>(5)</sup> |       |                         |

| F27h  | TXB0D1 <sup>(5)</sup>      | EF6h  | RXF5EIDH <sup>(5)</sup>    | EC6h  | B4D0 <sup>(5)</sup>        | E96h  | B1D0 <sup>(5)</sup>        | E66h  | RXF13EIDH <sup>(5)</sup> |       |                         |

| F26h  | TXB0D0 <sup>(5)</sup>      | EF5h  | RXF5SIDL <sup>(5)</sup>    | EC5h  | B4DLC <sup>(5)</sup>       | E95h  | B1DLC <sup>(5)</sup>       | E65h  | RXF13SIDL <sup>(5)</sup> |       |                         |

| F25h  | TXB0DLC <sup>(5)</sup>     | EF4h  | RXF5SIDH <sup>(5)</sup>    | EC4h  | B4EIDL <sup>(5)</sup>      | E94h  | B1EIDL <sup>(5)</sup>      |       | RXF13SIDH(5)             |       |                         |

| F24h  | TXB0EIDL <sup>(5)</sup>    | EF3h  | RXF4EIDL <sup>(5)</sup>    | EC3h  | B4EIDH <sup>(5)</sup>      | E93h  |                            |       | RXF12EIDL <sup>(5)</sup> |       |                         |

| F23h  | TXB0EIDH <sup>(5)</sup>    | EF2h  | RXF4EIDH <sup>(5)</sup>    | EC2h  | B4SIDL <sup>(5)</sup>      | E92h  | B1SIDL <sup>(5)</sup>      |       | RXF12EIDH <sup>(5)</sup> |       |                         |

| F22h  | TXB0SIDL <sup>(5)</sup>    | EF1h  | RXF4SIDL <sup>(5)</sup>    | EC1h  | B4SIDH <sup>(5)</sup>      | E91h  | B1SIDH <sup>(5)</sup>      |       | RXF12SIDL <sup>(5)</sup> |       |                         |

| F21h  | TXB0SIDH <sup>(5)</sup>    | EF0h  | RXF4SIDH <sup>(5)</sup>    | EC0h  | B4CON <sup>(5)</sup>       | E90h  | B1CON <sup>(5)</sup>       |       | RXF12SIDH <sup>(5)</sup> |       |                         |

| F20h  | TXB0CON <sup>(5)</sup>     | EEFh  | RXF3EIDL <sup>(5)</sup>    |       | CANCON_RO6 <sup>(5)</sup>  | E90h  |                            |       | RXF11EIDL <sup>(5)</sup> |       |                         |

|       | CANCON_RO2 <sup>(5)</sup>  | EEEh  | RXF3EIDH <sup>(5)</sup>    | EBEh  | CANSTAT_RO6 <sup>(5)</sup> |       | CANCON_RO9 <sup>(5)</sup>  |       | RXF11EIDH <sup>(5)</sup> |       |                         |

| F1Eh  | CANSTAT_RO2 <sup>(5)</sup> | EEDh  | RXF3SIDL <sup>(5)</sup>    | EBDh  | B3D7 <sup>(5)</sup>        | E8Eh  | CANSTAT_RO9 <sup>(5)</sup> |       | RXF11SIDL <sup>(5)</sup> |       |                         |

| F1Dh  | TXB1D7 <sup>(5)</sup>      | EECh  | RXF3SIDH <sup>(5)</sup>    | EBCh  | B3D6 <sup>(5)</sup>        | E8Dh  |                            |       | RXF11SIDH <sup>(5)</sup> |       |                         |

| F1Ch  |                            | EEBh  | RXF2EIDL <sup>(5)</sup>    | EBBh  |                            | E8Ch  |                            |       | RXF10EIDL <sup>(5)</sup> |       |                         |

| F1Bh  |                            | EEAh  |                            | EBAh  |                            | E8Bh  |                            |       | RXF10EIDH <sup>(5)</sup> |       |                         |

| F1Ah  | TXB1D4 <sup>(5)</sup>      | EE9h  | RXF2SIDL <sup>(5)</sup>    | EB9h  | B3D3 <sup>(5)</sup>        | E8Ah  |                            |       | RXF10SIDL <sup>(5)</sup> |       |                         |

| F19h  | TXB1D3 <sup>(5)</sup>      | EE8h  | RXF2SIDH <sup>(5)</sup>    | EB8h  |                            | E89h  |                            |       | RXF10SIDH(5)             |       |                         |

| F18h  | TXB1D2 <sup>(5)</sup>      | EE7h  | RXF1EIDL <sup>(5)</sup>    | EB7h  | B3D1 <sup>(5)</sup>        | E88h  |                            |       | RXF9EIDL <sup>(5)</sup>  |       |                         |

| F17h  | TXB1D1 <sup>(5)</sup>      | EE6h  | RXF1EIDH <sup>(5)</sup>    | EB6h  | B3D0 <sup>(5)</sup>        | E87h  |                            | E56h  | RXF9EIDH <sup>(5)</sup>  |       |                         |

| F16h  | TXB1D0 <sup>(5)</sup>      | EE5h  | RXF1SIDL <sup>(5)</sup>    | EB5h  | B3DLC <sup>(5)</sup>       | E86h  |                            | E55h  |                          |       |                         |

| F15h  | TXB1DLC <sup>(5)</sup>     | EE4h  | RXF1SIDH <sup>(5)</sup>    | EB4h  | -                          | E85h  |                            |       | RXF9SIDH <sup>(5)</sup>  |       |                         |

| F14h  | TXB1EIDL <sup>(5)</sup>    | EE3h  | RXF0EIDL <sup>(5)</sup>    | EB3h  |                            | E84h  |                            |       | RXF8EIDL <sup>(5)</sup>  |       |                         |

| F13h  | TXB1EIDH <sup>(5)</sup>    | EE2h  | RXF0EIDH <sup>(5)</sup>    | EB2h  | B3SIDL <sup>(5)</sup>      | E83h  |                            | E52h  | RXF8EIDH <sup>(5)</sup>  |       |                         |

| F12h  | TXB1SIDL <sup>(5)</sup>    | EE1h  | RXF0SIDL <sup>(5)</sup>    | EB1h  |                            | E82h  |                            | E51h  |                          |       |                         |

| F11h  | TXB1SIDH <sup>(5)</sup>    | EE0h  | RXF0SIDH <sup>(5)</sup>    | EB0h  | B3CON <sup>(5)</sup>       | E81h  |                            | E50h  | RXF8SIDH <sup>(5)</sup>  |       |                         |

| F10h  | TXB1CON <sup>(5)</sup>     |       |                            |       |                            | E80h  | B0CON <sup>(5)</sup>       |       |                          |       |                         |

#### **TABLE 6-1:** SPECIAL FUNCTION REGISTER MAP FOR PIC18F66K80 FAMILY (CONTINUED)

Note 1:

2:

This is not a physical register. Unimplemented registers are read as '0'. This register is only available on devices with 64 pins. 3:

4: This register is not available on devices with 28 pins.

Addresses, E41h through F5Fh, are also used by the SFRs, but are not part of the Access RAM. To access these registers, users must 5: always load the proper BSR value.

## 8.6 Operation During Code-Protect

Data EEPROM memory has its own code-protect bits in Configuration Words. External read and write operations are disabled if code protection is enabled.

The microcontroller itself can both read and write to the internal data EEPROM regardless of the state of the code-protect Configuration bit. Refer to **Section 28.0 "Special Features of the CPU"** for additional information.

## 8.7 Protection Against Spurious Write

There are conditions when the device may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been implemented. On power-up, the WREN bit is cleared. In addition, writes to the EEPROM are blocked during the Power-up Timer period (TPWRT, Parameter 33).

The write initiate sequence, and the WREN bit together, help prevent an accidental write during brown-out, power glitch or software malfunction.

## 8.8 Using the Data EEPROM

The data EEPROM is a high-endurance, byteaddressable array that has been optimized for the storage of frequently changing information (e.g., program variables or other data that are updated often). Frequently changing values will typically be updated more often than Parameter D124. If this is not the case, an array refresh must be performed. For this reason, variables that change infrequently (such as constants, IDs, calibration, etc.) should be stored in Flash program memory.

A simple data EEPROM refresh routine is shown in Example 8-3.

Note: If data EEPROM is only used to store constants and/or data that changes often, an array refresh is likely not required. See Parameter D124.

EXAMPLE 8-3: DATA EEPROM REFRESH ROUTINE

|      | CLRF   | EEADR         | ; Start at address 0         |

|------|--------|---------------|------------------------------|

|      | CLRF   | EEADRH        | 7                            |

|      | BCF    | EECON1, CFGS  | ; Set for memory             |

|      | BCF    | EECON1, EEPGD | ; Set for Data EEPROM        |

|      | BCF    | INTCON, GIE   | ; Disable interrupts         |

|      | BSF    | EECON1, WREN  | ; Enable writes              |

| LOOP |        |               | ; Loop to refresh array      |

|      | BSF    | EECON1, RD    | ; Read current address       |

|      | MOVLW  | 55h           | ;                            |

|      | MOVWF  | EECON2        | ; Write 55h                  |

|      | MOVLW  | 0AAh          | i                            |

|      | MOVWF  | EECON2        | ; Write OAAh                 |

|      | BSF    | EECON1, WR    | ; Set WR bit to begin write  |

|      | BTFSC  | EECON1, WR    | ; Wait for write to complete |

|      | BRA    | \$-2          |                              |

|      | INCFSZ | EEADR, F      | ; Increment address          |

|      | BRA    | LOOP          | ; Not zero, do it again      |

|      | INCFSZ | EEADRH, F     | ; Increment the high address |

|      | BRA    | LOOP          | ; Not zero, do it again      |

|      | BCF    | EECON1, WREN  | ; Disable writes             |

|      | BSF    | INTCON, GIE   | ; Enable interrupts          |

| 1    |        |               |                              |

## **10.0 INTERRUPTS**

Members of the PIC18F66K80 family of devices have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a high-priority level or a low-priority level. The high-priority interrupt vector is at 0008h and the low-priority interrupt vector is at 0018h. High-priority interrupt events will interrupt any low-priority interrupts that may be in progress.

The registers for controlling interrupt operation are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2, PIR3, PIR4 and PIR5

- PIE1, PIE2, PIE3, PIE4 and PIE5

- IPR1, IPR2, IPR3, IPR4 and IPR5

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit Indicating that an interrupt event occurred

- Enable bit Enabling program execution to branch to the interrupt vector address when the flag bit is set

- **Priority bit** Specifying high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits that enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate Global Interrupt Enable bit are set, the interrupt will vector immediately to address 0008h or 0018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit that enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit that enables/disables all interrupt sources. All interrupts branch to address 0008h in Compatibility mode.

When an interrupt is responded to, the Global Interrupt Enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a low-priority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine (ISR), the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used) that re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding enable bit or the GIE bit.

**Note:** Do not use the MOVFF instruction to modify any of the Interrupt Control registers while **any** interrupt is enabled. Doing so may cause erratic microcontroller behavior.

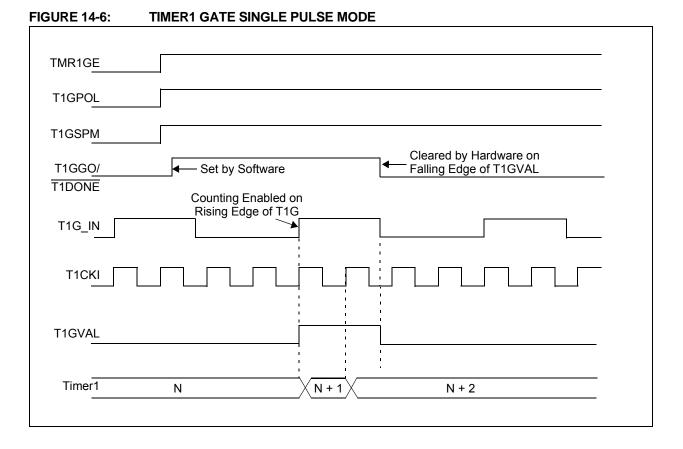

## 14.8.4 TIMER1 GATE SINGLE PULSE MODE

When Timer1 Gate Single Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single Pulse mode is enabled by setting the T1GSPM bit (T1GCON<4>) and the T1GGO/T1DONE bit (T1GCON<3>). The Timer1 will be fully enabled on the next incrementing edge.

On the next trailing edge of the pulse, the T1GGO/ T1DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/T1DONE bit is once again set in software. Clearing the T1GSPM <u>bit of the</u> T1GCON register will also clear the T1GGO/T1DONE bit. (For timing details, see Figure 14-6.)

Simultaneously enabling the Toggle and Single Pulse modes will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. (For timing details, see Figure 14-7.)

## 14.8.5 TIMER1 GATE VALUE STATUS

When the Timer1 gate value status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit (T1GCON<2>). This bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

### © 2010-2012 Microchip Technology Inc.

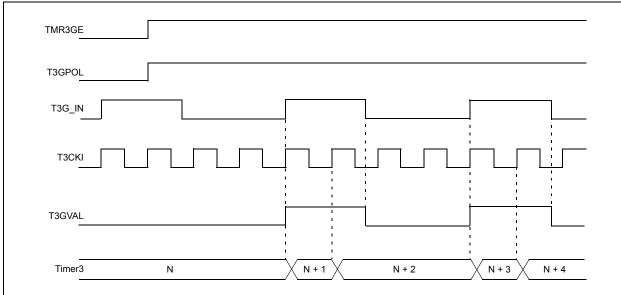

## 16.5 Timer3 Gates

Timer3 can be configured to count freely or the count can be enabled and disabled using the Timer3 gate circuitry. This is also referred to as the Timer3 gate count enable.

The Timer3 gate can also be driven by multiple selectable sources.

## 16.5.1 TIMER3 GATE COUNT ENABLE

The Timer3 Gate Enable mode is enabled by setting the TMR3GE bit (TxGCON<7>). The polarity of the Timer3 Gate Enable mode is configured using the T3GPOL bit (T3GCON<6>).

When Timer3 Gate Enable mode is enabled, Timer3 will increment on the rising edge of the Timer3 clock source. When Timer3 Gate Enable mode is disabled, no incrementing will occur and Timer3 will hold the current count. See Figure 16-2 for timing details.

## TABLE 16-1: TIMER3 GATE ENABLE SELECTIONS

| T3CLK <sup>(†)</sup> | T3GPOL<br>(T3GCON<6>) | T3G Pin | Timer3<br>Operation |  |

|----------------------|-----------------------|---------|---------------------|--|

| 1                    | 0                     | 0       | Counts              |  |

| $\uparrow$           | 0                     | 1       | Holds Count         |  |

| $\uparrow$           | 1                     | 0       | Holds Count         |  |

| $\uparrow$           | 1                     | 1       | Counts              |  |

† The clock on which TMR3 is running. For more information, see T3CLK in Figure 16-1.

## FIGURE 16-2: TIMER3 GATE COUNT ENABLE MODE

## 16.6 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and overflows to 0000h. The Timer3 interrupt, if enabled, is generated on overflow and is latched in the interrupt flag bit, TMR3IF. Table 16-3 gives each module's flag bit.

This interrupt can be enabled or disabled by setting or clearing the TMR3IE bit. Table 16-3 displays each module's enable bit.

## 16.7 Resetting Timer3 Using the ECCP Special Event Trigger

If the ECCP modules are configured to use Timer3 and to generate a Special Event Trigger in Compare mode (CCP3M<3:0> = 1011), this signal will reset Timer3. The trigger from ECCP will also start an A/D conversion if the A/D module is enabled (For more information, see **Section 20.3.4 "Special Event Trigger"**.) The module must be configured as either a timer or synchronous counter to take advantage of this feature. When used this way, the CCPR3H:CCPR3L register pair effectively becomes a Period register for Timer3.

If Timer3 is running in Asynchronous Counter mode, the Reset operation may not work.

In the event that a write to Timer3 coincides with a Special Event Trigger from an ECCP module, the write will take precedence.

- **Note:** The Special Event Triggers from the ECCPx module will only clear the TMR3 register's content, but not set the TMR3IF interrupt flag bit (PIR2<1>).

- Note: The CCP and ECCP modules use Timers, 1 through 4, for some modes. The assignment of a particular timer to a CCP/ECCP module is determined by the Timer to CCP enable bits in the CCPTMRS register. For more details, see Register 20-2 and Register 19-2.

| Name    | Bit 7       | Bit 6          | Bit 5   | Bit 4   | Bit 3            | Bit 2  | Bit 1  | Bit 0   |

|---------|-------------|----------------|---------|---------|------------------|--------|--------|---------|

| INTCON  | GIE/GIEH    | PEIE/GIEL      | TMR0IE  | INT0IE  | RBIE             | TMR0IF | INT0IF | RBIF    |

| PIR5    | IRXIF       | WAKIF          | ERRIF   | TXB2IF  | TXB1IF           | TXB0IF | RXB1IF | RXB0IF  |

| PIE5    | IRXIE       | WAKIE          | ERRIE   | TX2BIE  | TXB1IE           | TXB0IE | RXB1IE | RXB0IE  |

| PIR2    | OSCFIF      |                |         |         | BCLIF            | HLVDIF | TMR3IF | TMR3GIF |

| PIE2    | OSCFIE      | _              | _       | _       | BCLIE            | HLVDIE | TMR3IE | TMR3GIE |

| TMR3H   | Timer3 Regi | ster High Byte | 9       |         |                  |        |        |         |

| TMR3L   | Timer3 Regi | ster Low Byte  | •       |         |                  |        |        |         |

| T3GCON  | TMR3GE      | T3GPOL         | T3GTM   | T3GSPM  | T3GGO/<br>T3DONE | T3GVAL | T3GSS1 | T3GSS0  |

| T3CON   | TMR3CS1     | TMR3CS0        | T3CKPS1 | T3CKPS0 | SOSCEN           | T3SYNC | RD16   | TMR3ON  |

| OSCCON2 | —           | SOSCRUN        | _       | SOSCDRV | SOSCGO           | _      | MFIOFS | MFIOSEL |

| PMD1    | PSPMD       | CTMUMD         | ADCMD   | TMR4MD  | TMR3MD           | TMR2MD | TMR1MD | TMR0MD  |

## TABLE 16-3: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer3 module.

## 21.3.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register 1 (SSPCON1)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON1 and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON1 register is readable and writable. The lower 6 bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write.

SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together, create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not double-buffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

## REGISTER 21-1: SSPSTAT: MSSP STATUS REGISTER (SPI MODE)

| -             |                                          |                                      |                  | <b>\</b> -        | ,                          |                 |             |  |  |  |

|---------------|------------------------------------------|--------------------------------------|------------------|-------------------|----------------------------|-----------------|-------------|--|--|--|

| R/W-0         | R/W-0                                    | R-0                                  | R-0              | R-0               | R-0                        | R-0             | R-0         |  |  |  |

| SMP           | CKE <sup>(1)</sup>                       | D/A                                  | Р                | S                 | R/W                        | UA              | BF          |  |  |  |

| bit 7         | •                                        |                                      |                  |                   |                            |                 | bit         |  |  |  |

|               |                                          |                                      |                  |                   |                            |                 |             |  |  |  |

| Legend:       |                                          |                                      |                  |                   |                            |                 |             |  |  |  |

| R = Readabl   | e bit                                    | W = Writable                         | bit              | U = Unimpler      | nented bit, rea            | d as '0'        |             |  |  |  |

| -n = Value at | POR                                      | '1' = Bit is set                     |                  | '0' = Bit is cle  | ared                       | x = Bit is unkn | nown        |  |  |  |

|               |                                          |                                      |                  |                   |                            |                 |             |  |  |  |

| bit 7         | SMP: Samp                                | le bit                               |                  |                   |                            |                 |             |  |  |  |

|               | SPI Master I                             |                                      |                  |                   |                            |                 |             |  |  |  |

|               |                                          | ta is sampled at<br>ta is sampled at |                  |                   | 2                          |                 |             |  |  |  |

|               | <u>SPI Slave m</u>                       | •                                    |                  |                   |                            |                 |             |  |  |  |

|               |                                          | e cleared when                       | SPI is used ir   | n Slave mode.     |                            |                 |             |  |  |  |

| bit 6         | CKE: SPI Clock Select bit <sup>(1)</sup> |                                      |                  |                   |                            |                 |             |  |  |  |

|               |                                          | t occurs on trans                    |                  |                   |                            |                 |             |  |  |  |

|               |                                          | t occurs on trans                    | sition from Idle | e to active clock | state                      |                 |             |  |  |  |

| bit 5         | D/A: Data/A                              |                                      |                  |                   |                            |                 |             |  |  |  |

|               |                                          | ™ mode only.                         |                  |                   |                            |                 |             |  |  |  |

| bit 4         | P: Stop bit                              |                                      |                  |                   |                            |                 |             |  |  |  |

|               |                                          | mode only. This                      | bit is cleared   | when the MSSF     | <sup>o</sup> module is dis | abled; SSPEN i  | is cleared. |  |  |  |

| bit 3         | <b>S:</b> Start bit                      | manala amb i                         |                  |                   |                            |                 |             |  |  |  |

| h:: 0         | Used in I <sup>2</sup> C                 |                                      | . 1. 14          |                   |                            |                 |             |  |  |  |

| bit 2         | Used in I <sup>2</sup> C                 | Write Information                    | 1 DIT            |                   |                            |                 |             |  |  |  |

| bit 1         | USed In T C<br>UA: Update                | ,                                    |                  |                   |                            |                 |             |  |  |  |

| DILI          | Used in I <sup>2</sup> C                 |                                      |                  |                   |                            |                 |             |  |  |  |

| bit 0         |                                          | fill Status bit (Re                  | ceive mode (     | only)             |                            |                 |             |  |  |  |

|               |                                          | is complete, SS                      |                  | Jiliy)            |                            |                 |             |  |  |  |

|               |                                          | is not complete,                     |                  | empty             |                            |                 |             |  |  |  |

|               |                                          |                                      |                  |                   |                            |                 |             |  |  |  |

| NOTE 1: PO    | Diarity of Clock                         | state is set by th                   | 18 CKP bit (S    | 5PCUN1<4>).       |                            |                 |             |  |  |  |

Note 1: Polarity of clock state is set by the CKP bit (SSPCON1<4>).

#### 21.3.4 **ENABLING SPI I/O**

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON1<5>), must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, reinitialize the SSPCON registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- · SDI is automatically controlled by the SPI module

- SDO must have the TRISC<5> bit cleared

- SCK (Master mode) must have the TRISC<3> bit cleared

- SCK (Slave mode) must have the TRISC<3> bit set

- SS must have the TRISA<5> bit set

Any serial port function that is not desired may be overridden by programming the corresponding Data Direction (TRIS) register to the opposite value.

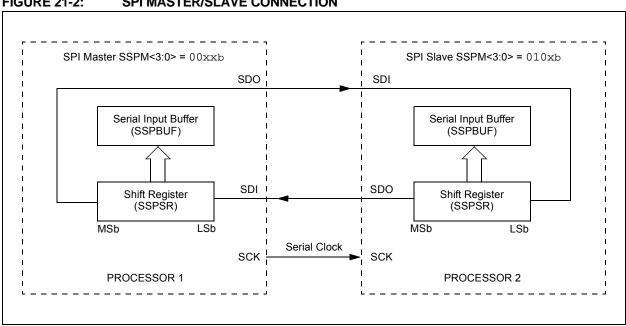

### 21.3.5 TYPICAL CONNECTION

Figure 21-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- · Master sends data Slave sends dummy data

- Master sends data Slave sends data

- · Master sends dummy data Slave sends data

#### **FIGURE 21-2:** SPI MASTER/SLAVE CONNECTION

## 21.4.2 OPERATION

The MSSP module functions are enabled by setting the MSSP Enable bit, SSPEN (SSPCON1<5>).

The SSPCON1 register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON1<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Master mode, clock

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Firmware Controlled Master mode, slave is Idle

Selection of any I<sup>2</sup>C mode with the SSPEN bit set forces the SCL and SDA pins to be open-drain, provided these pins are programmed as inputs by setting the appropriate TRISC bit. To ensure proper operation of the module, pull-up resistors must be provided externally to the SCL and SDA pins.

### 21.4.3 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The MSSP module will override the input state with the output data when required (slave-transmitter).

The  $I^2C$  Slave mode hardware will always generate an interrupt on an address match. Address masking will allow the hardware to generate an interrupt for more than one address (up to 31 in 7-bit addressing and up to 63 in 10-bit addressing). Through the mode select bits, the user can also choose to interrupt on Start and Stop bits.

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overrightarrow{ACK}$ ) pulse and load the SSPBUF register with the received value currently in the SSPSR register.

Any combination of the following conditions will cause the MSSP module not to give this ACK pulse:

- The Buffer Full bit, BF (SSPSTAT<0>), was set before the transfer was received.

- The overflow bit, SSPOV (SSPCON1<6>), was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit, SSPIF, is set. The BF bit is cleared by reading the SSPBUF register, while bit, SSPOV, is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, are shown in timing Parameter 100 and Parameter 101.

## 21.4.3.1 Addressing

Once the MSSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8 bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register, SSPSR<7:1>, is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- 1. The SSPSR register value is loaded into the SSPBUF register.

- 2. The Buffer Full bit, BF, is set.

- 3. An ACK pulse is generated.

- 4. The MSSP Interrupt Flag bit, SSPIF, is set (and interrupt is generated, if enabled) on the falling edge of the ninth SCL pulse.

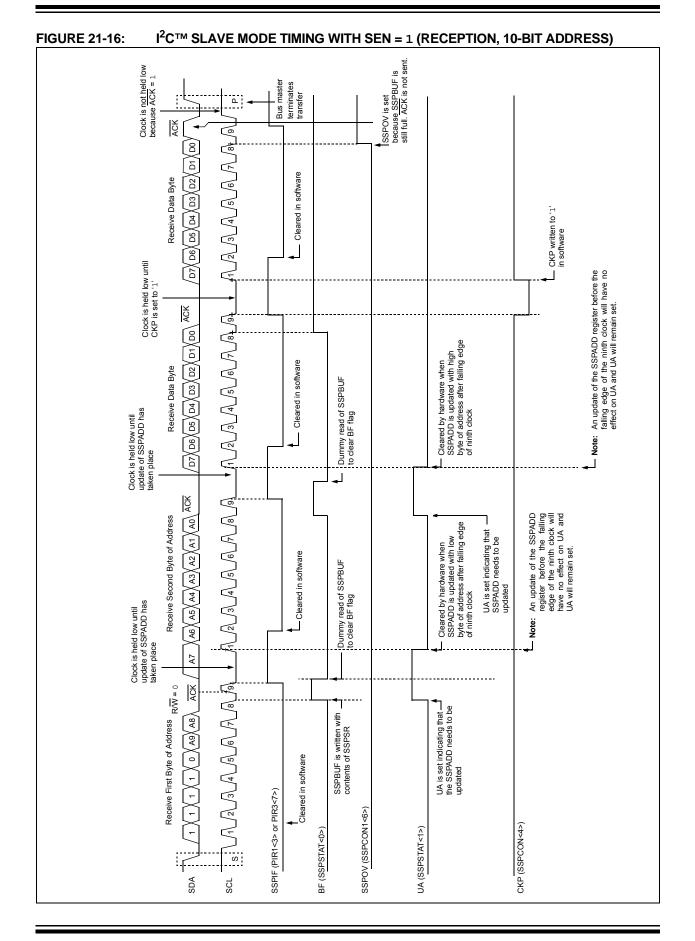

In 10-Bit Addressing mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. The  $R/\overline{W}$  (SSPSTAT<2>) bit must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '11110 A9 A8 0', where 'A9' and 'A8' are the two MSbs of the address. The sequence of events for 10-bit addressing is as follows, with Steps 7 through 9 for the slave-transmitter:

- 1. Receive first (high) byte of address (bits, SSPIF, BF and UA, are set on address match).

- 2. Update the SSPADD register with second (low) byte of address (clears bit, UA, and releases the SCL line).

- 3. Read the SSPBUF register (clears bit, BF) and clear flag bit, SSPIF.

- 4. Receive second (low) byte of address (bits, SSPIF, BF and UA, are set).

- 5. Update the SSPADD register with the first (high) byte of address. If match releases SCL line, this will clear bit, UA.

- 6. Read the SSPBUF register (clears bit, BF) and clear flag bit SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (bits, SSPIF and BF, are set).

- 9. Read the SSPBUF register (clears bit, BF) and clear flag bit, SSPIF.

| REGISTERS ASSOCIATED WITH STNCHRONOUS MASTER RECEPTION |                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit 7                                                  | Bit 6                                                                                                                                                                                                 | Bit 5                                                                                                                                                                                                                                                                                                                                                       | Bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| GIE/GIEH                                               | PEIE/GIEL                                                                                                                                                                                             | TMR0IE                                                                                                                                                                                                                                                                                                                                                      | INT0IE                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RBIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TMR0IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>INT0IF</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RBIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| PSPIF                                                  | ADIF                                                                                                                                                                                                  | RC1IF                                                                                                                                                                                                                                                                                                                                                       | TX1IF                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SSPIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TMR1GIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TMR2IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TMR1IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| PSPIE                                                  | ADIE                                                                                                                                                                                                  | RC1IE                                                                                                                                                                                                                                                                                                                                                       | TX1IE                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SSPIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TMR1GIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TMR2IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TMR1IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| PSPIP                                                  | ADIP                                                                                                                                                                                                  | RC1IP                                                                                                                                                                                                                                                                                                                                                       | TX1IP                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SSPIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TMR1GIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TMR2IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TMR1IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |