Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

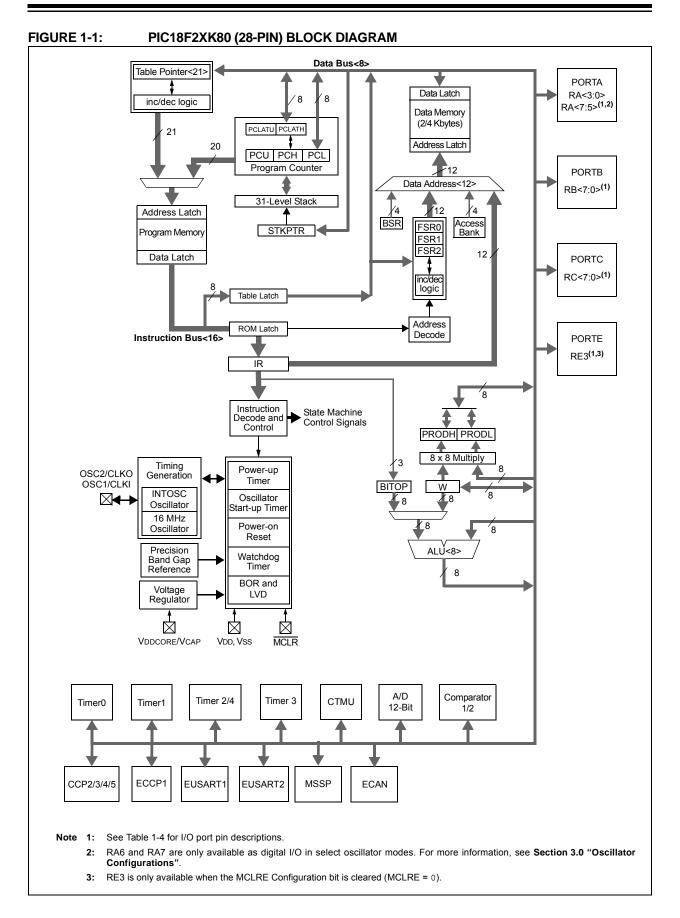

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | ECANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 8x12b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f25k80-e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.2 Power Supply Pins

## 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

## 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ .

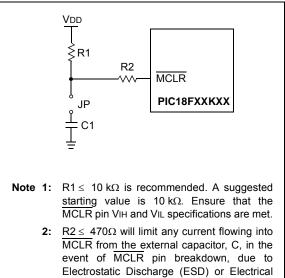

# 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: Device Reset, and Device Programming and Debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

## FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

Overstress (EOS). Ensure that the MCLR pin

VIH and VIL specifications are met.

| TABLE 5-4: | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |                 |             |                                          |                                                                  |                                    |  |  |  |  |  |

|------------|---------------------------------------------------------|-----------------|-------------|------------------------------------------|------------------------------------------------------------------|------------------------------------|--|--|--|--|--|

| Register   | A                                                       | pplicable Devic | es          | Power-on<br>Reset,<br>Brown-out<br>Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via<br>WDT<br>or Interrupt |  |  |  |  |  |

| RXF12SIDH  | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |  |  |  |

| RXF11EIDL  | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |  |  |  |

| RXF11EIDH  | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |  |  |  |

| RXF11SIDL  | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxx- x-xx                                | uuu- u-uu                                                        | uuu- u-uu                          |  |  |  |  |  |

| RXF11SIDH  | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |  |  |  |

| RXF10EIDL  | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |  |  |  |

| RXF10EIDH  | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |  |  |  |

| RXF10SIDL  | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxx- x-xx                                | uuu- u-uu                                                        | uuu- u-uu                          |  |  |  |  |  |

| RXF10SIDH  | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |  |  |  |

| RXF9EIDL   | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |  |  |  |

| RXF9EIDH   | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |  |  |  |

| RXF9SIDL   | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxx- x-xx                                | uuu- u-uu                                                        | uuu- u-uu                          |  |  |  |  |  |

| RXF9SIDH   | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |  |  |  |

| RXF8EIDL   | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |  |  |  |

| RXF8EIDH   | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |  |  |  |

| RXF8SIDL   | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxx- x-xx                                | uuu- u-uu                                                        | uuu- u-uu                          |  |  |  |  |  |

| RXF8SIDH   | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |  |  |  |

| RXF7EIDL   | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |  |  |  |

| RXF7EIDH   | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |  |  |  |

| RXF7SIDL   | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxx- x-xx                                | uuu- u-uu                                                        | uuu- u-uu                          |  |  |  |  |  |

| RXF7SIDH   | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |  |  |  |

| RXF6EIDL   | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |  |  |  |

| RXF6EIDH   | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |  |  |  |

| RXF6SIDL   | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxx- x-xx                                | uuu- u-uu                                                        | uuu- u-uu                          |  |  |  |  |  |

| RXF6SIDH   | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |  |  |  |

| RXFCON0    | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | 0000 0000                                | 0000 0000                                                        | uuuu uuuu                          |  |  |  |  |  |

| RXFCON1    | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | 0000 0000                                | 0000 0000                                                        | uuuu uuuu                          |  |  |  |  |  |

| BRGCON3    | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | 00000                                    | 00000                                                            | uuuuu                              |  |  |  |  |  |

| BRGCON2    | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | 0000 0000                                | 0000 0000                                                        | uuuu uuuu                          |  |  |  |  |  |

| BRGCON1    | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | 0000 0000                                | 0000 0000                                                        | uuuu uuuu                          |  |  |  |  |  |

| TXERRCNT   | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | 0000 0000                                | 0000 0000                                                        | uuuu uuuu                          |  |  |  |  |  |

| RXERRCNT   | PIC18F2XK80                                             | PIC18F4XK80     | PIC18F6XK80 | 0000 0000                                | 0000 0000                                                        | uuuu uuuu                          |  |  |  |  |  |

## TABLE 5-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged; x = unknown; - = unimplemented bit, read as '0'; q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 5-3 for Reset value for specific conditions.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read as '0'.

# 10.3 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are six Peripheral Interrupt Enable registers (PIE1 through PIE6). When IPEN (RCON<7>) = 0, the PEIE bit must be set to enable any of these peripheral interrupts.

## REGISTER 10-9: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0  | R/W-0  |

|-------|-------|-------|-------|-------|---------|--------|--------|

| PSPIE | ADIE  | RC1IE | TX1IE | SSPIE | TMR1GIE | TMR2IE | TMR1IE |

| bit 7 |       |       |       |       |         |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | <b>PSPIE:</b> Parallel Slave Port Read/Write Interrupt Enable bit<br>1 = Enables the PSP read/write interrupt<br>0 = Disables the PSP read/write interrupt |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | ADIE: A/D Converter Interrupt Enable bit<br>1 = Enables the A/D interrupt<br>0 = Disables the A/D interrupt                                                |

| bit 5 | <b>RC1IE:</b> EUSARTx Receive Interrupt Enable bit<br>1 = Enables the EUSARTx receive interrupt<br>0 = Disables the EUSARTx receive interrupt              |

| bit 4 | <b>TX1IE:</b> EUSARTx Transmit Interrupt Enable bit<br>1 = Enables the EUSARTx transmit interrupt<br>0 = Disables the EUSARTx transmit interrupt           |

| bit 3 | <b>SSPIE:</b> Master Synchronous Serial Port Interrupt Enable bit<br>1 = Enables the MSSP interrupt<br>0 = Disables the MSSP interrupt                     |

| bit 2 | <b>TMR1GIE:</b> TMR1 Gate Interrupt Enable bit<br>1 = Enables the gate<br>0 = Disabled the gate                                                            |

| bit 1 | <b>TMR2IE:</b> TMR2 to PR2 Match Interrupt Enable bit<br>1 = Enables the TMR2 to PR2 match interrupt<br>0 = Disables the TMR2 to PR2 match interrupt       |

| bit 0 | <b>TMR1IE:</b> TMR1 Overflow Interrupt Enable bit<br>1 = Enables the TMR1 overflow interrupt<br>0 = Disables the TMR1 overflow interrupt                   |

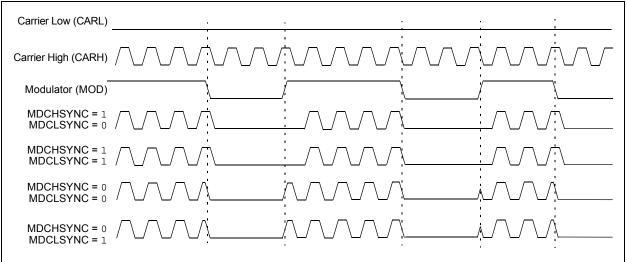

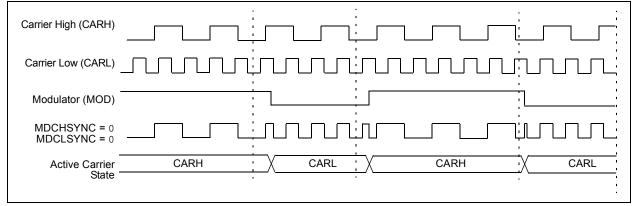

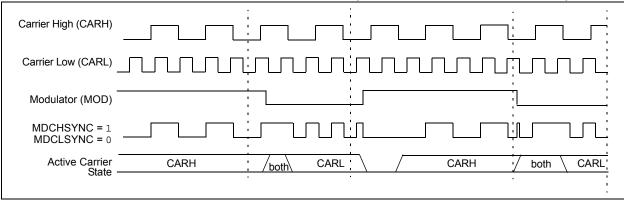

## EXAMPLE 12-1: NO SYNCHRONIZATION (MDCHSYNC = 0, MDCLSYNC = 0)

## FIGURE 12-3: CARRIER HIGH SYNCHRONIZATION (MDCHSYNC = 1, MDCLSYNC = 0)

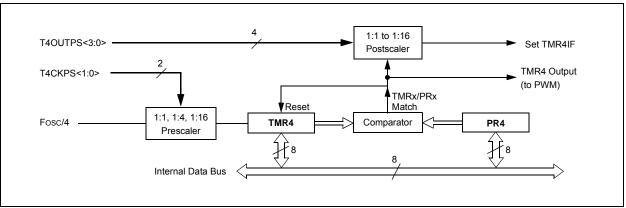

## 17.2 Timer4 Interrupt

The Timer4 module has an eight-bit Period register, PR4, that is both readable and writable. Timer4 increment from 00h until it matches PR4 and then resets to 00h on the next increment cycle. The PR4 register is initialized to FFh upon Reset.

17.3

**Output of TMR4**

as is the Timer2 output.

The outputs of TMR4 (before the postscaler) are used

only as a PWM time base for the ECCP modules. They

are not used as baud rate clocks for the MSSP module

### FIGURE 17-1: TIMER4 BLOCK DIAGRAM

### TABLE 17-1: REGISTERS ASSOCIATED WITH TIMER4 AS A TIMER/COUNTER

| Name   | Bit 7                  | Bit 6     | Bit 5    | Bit 4    | Bit 3    | Bit 2  | Bit 1   | Bit 0   |  |  |  |

|--------|------------------------|-----------|----------|----------|----------|--------|---------|---------|--|--|--|

| INTCON | GIE/GIEH               | PEIE/GIEL | TMR0IE   | INT0IE   | RBIE     | TMR0IF | INT0IF  | RBIF    |  |  |  |

| IPR4   | TMR4IP                 | EEIP      | CMP2IP   | CMP1IP   | —        | CCP5IP | CCP4IP  | CCP3IP  |  |  |  |

| PIR4   | TMR4IF                 | EEIF      | CMP2IF   | CMP1IF   | —        | CCP5IF | CCP4IF  | CCP3IF  |  |  |  |

| PIE4   | TMR4IE                 | EEIE      | CMP2IE   | CMP1IE   | —        | CCP5IE | CCP4IE  | CCP3IE  |  |  |  |

| TMR4   | Timer4 Register        |           |          |          |          |        |         |         |  |  |  |

| T4CON  | —                      | T4OUTPS3  | T4OUTPS2 | T4OUTPS1 | T4OUTPS0 | TMR40N | T4CKPS1 | T4CKPS0 |  |  |  |

| PR4    | Timer4 Period Register |           |          |          |          |        |         |         |  |  |  |

| PMD1   | PSPMD                  | CTMUMD    | ADCMD    | TMR4MD   | TMR3MD   | TMR2MD | TMR1MD  | TMR0MD  |  |  |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer4 module.

| U-0           | U-0          | U-0                                | R/W-0    | R/W-0            | R/W-0           | R/W-0          | R/W-0  |  |  |  |  |  |

|---------------|--------------|------------------------------------|----------|------------------|-----------------|----------------|--------|--|--|--|--|--|

|               | —            | _                                  | C5TSEL   | C4TSEL           | C3TSEL          | C2TSEL         | C1TSEL |  |  |  |  |  |

| bit 7         |              |                                    |          |                  |                 |                | bit 0  |  |  |  |  |  |

|               |              |                                    |          |                  |                 |                |        |  |  |  |  |  |

| Legend:       |              |                                    |          |                  |                 |                |        |  |  |  |  |  |

| R = Readabl   | le bit       | W = Writable                       | bit      | U = Unimpler     | mented bit, rea | d as '0'       |        |  |  |  |  |  |

| -n = Value at | t POR        | '1' = Bit is set                   |          | '0' = Bit is cle | ared            | x = Bit is unk | nown   |  |  |  |  |  |

|               |              |                                    |          |                  |                 |                |        |  |  |  |  |  |

| bit 7-5       | Unimplemen   | ted: Read as '                     | 0'       |                  |                 |                |        |  |  |  |  |  |

| bit 4         | C5TSEL: CC   | P5 Timer Selec                     | tion bit |                  |                 |                |        |  |  |  |  |  |

|               | 0 = CCP5 is  | 0 = CCP5 is based off of TMR1/TMR2 |          |                  |                 |                |        |  |  |  |  |  |

|               | 1 = CCP5 is  | 1 = CCP5 is based off of TMR3/TMR4 |          |                  |                 |                |        |  |  |  |  |  |

| bit 3         | C4TSEL: CC   | P4 Timer Selec                     | tion bit |                  |                 |                |        |  |  |  |  |  |

|               |              | based off of TN                    |          |                  |                 |                |        |  |  |  |  |  |

|               |              | based off of TN                    |          |                  |                 |                |        |  |  |  |  |  |

| bit 2         | C3TSEL: CC   | P3 Timer Selec                     | tion bit |                  |                 |                |        |  |  |  |  |  |

|               |              | based off of TN                    |          |                  |                 |                |        |  |  |  |  |  |

|               | 1 = CCP3 is  | based off of TN                    | /R3/TMR4 |                  |                 |                |        |  |  |  |  |  |

| bit 1         | C2TSEL: CC   | P2 Timer Selec                     | tion bit |                  |                 |                |        |  |  |  |  |  |

|               |              | based off of TN                    |          |                  |                 |                |        |  |  |  |  |  |

|               | 1 = CCP2 is  | based off of TN                    | /R3/TMR4 |                  |                 |                |        |  |  |  |  |  |

| bit 0         |              | P1 Timer Selec                     |          |                  |                 |                |        |  |  |  |  |  |

|               |              | s based off of T                   |          |                  |                 |                |        |  |  |  |  |  |

|               | 1 = ECCP1 is | s based off of 1                   | MR3/TMR4 |                  |                 |                |        |  |  |  |  |  |

## REGISTER 19-2: CCPTMRS: CCP TIMER SELECT REGISTER

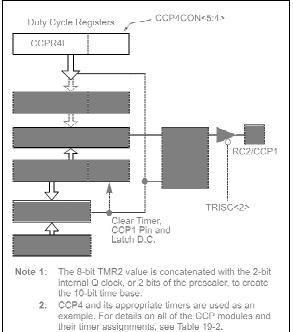

## 19.4 PWM Mode

In Pulse-Width Modulation (PWM) mode, the CCPx pin produces up to a 10-bit resolution PWM output. Since the CCPx pin is multiplexed with a PORTC or PORTB data latch, the appropriate TRIS bit must be cleared to make the CCPx pin an output.

| Note: | Clearing the CCPxCON register will force   |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|

|       | the corresponding CCPx output latch        |  |  |  |  |  |  |  |

|       | (depending on device configuration) to the |  |  |  |  |  |  |  |

|       | default low level. This is not the PORTx   |  |  |  |  |  |  |  |

|       | I/O data latch.                            |  |  |  |  |  |  |  |

Figure 19-3 shows a simplified block diagram of the CCPx module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 19.4.3** "Setup for PWM Operation".

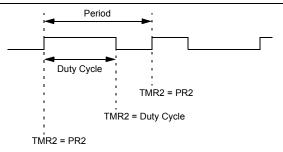

A PWM output (Figure 19-4) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

FIGURE 19-4: PWM OUTPUT

## 19.4.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

## **EQUATION 19-1:**

$PWM Period = [(PR2) + 1] \cdot 4 \cdot TOSC \cdot (TMR2 Prescale Value)$

PWM frequency is defined as 1/[PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP4 pin is set (An exception: If PWM duty cycle = 0%, the CCP4 pin will not be set)

- The PWM duty cycle is latched from CCPR4L into CCPR4H

| Note: | The     | Timer2      | postscalers        | (see     |

|-------|---------|-------------|--------------------|----------|

|       | Sectior | n 15.0 "Tin | ner2 Module") a    | are not  |

|       | used in | the deter   | mination of the    | PWM      |

|       | frequen | cy. The po  | stscaler could be  | e used   |

|       | to have | a servo up  | odate rate at a di | ifferent |

|       | frequen | cy than the | PWM output.        |          |

| ECCP Mode            | P1M<1:0> | P1A                | P1B                | P1C                | P1D                |

|----------------------|----------|--------------------|--------------------|--------------------|--------------------|

| Single               | 00       | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> |

| Half-Bridge          | 10       | Yes                | Yes                | No                 | No                 |

| Full-Bridge, Forward | 01       | Yes                | Yes                | Yes                | Yes                |

| Full-Bridge, Reverse | 11       | Yes                | Yes                | Yes                | Yes                |

#### **TABLE 20-2: EXAMPLE PIN ASSIGNMENTS FOR VARIOUS PWM ENHANCED MODES**

Note 1: Outputs are enabled by pulse steering in Single mode (see Register 20-5).

#### **FIGURE 20-4: EXAMPLE PWM (ENHANCED MODE) OUTPUT RELATIONSHIPS** (ACTIVE-HIGH STATE)

|    | P1M<1:0>        | Signal        | 0        | Pulse Width          | ►                    | PR2 + 1             |

|----|-----------------|---------------|----------|----------------------|----------------------|---------------------|

|    |                 |               | -<br>    | 4                    | Period               |                     |

| 00 | (Single Output) | P1A Modulated |          | Delay <sup>(1)</sup> | Delay <sup>(1)</sup> |                     |

|    |                 | P1A Modulated |          |                      |                      |                     |

| 10 | (Half-Bridge)   | P1B Modulated | ;        |                      |                      |                     |

|    |                 | P1A Active    | ;        |                      |                      | <u></u> і<br>і<br>і |

| 01 | (Full-Bridge,   | P1B Inactive  |          |                      | 1<br>1<br>1          | 1<br>1<br>1         |

| UT | Forward)        | P1C Inactive  | _ ;<br>; |                      | 1<br>1<br>1          | 1<br>               |

|    |                 | P1D Modulated | =ť       |                      | -                    |                     |

|    |                 | P1A Inactive  | ;        |                      | 1<br>1<br>1          | 1<br>1<br>1         |

| 11 | (Full-Bridge,   | P1B Modulated | =        |                      | -j                   | 1<br>1<br>1         |

|    | Reverse)        | P1C Active -  |          |                      |                      |                     |

|    |                 | P1D Inactive  | ;        |                      | 1<br>1               |                     |

Relationships:

Period = 4 \* Tosc \* (PR2 + 1) \* (TMR2 Prescale Value)

Pulse Width = Tosc \* (CCPR1L<7:0>:CCP1CON<5:4>) \* (TMR2 Prescale Value)

Delay = 4 \* Tosc \* (ECCP1DEL<6:0>)

Note 1: Dead-band delay is programmed using the ECCP1DEL register (Section 20.4.6 "Programmable Dead-Band Delay Mode").

#### ECCP1DEL: ENHANCED PWM CONTROL REGISTER REGISTER 20-4:

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| P1RSEN | P1DC6 | P1DC5 | P1DC4 | P1DC3 | P1DC2 | P1DC1 | P1DC0 |

| bit 7  |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7 P1RSEN: PWM Restart Enable bit

- 1 = Upon auto-shutdown, the ECCP1ASE bit clears automatically once the shutdown event goes away; the PWM restarts automatically

- 0 = Upon auto-shutdown, ECCP1ASE must be cleared by software to restart the PWM

bit 6-0

P1DC<6:0>: PWM Delay Count bits

P1DCn = Number of Fosc/4 (4 \* Tosc) cycles between the scheduled time when a PWM signal should transition active and the actual time it does transition active.

#### 20.4.7 PULSE STEERING MODE

In Single Output mode, pulse steering allows any of the PWM pins to be the modulated signal. Additionally, the same PWM signal can simultaneously be available on multiple pins.

Once the Single Output mode is selected (CCP1M<3:2> = 11 and P1M<1:0> = 00 of theCCP1CON register), the user firmware can bring out the same PWM signal to one, two, three or four output pins by setting the appropriate STR<D:A> bits (PSTR1CON<3:0>), as provided in Table 20-2.

Note: The associated TRIS bits must be set to output ('0') to enable the pin output driver in order to see the PWM signal on the pin.

While the PWM Steering mode is active, the CCP1M<1:0> bits (CCP1CON<1:0>) select the PWM output polarity for the P1<D:A> pins.

The PWM auto-shutdown operation also applies to the PWM Steering mode, as described in Section 20.4.4 "Enhanced PWM Auto-shutdown mode". An auto-shutdown event will only affect pins that have PWM outputs enabled.

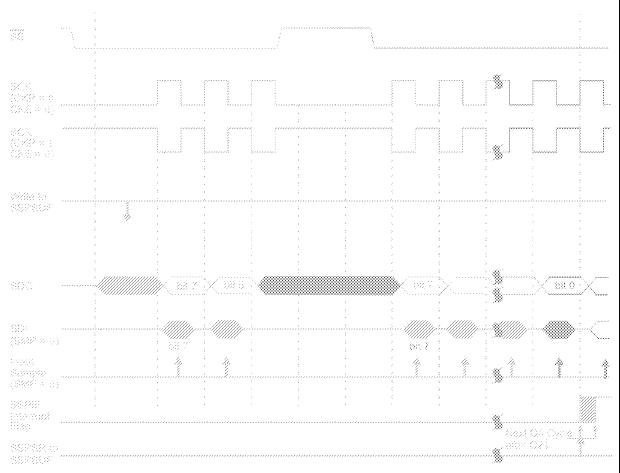

## 21.3.7 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device can be configured to wake-up from Sleep.

## 21.3.8 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with the  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 04h). When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a

transmitted byte, and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

- Note 1: When the SPI is in Slave mode, with  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 0100), the SPI module will reset if the  $\overline{SS}$  pin is set to VDD.

- 2: If the SPI is used in Slave mode, with CKE set, then the SS pin control must be enabled.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver, the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

## 22.5 EUSARTx Synchronous Slave Mode

Synchronous Slave mode is entered by clearing bit, CSRC (TXSTAx<7>). This mode differs from the Synchronous Master mode in that the shift clock is supplied externally at the CKx pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in any low-power mode.

### 22.5.1 EUSARTx SYNCHRONOUS SLAVE TRANSMISSION

The operation of the Synchronous Master and Slave modes is identical, except in the case of Sleep mode.

If two words are written to the TXREGx and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in the TXREGx register.

- c) Flag bit, TXxIF, will not be set.

- When the first word has been shifted out of TSR, the TXREGx register will transfer the second word to the TSR and flag bit, TXxIF, will now be set.

e) If enable bit, TXxIE, is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. Clear bits, CREN and SREN.

- 3. If interrupts are desired, set enable bit, TXxIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting enable bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREGx register.

- 8. If using interrupts, ensure that the GIE and PEIE bits (INTCON<7:6>) are set.

| Name     | Bit 7                                          | Bit 6         | Bit 5        | Bit 4         | Bit 3  | Bit 2   | Bit 1   | Bit 0  |

|----------|------------------------------------------------|---------------|--------------|---------------|--------|---------|---------|--------|

| INTCON   | GIE/GIEH                                       | PEIE/GIEL     | TMR0IE       | INT0IE        | RBIE   | TMR0IF  | INT0IF  | RBIF   |

| PIR1     | PSPIF                                          | ADIF          | RC1IF        | TX1IF         | SSPIF  | TMR1GIF | TMR2IF  | TMR1IF |

| PIE1     | PSPIE                                          | ADIE          | RC1IE        | TX1IE         | SSPIE  | TMR1GIE | TMR2IE  | TMR1IE |

| IPR1     | PSPIP                                          | ADIP          | RC1IP        | TX1IP         | SSPIP  | TMR1GIP | TMR2IP  | TMR1IP |

| PIR3     | —                                              | _             | RC2IF        | TX2IF         | CTMUIF | CCP2IF  | CCP1IF  | -      |

| PIE3     | —                                              | _             | RC2IE        | TX2IE         | CTMUIE | CCP2IE  | CCP1IE  | _      |

| IPR3     | —                                              | _             | RC2IP        | TX2IP         | CTMUIP | CCP2IP  | CCP1IP  | _      |

| RCSTA1   | SPEN                                           | RX9           | SREN         | CREN          | ADDEN  | FERR    | OERR    | RX9D   |

| TXREG1   | EUSART1 Transmit Register                      |               |              |               |        |         |         |        |

| TXSTA1   | CSRC                                           | TX9           | TXEN         | SYNC          | SENDB  | BRGH    | TRMT    | TX9D   |

| BAUDCON1 | ABDOVF                                         | RCIDL         | RXDTP        | TXCKP         | BRG16  | _       | WUE     | ABDEN  |

| SPBRGH1  | EUSART1 Baud Rate Generator Register High Byte |               |              |               |        |         |         |        |

| SPBRG1   | EUSART1 B                                      | aud Rate Ger  | nerator Regi | ster Low Byte | 9      |         |         |        |

| RCSTA2   | SPEN                                           | RX9           | SREN         | CREN          | ADDEN  | FERR    | OERR    | RX9D   |

| TXREG2   | EUSART2 T                                      | ransmit Regis | ster         |               |        |         |         |        |

| TXSTA2   | CSRC                                           | TX9           | TXEN         | SYNC          | SENDB  | BRGH    | TRMT    | TX9D   |

| BAUDCON2 | ABDOVF                                         | RCIDL         | RXDTP        | TXCKP         | BRG16  | _       | WUE     | ABDEN  |

| SPBRGH2  | EUSART2 Baud Rate Generator Register High Byte |               |              |               |        |         |         |        |

| SPBRG2   | EUSART2 Baud Rate Generator Register Low Byte  |               |              |               |        |         |         |        |

| PMD0     | CCP5MD                                         | CCP4MD        | CCP3MD       | CCP2MD        | CCP1MD | UART2MD | UART1MD | SSPMD  |

| ODCON    | SSPOD                                          | CCP5OD        | CCP4OD       | CCP3OD        | CCP2OD | CCP10D  | U2OD    | U10D   |

## TABLE 22-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

NOTES:

## 27.2 CAN Module Registers

Note: Not all CAN registers are available in the Access Bank.

There are many control and data registers associated with the CAN module. For convenience, their descriptions have been grouped into the following sections:

- Control and Status Registers

- Dedicated Transmit Buffer Registers

- Dedicated Receive Buffer Registers

- Programmable TX/RX and Auto RTR Buffers

- Baud Rate Control Registers

- I/O Control Register

- Interrupt Status and Control Registers

Detailed descriptions of each register and their usage are described in the following sections.

## 27.2.1 CAN CONTROL AND STATUS REGISTERS

The registers described in this section control the overall operation of the CAN module and show its operational status.

| COMF                  | Compleme                   | ent f                                                                                 |                                 | CPFS    | EQ                                       | Compare f                  | with W, Skip                                                                      | if f = W                           |

|-----------------------|----------------------------|---------------------------------------------------------------------------------------|---------------------------------|---------|------------------------------------------|----------------------------|-----------------------------------------------------------------------------------|------------------------------------|

| Syntax:               | COMF f                     | {,d {,a}}                                                                             |                                 | Syntax  | C:                                       | CPFSEQ                     | f {,a}                                                                            |                                    |

| Operands:             | 0 ≤ f ≤ 255                |                                                                                       |                                 | Opera   | nds:                                     | $0 \leq f \leq 255$        |                                                                                   |                                    |

|                       | $d \in [0,1]$              |                                                                                       |                                 |         |                                          | a ∈ [0,1]                  |                                                                                   |                                    |

|                       | a ∈ [0,1]                  |                                                                                       |                                 | Opera   | tion:                                    | (f) - (W),                 | (14/)                                                                             |                                    |

| Operation:            | $f \rightarrow dest$       |                                                                                       |                                 |         |                                          | skip if (f) =              | (VV)<br>comparison)                                                               |                                    |

| Status Affected:      | N, Z                       |                                                                                       |                                 | Status  | Affected:                                | None                       | ompanson                                                                          |                                    |

| Encoding:             | 0001                       | 11da ff:                                                                              | ff ffff                         | Encod   |                                          | 0110                       | 001a ff:                                                                          | ff ffff                            |

| Description:          | complemer<br>stored in W   | ts of register 'f<br>nted. If 'd' is '0'<br>/. If 'd' is '1', th<br>< in register 'f' | ', the result is<br>e result is | Descri  | 0                                        | Compares<br>location 'f' t |                                                                                   | f data memory<br>s of W by         |

|                       | lf 'a' is '0', t           | he Access Bar<br>he BSR is use                                                        |                                 |         |                                          | discarded a                | en the fetched<br>and a NOP is ex<br>aking this a two                             | xecuted                            |

|                       | set is enabl<br>in Indexed | and the extended<br>led, this instruct<br>Literal Offset A<br>never $f \le 95$ (5)    | ction operates                  |         |                                          |                            |                                                                                   | nk is selected.<br>d to select the |

|                       | Section 29<br>Bit-Oriente  | 0.2.3 "Byte-Or<br>ed Instruction<br>set Mode" for                                     | iented and s in Indexed         |         |                                          | set is enab<br>in Indexed  | nd the extende<br>led, this instruct<br>Literal Offset A<br>never f $\leq$ 95 (5) | ction operates<br>Addressing       |

| Words:                | 1                          |                                                                                       |                                 |         |                                          |                            | .2.3 "Byte-Or                                                                     | ,                                  |

| Cycles:               | 1                          |                                                                                       |                                 |         |                                          | Bit-Oriente                | ed Instruction                                                                    | s in Indexed                       |

| Q Cycle Activity:     |                            |                                                                                       |                                 |         |                                          | Literal Offs               | set Mode" for                                                                     | details.                           |

| Q1                    | Q2                         | Q3                                                                                    | Q4                              | Words   |                                          | 1                          |                                                                                   |                                    |

| Decode                | Read<br>register 'f'       | Process<br>Data                                                                       | Write to destination            | Cycles  | 3:                                       |                            | cles if skip and<br>2-word instrue                                                |                                    |

| <b>E</b> uropean la c |                            |                                                                                       |                                 | Q Cy    | cle Activity:                            |                            |                                                                                   |                                    |

| Example:              | COMF                       | REG, 0, 0                                                                             |                                 | -       | Q1                                       | Q2                         | Q3                                                                                | Q4                                 |

| Before Instruc<br>REG | tion<br>= 13h              |                                                                                       |                                 |         | Decode                                   | Read                       | Process                                                                           | No                                 |

| After Instruction     |                            |                                                                                       |                                 | الأعاد  |                                          | register 'f'               | Data                                                                              | operation                          |

| REG                   | = 13h                      |                                                                                       |                                 | lf skip | ,<br>Q1                                  | Q2                         | Q3                                                                                | Q4                                 |

| W                     | = ECh                      |                                                                                       |                                 | Г       | No                                       | No                         | No                                                                                | No                                 |

|                       |                            |                                                                                       |                                 |         | operation                                | operation                  | operation                                                                         | operation                          |

|                       |                            |                                                                                       |                                 | lf skip |                                          | d by 2-word in             | struction:                                                                        |                                    |

|                       |                            |                                                                                       |                                 | г       | Q1                                       | Q2                         | Q3                                                                                | Q4                                 |

|                       |                            |                                                                                       |                                 |         | No<br>operation                          | No<br>operation            | No<br>operation                                                                   | No<br>operation                    |

|                       |                            |                                                                                       |                                 | F       | No                                       | No                         | No                                                                                | No                                 |

|                       |                            |                                                                                       |                                 |         | operation                                | operation                  | operation                                                                         | operation                          |

|                       |                            |                                                                                       |                                 | Exam    | <u>ole:</u>                              | HERE<br>NEQUAL             | CPFSEQ REG<br>:                                                                   | G, O                               |

|                       |                            |                                                                                       |                                 |         | efore Instruction<br>PC Addr<br>W<br>REG | ess = HE<br>= ?<br>= ?     | :<br>RE                                                                           |                                    |

W; Address (EQUAL) W; Address (NEQUAL)

After Instruction

If REG PC If REG PC

= = ≠

## 32.1 Package Marking Information (Continued)

40-Lead PDIP

### 44-Lead QFN

44-Lead TQFP

64-Lead QFN

## 64-Lead TQFP

Example

## Example

## Example

## Example

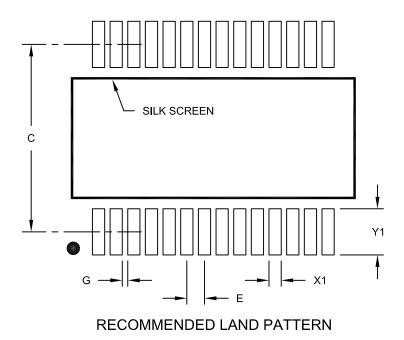

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Ν   |          | S    |      |

|--------------------------|-----|----------|------|------|

| Dimension                | MIN | NOM      | MAX  |      |

| Contact Pitch            | E   | 0.65 BSC |      |      |

| Contact Pad Spacing      | С   |          | 7.20 |      |

| Contact Pad Width (X28)  | X1  |          |      | 0.45 |

| Contact Pad Length (X28) | Y1  |          |      | 1.75 |

| Distance Between Pads    | G   | 0.20     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

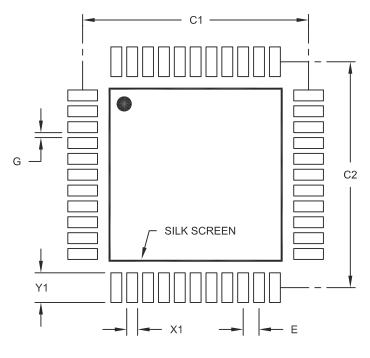

# 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | MILLIM | ETERS |          |      |

|--------------------------|--------|-------|----------|------|

| Dimension Limits         |        | MIN   | NOM      | MAX  |

| Contact Pitch            | E      |       | 0.80 BSC |      |

| Contact Pad Spacing      | C1     |       | 11.40    |      |

| Contact Pad Spacing      | C2     |       | 11.40    |      |

| Contact Pad Width (X44)  | X1     |       |          | 0.55 |

| Contact Pad Length (X44) | Y1     |       |          | 1.50 |

| Distance Between Pads    | G      | 0.25  |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076A

| Configuration Mode                   | 438 |

|--------------------------------------|-----|

| Configuration Register Protection    | 482 |

| Core Features                        |     |

| Easy Migration                       | 12  |

| Extended Instruction Set             | 11  |

| Memory Options                       | 11  |

| nanoWatt Technology                  | 11  |

| Oscillator Options and Features      | 11  |

| CPFSEQ                               |     |

| CPFSGT                               | 501 |

| CPFSLT                               | 501 |

| Crystal Oscillator/Ceramic Resonator |     |

| Customer Change Notification Service | 617 |

| Customer Notification Service        |     |

| Customer Support                     | 617 |

|                                      |     |

# D

| Data Addressing Modes                            |       |

|--------------------------------------------------|-------|

| Comparing Addressing Modes with the Extended     | l In- |

| struction Set Enabled                            | 127   |

| Direct                                           |       |

| Indexed Literal Offset                           | 126   |

| BSR                                              |       |

| Instructions Affected                            |       |

| Mapping Access Bank                              |       |

| Indirect                                         |       |

| Inherent and Literal                             | 123   |

| Data EEPROM                                      |       |

| Associated Registers                             |       |

| Code Protection                                  |       |

| During Code-Protect                              |       |

| EEADR and EEADRH Registers                       | 139   |

| EECON1 and EECON2 Registers                      |       |

| Overview                                         |       |

| Reading                                          | 141   |

| Spurious Write Protection                        |       |

| Using                                            |       |

| Write Verify                                     |       |

| Writing                                          | 141   |

| Data EEPROM Memory                               |       |

| Operation During Code-Protect                    |       |

| Data Memory                                      |       |

| Access Bank                                      |       |

| Bank Select Register (BSR)                       |       |

| Extended Instruction Set                         |       |

| General Purpose Registers                        | 110   |

| Memory Maps                                      |       |

| PIC18FX5K80/X6K80 Devices                        |       |

| Special Function Registers                       |       |

| Special Function Registers                       |       |

| Data Signal Modulator (DSM)                      | 195   |

| Associated Registers                             |       |

| Carrier Signal Sources                           | 197   |

| Carrier Source                                   | ~~~   |

| Pin Disable                                      |       |

| Polarity Select                                  |       |

| Carrier Synchronization                          |       |

| Effects of a Reset                               |       |

| Modulated Output Polarity                        | 200   |

| Modulator Signal Sources                         |       |

| Modulator Source Pin Disable                     |       |

| Operation                                        |       |

| Operation in Sleep Mode                          |       |

| Programmable Modulator Data<br>Slew Rate Control |       |

| DAW                                              |       |

|                                                  | 00Z   |

| DC Characteristics                   |        |

|--------------------------------------|--------|

| CTMU Current Source Specifications   | 557    |

| PIC18F66K80 Family (Industrial) 55   | 5, 557 |

| Power-Down and Supply Current        | 540    |

| Supply Voltage                       | 539    |

| DCFSNZ                               | 503    |

| DECF                                 | 502    |

| DECFSZ                               | 503    |

| Default System Clock                 | 57     |

| Details on Individual Family Members | 12     |

| Development Support                  |        |

| Device Overview                      | 11     |

| Features (28-Pin Devices)            |        |

| Features (40/44-Pin Devices)         | 13     |

| Features (64-Pin Devices)            | 14     |

| Device Reset Timers                  | 83     |

| Oscillator Start-up Timer (OST)      | 83     |

| PLL Lock Time-out                    | 83     |

| Power-up Timer (PWRT)                | 83     |

| Direct Addressing                    | 124    |

| Disable/Sleep Mode                   | 438    |

## Е

| ECAN Module                                         | 391 |

|-----------------------------------------------------|-----|

| Baud Rate Setting                                   | 446 |

| Bit Time Partitioning                               |     |

| Bit Timing Configuration Registers                  |     |

| Calculating To, Nominal Bit Rate and Nominal Bit Ti |     |

| 449                                                 |     |

| CAN Baud Rate Registers                             | 430 |

| CAN Control and Status Registers                    | 393 |

| CAN I/O Control Register                            | 433 |

| CAN Interrupt Registers                             |     |

| CAN Interrupts                                      | 453 |

| Bus Activity Wake-up                                | 454 |

| Bus-Off                                             | 455 |

| Code Bits                                           |     |

| Error                                               | 454 |

| Message Error                                       | 454 |

| Receive                                             | 454 |

| Receiver Bus Passive                                | 455 |

| Receiver Overflow                                   | 455 |

| Receiver Warning                                    |     |

| Transmit                                            |     |

| Transmitter Bus Passive                             | 455 |

| Transmitter Warning                                 |     |

| CAN Message Buffers                                 | 440 |

| Dedicated Receive                                   |     |

| Dedicated Transmit                                  |     |

| Programmable Auto-RTR                               |     |

| Programmable Transmit/Receive                       |     |

| CAN Message Transmission                            | 441 |

| Aborting                                            |     |

| Initiating                                          | 441 |

| Priority                                            |     |

| CAN Modes of Operation                              |     |

| CAN Registers                                       |     |

| Configuration Mode                                  |     |

| Dedicated CAN Receive Buffer Registers              |     |

| Dedicated CAN Transmit Buffer Registers             |     |

| Disable/Sleep Mode                                  |     |

| Error Detection                                     |     |

| Acknowledge                                         |     |

| Bit                                                 |     |

| CRC                                                 |     |

| Error Modes and Counters                            |     |

$\ensuremath{\textcircled{}^{\odot}}$  2010-2012 Microchip Technology Inc.