Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

:XFI

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | ECANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6К х 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x12b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN-S (6x6)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f25k80-h-mm |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                                                                                                                                   | Pin N | umber        | Pin  | Buffer      |                                                             |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------|------|-------------|-------------------------------------------------------------|--|--|--|

| Pin Name                                                                                                                                                          | PDIP  | QFN/<br>TQFP | Туре |             | Description                                                 |  |  |  |

| RB6/PGC/KBI2                                                                                                                                                      | 39    | 16           |      |             |                                                             |  |  |  |

| RB6                                                                                                                                                               |       |              | I/O  | ST/<br>CMOS | Digital I/O.                                                |  |  |  |

| PGC                                                                                                                                                               |       |              | I    | ST          | In-Circuit Debugger and ICSP™ programming clock inp<br>pin. |  |  |  |

| KBI2                                                                                                                                                              |       |              | Ι    | ST          | Interrupt-on-change pin.                                    |  |  |  |

| RB7/PGD/T3G/KBI3                                                                                                                                                  | 40    | 17           |      |             |                                                             |  |  |  |

| RB7                                                                                                                                                               |       |              | I/O  | ST/<br>CMOS | Digital I/O.                                                |  |  |  |

| PGD                                                                                                                                                               |       |              | I/O  | ST          | In-Circuit Debugger and ICSP™ programming data pin.         |  |  |  |

| T3G                                                                                                                                                               |       |              | I    | ST          | Timer3 external clock gate input.                           |  |  |  |

| KBI3                                                                                                                                                              |       |              | I    | ST          | Interrupt-on-change pin.                                    |  |  |  |

| Legend: $I^2C^{TM} = I^2C/SMBus input bufferCMOS= CMOS compatible input or outputST= Schmitt Trigger input with CMOS levelsAnalog= Analog inputI= InputO= Output$ |       |              |      |             |                                                             |  |  |  |

= Input Ρ = Power

NOTES:

| TABLE 5-4:  |             |                    | JNS FUR ALL | REGISTERS (                              |                                                                  |                                    |  |

|-------------|-------------|--------------------|-------------|------------------------------------------|------------------------------------------------------------------|------------------------------------|--|

| Register    | A           | Applicable Devices |             | Power-on<br>Reset,<br>Brown-out<br>Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via<br>WDT<br>or Interrupt |  |

| PMD1        | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | 0000 0000                                | 0000 0000                                                        | uuuu uuuu                          |  |

| PMD2        | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | 0000                                     | 0000                                                             | uuuu                               |  |

| PADCFG1     | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | 00000                                    | 00000                                                            | uuuuu                              |  |

| CTMUCONH    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | 0-00 0000                                | 0-00 0000                                                        | u-uu uuuu                          |  |

| CTMUCONL    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | 0000 0000                                | 0000 0000                                                        | uuuu uuuu                          |  |

| CTMUICON    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | 0000 0000                                | 0000 0000                                                        | uuuu uuuu                          |  |

| CCPR2H      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | xxxx xxxx                                                        | uuuu uuuu                          |  |

| CCPR2L      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | xxxx xxxx                                                        | uuuu uuuu                          |  |

| CCP2CON     | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | 00 0000                                  | 00 0000                                                          | uu uuuu                            |  |

| CCPR3H      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | xxxx xxxx                                                        | uuuu uuuu                          |  |

| CCPR3L      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | xxxx xxxx                                                        | uuuu uuuu                          |  |

| CCP3CON     | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | 00 0000                                  | 00 0000                                                          | uu uuuu                            |  |

| CCPR4H      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | xxxx xxxx                                                        | uuuu uuuu                          |  |

| CCPR4L      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | xxxx xxxx                                                        | uuuu uuuu                          |  |

| CCP4CON     | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | 00 0000                                  | 00 0000                                                          | uu uuuu                            |  |

| CCPR5H      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | xxxx xxxx                                                        | uuuu uuuu                          |  |

| CCPR5L      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | xxxx xxxx                                                        | uuuu uuuu                          |  |

| CCP5CON     | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | 00 0000                                  | 00 0000                                                          | uu uuuu                            |  |

| PSPCON      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | 0000                                     | 0000                                                             | uuuu                               |  |

| MDCON       | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | 0010 00                                  | 0010 00                                                          | uuuu uu                            |  |

| MDSRC       | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | 0 xxxx                                   | 0 xxxx                                                           | u uuuu                             |  |

| MDCARH      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | 0xx- xxxx                                | 0xx- xxxx                                                        | uuu- uuuu                          |  |

| MDCARL      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | 0xx- xxxx                                | 0xx- xxxx                                                        | uuu- uuuu                          |  |

| CANCON_RO0  | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | 1000 0000                                | 1000 0000                                                        | uuuu uuuu                          |  |

| CANSTAT_RO0 | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | 1000 0000                                | 1000 0000                                                        | uuuu uuuu                          |  |

| RXB1D7      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |

| RXB1D6      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |

| RXB1D5      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |

| RXB1D4      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |

| RXB1D3      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |

| RXB1D2      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |

| RXB1D1      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |

| RXB1D0      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |

| RXB1DLC     | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | xxxx xxxx                          |  |

### TABLE 5-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Legend: u = unchanged; x = unknown; - = unimplemented bit, read as '0'; q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 5-3 for Reset value for specific conditions.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read as '0'.

### 6.1.2 PROGRAM COUNTER

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide and contained in three separate 8-bit registers.

The low byte, known as the PCL register, is both readable and writable. The high byte, or PCH register, contains the PC<15:8> bits and is not directly readable or writable. Updates to the PCH register are performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCU register are performed through the PCLATU register.

The contents of PCLATH and PCLATU are transferred to the Program Counter by any operation that writes PCL. Similarly, the upper two bytes of the Program Counter are transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 6.1.5.1 "Computed** GOTO").

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the Least Significant bit (LSb) of PCL is fixed to a value of '0'. The PC increments by two to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the Program Counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the Program Counter.

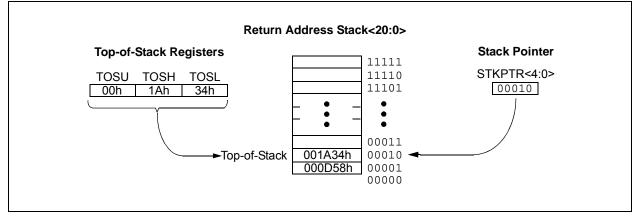

### 6.1.3 RETURN ADDRESS STACK

The return address stack enables execution of any combination of up to 31 program calls and interrupts. The PC is pushed onto the stack when a CALL or RCALL instruction is executed or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or a RETFIE instruction. The value is also pulled off the stack on ADDULNK and SUBULNK instructions if the extended instruction set is enabled. PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions.

The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer, STKPTR. The stack space is not part of either program or data space. The Stack Pointer is readable and writable and the address on the top of the stack is readable and writable through the Top-of-Stack (TOS) Special Function Registers. Data can also be pushed to, or popped from the stack, using these registers.

A CALL type instruction causes a push onto the stack. The Stack Pointer is first incremented and the location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction following the CALL). A RETURN type instruction causes a pop from the stack. The contents of the location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The Stack Pointer is initialized to '00000' after all Resets. There is no RAM associated with the location corresponding to a Stack Pointer value of '00000'; this is only a Reset value. Status bits indicate if the stack is full, has overflowed or has underflowed.

### 6.1.3.1 Top-of-Stack Access

Only the top of the return address stack is readable and writable. A set of three registers, TOSU:TOSH:TOSL, holds the contents of the stack location pointed to by the STKPTR register (Figure 6-3). This allows users to implement a software stack, if necessary. After a CALL, RCALL or interrupt (or ADDULNK and SUBULNK instructions, if the extended instruction set is enabled), the software can read the pushed value by reading the TOSU:TOSH:TOSL registers. These values can be placed on a user-defined software stack. At return time, the software can return these values to TOSU:TOSH:TOSL and do a return.

While accessing the stack, users must disable the Global Interrupt Enable bits to prevent inadvertent stack corruption.

### FIGURE 6-3: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

#### 6.2.3 INSTRUCTIONS IN PROGRAM MEMORY

The program memory is addressed in bytes. Instructions are stored as two or four bytes in program memory. The Least Significant Byte (LSB) of an instruction word is always stored in a program memory location with an even address (LSB = 0). To maintain alignment with instruction boundaries, the PC increments in steps of two and the LSB will always read '0' (see Section 6.1.2 "Program Counter").

Figure 6-5 shows an example of how instruction words are stored in the program memory.

The CALL and GOTO instructions have the absolute program memory address embedded into the instruction. Since instructions are always stored on word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1> which accesses the desired byte address in program memory. Instruction #2 in Figure 6-5 shows how the instruction, GOTO 0006h, is encoded in the program memory. Program branch instructions, which encode a relative address offset, operate in the same manner. The offset value stored in a branch instruction represents the number of single-word instructions that the PC will be offset by. For more details on the instruction set, see Section 29.0 "Instruction Set Summary".

|                |            |                    | LSB = 1 | LSB = 0 | Word Address $\downarrow$ |

|----------------|------------|--------------------|---------|---------|---------------------------|

|                | Program M  | lemory             |         |         | 000000h                   |

|                | Byte Locat | ions $\rightarrow$ |         |         | 000002h                   |

|                |            |                    |         |         | 000004h                   |

|                |            |                    |         |         | 000006h                   |

| Instruction 1: | MOVLW      | 055h               | 0Fh     | 55h     | 000008h                   |

| Instruction 2: | GOTO       | 0006h              | EFh     | 03h     | 00000Ah                   |

|                |            |                    | F0h     | 00h     | 00000Ch                   |

| Instruction 3: | MOVFF      | 123h, 456h         | C1h     | 23h     | 00000Eh                   |

|                |            |                    | F4h     | 56h     | 000010h                   |

|                |            |                    |         |         | 000012h                   |

|                |            |                    |         |         | 000014h                   |

####

#### 6.2.4 **TWO-WORD INSTRUCTIONS**

The standard PIC18 instruction set has four, two-word instructions: CALL, MOVFF, GOTO and LSFR. In all cases, the second word of the instructions always has '1111' as its four Most Significant bits (MSbs). The other 12 bits are literal data, usually a data memory address.

The use of '1111' in the 4 MSbs of an instruction specifies a special form of NOP. If the instruction is executed in proper sequence, immediately after the first word, the data in the second word is accessed and

used by the instruction sequence. If the first word is skipped for some reason and the second word is executed by itself, a NOP is executed instead. This is necessary for cases when the two-word instruction is preceded by a conditional instruction that changes the PC. Example 6-4 shows how this works.

Note: For information on two-word instructions in the extended instruction set, see Section 6.5 "Program Memory and the Extended Instruction Set".

| EXAMPLE 6-4: | <b>TWO-WORD INSTRUCTIONS</b> |

|--------------|------------------------------|

|              |                              |

| CASE 1:             |                  |                              |

|---------------------|------------------|------------------------------|

| Object Code         | Source Code      |                              |

| 0110 0110 0000 0000 | TSTFSZ REG1      | ; is RAM location 0?         |

| 1100 0001 0010 0011 | MOVFF REG1, REG2 | ; No, skip this word         |

| 1111 0100 0101 0110 |                  | ; Execute this word as a NOP |

| 0010 0100 0000 0000 | ADDWF REG3       | ; continue code              |

| CASE 2:             |                  |                              |

| Object Code         | Source Code      |                              |

| 0110 0110 0000 0000 | TSTFSZ REG1      | ; is RAM location 0?         |

| 1100 0001 0010 0011 | MOVFF REG1, REG2 | ; Yes, execute this word     |

| 1111 0100 0101 0110 |                  | ; 2nd word of instruction    |

| 0010 0100 0000 0000 | ADDWF REG3       | ; continue code              |

© 2010-2012 Microchip Technology Inc.

### REGISTER 10-3: INTCON3: INTERRUPT CONTROL REGISTER 3

| R/W-1                | R/W-1               | R/W-0             | R/W-0            | R/W-0            | R/W-0           | R/W-0            | R/W-0         |

|----------------------|---------------------|-------------------|------------------|------------------|-----------------|------------------|---------------|

| INT2IP               | INT1IP              | INT3IE            | INT2IE           | INT1IE           | INT3IF          | INT2IF           | INT1IF        |

| bit 7                |                     |                   |                  |                  |                 |                  | bit (         |

|                      |                     |                   |                  |                  |                 |                  |               |

| Legend:<br>R = Reada | able bit            | W = Writable      | hit              | II – I Inimpler  | nented bit, rea | d as '0'         |               |

| -n = Value           |                     | '1' = Bit is set  |                  | '0' = Bit is cle |                 | x = Bit is unkr  | NOW/D         |

|                      |                     |                   |                  |                  | arcu            |                  |               |

| bit 7                | INT2IP: INT2        | External Interr   | upt Priority bit |                  |                 |                  |               |

|                      | 1 = High pric       |                   |                  |                  |                 |                  |               |

|                      | 0 = Low prio        | rity              |                  |                  |                 |                  |               |

| bit 6                |                     | External Interr   | upt Priority bit |                  |                 |                  |               |

|                      | 1 = High pric       |                   |                  |                  |                 |                  |               |

| bit 5                | 0 = Low prio        | External Interr   | unt Enable bit   |                  |                 |                  |               |

| DILO                 |                     | the INT3 exteri   | •                |                  |                 |                  |               |

|                      |                     | the INT3 exter    |                  |                  |                 |                  |               |

| bit 4                |                     | External Interr   | •                |                  |                 |                  |               |

|                      |                     | the INT2 extern   |                  |                  |                 |                  |               |

|                      | 0 = Disables        | the INT2 exter    | nal interrupt    |                  |                 |                  |               |

| bit 3                |                     | External Interr   | •                |                  |                 |                  |               |

|                      |                     | the INT1 extern   |                  |                  |                 |                  |               |

| <b>h</b> it 0        |                     | the INT1 exter    | •                |                  |                 |                  |               |

| bit 2                |                     | External Interr   |                  | must be cleared  | din ooffwara)   |                  |               |

|                      |                     | 3 external interi |                  |                  | u in soltware)  |                  |               |

| bit 1                |                     | External Interr   |                  |                  |                 |                  |               |

|                      |                     |                   |                  | must be cleared  | d in software)  |                  |               |

|                      | 0 = The INT2        | 2 external interi | upt did not oc   | cur              |                 |                  |               |

| bit 0                | INT1IF: INT1        | External Interr   | upt Flag bit     |                  |                 |                  |               |

|                      |                     |                   |                  | must be cleared  | d in software)  |                  |               |

|                      | 0 = The INT         | 1 external interi | upt did not oc   | cur              |                 |                  |               |

| Note:                | Interrupt flag bits | are set when      | an interrupt co  | ondition occurs  | regardless of   | the state of its | corresponding |

|                      | enable bit or the   |                   |                  |                  |                 |                  |               |

|                      | are clear prior to  |                   |                  |                  |                 |                  |               |

### REGISTER 12-4: MDCARL: MODULATION LOW CARRIER CONTROL REGISTER

| R/W-0                                                                                                                            | R/W-x                                                                                  | R/W-x                                | U-0          | R/W-x                          | R/W-x                        | R/W-x                | R/W-x                |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------|--------------|--------------------------------|------------------------------|----------------------|----------------------|--|--|--|

| MDCLODIS                                                                                                                         | MDCLPOL                                                                                | MDCLSYNC                             | _            | MDCL3 <sup>(1)</sup>           | MDCL2 <sup>(1)</sup>         | MDCL1 <sup>(1)</sup> | MDCL0 <sup>(1)</sup> |  |  |  |

| bit 7                                                                                                                            |                                                                                        |                                      |              |                                |                              |                      | bit C                |  |  |  |

|                                                                                                                                  |                                                                                        |                                      |              |                                |                              |                      |                      |  |  |  |

| Legend:                                                                                                                          | L :1                                                                                   |                                      | :4           |                                |                              |                      |                      |  |  |  |

| R = Readable bit $W$ = Writable bit $U$ = Unimplemented bit, read as '0' $r = Velue et DOD(4) = Dit is act(2) = Dit is also and$ |                                                                                        |                                      |              |                                |                              |                      |                      |  |  |  |

| -n = Value at F                                                                                                                  | 'UR                                                                                    | '1' = Bit is set                     |              | '0' = Bit is clea              | ared                         | x = Bit is unkr      | nown                 |  |  |  |

| bit 7                                                                                                                            | MDCLODIS:                                                                              | Modulator Low                        | Carrier Out  | out Disable bit                |                              |                      |                      |  |  |  |

|                                                                                                                                  |                                                                                        | ignal driving the                    |              | output pin (selec              | ted by MDCL<3                | 3:0> of the MDC      | CARL register        |  |  |  |

|                                                                                                                                  | 0 = Output si<br>is enable                                                             | • •                                  | peripheral o | output pin (selec              | ted by MDCL<3                | 3:0> of the MDC      | CARL register        |  |  |  |

| bit 6                                                                                                                            | MDCLPOL: N                                                                             | Modulator Low C                      | arrier Polar | ity Select bit                 |                              |                      |                      |  |  |  |

|                                                                                                                                  |                                                                                        | low carrier sign<br>low carrier sign |              |                                |                              |                      |                      |  |  |  |

| bit 5                                                                                                                            | MDCLSYNC:                                                                              | : Modulator Low                      | Carrier Syr  | hchronization En               | able bit                     |                      |                      |  |  |  |

|                                                                                                                                  | time carr                                                                              | ier                                  |              | the low time carr              |                              |                      | itch to the higl     |  |  |  |

|                                                                                                                                  |                                                                                        |                                      |              | d to the low time              | carrier signal <sup>(1</sup> | )                    |                      |  |  |  |

| bit 4                                                                                                                            | •                                                                                      | ted: Read as '0                      |              |                                |                              |                      |                      |  |  |  |

| bit 3-0                                                                                                                          |                                                                                        |                                      | High Carrie  | r Selection bits <sup>(1</sup> | )                            |                      |                      |  |  |  |

|                                                                                                                                  | 1111-1001 =                                                                            |                                      | S <b>.</b>   |                                |                              |                      |                      |  |  |  |

|                                                                                                                                  | 1000 = CCP5 output (PWM Output mode only)<br>0111 = CCP4 output (PWM Output mode only) |                                      |              |                                |                              |                      |                      |  |  |  |

|                                                                                                                                  |                                                                                        | 3 output (PWM (                      |              | .,                             |                              |                      |                      |  |  |  |

|                                                                                                                                  | 0101 = CCP2 output (PWM Output mode only)                                              |                                      |              |                                |                              |                      |                      |  |  |  |

|                                                                                                                                  |                                                                                        | P1 output (PWN<br>rence clock mod    |              | de only)                       |                              |                      |                      |  |  |  |

|                                                                                                                                  | 0011 = Kelei<br>0010 = MDC                                                             |                                      | ule signai   |                                |                              |                      |                      |  |  |  |

|                                                                                                                                  | 0001 = MDC                                                                             |                                      |              |                                |                              |                      |                      |  |  |  |

|                                                                                                                                  | 0000 <b>= V</b> ss                                                                     |                                      |              |                                |                              |                      |                      |  |  |  |

**Note 1:** Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

| Name   | Bit 7    | Bit 6   | Bit 5    | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|--------|----------|---------|----------|--------|--------|--------|--------|--------|

| MDCARH | MDCHODIS | MDCHPOL | MDCHSYNC | _      | MDCH3  | MDCH2  | MDCH1  | MDCH0  |

| MDCARL | MDCLODIS | MDCLPOL | MDCLSYNC | _      | MDCL3  | MDCL2  | MDCL1  | MDCL0  |

| MDCON  | MDEN     | MDOE    | MDSLR    | MDOPOL | MDO    | _      | _      | MDBIT  |

| MDSRC  | MDSODIS  |         | —        | —      | MDSRC3 | MDSRC2 | MDSRC1 | MDSRC0 |

| PMD2   | _        | —       | —        | _      | MODMD  | ECANMD | CMP2MD | CMP1MD |

## TABLE 12-1: SUMMARY OF REGISTERS ASSOCIATED WITH DATA SIGNAL MODULATOR MODE

Legend: — = unimplemented, read as '0'. Shaded cells are not used in the Data Signal Modulator mode.

For more details on selecting the optimum C1 and C2 for a given crystal, see the crystal manufacture's applications information. The optimum value depends in part on the amount of parasitic capacitance in the circuit, which is often unknown. For that reason, it is highly recommended that thorough testing and validation of the oscillator be performed after values have been selected.

### 14.5.1 USING SOSC AS A CLOCK SOURCE

The SOSC oscillator is also available as a clock source in power-managed modes. By setting the clock select bits, SCS<1:0> (OSCCON<1:0>), to '01', the device switches to SEC\_RUN mode and both the CPU and peripherals are clocked from the SOSC oscillator. If the IDLEN bit (OSCCON<7>) is cleared and a SLEEP instruction is executed, the device enters SEC\_IDLE mode. Additional details are available in **Section 4.0 "Power-Managed Modes"**.

Whenever the SOSC oscillator is providing the clock source, the SOSC System Clock Status flag, SOSCRUN (OSCCON2<6>), is set. This can be used to determine the controller's current clocking mode. It can also indicate the clock source currently being used by the Fail-Safe Clock Monitor.

If the Clock Monitor is enabled and the SOSC oscillator fails while providing the clock, polling the SOCSRUN bit will indicate whether the clock is being provided by the SOSC oscillator or another source.

# 14.5.2 SOSC OSCILLATOR LAYOUT CONSIDERATIONS

The SOSC oscillator circuit draws very little power during operation. Due to the low-power nature of the oscillator, it may also be sensitive to rapidly changing signals in close proximity. This is especially true when the oscillator is configured for extremely Low-Power mode, SOSCSEL<1:0> (CONFIG1L<4:3>) = 01.

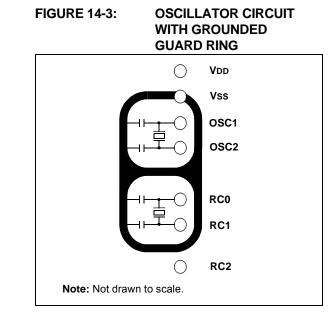

The oscillator circuit, displayed in Figure 14-2, should be located as close as possible to the microcontroller. There should be no circuits passing within the oscillator circuit boundaries other than Vss or VDD.

If a high-speed circuit must be located near the oscillator, it may help to have a grounded guard ring around the oscillator circuit. The guard, as displayed in Figure 14-3, could be used on a single-sided PCB or in addition to a ground plane. (Examples of a high-speed circuit include the ECCP1 pin, in Output Compare or PWM mode, or the primary oscillator, using the OSC2 pin.)

In the Low Drive Level mode, SOSCSEL<1:0> = 01, it is critical that RC2 I/O pin signals be kept away from the oscillator circuit. Configuring RC2 as a digital output, and toggling it, can potentially disturb the oscillator circuit, even with a relatively good PCB layout. If possible, either leave RC2 unused or use it as an input pin with a slew rate limited signal source. If RC2 must be used as a digital output, it may be necessary to use the Higher Drive Level Oscillator mode (SOSCSEL<1:0> = 11) with many PCB layouts.

Even in the Higher Drive Level mode, careful layout procedures should still be followed when designing the oscillator circuit.

In addition to dV/dt induced noise considerations, it is important to ensure that the circuit board is clean. Even a very small amount of conductive, soldering flux residue can cause PCB leakage currents that can overwhelm the oscillator circuit.

## 14.6 Timer1 Interrupt

The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The Timer1 interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled or disabled by setting or clearing the Timer1 Interrupt Enable bit, TMR1IE (PIE1<0>).

#### EXAMPLE 18-2: CURRENT CALIBRATION ROUTINE

```

#include "p18cxxx.h"

#define COUNT 500

//@ 8MHz = 125uS.

#define DELAY for(i=0;i<COUNT;i++)</pre>

#define RCAL .027

//R value is 4200000 (4.2M)

//scaled so that result is in

//1/100th of uA

#define ADSCALE 1023

//for unsigned conversion 10 sig bits

#define ADREF 3.3

//Vdd connected to A/D Vr+

int main(void)

int i;

int j = 0; //index for loop

unsigned int Vread = 0;

double VTot = 0;

float Vavg=0, Vcal=0, CTMUISrc = 0; //float values stored for calcs

//assume CTMU and A/D have been setup correctly

//see Example 25-1 for CTMU & A/D setup

setup();

CTMUCONHbits.CTMUEN = 1;

//Enable the CTMU

for(j=0;j<10;j++)</pre>

{

//drain charge on the circuit

CTMUCONHbits.IDISSEN = 1;

//wait 125us

DELAY;

CTMUCONHbits.IDISSEN = 0;

//end drain of circuit

CTMUCONLbits.EDG1STAT = 1;

//Begin charging the circuit

//using CTMU current source

DELAY;

//wait for 125us

//Stop charging circuit

CTMUCONLbits.EDG1STAT = 0;

PIR1bits.ADIF = 0;

//make sure A/D Int not set

ADCON0bits.GO=1;

//and begin A/D conv.

while(!PIR1bits.ADIF);

//Wait for A/D convert complete

Vread = ADRES;

//Get the value from the A/D

PIR1bits.ADIF = 0;

//Clear A/D Interrupt Flag

VTot += Vread;

//Add the reading to the total

}

Vavg = (float)(VTot/10.000);

//Average of 10 readings

Vcal = (float)(Vavg/ADSCALE*ADREF);

CTMUISrc = Vcal/RCAL;

//CTMUISrc is in 1/100ths of uA

```

| R/W-0      | R/W-0                                  | R/W-0                               | R/W-0           | R/W-0                | R/W-0                  | R/W-0                | R/W-0                |

|------------|----------------------------------------|-------------------------------------|-----------------|----------------------|------------------------|----------------------|----------------------|

| WCOL       | SSPOV                                  | SSPEN <sup>(1)</sup>                | CKP             | SSPM3 <sup>(2)</sup> | SSPM2 <sup>(2)</sup>   | SSPM1 <sup>(2)</sup> | SSPM0 <sup>(2)</sup> |

| bit 7      | I                                      |                                     |                 |                      |                        |                      | bit 0                |

| Legend:    |                                        |                                     |                 |                      |                        |                      |                      |

| R = Reada  | able bit                               | W = Writable                        | bit             | U = Unimplen         | nented bit, read       | d as '0'             |                      |

| -n = Value | at POR                                 | '1' = Bit is set                    |                 | '0' = Bit is clea    |                        | x = Bit is unkr      | nown                 |

|            |                                        |                                     |                 |                      |                        |                      |                      |

| bit 7      | WCOL: Write                            | e Collision Dete                    | ct bit          |                      |                        |                      |                      |

|            | In Master Tra                          |                                     |                 |                      |                        |                      |                      |

|            |                                        | to the SSPBUR                       |                 |                      |                        | nditions were i      | not valid for a      |

|            | 0 = No collis                          | sion to be starte                   | ea (must be ci  | eared in softwar     | e)                     |                      |                      |

|            | In Slave Trar                          |                                     |                 |                      |                        |                      |                      |

|            |                                        | PBUF register is                    | written while   | it is still transm   | itting the previ       | ous word (mus        | t be cleared in      |

|            | software                               | ,                                   |                 |                      |                        |                      |                      |

|            | 0 = No collis                          |                                     |                 |                      |                        |                      |                      |

|            | In Receive m<br>This is a "dor         | node (Master or                     | Slave modes     | <u>):</u>            |                        |                      |                      |

| bit 6      |                                        | ceive Overflow li                   | ndicator hit    |                      |                        |                      |                      |

|            | In Receive m                           |                                     |                 |                      |                        |                      |                      |

|            |                                        | received while                      | the SSPBUF      | register is still h  | olding the prev        | vious byte (mus      | t be cleared in      |

|            | software                               | /                                   |                 |                      |                        |                      |                      |

|            | 0 = No over                            |                                     |                 |                      |                        |                      |                      |

|            | <u>In Transmit n</u><br>This is a "dor | <u>node:</u><br>n't care" bit in Tr | ansmit mode     |                      |                        |                      |                      |

| bit 5      |                                        | ster Synchronou                     |                 |                      |                        |                      |                      |

| bit 0      |                                        | the serial port a                   |                 |                      | CL pins as the         | serial port pins     |                      |

|            |                                        | serial port and                     |                 |                      |                        |                      |                      |

| bit 4      | CKP: SCK R                             | elease Control                      | bit             |                      |                        |                      |                      |

|            | In Slave mod                           |                                     |                 |                      |                        |                      |                      |

|            | 1 = Releases                           |                                     |                 |                      |                        |                      |                      |

|            | 0 = Holds cid                          | ock low (clock st                   | retch), used to | o ensure data se     | etup time              |                      |                      |

|            | Unused in th                           |                                     |                 |                      |                        |                      |                      |

| bit 3-0    | SSPM<3:0>:                             | : Master Synchr                     | onous Serial I  | Port Mode Selec      | ct bits <sup>(2)</sup> |                      |                      |

|            | 1111 = I <sup>2</sup> C S              | Slave mode, 10-                     | bit address wi  | th Start and Sto     | p bit interrupts       |                      |                      |

|            |                                        | Slave mode, 7-b                     |                 |                      |                        | nabled               |                      |

|            |                                        | Firmware Contro                     |                 |                      |                        |                      |                      |

|            |                                        | I SSPMSK regis<br>/laster mode, clo |                 |                      |                        |                      |                      |

|            |                                        | Blave mode, 10-                     |                 |                      | //                     |                      |                      |

|            | 0110 = I <sup>2</sup> C S              | Slave mode, 7-b                     | it address      |                      |                        |                      |                      |

| Note 1:    | When enabled, t                        | he SDA and SC                       | L pins must b   | e configured as      | inputs.                |                      |                      |

| 2:         | Bit combinations                       |                                     |                 | -                    | -                      | ed in SPI mode       | e only.              |

| 3:         | When SSPM<3:0                          |                                     |                 |                      |                        |                      | •                    |

|            | SSPMSK registe                         |                                     |                 |                      |                        |                      |                      |

| 4:         | This mode is only                      | y available whe                     | n 7-Bit Addres  | s Masking mod        | e is selected (N       | ASSPMSK Cor          | figuration bit       |

|            | is '1').                               |                                     |                 |                      |                        |                      |                      |

## REGISTER 21-4: SSPCON1: MSSP CONTROL REGISTER 1 (I<sup>2</sup>C<sup>™</sup> MODE)

#### 27.15.6.1 Receiver Overflow

An overflow condition occurs when the MAB has assembled a valid received message (the message meets the criteria of the acceptance filters) and the receive buffer associated with the filter is not available for loading of a new message. The associated RXBnOVFL bit in the COMSTAT register will be set to indicate the overflow condition. This bit must be cleared by the MCU.

#### 27.15.6.2 Receiver Warning

The receive error counter has reached the MCU warning limit of 96.

#### 27.15.6.3 Transmitter Warning

The transmit error counter has reached the MCU warning limit of 96.

#### 27.15.6.4 Receiver Bus Passive

This will occur when the device has gone to the errorpassive state because the receive error counter is greater or equal to 128.

#### 27.15.6.5 Transmitter Bus Passive

This will occur when the device has gone to the errorpassive state because the transmit error counter is greater or equal to 128.

#### 27.15.6.6 Bus-Off

The transmit error counter has exceeded 255 and the device has gone to bus-off state.

| Mnemonic, |                                 | Description                              | Cualas     | 16-Bit Instruction Word |               |      |      | Status            | Natas       |

|-----------|---------------------------------|------------------------------------------|------------|-------------------------|---------------|------|------|-------------------|-------------|

| Opera     | nds                             | Description                              | Cycles     | MSb                     |               |      | LSb  | Affected          | Notes       |

| BYTE-OR   | IENTED                          | OPERATIONS                               |            |                         |               |      |      |                   |             |

| ADDWF     | f, d, a                         | Add WREG and f                           | 1          | 0010                    | 01da          | ffff | ffff | C, DC, Z, OV, N   | 1, 2        |

| ADDWFC    | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010                    | 00da          | ffff | ffff | C, DC, Z, OV, N   | 1, 2        |

| ANDWF     | f, d, a                         | AND WREG with f                          | 1          | 0001                    | 01da          | ffff | ffff | Z, N              | 1,2         |

| CLRF      | f, a                            | Clear f                                  | 1          | 0110                    | 101a          | ffff | ffff | Z                 | 2           |

| COMF      | f, d, a                         | Complement f                             | 1          | 0001                    | 11da          | ffff | ffff | Z, N              | 1, 2        |

| CPFSEQ    | f, a                            | Compare f with WREG, Skip =              | 1 (2 or 3) | 0110                    | 001a          | ffff | ffff | None              | 4           |

| CPFSGT    | f, a                            | Compare f with WREG, Skip >              | 1 (2 or 3) | 0110                    | 010a          | ffff | ffff | None              | 4           |

| CPFSLT    | f, a                            | Compare f with WREG, Skip <              | 1 (2 or 3) | 0110                    | 000a          | ffff | ffff | None              | 1, 2        |

| DECF      | f, d, a                         | Decrement f                              | 1          | 0000                    | 01da          | ffff | ffff | C, DC, Z, OV, N   | 1, 2, 3, 4  |

| DECFSZ    | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010                    | 11da          | ffff | ffff | None              | 1, 2, 3, 4  |

| DCFSNZ    | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 11da          | ffff | ffff | None              | 1, 2        |

| INCF      | f, d, a                         | Increment f                              | 1          | 0010                    | 10da          | ffff | ffff | C, DC, Z, OV, N   | 1, 2, 3, 4  |

| INCFSZ    | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011                    | 11da          | ffff | ffff | None              | 4           |

| INFSNZ    | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 10da          | ffff | ffff | None              | 1, 2        |

| IORWF     | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001                    | 00da          | ffff | ffff | Z, N              | 1, 2        |

| MOVF      | f, d, a                         | Move f                                   | 1          | 0101                    | 00da          | ffff | ffff | Z, N              | 1           |

| MOVFF     | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          | 1100                    | ffff          | ffff | ffff | None              |             |

|           | 0 u                             | f <sub>d</sub> (destination) 2nd word    |            | 1111                    | ffff          | ffff | ffff |                   |             |

| MOVWF     | f, a                            | Move WREG to f                           | 1          | 0110                    | 111a          | ffff | ffff | None              |             |

| MULWF     | f, a                            | Multiply WREG with f                     | 1          | 0000                    | 001a          | ffff | ffff | None              | 1, 2        |

| NEGF      | f, a                            | Negate f                                 | 1          | 0110                    | 110a          | ffff | ffff | C, DC, Z, OV, N   |             |

| RLCF      | f, d, a                         | Rotate Left f through Carry              | 1          | 0011                    | 01da          | ffff | ffff | C, Z, N           | 1, 2        |

| RLNCF     | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100                    | 01da          | ffff | ffff | Z, N              |             |

| RRCF      | f, d, a                         | Rotate Right f through Carry             | 1          | 0011                    | 00da          | ffff | ffff | C, Z, N           |             |

| RRNCF     | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100                    | 00da          | ffff | ffff | Z, N              |             |

| SETF      | f, a                            | Set f                                    | 1          | 0110                    | 100a          | ffff | ffff | None              | 1, 2        |

| SUBFWB    | f, d, a                         | Subtract f from WREG with<br>Borrow      | 1          | 0101                    | 01da          | ffff | ffff | C, DC, Z, OV, N   |             |

| SUBWF     | f, d, a                         | Subtract WREG from f                     | 1          | 0101                    | 11da          | ffff | ffff | C, DC, Z, OV, N   | 1, 2        |

| SUBWFB    |                                 | Subtract WREG from f with<br>Borrow      | 1          |                         | 10da          | ffff | ffff | C, DC, Z, OV, N   | -           |

| SWAPF     | f, d, a                         | Swap Nibbles in f                        | 1          | 0011                    | 10da          | ffff | ffff | None              | 4           |

| TSTFSZ    | f. a                            | Test f, Skip if 0                        | 1 (2 or 3) |                         | 011a          | ffff | ffff | None              | 4<br>1, 2   |

| XORWF     | , -                             | Exclusive OR WREG with f                 | 1 (2 01 3) |                         | 1011a<br>10da |      | ffff |                   | ı, <b>∠</b> |

|           |                                 | PORT register is modified as a fu        | -          |                         |               |      |      | $(2, \mathbf{N})$ |             |

#### TABLE 29-2: PIC18F66K80 FAMILY INSTRUCTION SET

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as an input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| RCA   | LL             | Relative C                                                                                          | all                                                                                                                                                                                                                                                                                                                                                      |     |          |      |  |

|-------|----------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|------|--|

| Synta | ax:            | RCALL n                                                                                             | RCALL n                                                                                                                                                                                                                                                                                                                                                  |     |          |      |  |

| Oper  | ands:          | -1024 ≤ n ≤                                                                                         | ≤ 1023                                                                                                                                                                                                                                                                                                                                                   |     |          |      |  |

| Oper  | ation:         | ( )                                                                                                 | $(PC) + 2 \rightarrow TOS, (PC) + 2 + 2n \rightarrow PC$                                                                                                                                                                                                                                                                                                 |     |          |      |  |

| Statu | s Affected:    | None                                                                                                |                                                                                                                                                                                                                                                                                                                                                          |     |          |      |  |

| Enco  | ding:          | 1101                                                                                                | 1nnn                                                                                                                                                                                                                                                                                                                                                     | nnn | in n     | nnn  |  |

| Desc  | ription:       | from the cu<br>address (P<br>stack. Ther<br>number '2r<br>have increr<br>instruction,<br>PC + 2 + 2 | Subroutine call with a jump up to 1K<br>from the current location. First, return<br>address (PC + 2) is pushed onto the<br>stack. Then, add the 2's complement<br>number '2n' to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is a<br>two-cycle instruction. |     |          |      |  |

| Word  | ls:            | 1                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                        |     |          |      |  |

| Cycle | es:            | 2                                                                                                   |                                                                                                                                                                                                                                                                                                                                                          |     |          |      |  |

| QC    | ycle Activity: |                                                                                                     |                                                                                                                                                                                                                                                                                                                                                          |     |          |      |  |

|       | Q1             | Q2                                                                                                  | Q                                                                                                                                                                                                                                                                                                                                                        | 3   | Q        | 4    |  |

|       | Decode         | Read literal<br>'n'<br>PUSH PC                                                                      | Proce<br>Data                                                                                                                                                                                                                                                                                                                                            |     | Write to | o PC |  |

|       |                | to stack                                                                                            |                                                                                                                                                                                                                                                                                                                                                          |     |          |      |  |

|       | No             | No                                                                                                  | No                                                                                                                                                                                                                                                                                                                                                       |     | Nc       | )    |  |

| RES        | ET             | Reset                      |                                                                                      |          |    |               |  |  |

|------------|----------------|----------------------------|--------------------------------------------------------------------------------------|----------|----|---------------|--|--|

| Synta      | ax:            | RESET                      | RESET                                                                                |          |    |               |  |  |

| Oper       | ands:          | None                       | None                                                                                 |          |    |               |  |  |

| Operation: |                |                            | Reset all registers and flags that are affected by a $\overline{\text{MCLR}}$ Reset. |          |    |               |  |  |

| Statu      | s Affected:    | All                        | All                                                                                  |          |    |               |  |  |

| Enco       | ding:          | 0000                       | 0000                                                                                 | 000 1111 |    | 1111          |  |  |

| Desc       | ription:       | This instruction execute a |                                                                                      |          |    |               |  |  |

| Word       | ls:            | 1                          | 1                                                                                    |          |    |               |  |  |

| Cycle      | es:            | 1                          |                                                                                      |          |    |               |  |  |

| QC         | ycle Activity: |                            |                                                                                      |          |    |               |  |  |

|            | Q1             | Q2                         | Q3                                                                                   | 8        |    | Q4            |  |  |

|            | Decode         | Start<br>reset             | No<br>operat                                                                         |          | ор | No<br>eration |  |  |

Example:

| r | Instruction |  |

|---|-------------|--|

| After Instruction |             |

|-------------------|-------------|

| Registers =       | Reset Value |

| Flags* =          | Reset Value |

RESET

Example: HERE RCALL Jump

operation

operation

operation

Before Instruction

operation

PC = Address (HERE) After Instruction PC = TOS = Address (Jump) Address (HERE + 2)

## 30.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 30.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 30.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 30.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express