Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | ECANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 8x12b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN-S (6x6)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f25k80-i-mm |

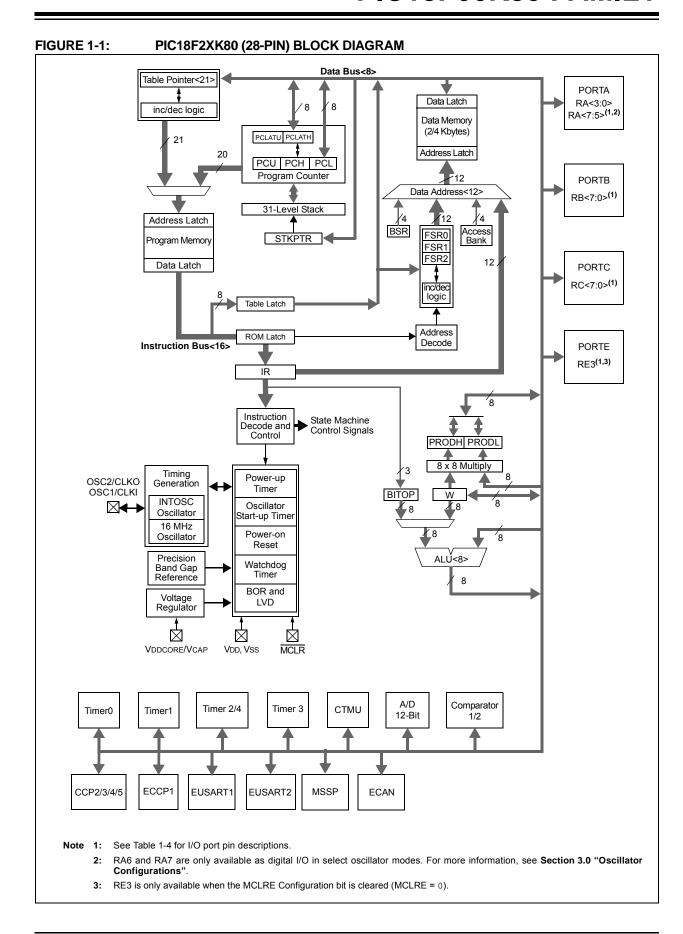

TABLE 1-1: DEVICE FEATURES FOR THE PIC18F2XK80 (28-PIN DEVICES)

| Features                             | PIC18F25K80                                                                                    | PIC18F26K80                     |  |  |  |

|--------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------|--|--|--|

| Operating Frequency                  | DC – 64 MHz                                                                                    |                                 |  |  |  |

| Program Memory (Bytes)               | 32K                                                                                            | 64K                             |  |  |  |

| Program Memory (Instructions)        | 16,384                                                                                         | 32,768                          |  |  |  |

| Data Memory (Bytes)                  |                                                                                                | 3.6K                            |  |  |  |

| Interrupt Sources                    |                                                                                                | 31                              |  |  |  |

| I/O Ports                            | Por                                                                                            | rts A, B, C                     |  |  |  |

| Parallel Communications              | Parallel S                                                                                     | Slave Port (PSP)                |  |  |  |

| Timers                               |                                                                                                | Five                            |  |  |  |

| Comparators                          |                                                                                                | Two                             |  |  |  |

| CTMU                                 |                                                                                                | Yes                             |  |  |  |

| Capture/Compare/PWM (CCP)<br>Modules |                                                                                                | Four                            |  |  |  |

| Enhanced CCP (ECCP) Modules          |                                                                                                | One                             |  |  |  |

| Serial Communications                | One MSSP and Two E                                                                             | nhanced USARTs (EUSART)         |  |  |  |

| 12-Bit Analog-to-Digital Module      | Eight Ir                                                                                       | nput Channels                   |  |  |  |

| Resets (and Delays)                  | Resets (and Delays)  POR, BOR, RESET Instruction, Stack Full, Stack Underflow, WDT (PWRT, OST) |                                 |  |  |  |

| Instruction Set                      | 75 Instructions, 83 with E                                                                     | xtended Instruction Set Enabled |  |  |  |

| Packages                             | 28-Pin QFN-S, SOIC, SPDIP and SSOP                                                             |                                 |  |  |  |

TABLE 1-2: DEVICE FEATURES FOR THE PIC18F4XK80 (40/44-PIN DEVICES)

| Features                             | PIC18F45K80                  | PIC18F46K80                        |  |  |  |

|--------------------------------------|------------------------------|------------------------------------|--|--|--|

| Operating Frequency                  | DC – 64 MHz                  |                                    |  |  |  |

| Program Memory (Bytes)               | 32K                          | 64K                                |  |  |  |

| Program Memory (Instructions)        | 16,384                       | 32,768                             |  |  |  |

| Data Memory (Bytes)                  | ;                            | 3.6K                               |  |  |  |

| Interrupt Sources                    |                              | 32                                 |  |  |  |

| I/O Ports                            | Ports A                      | , B, C, D, E                       |  |  |  |

| Parallel Communications              | Parallel Sla                 | ave Port (PSP)                     |  |  |  |

| Timers                               |                              | Five                               |  |  |  |

| Comparators                          |                              | Two                                |  |  |  |

| СТМИ                                 |                              | Yes                                |  |  |  |

| Capture/Compare/PWM (CCP)<br>Modules | ı                            | Four                               |  |  |  |

| Enhanced CCP (ECCP) Modules          |                              | One                                |  |  |  |

| Serial Communications                | One MSSP and Two En          | hanced USARTs (EUSART)             |  |  |  |

| 12-Bit Analog-to-Digital Module      | Eleven In                    | put Channels                       |  |  |  |

| Resets (and Delays)                  |                              | Stack Full, Stack Underflow, MCLR, |  |  |  |

| Instruction Set                      | 75 Instructions, 83 with Ext | tended Instruction Set Enabled     |  |  |  |

| Packages                             | 40-Pin PDIP and 4            | I4-Pin QFN and TQFP                |  |  |  |

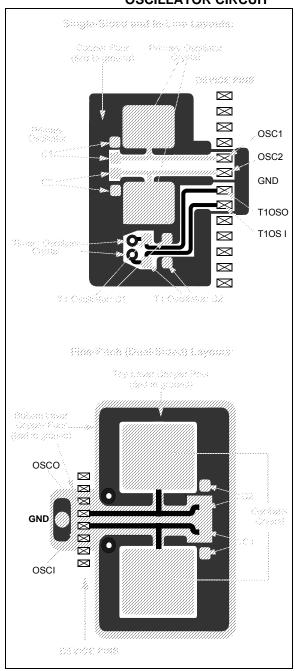

#### 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 3.0 "Oscillator Configurations"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-4. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC™ and PICmicro® Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- · AN949, "Making Your Oscillator Work"

#### 2.7 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

FIGURE 2-5: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

### REGISTER 3-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

bit 2 **HFIOFS:** HF-INTOSC Frequency Stable bit

1 = HF-INTOSC oscillator frequency is stable

0 = HF-INTOSC oscillator frequency is not stable

bit 1-0 SCS<1:0>: System Clock Select bits<sup>(4)</sup>

1x = Internal oscillator block (LF-INTOSC, MF-INTOSC or HF-INTOSC)

01 = SOSC oscillator

00 = Default primary oscillator (OSC1/OSC2 or HF-INTOSC with or without PLL; defined by the FOSC<3:0> Configuration bits, CONFIG1H<3:0>)

Note 1: The Reset state depends on the state of the IESO Configuration bit (CONFIG1H<7>).

- 2: Modifying these bits will cause an immediate clock frequency switch if the internal oscillator is providing the device clocks.

- 3: The source is selected by the INTSRC bit (OSCTUNE<7>).

- 4: Modifying these bits will cause an immediate clock source switch.

- 5: INTSRC = OSCTUNE<7> and MFIOSEL = OSCCON2<0>.

- **6:** This is the lowest power option for an internal source.

#### REGISTER 3-2: OSCCON2: OSCILLATOR CONTROL REGISTER 2

| U-0   | R-0     | U-0 | R/W-1                  | R/W-0  | U-0 | R-x    | R/W-0   |

|-------|---------|-----|------------------------|--------|-----|--------|---------|

| _     | SOSCRUN | _   | SOSCDRV <sup>(1)</sup> | SOSCGO | _   | MFIOFS | MFIOSEL |

| bit 7 |         |     |                        |        |     |        | bit 0   |

|   | _ | ~ | _ | n | ᆈ |  |

|---|---|---|---|---|---|--|

| ᆫ | u | u | u | H | d |  |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 Unimplemented: Read as '0'

bit 6 SOSCRUN: SOSC Run Status bit

1 = System clock comes from a secondary SOSC

0 = System clock comes from an oscillator other than SOSC

bit 5 **Unimplemented:** Read as '0'

bit 4 **SOSCDRV:** Secondary Oscillator Drive Control bit<sup>(1)</sup>

1 = High-power SOSC circuit is selected

0 = Low/high-power select is done via the SOSCSEL<1:0> Configuration bits

bit 3 SOSCGO: Oscillator Start Control bit

1 = Oscillator is running even if no other sources are requesting it.

0 = Oscillator is shut off if no other sources are requesting it (When the SOSC is selected to run from a digital clock input, rather than an external crystal, this bit has no effect.)

bit 2 **Unimplemented:** Read as '0'

bit 1 MFIOFS: MF-INTOSC Frequency Stable bit

1 = MF-INTOSC is stable

0 = MF-INTOSC is not stable

bit 0 MFIOSEL: MF-INTOSC Select bit

1 = MF-INTOSC is used in place of HF-INTOSC frequencies of 500 kHz, 250 kHz and 31.25 kHz

0 = MF-INTOSC is not used

**Note 1:** When SOSC is selected to run from a digital clock input, rather than an external crystal, this bit has no effect.

# 3.6.3 INTERNAL OSCILLATOR OUTPUT FREQUENCY AND TUNING

The internal oscillator block is calibrated at the factory to produce an INTOSC output frequency of 16 MHz. It can be adjusted in the user's application by writing to TUN<5:0> (OSCTUNE<5:0>) in the OSCTUNE register (Register 3-3).

When the OSCTUNE register is modified, the INTOSC (HF-INTOSC and MF-INTOSC) frequency will begin shifting to the new frequency. The oscillator will require some time to stabilize. Code execution continues during this shift and there is no indication that the shift has occurred.

The LF-INTOSC oscillator operates independently of the HF-INTOSC or the MF-INTOSC source. Any changes in the HF-INTOSC or the MF-INTOSC source, across voltage and temperature, are not necessarily reflected by changes in LF-INTOSC or vice versa. The frequency of LF-INTOSC is not affected by OSCTUNE.

### 3.6.4 INTOSC FREQUENCY DRIFT

The INTOSC frequency may drift as VDD or temperature changes and can affect the controller operation in a variety of ways. It is possible to adjust the INTOSC frequency by modifying the value in the OSCTUNE register. Depending on the device, this may have no effect on the LF-INTOSC clock source frequency.

Tuning INTOSC requires knowing when to make the adjustment, in which direction it should be made, and in some cases, how large a change is needed. Three compensation techniques are shown here.

#### 3.6.4.1 Compensating with the EUSARTx

An adjustment may be required when the EUSARTx begins to generate framing errors or receives data with errors while in Asynchronous mode. Framing errors indicate that the device clock frequency is too high. To adjust for this, decrement the value in OSCTUNE to reduce the clock frequency. On the other hand, errors in data may suggest that the clock speed is too low. To compensate, increment OSCTUNE to increase the clock frequency.

#### 3.6.4.2 Compensating with the Timers

This technique compares device clock speed to some reference clock. Two timers may be used; one timer is clocked by the peripheral clock, while the other is clocked by a fixed reference source, such as the SOSC oscillator.

Both timers are cleared, but the timer clocked by the reference generates interrupts. When an interrupt occurs, the internally clocked timer is read and both timers are cleared. If the internally clocked timer value is much greater than expected, then the internal oscillator block is running too fast. To adjust for this, decrement the OSCTUNE register.

# 3.6.4.3 Compensating with the CCP Module in Capture Mode

A CCP module can use free-running Timer1 (or Timer3), clocked by the internal oscillator block and an external event with a known period (i.e., AC power frequency). The time of the first event is captured in the CCPRxH:CCPRxL registers and is recorded for use later. When the second event causes a capture, the time of the first event is subtracted from the time of the second event. Since the period of the external event is known, the time difference between events can be calculated.

If the measured time is much greater than the calculated time, the internal oscillator block is running too fast. To compensate, decrement the OSCTUNE register. If the measured time is much less than the calculated time, the internal oscillator block is running too slow. To compensate, increment the OSCTUNE register.

#### 3.7 Reference Clock Output

In addition to the Fosc/4 clock output, in certain oscillator modes, the device clock in the PIC18F66K80 family can also be configured to provide a reference clock output signal to a port pin. This feature is available in all oscillator configurations and allows the user to select a greater range of clock submultiples to drive external devices in the application.

This reference clock output is controlled by the REFOCON register (Register 3-4). Setting the ROON bit (REFOCON<7>) makes the clock signal available on the REFO (RC3) pin. The RODIV<3:0> bits enable the selection of 16 different clock divider options.

The ROSSLP and ROSEL bits (REFOCON<5:4>) control the availability of the reference output during Sleep mode. The ROSEL bit determines if the oscillator on OSC1 and OSC2, or the current system clock source, is used for the reference clock output. The ROSSLP bit determines if the reference source is available on RE3 when the device is in Sleep mode.

To use the reference clock output in Sleep mode, both the ROSSLP and ROSEL bits must be set. The device clock must also be configured for an EC or HS mode. If not, the oscillator on OSC1 and OSC2 will be powered down when the device enters Sleep mode. Clearing the ROSEL bit allows the reference output frequency to change as the system clock changes during any clock switches.

### 6.1 Program Memory Organization

PIC18 microcontrollers implement a 21-bit Program Counter (PC) that is capable of addressing a 2-Mbyte program memory space. Accessing a location between the upper boundary of the physically implemented memory and the 2-Mbyte address will return all '0's (a NOP instruction).

The entire PIC18F66K80 family offers a range of on-chip Flash program memory sizes, from 32 Kbytes (16,384 single-word instructions) to 64 Kbytes (32,768 single-word instructions).

- PIC18F25K80, PIC18F45K80 and PIC18F65K80 32 Kbytes of Flash memory, storing up to 16,384 single-word instructions

- PIC18F26K80, PIC18F46K80 and PIC18F66K80 64 Kbytes of Flash memory, storing up to 32,768 single-word instructions

The program memory maps for individual family members are shown in Figure 6-1.

#### 6.1.1 HARD MEMORY VECTORS

All PIC18 devices have a total of three hard-coded return vectors in their program memory space. The Reset vector address is the default value to which the Program Counter returns on all device Resets. It is located at 0000h.

PIC18 devices also have two interrupt vector addresses for handling high-priority and low-priority interrupts. The high-priority interrupt vector is located at 0008h and the low-priority interrupt vector is at 0018h. The locations of these vectors are shown, in relation to the program memory map, in Figure 6-2.

FIGURE 6-2: HARD VECTOR FOR PIC18F66K80 FAMILY DEVICES

| [      | Reset Vector                   | 0000h   |

|--------|--------------------------------|---------|

|        | High-Priority Interrupt Vector | 0008h   |

|        | Low-Priority Interrupt Vector  | 0018h   |

|        | On-Chip<br>Program Memory      |         |

|        | Read '0'                       | 1FFFFFh |

| Legend | : (Top of Memory) represent    |         |

Figure 6-1 for device-specific values). Shaded area represents unimplemented memory. Areas are not shown to scale.

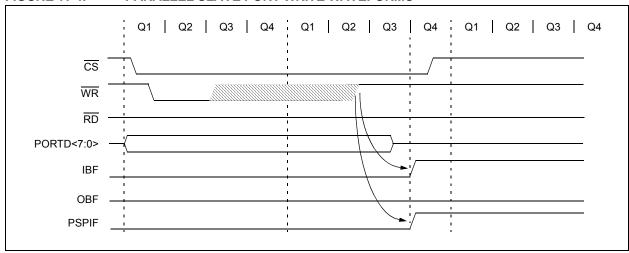

#### REGISTER 11-5: PSPCON: PARALLEL SLAVE PORT CONTROL REGISTER

| R-0   | R-0 | R/W-0 | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-------|---------|-----|-----|-----|-------|

| IBF   | OBF | IBOV  | PSPMODE | _   | _   | _   | _     |

| bit 7 |     |       |         |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 IBF: Input Buffer Full Status bit

1 = A word has been received and is waiting to be read by the CPU

0 = No word has been received

bit 6 OBF: Output Buffer Full Status bit

1 = The output buffer still holds a previously written word

0 = The output buffer has been read

bit 5 IBOV: Input Buffer Overflow Detect bit

1 = A write occurred when a previously input word had not been read (must be cleared in software)

0 = No overflow occurred

bit 4 **PSPMODE:** Parallel Slave Port Mode Select bit

1 = Parallel Slave Port mode0 = General Purpose I/O mode

bit 3-0 **Unimplemented:** Read as '0'

#### FIGURE 11-4: PARALLEL SLAVE PORT WRITE WAVEFORMS

#### 18.2 CTMU Operation

The CTMU works by using a fixed current source to charge a circuit. The type of circuit depends on the type of measurement being made.

In the case of charge measurement, the current is fixed and the amount of time the current is applied to the circuit is fixed. The amount of voltage read by the A/D becomes a measurement of the circuit's capacitance.

In the case of time measurement, the current, as well as the capacitance of the circuit, is fixed. In this case, the voltage read by the A/D is representative of the amount of time elapsed from the time the current source starts and stops charging the circuit.

If the CTMU is being used as a time delay, both capacitance and current source are fixed, as well as the voltage supplied to the comparator circuit. The delay of a signal is determined by the amount of time it takes the voltage to charge to the comparator threshold voltage.

#### 18.2.1 THEORY OF OPERATION

The operation of the CTMU is based on the equation for charge:

$$I = C \cdot \frac{dV}{dT}$$

More simply, the amount of charge measured in coulombs in a circuit is defined as current in amperes (I) multiplied by the amount of time in seconds that the current flows (t). Charge is also defined as the capacitance in farads (C) multiplied by the voltage of the circuit (V). It follows that:

$$I \bullet t = C \bullet V$$

The CTMU module provides a constant, known current source. The A/D Converter is used to measure (V) in the equation, leaving two unknowns: capacitance (C) and time (t). The above equation can be used to calculate capacitance or time, by either the relationship using the known fixed capacitance of the circuit:

$$t = (C \cdot V)/I$$

or by:

$$C = (I \cdot t)/V$$

using a fixed time that the current source is applied to the circuit.

#### 18.2.2 CURRENT SOURCE

At the heart of the CTMU is a precision current source, designed to provide a constant reference for measurements. The level of current is user-selectable across three ranges, or a total of two orders of magnitude, with the ability to trim the output in ±2% increments (nominal). The current range is selected by the IRNG<1:0> bits (CTMUICON<1:0>), with a value of '01' representing the lowest range.

Current trim is provided by the ITRIM<5:0> bits (CTMUICON<7:2>). These six bits allow trimming of the current source in steps of approximately 2% per step. Half of the range adjusts the current source positively and the other half reduces the current source. A value of '000000' is the neutral position (no change). A value of '100001' is the maximum negative adjustment (approximately -62%) and '011111' is the maximum positive adjustment (approximately +62%).

#### 18.2.3 EDGE SELECTION AND CONTROL

CTMU measurements are controlled by edge events occurring on the module's two input channels. Each channel, referred to as Edge 1 and Edge 2, can be configured to receive input pulses from one of the edge input pins (CTED1 and CTED2) or CCPx Special Event Triggers (ECCP1 and CCP2). The input channels are level-sensitive, responding to the instantaneous level on the channel rather than a transition between levels. The inputs are selected using the EDG1SEL and EDG2SEL bit pairs (CTMUCONL<3:2>, 6:5>).

In addition to source, each channel can be configured for event polarity using the EDGE2POL and EDGE1POL bits (CTMUCONL<7,4>). The input channels can also be filtered for an edge event sequence (Edge 1 occurring before Edge 2) by setting the EDGSEQEN bit (CTMUCONH<2>).

#### 18.2.4 EDGE STATUS

The CTMUCONL register also contains two status bits, EDG2STAT and EDG1STAT (CTMUCONL<1:0>). Their primary function is to show if an edge response has occurred on the corresponding channel. The CTMU automatically sets a particular bit when an edge response is detected on its channel. The level-sensitive nature of the input channels also means that the status bits become set immediately if the channel's configuration is changed and matches the channel's current state.

The module uses the edge status bits to control the current source output to external analog modules (such as the A/D Converter). Current is only supplied to external modules when only one (not both) of the status bits is set. Current is shut off when both bits are either set or cleared. This allows the CTMU to measure current only during the interval between edges. After both status bits are set, it is necessary to clear them before another measurement is taken. Both bits should be cleared simultaneously, if possible, to avoid re-enabling the CTMU current source.

In addition to being set by the CTMU hardware, the edge status bits can also be set by software. This permits a user application to manually enable or disable the current source. Setting either (but not both) of the bits enables the current source. Setting or clearing both bits at once disables the source.

#### 19.3 Compare Mode

In Compare mode, the 16-bit CCPRx register value is constantly compared against the Timer register pair value selected in the CCPTMR register. When a match occurs, the CCPx pin can be:

- · Driven high

- · Driven low

- Toggled (high-to-low or low-to-high)

- Unchanged (that is, reflecting the state of the I/O latch)

The action on the pin is based on the value of the mode select bits (CCPxM<3:0>). At the same time, the interrupt flag bit, CCPxIF, is set.

Figure 19-2 gives the Compare mode block diagram

#### 19.3.1 CCP PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the appropriate TRIS bit.

Note: Clearing the CCPxCON register will force the corresponding CCPx compare output latch (depending on device configuration) to the default low level. This is not the PORTx data latch.

#### 19.3.2 TIMER1/3 MODE SELECTION

If the CCPx module is using the compare feature in conjunction with any of the Timer1/3 timers, the timers must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the compare operation may not work.

**Note:** Details of the timer assignments for the CCPx modules are given in Table 19-2.

#### 19.3.3 SOFTWARE INTERRUPT MODE

When the Generate Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPx pin is not affected. Only a CCP interrupt is generated, if enabled, and the CCPxIE bit is set.

#### 19.3.4 SPECIAL EVENT TRIGGER

All CCP modules are equipped with a Special Event Trigger. This is an internal hardware signal generated in Compare mode to trigger actions by other modules. The Special Event Trigger is enabled by selecting the Compare Special Event Trigger mode bits (CCPxM<3:0> = 1011).

For either CCPx module, the Special Event Trigger resets the Timer register pair for whichever timer resource is currently assigned as the module's time base. This allows the CCPRx registers to serve as a programmable Period register for either timer.

#### 21.3.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register 1 (SSPCON1)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON1 and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON1 register is readable and writable. The lower 6 bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write.

SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together, create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not double-buffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

#### REGISTER 21-1: SSPSTAT: MSSP STATUS REGISTER (SPI MODE)

| R/W-0 | R/W-0              | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |

|-------|--------------------|-----|-----|-----|-----|-----|-------|

| SMP   | CKE <sup>(1)</sup> | D/Ā | Р   | S   | R/W | UA  | BF    |

| bit 7 |                    |     |     |     |     |     | bit 0 |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7 SMP: Sample bit

SPI Master mode:

1 = Input data is sampled at the end of data output time

0 = Input data is sampled at the middle of data output time

SPI Slave mode:

SMP must be cleared when SPI is used in Slave mode.

bit 6 CKE: SPI Clock Select bit<sup>(1)</sup>

1 = Transmit occurs on transition from active to Idle clock state

0 = Transmit occurs on transition from Idle to active clock state

bit 5 D/A: Data/Address bit

Used in  $I^2C^{TM}$  mode only.

bit 4 P: Stop bit

Used in I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled; SSPEN is cleared.

bit 3 S: Start bit

Used in I<sup>2</sup>C mode only.

bit 2 R/W: Read/Write Information bit

Used in I<sup>2</sup>C mode only.

bit 1 **UA:** Update Address bit

Used in I<sup>2</sup>C mode only.

bit 0 **BF:** Buffer Full Status bit (Receive mode only)

1 = Receive is complete, SSPBUF is full

0 = Receive is not complete, SSPBUF is empty

**Note 1:** Polarity of clock state is set by the CKP bit (SSPCON1<4>).

#### 21.4.2 OPERATION

The MSSP module functions are enabled by setting the MSSP Enable bit, SSPEN (SSPCON1<5>).

The SSPCON1 register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON1<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Master mode, clock

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Firmware Controlled Master mode, slave is Idle

Selection of any I<sup>2</sup>C mode with the SSPEN bit set forces the SCL and SDA pins to be open-drain, provided these pins are programmed as inputs by setting the appropriate TRISC bit. To ensure proper operation of the module, pull-up resistors must be provided externally to the SCL and SDA pins.

#### 21.4.3 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The MSSP module will override the input state with the output data when required (slave-transmitter).

The I<sup>2</sup>C Slave mode hardware will always generate an interrupt on an address match. Address masking will allow the hardware to generate an interrupt for more than one address (up to 31 in 7-bit addressing and up to 63 in 10-bit addressing). Through the mode select bits, the user can also choose to interrupt on Start and Stop bits.

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge (ACK) pulse and load the SSPBUF register with the received value currently in the SSPSR register.

Any combination of the following conditions will cause the MSSP module not to give this  $\overline{ACK}$  pulse:

- The Buffer Full bit, BF (SSPSTAT<0>), was set before the transfer was received.

- The overflow bit, SSPOV (SSPCON1<6>), was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit, SSPIF, is set. The BF bit is cleared by reading the SSPBUF register, while bit, SSPOV, is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the I<sup>2</sup>C specification, as well as the requirement of the MSSP module, are shown in timing Parameter 100 and Parameter 101.

#### 21.4.3.1 Addressing

Once the MSSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8 bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register, SSPSR<7:1>, is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- The SSPSR register value is loaded into the SSPBUF register.

- 2. The Buffer Full bit, BF, is set.

- 3. An ACK pulse is generated.

- 4. The MSSP Interrupt Flag bit, SSPIF, is set (and interrupt is generated, if enabled) on the falling edge of the ninth SCL pulse.

In 10-Bit Addressing mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. The R/W (SSPSTAT<2>) bit must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '11110 A9 A8 0', where 'A9' and 'A8' are the two MSbs of the address. The sequence of events for 10-bit addressing is as follows, with Steps 7 through 9 for the slave-transmitter:

- 1. Receive first (high) byte of address (bits, SSPIF, BF and UA, are set on address match).

- Update the SSPADD register with second (low) byte of address (clears bit, UA, and releases the SCL line).

- 3. Read the SSPBUF register (clears bit, BF) and clear flag bit, SSPIF.

- Receive second (low) byte of address (bits, SSPIF, BF and UA, are set).

- 5. Update the SSPADD register with the first (high) byte of address. If match releases SCL line, this will clear bit, UA.

- Read the SSPBUF register (clears bit, BF) and clear flag bit SSPIF.

- 7. Receive Repeated Start condition.

- Receive first (high) byte of address (bits, SSPIF and BF, are set).

- 9. Read the SSPBUF register (clears bit, BF) and clear flag bit, SSPIF.

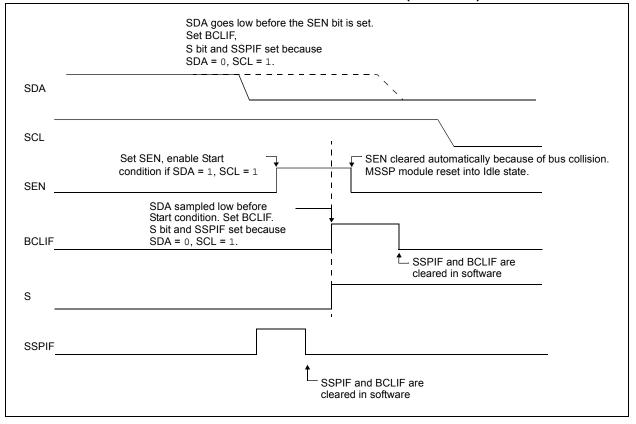

# 21.4.17.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- SDA or SCL is sampled low at the beginning of the Start condition (Figure 21-28).

- SCL is sampled low before SDA is asserted low (Figure 21-29).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- · the Start condition is aborted,

- · the BCLIF flag is set and

- the MSSP module is reset to its inactive state (Figure 21-28)

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 21-30). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to 0. If the SCL pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

FIGURE 21-28: BUS COLLISION DURING START CONDITION (SDA ONLY)

TABLE 21-4: REGISTERS ASSOCIATED WITH I<sup>2</sup>C™ OPERATION

| Name                  | Bit 7     | Bit 6          | Bit 5                                                    | Bit 4                 | Bit 3                 | Bit 2                 | Bit 1                 | Bit 0   |

|-----------------------|-----------|----------------|----------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|---------|

| INTCON                | GIE/GIEH  | PEIE/GIEL      | TMR0IE                                                   | INT0IE                | RBIE                  | TMR0IF                | INT0IF                | RBIF    |

| PIR1                  | PSPIF     | ADIF           | RC1IF                                                    | TX1IF                 | SSPIF                 | TMR1GIF               | TMR2IF                | TMR1IF  |

| PIE1                  | PSPIE     | ADIE           | RC1IE                                                    | TX1IE                 | SSPIE                 | TMR1GIE               | TMR2IE                | TMR1IE  |

| IPR1                  | PSPIP     | ADIP           | RC1IP                                                    | TX1IP                 | SSPIP                 | TMR1GIP               | TMR2IP                | TMR1IP  |

| PIR2                  | OSCFIF    | _              | _                                                        | _                     | BCLIF                 | HLVDIF                | TMR3IF                | TMR3GIF |

| PIE2                  | OSCFIE    | _              | _                                                        | _                     | BCLIE                 | HLVDIE                | TMR3IE                | TMR3GIE |

| IPR2                  | OSCFIP    | _              | _                                                        | _                     | BCLIP                 | HLVDIP                | TMR3IP                | TMR3GIP |

| TRISC                 | TRISC7    | TRISC6         | TRISC5                                                   | TRISC4                | TRISC3                | TRISC2                | TRISC1                | TRISC0  |

| SSPBUF                | MSSP Rece | ive Buffer/Tra | ansmit Regist                                            | er                    |                       |                       |                       |         |

| SSPADD                |           |                | (I <sup>2</sup> C™ Slave<br>d Register (I <sup>2</sup> 0 |                       | de)                   |                       |                       |         |

| SSPMSK <sup>(1)</sup> | MSK7      | MSK6           | MSK5                                                     | MSK4                  | MSK3                  | MSK2                  | MSK1                  | MSK0    |

| SSPCON1               | WCOL      | SSPOV          | SSPEN                                                    | CKP                   | SSPM3                 | SSPM2                 | SSPM1                 | SSPM0   |

| SSPCON2               | GCEN      | ACKSTAT        | ACKDT                                                    | ACKEN                 | RCEN                  | PEN                   | RSEN                  | SEN     |

|                       | GCEN      | ACKSTAT        | ADMSK5 <sup>(2)</sup>                                    | ADMSK4 <sup>(2)</sup> | ADMSK3 <sup>(2)</sup> | ADMSK2 <sup>(2)</sup> | ADMSK1 <sup>(2)</sup> | SEN     |

| SSPSTAT               | SMP       | CKE            | D/A                                                      | Р                     | S                     | R/W                   | UA                    | BF      |

| PMD0                  | CCP5MD    | CCP4MD         | CCP3MD                                                   | CCP2MD                | CCP1MD                | UART2MD               | UART1MD               | SSPMD   |

| ODCON                 | SSPOD     | CCP5OD         | CCP4OD                                                   | CCP3OD                | CCP2OD                | CCP10D                | U2OD                  | U10D    |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the MSSP module in  $I^2C^{TM}$  mode.

Note 1: SSPMSK shares the same address in SFR space as SSPADD, but is only accessible in certain I<sup>2</sup>C™ Slave operating modes in 7-Bit Masking mode. See **Section 21.4.3.4 "7-Bit Address Masking Mode"** for more details.

2: Alternate bit definitions for use in I<sup>2</sup>C Slave mode operations only.

### 24.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional, if enabled. This interrupt will wake-up the device from Sleep mode, when enabled. Each operational comparator will consume additional current.

To minimize power consumption while in Sleep mode, turn off the comparators (CON = 0) before entering Sleep. If the device wakes up from Sleep, the contents of the CMxCON register are not affected.

#### 24.8 Effects of a Reset

A device Reset forces the CMxCON registers to their Reset state. This forces both comparators and the voltage reference to the OFF state.

TABLE 24-3: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

| Name   | Bit 7    | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

|--------|----------|-----------|---------|---------|---------|---------|--------|--------|

| INTCON | GIE/GIEH | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF  | INT0IF | RBIF   |

| CM1CON | CON      | COE       | CPOL    | EVPOL1  | EVPOL0  | CREF    | CCH1   | CCH0   |

| CM2CON | CON      | COE       | CPOL    | EVPOL1  | EVPOL0  | CREF    | CCH1   | CCH0   |

| CVRCON | CVREN    | CVROE     | CVRSS   | CVR4    | CVR3    | CVR2    | CVR1   | CVR0   |

| CMSTAT | CMP2OUT  | CMP1OUT   | _       | _       | _       | _       | _      | _      |

| PIR4   | TMR4IF   | EEIF      | CMP2IF  | CMP1IF  | _       | CCP5IF  | CCP4IF | CCP3IF |

| PIE4   | TMR4IE   | EEIE      | CMP2IE  | CMP1IE  | _       | CCP5IE  | CCP4IE | CCP3IE |

| IPR4   | TMR4IP   | EEIP      | CMP2IP  | CMP1IP  | _       | CCP5IP  | CCP4IP | CCP3IP |

| ANCON0 | ANSEL7   | ANSEL6    | ANSEL5  | ANSEL4  | ANSEL3  | ANSEL2  | ANSEL1 | ANSEL0 |

| ANCON1 | _        | ANSEL14   | ANSEL13 | ANSEL12 | ANSEL11 | ANSEL10 | ANSEL9 | ANSEL8 |

| PMD2   | _        | _         | _       | _       | MODMD   | ECANMD  | CMP2MD | CMP1MD |

**Legend:** — = unimplemented, read as '0'.

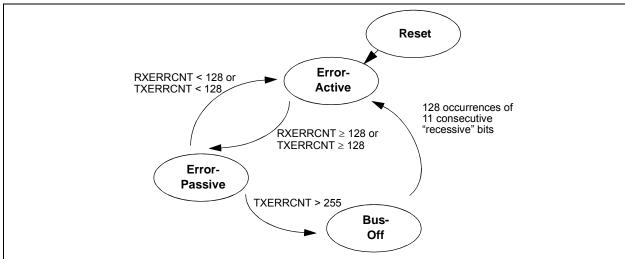

The PIC18F66K80 family devices are error-active if both error counters are below the error-passive limit of 128. They are error-passive if at least one of the error counters equals or exceeds 128. They go to bus-off if the transmit error counter equals or exceeds the bus-off limit of 256. The devices remain in this state until the bus-off recovery sequence is finished. The bus-off recovery sequence consists of 128 occurrences of 11 consecutive recessive bits (see Figure 27-8). Note that the CAN module, after going bus-off, will recover back to error-active without any intervention by the

MCU if the bus remains Idle for 128 x 11 bit times. If this is not desired, the error Interrupt Service Routine should address this. The current Error mode of the CAN module can be read by the MCU via the COMSTAT register.

Additionally, there is an Error State Warning flag bit, EWARN, which is set if at least one of the error counters equals or exceeds the error warning limit of 96. EWARN is reset if both error counters are less than the error warning limit.

FIGURE 27-8: ERROR MODES STATE DIAGRAM

#### 27.15 CAN Interrupts

The module has several sources of interrupts. Each of these interrupts can be individually enabled or disabled. The PIR5 register contains interrupt flags. The PIE5 register contains the enables for the 8 main interrupts. A special set of read-only bits in the CANSTAT register, the ICODE bits, can be used in combination with a jump table for efficient handling of interrupts.

All interrupts have one source, with the exception of the error interrupt and buffer interrupts in Mode 1 and 2. Any of the error interrupt sources can set the error interrupt flag. The source of the error interrupt can be determined by reading the Communication Status register, COMSTAT. In Mode 1 and 2, there are two interrupt enable/disable and flag bits – one for all transmit buffers and the other for all receive buffers.

The interrupts can be broken up into two categories: receive and transmit interrupts.

The receive related interrupts are:

- · Receive Interrupts

- · Wake-up Interrupt

- · Receiver Overrun Interrupt

- · Receiver Warning Interrupt

- Receiver Error-Passive Interrupt

The transmit related interrupts are:

- Transmit Interrupts

- · Transmitter Warning Interrupt

- Transmitter Error-Passive Interrupt

- · Bus-Off Interrupt

TABLE 29-2: PIC18F66K80 FAMILY INSTRUCTION SET

| Mnemonic,<br>Operands |            | Decembries                               | Cualas     | 16-E | Bit Instr | uction V | Vord | Status          | Notes      |

|-----------------------|------------|------------------------------------------|------------|------|-----------|----------|------|-----------------|------------|

|                       |            | Description                              | Cycles     | MSb  |           |          | LSb  | Affected        | Notes      |

| BYTE-ORI              | ENTED      | OPERATIONS                               |            |      |           |          |      |                 |            |

| ADDWF                 | f, d, a    | Add WREG and f                           | 1          | 0010 | 01da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| ADDWFC                | f, d, a    | Add WREG and Carry bit to f              | 1          | 0010 | 00da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| ANDWF                 | f, d, a    | AND WREG with f                          | 1          | 0001 | 01da      | ffff     | ffff | Z, N            | 1,2        |

| CLRF                  | f, a       | Clear f                                  | 1          | 0110 | 101a      | ffff     | ffff | Z               | 2          |

| COMF                  | f, d, a    | Complement f                             | 1          | 0001 | 11da      | ffff     | ffff | Z, N            | 1, 2       |

| CPFSEQ                | f, a       | Compare f with WREG, Skip =              | 1 (2 or 3) | 0110 | 001a      | ffff     | ffff | None            | 4          |

| CPFSGT                | f, a       | Compare f with WREG, Skip >              | 1 (2 or 3) | 0110 | 010a      | ffff     | ffff | None            | 4          |

| CPFSLT                | f, a       | Compare f with WREG, Skip <              | 1 (2 or 3) | 0110 | 000a      | ffff     | ffff | None            | 1, 2       |

| DECF                  | f, d, a    | Decrement f                              | 1          | 0000 | 01da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ                | f, d, a    | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010 | 11da      | ffff     | ffff | None            | 1, 2, 3, 4 |

| DCFSNZ                | f, d, a    | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100 | 11da      | ffff     | ffff | None            | 1, 2       |

| INCF                  | f, d, a    | Increment f                              | 1          | 0010 | 10da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| INCFSZ                | f, d, a    | Increment f, Skip if 0                   | 1 (2 or 3) | 0011 | 11da      | ffff     | ffff | None            | 4          |

| INFSNZ                | f, d, a    | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100 | 10da      | ffff     | ffff | None            | 1, 2       |

| IORWF                 | f, d, a    | Inclusive OR WREG with f                 | 1          | 0001 | 00da      | ffff     | ffff | Z, N            | 1, 2       |

| MOVF                  | f, d, a    | Move f                                   | 1          | 0101 | 00da      | ffff     | ffff | Z, N            | 1          |

| MOVFF                 | $f_s, f_d$ | Move f <sub>s</sub> (source) to 1st word | 2          | 1100 | ffff      | ffff     | ffff | None            |            |

|                       | 0 0        | f <sub>d</sub> (destination) 2nd word    |            | 1111 | ffff      | ffff     | ffff |                 |            |

| MOVWF                 | f, a       | Move WREG to f                           | 1          | 0110 | 111a      | ffff     | ffff | None            |            |

| MULWF                 | f, a       | Multiply WREG with f                     | 1          | 0000 | 001a      | ffff     | ffff | None            | 1, 2       |

| NEGF                  | f, a       | Negate f                                 | 1          | 0110 | 110a      | ffff     | ffff | C, DC, Z, OV, N |            |

| RLCF                  | f, d, a    | Rotate Left f through Carry              | 1          | 0011 | 01da      | ffff     | ffff | C, Z, N         | 1, 2       |

| RLNCF                 | f, d, a    | Rotate Left f (No Carry)                 | 1          | 0100 | 01da      | ffff     | ffff | Z, N            |            |

| RRCF                  | f, d, a    | Rotate Right f through Carry             | 1          | 0011 | 00da      | ffff     | ffff | C, Z, N         |            |

| RRNCF                 | f, d, a    | Rotate Right f (No Carry)                | 1          | 0100 | 00da      | ffff     | ffff | Z, N            |            |

| SETF                  | f, a       | Set f                                    | 1          | 0110 | 100a      | ffff     | ffff | None            | 1, 2       |

| SUBFWB                | f, d, a    | Subtract f from WREG with Borrow         | 1          | 0101 | 01da      | ffff     | ffff | C, DC, Z, OV, N |            |

| SUBWF                 | f, d, a    | Subtract WREG from f                     | 1          | 0101 | 11da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| SUBWFB                |            | Subtract WREG from f with                | 1          |      | 10da      | ffff     |      | C, DC, Z, OV, N |            |

|                       | ,,         | Borrow                                   |            |      |           |          |      | , -, -,,        |            |

| SWAPF                 | f, d, a    | Swap Nibbles in f                        | 1          | 0011 | 10da      | ffff     | ffff | None            | 4          |

| TSTFSZ                | f, a       | Test f, Skip if 0                        | 1 (2 or 3) | 0110 | 011a      | ffff     | ffff | None            | 1, 2       |

| XORWF                 | f, d, a    | Exclusive OR WREG with f                 | 1          | -    | 10da      | ffff     | ffff |                 | ,          |

|                       |            | l ·                                      |            |      |           |          |      | <u>'</u>        |            |

Note 1: When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as an input and is driven low by an external device, the data will be written back with a '0'.

- 2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

- **3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

- **4:** Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

TABLE 29-2: PIC18F66K80 FAMILY INSTRUCTION SET (CONTINUED)

| Mnemonic,<br>Operands |                                         | Description                     | Cycles | 16-Bit Instruction Word |      |      |          | Status          | Notes |

|-----------------------|-----------------------------------------|---------------------------------|--------|-------------------------|------|------|----------|-----------------|-------|

|                       |                                         | Description                     | Cycles | MSb                     | LSb  |      | Affected | Notes           |       |

| LITERAL OPERATIONS    |                                         |                                 |        |                         |      |      |          |                 |       |

| ADDLW                 | k                                       | Add Literal and WREG            | 1      | 0000                    | 1111 | kkkk | kkkk     | C, DC, Z, OV, N |       |

| ANDLW                 | k                                       | AND Literal with WREG           | 1      | 0000                    | 1011 | kkkk | kkkk     | Z, N            |       |

| IORLW                 | k                                       | Inclusive OR Literal with WREG  | 1      | 0000                    | 1001 | kkkk | kkkk     | Z, N            |       |

| LFSR                  | f, k                                    | Move literal (12-bit) 2nd word  | 2      | 1110                    | 1110 | 00ff | kkkk     | None            |       |

|                       |                                         | to FSR(f) 1st word              |        | 1111                    | 0000 | kkkk | kkkk     |                 |       |

| MOVLB                 | k                                       | Move Literal to BSR<3:0>        | 1      | 0000                    | 0001 | 0000 | kkkk     | None            |       |

| MOVLW                 | k                                       | Move Literal to WREG            | 1      | 0000                    | 1110 | kkkk | kkkk     | None            |       |

| MULLW                 | k                                       | Multiply Literal with WREG      | 1      | 0000                    | 1101 | kkkk | kkkk     | None            |       |

| RETLW                 | k                                       | Return with Literal in WREG     | 2      | 0000                    | 1100 | kkkk | kkkk     | None            |       |

| SUBLW                 | k                                       | Subtract WREG from Literal      | 1      | 0000                    | 1000 | kkkk | kkkk     | C, DC, Z, OV, N |       |

| XORLW                 | k                                       | Exclusive OR Literal with WREG  | 1      | 0000                    | 1010 | kkkk | kkkk     | Z, N            |       |

| DATA ME               | DATA MEMORY ↔ PROGRAM MEMORY OPERATIONS |                                 |        |                         |      |      |          |                 |       |

| TBLRD*                |                                         | Table Read                      | 2      | 0000                    | 0000 | 0000 | 1000     | None            |       |

| TBLRD*+               |                                         | Table Read with Post-Increment  |        | 0000                    | 0000 | 0000 | 1001     | None            |       |

| TBLRD*-               |                                         | Table Read with Post-Decrement  |        | 0000                    | 0000 | 0000 | 1010     | None            |       |

| TBLRD+*               |                                         | Table Read with Pre-Increment   |        | 0000                    | 0000 | 0000 | 1011     | None            |       |

| TBLWT*                |                                         | Table Write                     | 2      | 0000                    | 0000 | 0000 | 1100     | None            |       |

| TBLWT*+               |                                         | Table Write with Post-Increment |        | 0000                    | 0000 | 0000 | 1101     | None            |       |

| TBLWT*-               |                                         | Table Write with Post-Decrement |        | 0000                    | 0000 | 0000 | 1110     | None            |       |

| TBLWT+*               |                                         | Table Write with Pre-Increment  |        | 0000                    | 0000 | 0000 | 1111     | None            |       |

- Note 1: When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as an input and is driven low by an external device, the data will be written back with a '0'.

- 2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

- **3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

- **4:** Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

Set f

| RRNCF                                                                                             | Rotate Rig                                          | Rotate Right f (No Carry)                               |      |      |  |  |

|---------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------|------|------|--|--|

| Syntax:                                                                                           | RRNCF                                               | f {,d {,a}}                                             |      | _    |  |  |

| Operands:                                                                                         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$ |                                                         |      |      |  |  |

| Operation:                                                                                        | ` ,                                                 | $(f) \rightarrow dest,$<br>$(f<0>) \rightarrow dest<7>$ |      |      |  |  |

| Status Affected:                                                                                  | N, Z                                                | N, Z                                                    |      |      |  |  |

| Encoding:                                                                                         | 0100                                                | 00da                                                    | ffff | ffff |  |  |

| Description: The contents of register 'f' are rotate one bit to the right. If 'd' is '0', the re- |                                                     |                                                         |      |      |  |  |

one bit to the right. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed back in register 'f' (default).

If 'a' is '0', the Access Bank will be

selected, overriding the BSR value. If 'a' is '1', then the bank will be selected as per the BSR value.

If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f  $\leq$  95 (5Fh). See Section 29.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed

Literal Offset Mode" for details.

Words: 1 Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4          |

|--------|--------------|---------|-------------|

| Decode | Read         | Process | Write to    |

|        | register 'f' | Data    | destination |

Example 1: RRNCF REG, 1, 0

Before Instruction

REG = 1101 0111

After Instruction

REG = 1110 1011

Example 2: RRNCF REG, 0, 0

Before Instruction

W = ?

REG = 1101 0111

After Instruction

W = 1110 1011 REG = 1101 0111

| OE III           | OCC                                                                                                                                                                                                                                                                |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | SETF f {,a}                                                                                                                                                                                                                                                        |  |  |  |  |

| Operands:        | $0 \le f \le 255$                                                                                                                                                                                                                                                  |  |  |  |  |

|                  | a ∈ [0,1]                                                                                                                                                                                                                                                          |  |  |  |  |

| Operation:       | $FFh \rightarrow f$                                                                                                                                                                                                                                                |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                               |  |  |  |  |

| Encoding:        | 0110 100a ffff ffff                                                                                                                                                                                                                                                |  |  |  |  |

| Description:     | The contents of the specified register are set to FFh.                                                                                                                                                                                                             |  |  |  |  |

|                  | If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the GPR bank.                                                                                                                                                                 |  |  |  |  |

|                  | If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See Section 29.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                                    |  |  |  |  |

Words: 1

Cycles: 1

Q Cycle Activity:

**SETF**

| Q1     | Q2           | Q3      | Q4           |  |

|--------|--------------|---------|--------------|--|

| Decode | Read         | Process | Write        |  |

|        | register 'f' | Data    | register 'f' |  |

Example: SETF REG,1

Before Instruction

REG = 5Ah

After Instruction

REG = FFh

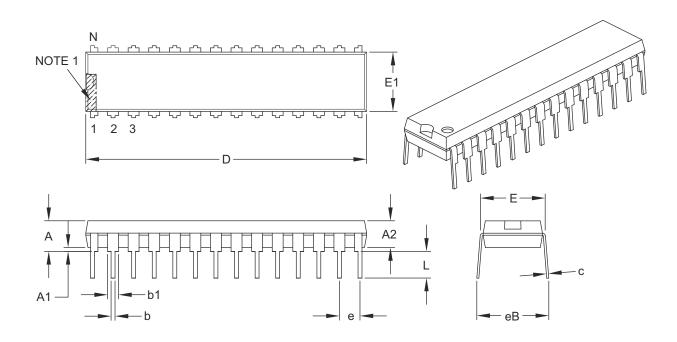

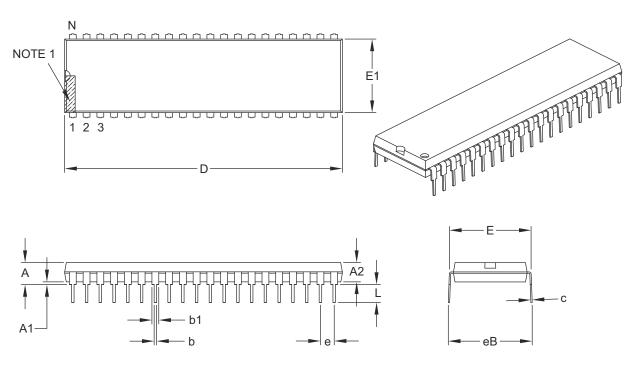

### 28-Lead Skinny Plastic Dual In-Line (SP) - 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |          | INCHES |       |

|----------------------------|----------|----------|--------|-------|

| Dimension                  | n Limits | MIN      | NOM    | MAX   |

| Number of Pins             | N        | 28       |        |       |

| Pitch                      | е        | .100 BSC |        |       |

| Top to Seating Plane       | Α        | _        | _      | .200  |

| Molded Package Thickness   | A2       | .120     | .135   | .150  |

| Base to Seating Plane      | A1       | .015     | _      | _     |

| Shoulder to Shoulder Width | Е        | .290     | .310   | .335  |

| Molded Package Width       | E1       | .240     | .285   | .295  |

| Overall Length             | D        | 1.345    | 1.365  | 1.400 |

| Tip to Seating Plane       | L        | .110     | .130   | .150  |

| Lead Thickness             | С        | .008     | .010   | .015  |

| Upper Lead Width           | b1       | .040     | .050   | .070  |

| Lower Lead Width           | b        | .014     | .018   | .022  |

| Overall Row Spacing §      | eВ       | -        | _      | .430  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

### 40-Lead Plastic Dual In-Line (P) - 600 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units              |       | INCHES   |       |

|----------------------------|--------------------|-------|----------|-------|

| Dimensio                   | n Limits           | MIN   | NOM      | MAX   |

| Number of Pins             | umber of Pins N 40 |       |          |       |

| Pitch                      | е                  |       | .100 BSC |       |

| Top to Seating Plane       | Α                  | _     | _        | .250  |

| Molded Package Thickness   | A2                 | .125  | -        | .195  |

| Base to Seating Plane      | A1                 | .015  | _        | _     |

| Shoulder to Shoulder Width | Е                  | .590  | _        | .625  |

| Molded Package Width       | E1                 | .485  | _        | .580  |

| Overall Length             | D                  | 1.980 | -        | 2.095 |

| Tip to Seating Plane       | L                  | .115  | -        | .200  |

| Lead Thickness             | С                  | .008  | -        | .015  |

| Upper Lead Width           | b1                 | .030  | _        | .070  |

| Lower Lead Width           | b                  | .014  | _        | .023  |

| Overall Row Spacing §      | eB                 | _     | _        | .700  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-016B