Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | ECANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 8x12b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

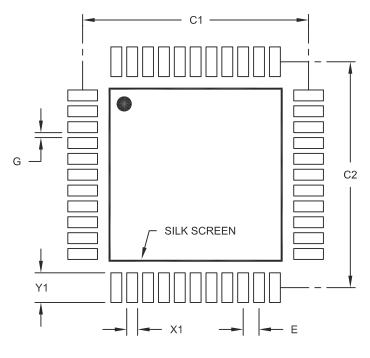

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f26k80-e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC18F66K80 FAMILY

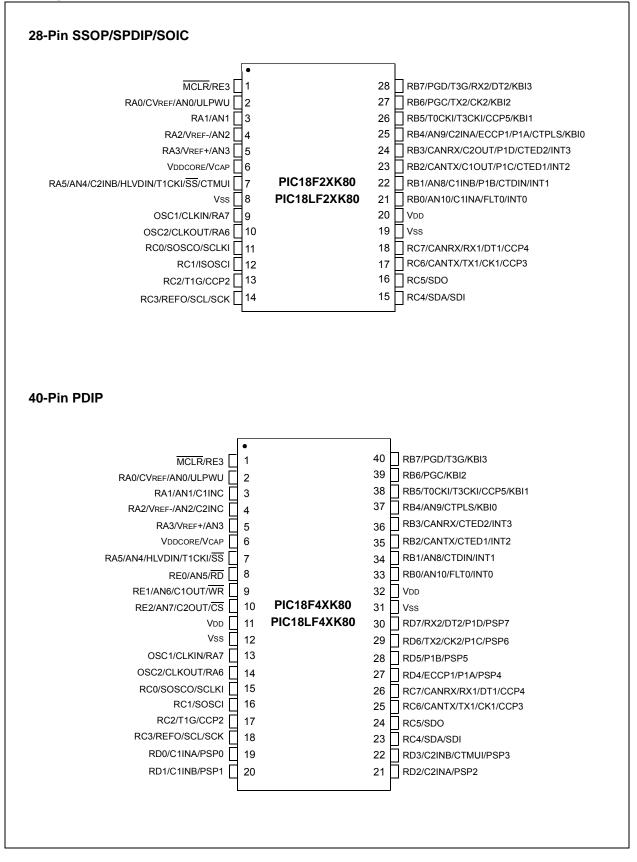

## **Pin Diagrams (Continued)**

# TABLE 4-4:EXIT DELAY ON WAKE-UP BY RESET FROM SLEEP MODE OR ANY IDLE MODE<br/>(BY CLOCK SOURCES)

| Power-Managed<br>Mode | Clock Source <sup>(5)</sup> | Exit Delay                 | Clock Ready<br>Status Bits |

|-----------------------|-----------------------------|----------------------------|----------------------------|

|                       | LP, XT, HS                  |                            |                            |

| PRI_IDLE mode         | HSPLL                       |                            | OSTS                       |

|                       | EC, RC                      | TCSD <sup>(1)</sup>        |                            |

|                       | HF-INTOSC <sup>(2)</sup>    | ICSD**                     | HFIOFS                     |

|                       | MF-INTOSC <sup>(2)</sup>    |                            |                            |

|                       | LF-INTOSC                   |                            | None                       |

| SEC_IDLE mode         | SOSC                        | TCSD <sup>(1)</sup>        | SOSCRUN                    |

|                       | HF-INTOSC <sup>(2)</sup>    |                            | HFIOFS                     |

| RC_IDLE mode          | MF-INTOSC <sup>(2)</sup>    | Tcsd <sup>(1)</sup>        | MFIOFS                     |

|                       | LF-INTOSC                   |                            | None                       |

|                       | LP, XT, HS                  | Tost <sup>(3)</sup>        |                            |

|                       | HSPLL                       | Tost + t <sub>rc</sub> (3) | OSTS                       |

| Sleep mode            | EC, RC                      | TCSD <sup>(1)</sup>        |                            |

| Sleep mode            | HF-INTOSC <sup>(2)</sup>    |                            | HFIOFS                     |

|                       | MF-INTOSC <sup>(2)</sup>    | TIOBST <sup>(4)</sup>      | MFIOFS                     |

|                       | LF-INTOSC                   |                            | None                       |

**Note 1:** TCSD (Parameter 38, Table 31-11) is a required delay when waking from Sleep and all Idle modes, and runs concurrently with any other required delays (see **Section 4.4 "Idle Modes"**).

2: Includes postscaler derived frequencies. On Reset, INTOSC defaults to HF-INTOSC at 8 MHz.

**3:** TOST is the Oscillator Start-up Timer (Parameter 32, Table 31-11). TRC is the PLL Lock-out Timer (Parameter F12, Table 31-7); it is also designated as TPLL.

4: Execution continues during TIOBST (Parameter 39, Table 31-11), the INTOSC stabilization period.

**5:** The clock source is dependent upon the settings of the SCSx (OSCCON<1:0>), IRCFx (OSCCON<6:4>) and FOSCx (CONFIG1H<3:0>) bits.

# PIC18F66K80 FAMILY

### TABLE 6-2: PIC18F66K80 FAMILY REGISTER FILE SUMMARY (CONTINUED)

| Addr.         | E 6-2: P             | Bit 7              | Bit 6         | Bit 5   | Bit 4         | Bit 3         | Bit 2              | Bit 1              | Bit 0         | Value on<br>POR, BOR<br>on page |

|---------------|----------------------|--------------------|---------------|---------|---------------|---------------|--------------------|--------------------|---------------|---------------------------------|

| F09h          | TXB2D3               | TXB2D37            | TXB2D36       | TXB2D35 | TXB2D34       | TXB2D33       | TXB2D32            | TXB2D31            | TXB2D30       | 95                              |

| F08h          | TXB2D2               | TXB2D27            | TXB2D26       | TXB2D25 | TXB2D24       | TXB2D23       | TXB2D22            | TXB2D21            | TXB2D20       | 95                              |

| F07h          | TXB2D2               | TXB2D27            | TXB2D20       | TXB2D25 | TXB2D24       | TXB2D23       | TXB2D22<br>TXB2D12 | TXB2D21<br>TXB2D11 | TXB2D10       | 95                              |

| F06h          | TXB2D1<br>TXB2D0     | TXB2D17<br>TXB2D07 | TXB2D10       | TXB2D15 | TXB2D14       | TXB2D13       | TXB2D12            | TXB2D11<br>TXB2D01 | TXB2D10       | 95                              |

| F05h          | TXB2D0               | TXB2D07            | TXRTR         |         | TAB2D04       | DLC3          | DLC2               | DLC1               | DLC0          | 95                              |

| F04h          | TXB2DLC              | EID7               | EID6          | EID5    | EID4          | EID3          | EID2               | EID1               | EID0          | 95                              |

| F0411<br>F03h | TXB2EIDL<br>TXB2EIDH | EID7<br>EID15      | EID0<br>EID14 | EID3    | EID4<br>EID12 | EID3<br>EID11 | EID2<br>EID10      | EID1<br>EID9       | EID0<br>EID8  | 95<br>95                        |

| F02h          | TXB2EIDH             | SID2               | SID14         | SIDO    | SRR           | EXID          | EIDIU              | EID9<br>EID17      | EID8<br>EID16 | 95<br>95                        |

| F0211         | TXB2SIDL<br>TXB2SIDH | SID2<br>SID10      | SID1          | SID0    | SID7          | SID6          | SID5               | SID4               | SID3          | 95<br>95                        |

|               | 1                    | TXBIF              |               |         |               |               | 3105               | TXPRI1             |               |                                 |

| F00h          | TXB2CON              |                    | TXABT         | TXLARB  | TXERR         | TXREQ         |                    |                    | TXPRI0        | 95                              |

| EFFh          | RXM1EIDL             | EID7               | EID6          | EID5    | EID4          | EID3          | EID2               | EID1               | EID0          | 95                              |

| EFEh          | RXM1EIDH             | EID15              | EID14         | EID13   | EID12         | EID11         | EID10              | EID9               | EID8          | 95                              |

| EFDh          | RXM1SIDL             | SID2               | SID1          | SID0    | -             | EXIDEN        | -                  | EID17              | EID16         | 95                              |

| EFCh          | RXM1SIDH             | SID10              | SID9          | SID8    | SID7          | SID6          | SID5               | SID4               | SID3          | 95                              |

| EFBh          | RXM0EIDL             | EID7               | EID6          | EID5    | EID4          | EID3          | EID2               | EID1               | EID0          | 95                              |

| EFAh          | RXM0EIDH             | EID15              | EID14         | EID13   | EID12         | EID11         | EID10              | EID9               | EID8          | 95                              |

| EF9h          | RXM0SIDL             | SID2               | SID1          | SID0    | —             | EXIDEN        | —                  | EID17              | EID16         | 95                              |

| EF8h          | RXM0SIDH             | SID10              | SID9          | SID8    | SID7          | SID6          | SID5               | SID4               | SID3          | 95                              |

| EF7h          | RXF5EIDL             | EID7               | EID6          | EID5    | EID4          | EID3          | EID2               | EID1               | EID0          | 95                              |

| EF6h          | RXF5EIDH             | EID15              | EID14         | EID13   | EID12         | EID11         | EID10              | EID9               | EID8          | 95                              |

| EF5h          | RXF5SIDL             | SID2               | SID1          | SID0    | —             | EXIDEN        | —                  | EID17              | EID16         | 95                              |

| EF4h          | RXF5SIDH             | SID10              | SID9          | SID8    | SID7          | SID6          | SID5               | SID4               | SID3          | 95                              |

| EF3h          | RXF4EIDL             | EID7               | EID6          | EID5    | EID4          | EID3          | EID2               | EID1               | EID0          | 95                              |

| EF2h          | RXF4EIDH             | EID15              | EID14         | EID13   | EID12         | EID11         | EID10              | EID9               | EID8          | 95                              |

| EF1h          | RXF4SIDL             | SID2               | SID1          | SID0    | —             | EXIDEN        | —                  | EID17              | EID16         | 95                              |

| EF0h          | RXF4SIDH             | SID10              | SID9          | SID8    | SID7          | SID6          | SID5               | SID4               | SID3          | 95                              |

| EEFh          | RXF3EIDL             | EID7               | EID6          | EID5    | EID4          | EID3          | EID2               | EID1               | EID0          | 95                              |

| EEEh          | RXF3EIDH             | EID15              | EID14         | EID13   | EID12         | EID11         | EID10              | EID9               | EID8          | 95                              |

| EEDh          | RXF3SIDL             | SID2               | SID1          | SID0    | —             | EXIDEN        | —                  | EID17              | EID16         | 95                              |

| EECh          | RXF3SIDH             | SID10              | SID9          | SID8    | SID7          | SID6          | SID5               | SID4               | SID3          | 95                              |

| EEBh          | RXF2EIDL             | EID7               | EID6          | EID5    | EID4          | EID3          | EID2               | EID1               | EID0          | 95                              |

| EEAh          | RXF2EIDH             | EID15              | EID14         | EID13   | EID12         | EID11         | EID10              | EID9               | EID8          | 95                              |

| EE9h          | RXF2SIDL             | SID2               | SID1          | SID0    | _             | EXIDEN        | _                  | EID17              | EID16         | 95                              |

| EE8h          | RXF2SIDH             | SID10              | SID9          | SID8    | SID7          | SID6          | SID5               | SID4               | SID3          | 95                              |

| EE7h          | RXF1EIDL             | EID7               | EID6          | EID5    | EID4          | EID3          | EID2               | EID1               | EID0          | 95                              |

| EE6h          | RXF1EIDH             | EID15              | EID14         | EID13   | EID12         | EID11         | EID10              | EID9               | EID8          | 95                              |

| EE5h          | RXF1SIDL             | SID2               | SID1          | SID0    | _             | EXIDEN        | _                  | EID17              | EID16         | 95                              |

| EE4h          | RXF1SIDH             | SID10              | SID9          | SID8    | SID7          | SID6          | SID5               | SID4               | SID3          | 95                              |

| EE3h          | RXF0EIDL             | EID7               | EID6          | EID5    | EID4          | EID3          | EID2               | EID1               | EID0          | 95                              |

| EE2h          | RXF0EIDH             | EID15              | EID14         | EID13   | EID12         | EID11         | EID10              | EID9               | EID8          | 95                              |

| EE1h          | RXF0SIDL             | SID2               | SID1          | SID0    | _             | EXIDEN        | _                  | EID17              | EID16         | 95                              |

| EE0h          | RXF0SIDH             | SID10              | SID9          | SID8    | SID7          | SID6          | SID5               | SID4               | SID3          | 95                              |

| EDFh          | CANCON RO4           | CANCON_R           |               | 5.20    | 5.51          | 5.20          | 5.20               | 5.5 1              | 0.20          | 95                              |

| EDEh          | CANSTAT RO4          | CANSTAT R          |               |         |               |               |                    |                    |               | 95                              |

| EDDh          | B5D7                 | B5D77              | B5D76         | B5D75   | B5D74         | B5D73         | B5D72              | B5D71              | B5D70         | 95<br>95                        |

| EDCh          | B5D6                 | B5D67              | B5D66         | B5D65   | B5D64         | B5D63         | B5D62              | B5D61              | B5D60         | 95<br>95                        |

| EDBh          | B5D6<br>B5D5         |                    |               |         |               |               |                    |                    |               | 95<br>95                        |

|               | 1                    | B5D57              | B5D56         | B5D55   | B5D54         | B5D53         | B5D52              | B5D51              | B5D50         |                                 |

| EDAh          | B5D4                 | B5D47              | B5D46         | B5D45   | B5D44         | B5D43         | B5D42              | B5D41              | B5D40         | 95                              |

| ED9h          | B5D3                 | B5D37              | B5D36         | B5D35   | B5D34         | B5D33         | B5D32              | B5D31              | B5D30         | 95                              |

| ED8h          | B5D2                 | B5D27              | B5D26         | B5D25   | B5D24         | B5D23         | B5D22              | B5D21              | B5D20         | 95                              |

| ED7h          | B5D1                 | B5D17              | B5D16         | B5D15   | B5D14         | B5D13         | B5D12              | B5D11              | B5D10         | 95                              |

# 8.0 DATA EEPROM MEMORY

The data EEPROM is a nonvolatile memory array, separate from the data RAM and program memory, that is used for long-term storage of program data. It is not directly mapped in either the register file or program memory space, but is indirectly addressed through the Special Function Registers (SFRs). The EEPROM is readable and writable during normal operation over the entire VDD range.

Five SFRs are used to read and write to the data EEPROM, as well as the program memory. They are:

- · EECON1

- EECON2

- EEDATA

- EEADR

- EEADRH

The data EEPROM allows byte read and write. When interfacing to the data memory block, EEDATA holds the 8-bit data for read/write and the EEADRH:EEADR register pair holds the address of the EEPROM location being accessed.

The EEPROM data memory is rated for high erase/write cycle endurance. A byte write automatically erases the location and writes the new data (erase-before-write). The write time is controlled by an on-chip timer; it will vary with voltage and temperature, as well as from chip-to-chip. Please refer to Parameter D122 (Table 31-1 in **Section 31.0** "**Electrical Characteristics**") for exact limits.

### 8.1 EEADR and EEADRH Registers

The EEADRH:EEADR register pair is used to address the data EEPROM for read and write operations. EEADRH holds the two MSbs of the address; the upper 6 bits are ignored. The 10-bit range of the pair can address a memory range of 1024 bytes (00h to 3FFh).

### 8.2 EECON1 and EECON2 Registers

Access to the data EEPROM is controlled by two registers: EECON1 and EECON2. These are the same registers which control access to the program memory and are used in a similar manner for the data EEPROM.

The EECON1 register (Register 8-1) is the control register for data and program memory access. Control bit, EEPGD, determines if the access will be to program memory or data EEPROM memory. When clear, operations will access the data EEPROM memory. When set, program memory is accessed.

Control bit, CFGS, determines if the access will be to the Configuration registers or to program memory/data EEPROM memory. When set, subsequent operations access Configuration registers. When CFGS is clear, the EEPGD bit selects either program Flash or data EEPROM memory.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WREN bit is set and cleared, when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR is       |

|-------|---------------------------------------------|

|       | read as '1'. This can indicate that a write |

|       | operation was prematurely terminated by     |

|       | a Reset, or a write operation was           |

|       | attempted improperly.                       |

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software; it is cleared in hardware at the completion of the write operation.

| Note: | The EEIF interrupt flag bit (PIR4<6>) is   |

|-------|--------------------------------------------|

|       | set when the write is complete. It must be |

|       | cleared in software.                       |

Control bits, RD and WR, start read and erase/write operations, respectively. These bits are set by firmware and cleared by hardware at the completion of the operation.

The RD bit cannot be set when accessing program memory (EEPGD = 1). Program memory is read using table read instructions. See **Section 7.1 "Table Reads and Table Writes"** regarding table reads.

The EECON2 register is not a physical register. It is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

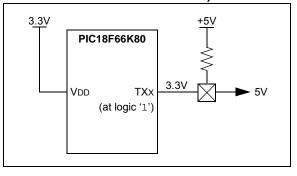

#### 11.1.3 OPEN-DRAIN OUTPUTS

The output pins for several peripherals are also equipped with a configurable, open-drain output option. This allows the peripherals to communicate with external digital logic, operating at a higher voltage level, without the use of level translators.

The open-drain option is implemented on port pins specifically associated with the data and clock outputs of the USARTs, the MSSP module (in SPI mode) and the CCP modules. This option is selectively enabled by setting the open-drain control bits in the ODCON register.

When the open-drain option is required, the output pin must also be tied through an external pull-up resistor provided by the user to a higher voltage level, up to 5V (Figure 11-2). When a digital logic high signal is output, it is pulled up to the higher voltage level.

#### FIGURE 11-2:

#### USING THE OPEN-DRAIN OUTPUT (USARTx SHOWN AS EXAMPLE)

#### REGISTER 11-3: ODCON: PERIPHERAL OPEN-DRAIN CONTROL REGISTER

| R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

|-------|--------|--------|--------|--------|--------|-------|-------|

| SSPOD | CCP5OD | CCP4OD | CCP3OD | CCP2OD | CCP10D | U2OD  | U10D  |

| bit 7 |        |        |        |        |        |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | SSPOD: SPI Open-Drain Output Enable bit                                                                 |

|-------|---------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Open-drain capability is enabled</li> <li>0 = Open-drain capability is disabled</li> </ul> |

|       |                                                                                                         |

| bit 6 | CCP5OD: CCP5 Open-Drain Output Enable bit                                                               |

|       | <ul> <li>1 = Open-drain capability is enabled</li> <li>0 = Open-drain capability is disabled</li> </ul> |

| bit 5 | CCP4OD: CCP4 Open-Drain Output Enable bit                                                               |

|       | 1 = Open-drain capability is enabled                                                                    |

|       | 0 = Open-drain capability is disabled                                                                   |

| bit 4 | CCP3OD: CCP3 Open-Drain Output Enable bit                                                               |

|       | 1 = Open-drain capability is enabled                                                                    |

|       | 0 = Open-drain capability is disabled                                                                   |

| bit 3 | CCP2OD: CCP2 Open-Drain Output Enable bit                                                               |

|       | 1 = Open-drain capability is enabled                                                                    |

|       | 0 = Open-drain capability is disabled                                                                   |

| bit 2 | CCP10D: CCP1 Open-Drain Output Enable bit                                                               |

|       | 1 = Open-drain capability is enabled                                                                    |

|       | 0 = Open-drain capability is disabled                                                                   |

| bit 1 | U20D: UART2 Open-Drain Output Enable bit                                                                |

|       | 1 = Open-drain capability is enabled                                                                    |

|       | 0 = Open-drain capability is disabled                                                                   |

| bit 0 | U10D: UART1 Open-Drain Output Enable bit                                                                |

|       | 1 = Open-drain capability is enabled                                                                    |

|       | 0 = Open-drain capability is disabled                                                                   |

|       |                                                                                                         |

#### 16.6 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and overflows to 0000h. The Timer3 interrupt, if enabled, is generated on overflow and is latched in the interrupt flag bit, TMR3IF. Table 16-3 gives each module's flag bit.

This interrupt can be enabled or disabled by setting or clearing the TMR3IE bit. Table 16-3 displays each module's enable bit.

### 16.7 Resetting Timer3 Using the ECCP Special Event Trigger

If the ECCP modules are configured to use Timer3 and to generate a Special Event Trigger in Compare mode (CCP3M<3:0> = 1011), this signal will reset Timer3. The trigger from ECCP will also start an A/D conversion if the A/D module is enabled (For more information, see **Section 20.3.4 "Special Event Trigger"**.) The module must be configured as either a timer or synchronous counter to take advantage of this feature. When used this way, the CCPR3H:CCPR3L register pair effectively becomes a Period register for Timer3.

If Timer3 is running in Asynchronous Counter mode, the Reset operation may not work.

In the event that a write to Timer3 coincides with a Special Event Trigger from an ECCP module, the write will take precedence.

- **Note:** The Special Event Triggers from the ECCPx module will only clear the TMR3 register's content, but not set the TMR3IF interrupt flag bit (PIR2<1>).

- Note: The CCP and ECCP modules use Timers, 1 through 4, for some modes. The assignment of a particular timer to a CCP/ECCP module is determined by the Timer to CCP enable bits in the CCPTMRS register. For more details, see Register 20-2 and Register 19-2.

| Name    | Bit 7       | Bit 6          | Bit 5   | Bit 4   | Bit 3            | Bit 2  | Bit 1  | Bit 0   |

|---------|-------------|----------------|---------|---------|------------------|--------|--------|---------|

| INTCON  | GIE/GIEH    | PEIE/GIEL      | TMR0IE  | INT0IE  | RBIE             | TMR0IF | INT0IF | RBIF    |

| PIR5    | IRXIF       | WAKIF          | ERRIF   | TXB2IF  | TXB1IF           | TXB0IF | RXB1IF | RXB0IF  |

| PIE5    | IRXIE       | WAKIE          | ERRIE   | TX2BIE  | TXB1IE           | TXB0IE | RXB1IE | RXB0IE  |

| PIR2    | OSCFIF      |                |         |         | BCLIF            | HLVDIF | TMR3IF | TMR3GIF |

| PIE2    | OSCFIE      | _              | _       | _       | BCLIE            | HLVDIE | TMR3IE | TMR3GIE |

| TMR3H   | Timer3 Regi | ster High Byte | 9       |         |                  |        |        |         |

| TMR3L   | Timer3 Regi | ster Low Byte  | •       |         |                  |        |        |         |

| T3GCON  | TMR3GE      | T3GPOL         | T3GTM   | T3GSPM  | T3GGO/<br>T3DONE | T3GVAL | T3GSS1 | T3GSS0  |

| T3CON   | TMR3CS1     | TMR3CS0        | T3CKPS1 | T3CKPS0 | SOSCEN           | T3SYNC | RD16   | TMR3ON  |

| OSCCON2 | —           | SOSCRUN        | _       | SOSCDRV | SOSCGO           | _      | MFIOFS | MFIOSEL |

| PMD1    | PSPMD       | CTMUMD         | ADCMD   | TMR4MD  | TMR3MD           | TMR2MD | TMR1MD | TMR0MD  |

### TABLE 16-3: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer3 module.

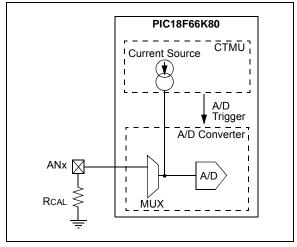

The CTMU current source may be trimmed with the trim bits in CTMUICON, using an iterative process to get the exact current desired. Alternatively, the nominal value without adjustment may be used. That value may be stored by software, for use in all subsequent capacitive or time measurements.

To calculate the optimal value for RCAL, the nominal current must be chosen.

For example, if the A/D Converter reference voltage is 3.3V, use 70% of full scale (or 2.31V) as the desired approximate voltage to be read by the A/D Converter. If the range of the CTMU current source is selected to be 0.55  $\mu$ A, the resistor value needed is calculated as RCAL = 2.31V/0.55  $\mu$ A, for a value of 4.2 MΩ. Similarly, if the current source is chosen to be 5.5  $\mu$ A, RCAL would be 420,000Ω, and 42,000Ω if the current source is set to 55  $\mu$ A.

#### FIGURE 18-2: CTMU CURRENT SOURCE CALIBRATION CIRCUIT

A value of 70% of full-scale voltage is chosen to make sure that the A/D Converter is in a range that is well above the noise floor. If an exact current is chosen to incorporate the trimming bits from CTMUICON, the resistor value of RCAL may need to be adjusted accordingly. RCAL also may be adjusted to allow for available resistor values. RCAL should be of the highest precision available, in light of the precision needed for the circuit that the CTMU will be measuring. A recommended minimum would be 0.1% tolerance.

The following examples show a typical method for performing a CTMU current calibration.

• Example 18-1 demonstrates how to initialize the A/D Converter and the CTMU.

This routine is typical for applications using both modules.

• Example 18-2 demonstrates one method for the actual calibration routine.

This method manually triggers the A/D Converter to demonstrate the entire step-wise process. It is also possible to automatically trigger the conversion by setting the CTMU's CTTRIG bit (CTMUCONH<0>).

# 19.0 CAPTURE/COMPARE/PWM (CCP) MODULES

PIC18F66K80 family devices have four CCP (Capture/Compare/PWM) modules, designated CCP2 through CCP5. All the modules implement standard Capture, Compare and Pulse-Width Modulation (PWM) modes.

**Note:** Throughout this section, generic references are used for register and bit names that are the same, except for an 'x' variable that indicates the item's association with the specific CCP module. For example, the control register is named CCPxCON and refers to CCP2CON through CCP5CON.

Each CCP module contains a 16-bit register that can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register. For the sake of clarity, all CCP module operation in the following sections is described with respect to CCP2, but is equally applicable to CCP3 through CCP5.

# REGISTER 19-1: CCPxCON: CCPx CONTROL REGISTER (CCP2-CCP5 MODULES)

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-----|-------|-------|-----------------------|-----------------------|-----------------------|-----------------------|

| —     | —   | DCxB1 | DCxB0 | CCPxM3 <sup>(1)</sup> | CCPxM2 <sup>(1)</sup> | CCPxM1 <sup>(1)</sup> | CCPxM0 <sup>(1)</sup> |

| bit 7 |     |       |       |                       |                       |                       | bit 0                 |

#### Legend:

| Legenu.           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                                                                |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | DCxB<1:0>: PWM Duty Cycle bit 1 and bit 0 for CCPx Module bits                                                                                                                                            |

|         | Capture mode:                                                                                                                                                                                             |

|         | Unused.                                                                                                                                                                                                   |

|         | Compare mode:                                                                                                                                                                                             |

|         | Unused.                                                                                                                                                                                                   |

|         | PWM mode:                                                                                                                                                                                                 |

|         | These bits are the two Least Significant bits (bit 1 and bit 0) of the 10-bit PWM duty cycle. The eight Most Significant bits (DCx<9:2>) of the duty cycle are found in CCPRxL.                           |

| bit 3-0 | CCPxM<3:0>: CCPx Module Mode Select bits <sup>(1)</sup>                                                                                                                                                   |

|         | 0000 = Capture/Compare/PWM disabled (resets CCPx module)<br>0001 = Reserved                                                                                                                               |

|         | 0001 – Reserved<br>0010 = Compare mode: toggle output on match (CCPxIF bit is set)                                                                                                                        |

|         | 0011 = Reserved                                                                                                                                                                                           |

|         | 0100 = Capture mode: every falling edge or CAN message received (time-stamp) <sup>(2)</sup>                                                                                                               |

|         | 0101 = Capture mode: every rising edge or CAN message received (time-stamp) <sup>(2)</sup>                                                                                                                |

|         | 0110 = Capture mode: every 4th rising edge or on every fourth CAN message received (time-stamp) $\binom{2}{2}$                                                                                            |

|         | 0111 = Capture mode: every 16th rising edge or on every 16th CAN message received (time-stamp) <sup>(2)</sup>                                                                                             |

|         | 1000 = Compare mode: initialize CCPx pin low; on compare match, force CCPx pin high (CCPxIF bit is set)                                                                                                   |

|         | 1001 = Compare mode: initialize CCPx pin high; on compare match, force CCPx pin low (CCPxIF bit is set)<br>1010 = Compare mode: generate software interrupt on compare match (CCPxIF bit is set, CCPx pin |

|         | reflects I/O state)                                                                                                                                                                                       |

|         | 1011 = Compare mode: Special Event Trigger; reset timer on CCPx match (CCPxIF bit is set)                                                                                                                 |

|         | 11xx = PWM mode                                                                                                                                                                                           |

| Note 1: | CCPxM<3:0> = 1011 will only reset the timer and not start an A/D conversion on CCPx match.                                                                                                                |

|         | Available only on CCP2. Selected by the CANCAP (CIOCON/A) bit Overrides the CCP2 input pin                                                                                                                |

2: Available only on CCP2. Selected by the CANCAP (CIOCON<4>) bit. Overrides the CCP2 input pin source.

## REGISTER 21-2: SSPCON1: MSSP CONTROL REGISTER 1 (SPI MODE)

| R/W-0      | R/W-0                                                           | R/W-0                                                                                                                        | R/W-0           | R/W-0                           | R/W-0                  | R/W-0                | R/W-0                |  |  |  |  |  |

|------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------|------------------------|----------------------|----------------------|--|--|--|--|--|

| WCOL       | SSPOV <sup>(1)</sup>                                            | SSPEN <sup>(2)</sup>                                                                                                         | CKP             | SSPM3 <sup>(3)</sup>            | SSPM2 <sup>(3)</sup>   | SSPM1 <sup>(3)</sup> | SSPM0 <sup>(3)</sup> |  |  |  |  |  |

| bit 7      |                                                                 |                                                                                                                              |                 |                                 | •                      | •<br>•               | bit (                |  |  |  |  |  |

|            |                                                                 |                                                                                                                              |                 |                                 |                        |                      |                      |  |  |  |  |  |

| Legend:    |                                                                 |                                                                                                                              |                 |                                 |                        |                      |                      |  |  |  |  |  |

| R = Reada  |                                                                 | W = Writable b                                                                                                               | bit             | -                               | nented bit, rea        |                      |                      |  |  |  |  |  |

| -n = Value | at POR                                                          | '1' = Bit is set                                                                                                             |                 | '0' = Bit is clea               | ared                   | x = Bit is unkr      | nown                 |  |  |  |  |  |

| bit 7      | WCOL: Write                                                     | Collision Detec                                                                                                              | t bit           |                                 |                        |                      |                      |  |  |  |  |  |

|            | software)                                                       |                                                                                                                              | written while   | it is still transm              | itting the previ       | ious word (mus       | t be cleared ir      |  |  |  |  |  |

|            |                                                                 | 0 = No collision                                                                                                             |                 |                                 |                        |                      |                      |  |  |  |  |  |

| bit 6      | SSPOV: Receive Overflow Indicator bit <sup>(1)</sup>            |                                                                                                                              |                 |                                 |                        |                      |                      |  |  |  |  |  |

|            |                                                                 | SPI Slave mode:<br>1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of over- |                 |                                 |                        |                      |                      |  |  |  |  |  |

|            |                                                                 | flow, the data in SSPSR is lost. Overflow can only occur in Slave mode. The user must read the                               |                 |                                 |                        |                      |                      |  |  |  |  |  |

|            |                                                                 |                                                                                                                              |                 | ta, to avoid settir             |                        |                      |                      |  |  |  |  |  |

|            | 0 = No overfl                                                   | ow                                                                                                                           | c               |                                 | •                      |                      |                      |  |  |  |  |  |

| bit 5      | SSPEN: Master Synchronous Serial Port Enable bit <sup>(2)</sup> |                                                                                                                              |                 |                                 |                        |                      |                      |  |  |  |  |  |

|            |                                                                 |                                                                                                                              |                 | SCK, SDO, SD<br>these pins as I |                        | erial port pins      |                      |  |  |  |  |  |

| bit 4      | CKP: Clock F                                                    | <b>CKP:</b> Clock Polarity Select bit                                                                                        |                 |                                 |                        |                      |                      |  |  |  |  |  |

|            | 1 = Idle state for clock is a high level                        |                                                                                                                              |                 |                                 |                        |                      |                      |  |  |  |  |  |

|            | 0 = Idle state                                                  | for clock is a lov                                                                                                           | w level         |                                 |                        |                      |                      |  |  |  |  |  |

| bit 3-0    | SSPM<3:0>:                                                      | Master Synchro                                                                                                               | nous Serial I   | Port Mode Selec                 | ct bits <sup>(3)</sup> |                      |                      |  |  |  |  |  |

|            |                                                                 | 1010 = SPI Master mode: clock = Fosc/8                                                                                       |                 |                                 |                        |                      |                      |  |  |  |  |  |

|            |                                                                 |                                                                                                                              |                 | <u>SS</u> pin control           |                        | an be used as l      | I/O pin              |  |  |  |  |  |

|            |                                                                 | 0100 = SPI Slave mode: clock = SCK pin; SS pin control enabled<br>0011 = SPI Master mode: clock = TMR2 output/2              |                 |                                 |                        |                      |                      |  |  |  |  |  |

|            |                                                                 | laster mode: clo<br>laster mode: clo                                                                                         |                 | •                               |                        |                      |                      |  |  |  |  |  |

|            |                                                                 | laster mode: clo                                                                                                             |                 |                                 |                        |                      |                      |  |  |  |  |  |

|            |                                                                 | laster mode: clo                                                                                                             |                 |                                 |                        |                      |                      |  |  |  |  |  |

|            | n Master mode, t<br>writing to the SSF                          |                                                                                                                              | is not set sind | ce each new rec                 | eption (and tra        | ansmission) is i     | nitiated by          |  |  |  |  |  |

|            | When enabled th                                                 | 0                                                                                                                            | n nronerly c    | onfigured as inn                | ute or outpute         |                      |                      |  |  |  |  |  |

- 2: When enabled, these pins must be properly configured as inputs or outputs.

- **3:** Bit combinations not specifically listed here are either reserved or implemented in I<sup>2</sup>C mode only.

| Name   | Bit 7                 | Bit 6                 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0  |

|--------|-----------------------|-----------------------|---------|---------|---------|---------|---------|--------|

| INTCON | GIE/GIEH              | PEIE/GIEL             | TMR0IE  | INT0IE  | RBIE    | TMR0IF  | INT0IF  | RBIF   |

| PIR1   | PSPIF                 | ADIF                  | RC1IF   | TX1IF   | SSPIF   | TMR1GIF | TMR2IF  | TMR1IF |

| PIE1   | PSPIE                 | ADIE                  | RC1IE   | TX1IE   | SSPIE   | TMR1GIE | TMR2IE  | TMR1IE |

| IPR1   | PSPIP                 | ADIP                  | RC1IP   | TX1IP   | SSPIP   | TMR1GIP | TMR2IP  | TMR1IP |

| ADRESH | A/D Result            | Register High         | n Byte  |         |         |         |         |        |

| ADRESL | A/D Result            | Register Low          | Byte    |         |         |         |         |        |

| ADCON0 | —                     | CHS4                  | CHS3    | CHS2    | CHS1    | CHS0    | GO/DONE | ADON   |

| ADCON1 | TRIGSEL1              | TRIGSEL0              | VCFG1   | VCFG0   | VNCFG   | CHSN2   | CHSN1   | CHSN0  |

| ADCON2 | ADFM                  |                       | ACQT2   | ACQT1   | ACQT0   | ADCS2   | ADCS1   | ADCS0  |

| ANCON0 | ANSEL7                | ANSEL6                | ANSEL5  | ANSEL4  | ANSEL3  | ANSEL2  | ANSEL1  | ANSEL0 |

| ANCON1 | —                     | ANSEL14               | ANSEL13 | ANSEL12 | ANSEL11 | ANSEL10 | ANSEL9  | ANSEL8 |

| PORTA  | RA7 <sup>(1)</sup>    | RA6 <sup>(1)</sup>    | RA5     | _       | RA3     | RA2     | RA1     | RA0    |

| TRISA  | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | TRISA5  | _       | TRISA3  | TRISA2  | TRISA1  | TRISA0 |

| PORTB  | RB7                   | RB6                   | RB5     | RB4     | RB3     | RB2     | RB1     | RB0    |

| TRISB  | TRISB7                | TRISB6                | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0 |

| PORTE  | RE7                   | RE6                   | RE5     | RE4     | RE3     | _       | RE1     | RE0    |

| TRISE  | TRISE7                | TRISE6                | TRISE5  | TRISE4  | _       | TRISE2  | TRISE1  | TRISE0 |

| PMD1   | PSPMD                 | CTMUMD                | ADCMD   | TMR4MD  | TMR3MD  | TMR2MD  | TMR1MD  | TMR0MD |

| TABLE 23-2: | <b>REGISTERS ASSOCIATED WITH THE A/D MODULE</b> |

|-------------|-------------------------------------------------|

|-------------|-------------------------------------------------|

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

**Note 1:** These bits are available only in certain oscillator modes when the FOSC2 Configuration bit = 0. If that Configuration bit is cleared, this signal is not implemented.

# 25.0 COMPARATOR VOLTAGE REFERENCE MODULE

The comparator voltage reference is a 32-tap resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it may also be used independently of them.

A block diagram of the module is shown in Figure 25-1. The resistor ladder is segmented to provide a range of CVREF values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/VSS or an external voltage reference.

#### 25.1 Configuring the Comparator Voltage Reference

The comparator voltage reference module is controlled through the CVRCON register (Register 25-1). The comparator voltage reference provides a range of output voltage with 32 levels.

The CVR<4:0> selection bits (CVRCON<4:0>) offer a range of output voltages. Equation 25-1 shows the how the comparator voltage reference is computed.

### EQUATION 25-1:

$$\frac{\text{If CVRSS} = 1:}{\text{CVREF}} = \left(\text{VREF} + \frac{\text{CVR} < 4:0>}{32}\right) \cdot (\text{VREF} + - \text{VREF})$$

$$\frac{\text{If CVRSS} = 0:}{\text{CVREF}} = \left(\text{AVSS} + \frac{\text{CVR} < 4:0>}{32}\right) \cdot (\text{AVDD} - \text{AVSS})$$

The comparator reference supply voltage can come from either VDD and Vss, or the external VREF+ and VREF- that are multiplexed with RA3 and RA2. The voltage source is selected by the CVRSS bit (CVRCON<5>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output (see Table 31-2 in **Section 31.0** "**Electrical Characteristics**").

# REGISTER 25-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0                                                                                       | R/W-0                                                   | R/W-0            | R/W-0           | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |

|---------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------|-----------------|-------------------|-----------------|-----------------|-------|--|--|--|

| CVREN                                                                                       | CVROE                                                   | CVRSS            | CVR4            | CVR3              | CVR2            | CVR1            | CVR0  |  |  |  |

| bit 7                                                                                       | -                                                       |                  |                 |                   |                 |                 | bit ( |  |  |  |

|                                                                                             |                                                         |                  |                 |                   |                 |                 |       |  |  |  |

| Legend:                                                                                     |                                                         |                  |                 |                   |                 |                 |       |  |  |  |

| R = Readable                                                                                | e bit                                                   | W = Writable b   | pit             | U = Unimplem      | nented bit, rea | d as '0'        |       |  |  |  |

| -n = Value at                                                                               | POR                                                     | '1' = Bit is set |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |  |  |  |

|                                                                                             |                                                         |                  |                 |                   |                 |                 |       |  |  |  |

| bit 7                                                                                       |                                                         | nparator Voltage |                 | nable bit         |                 |                 |       |  |  |  |

|                                                                                             | 1 = CVREF circuit powered on                            |                  |                 |                   |                 |                 |       |  |  |  |

|                                                                                             | 0 = CVREF circuit powered down                          |                  |                 |                   |                 |                 |       |  |  |  |

| bit 6                                                                                       | CVROE: Cor                                              | mparator VREF C  | output Enable   | bit               |                 |                 |       |  |  |  |

|                                                                                             | 1 = CVREF voltage level is output on CVREF pin          |                  |                 |                   |                 |                 |       |  |  |  |

|                                                                                             | 0 = CVREF voltage level is disconnected from CVREF pin  |                  |                 |                   |                 |                 |       |  |  |  |

| bit 5                                                                                       | CVRSS: Con                                              | nparator VREF S  | ource Selection | on bit            |                 |                 |       |  |  |  |

|                                                                                             | 1 = Comparator reference source, CVRSRC = VREF+ – VREF- |                  |                 |                   |                 |                 |       |  |  |  |

|                                                                                             | 0 = Comparator reference source, CVRSRC = AVDD – AVSS   |                  |                 |                   |                 |                 |       |  |  |  |

| bit 4-0 <b>CVR&lt;4:0&gt;:</b> Comparator VREF Value Selection $0 \le CVR<4:0> \le 31$ bits |                                                         |                  |                 |                   |                 |                 |       |  |  |  |

|                                                                                             | When CVRSS = 1:                                         |                  |                 |                   |                 |                 |       |  |  |  |

|                                                                                             | CVREF = (VRI                                            | EF-) + (CVR<4:0  | >/32) • (VREF   | + – Vref-)        |                 |                 |       |  |  |  |

|                                                                                             | When CVRS                                               |                  | (00) (1) (      |                   |                 |                 |       |  |  |  |

|                                                                                             | CVREF = (AV                                             | ss) + (CVR<4:0   | >/32) • (AVDD   | – AVSS)           |                 |                 |       |  |  |  |

|                                                                                             |                                                         |                  |                 |                   |                 |                 |       |  |  |  |

#### 27.2.2 DEDICATED CAN TRANSMIT BUFFER REGISTERS

This section describes the dedicated CAN Transmit Buffer registers and their associated control registers.

#### **REGISTER 27-5:** TXBnCON: TRANSMIT BUFFER n CONTROL REGISTERS $[0 \le n \le 2]$

| Mode 0 | U-0   | R-0                  | R-0                   | R-0                  | R/W-0                | U-0 | R/W-0                 | R/W-0                 |

|--------|-------|----------------------|-----------------------|----------------------|----------------------|-----|-----------------------|-----------------------|

|        | TXBIF | TXABT <sup>(1)</sup> | TXLARB <sup>(1)</sup> | TXERR <sup>(1)</sup> | TXREQ <sup>(2)</sup> |     | TXPRI1 <sup>(3)</sup> | TXPRI0 <sup>(3)</sup> |

| Mode 1,2 | R/C-0 | R-0                  | R-0                   | R-0                  | R/W-0                | U-0 | R/W-0                 | R/W-0                 |

|----------|-------|----------------------|-----------------------|----------------------|----------------------|-----|-----------------------|-----------------------|

| wode 1,2 | TXBIF | TXABT <sup>(1)</sup> | TXLARB <sup>(1)</sup> | TXERR <sup>(1)</sup> | TXREQ <sup>(2)</sup> | _   | TXPRI1 <sup>(3)</sup> | TXPRI0 <sup>(3)</sup> |

|          | bit 7 |                      |                       |                      |                      |     |                       | bit 0                 |

| Legend:           | C = Clearable bit |                        |                    |

|-------------------|-------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared   | x = Bit is unknown |

| b | oit 7   | <b>TXBIF:</b> Transmit Buffer Interrupt Flag bit<br>1 = Transmit buffer has completed transmission of a message and may be reloaded<br>0 = Transmit buffer has not completed transmission of a message |

|---|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b | oit 6   | <b>TXABT:</b> Transmission Aborted Status bit <sup>(1)</sup>                                                                                                                                           |

|   |         | 1 = Message was aborted<br>0 = Message was not aborted                                                                                                                                                 |

| b | oit 5   | TXLARB: Transmission Lost Arbitration Status bit <sup>(1)</sup>                                                                                                                                        |

|   |         | <ul> <li>1 = Message lost arbitration while being sent</li> <li>0 = Message did not lose arbitration while being sent</li> </ul>                                                                       |

| b | oit 4   | TXERR: Transmission Error Detected Status bit <sup>(1)</sup>                                                                                                                                           |

|   |         | <ul> <li>1 = A bus error occurred while the message was being sent</li> <li>0 = A bus error did not occur while the message was being sent</li> </ul>                                                  |

| b | it 3    | TXREQ: Transmit Request Status bit <sup>(2)</sup>                                                                                                                                                      |

|   |         | <ul> <li>1 = Requests sending a message; clears the TXABT, TXLARB and TXERR bits</li> <li>0 = Automatically cleared when the message is successfully sent</li> </ul>                                   |

| b | it 2    | Unimplemented: Read as '0'                                                                                                                                                                             |

| b | it 1-0  | TXPRI<1:0>: Transmit Priority bits <sup>(3)</sup>                                                                                                                                                      |

|   |         | <pre>11 = Priority Level 3 (highest priority) 10 = Priority Level 2 01 = Priority Level 1 00 = Priority Level 0 (lowest priority)</pre>                                                                |

| Ν | lote 1: | This bit is automatically cleared when TXREQ is set.                                                                                                                                                   |

|   | 2:      | While TXREQ is set, Transmit Buffer registers remain read-only. Clearing this bit in software while the bit is                                                                                         |

|   |         |                                                                                                                                                                                                        |

- set will request a message abort.

- **3:** These bits define the order in which transmit buffers will be transferred. They do not alter the CAN message identifier.

# PIC18F66K80 FAMILY

# $\label{eq:register27-26:BnSIDL: TX/RX BUFFER `n' STANDARD IDENTIFIER REGISTERS, \\ LOW BYTE IN RECEIVE MODE [0 \le n \le 5, TXnEN (BSEL0<n>) = 0]^{(1)}$

| R-x                                                                                                                                                                                          | R-x                        | R-x                                                                 | R-x           | R-x              | U-0              | R-x             | R-x           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------|---------------|------------------|------------------|-----------------|---------------|

| SID2                                                                                                                                                                                         | SID1                       | SID0                                                                | SRR           | EXIDE            | _                | EID17           | EID16         |

| bit 7                                                                                                                                                                                        |                            |                                                                     | -             |                  |                  |                 | bit 0         |

|                                                                                                                                                                                              |                            |                                                                     |               |                  |                  |                 |               |

| Legend:                                                                                                                                                                                      |                            |                                                                     |               |                  |                  |                 |               |

| R = Readable                                                                                                                                                                                 | bit                        | W = Writable                                                        | bit           | U = Unimpler     | mented bit, read | as '0'          |               |

| -n = Value at F                                                                                                                                                                              | POR                        | '1' = Bit is set                                                    |               | '0' = Bit is cle | ared             | x = Bit is unkr | iown          |

| bit 4                                                                                                                                                                                        | SRR: Substitu              | ntifier bits, EID <sup>.</sup><br>ute Remote Tra<br>ays '1' when E2 | insmission Re | equest bit       | of RXRTRRO (     | BnCON<5>) w     | hen EXID = 0. |

| bit 3 <b>EXIDE:</b> Extended Identifier Enable bit<br>1 = Received message is an extended identifier frame (SID<10:0> are EID<28:18>)<br>0 = Received message is a standard identifier frame |                            |                                                                     |               |                  |                  |                 |               |

| bit 2                                                                                                                                                                                        | Unimplemented: Read as '0' |                                                                     |               |                  |                  |                 |               |

| bit 1-0                                                                                                                                                                                      | EID<17:16>:                | Extended Iden                                                       | tifier bits   |                  |                  |                 |               |

| Note 1: The                                                                                                                                                                                  | ese registers are          | e available in M                                                    | lode 1 and 2  | only.            |                  |                 |               |

###

| R/W-x | R/W-x | R/W-x | U-0 | R/W-x | U-0 | R/W-x | R/W-x |

|-------|-------|-------|-----|-------|-----|-------|-------|

| SID2  | SID1  | SID0  | —   | EXIDE |     | EID17 | EID16 |

| bit 7 |       |       |     |       |     |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-5 | SID<2:0>: Standard Identifier bits (if EXIDE (TXBnSIDL<3>) = 0)                                                                                                                      |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Extended Identifier bits, EID<20:18> (if EXIDE = 1).                                                                                                                                 |

| bit 4   | Unimplemented: Read as '0'                                                                                                                                                           |

| bit 3   | EXIDE: Extended Identifier Enable bit                                                                                                                                                |

|         | <ul> <li>1 = Message will transmit extended ID, SID&lt;10:0&gt; bits become EID&lt;28:18&gt;</li> <li>0 = Received will transmit standard ID, EID&lt;17:0&gt; are ignored</li> </ul> |

| bit 2   | Unimplemented: Read as '0'                                                                                                                                                           |

| bit 1-0 | EID<17:16>: Extended Identifier bits                                                                                                                                                 |

|         |                                                                                                                                                                                      |

Note 1: These registers are available in Mode 1 and 2 only.

| Mode 0       | R/W-1                                                                                                                          | R/W-1                                         | R/W-1           | R/W-1           | R/W-1                          | R/W-1                          | R/W-1           | R/W-1             |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------|-----------------|--------------------------------|--------------------------------|-----------------|-------------------|--|--|

| Mode U       | IRXIP                                                                                                                          | WAKIP                                         | ERRIP           | TXB2IP          | TXB1IP <sup>(1)</sup>          | TXB0IP <sup>(1)</sup>          | RXB1IP          | RXB0IP            |  |  |

|              | DAM 4                                                                                                                          |                                               | D 44/ 4         |                 |                                |                                |                 |                   |  |  |

| Mode 1,2     | R/W-1                                                                                                                          | R/W-1<br>WAKIP                                | R/W-1<br>ERRIP  | R/W-1<br>TXBnIP | R/W-1<br>TXB1IP <sup>(1)</sup> | R/W-1<br>TXB0IP <sup>(1)</sup> | R/W-1<br>RXBnIP | R/W-1<br>FIFOWMIP |  |  |

|              | bit 7                                                                                                                          | WANIF                                         |                 | IADIIIF         | IND IIF (                      | I ADUIF (                      | RADIIIF         | bit (             |  |  |

|              |                                                                                                                                |                                               |                 |                 |                                |                                |                 |                   |  |  |

| Legend:      |                                                                                                                                |                                               |                 |                 |                                |                                |                 |                   |  |  |

| R = Readal   | ole bit                                                                                                                        |                                               | W = Writabl     | e bit           | U = Unimple                    | emented bit, r                 | ead as '0'      |                   |  |  |

| -n = Value a | at POR                                                                                                                         |                                               | '1' = Bit is s  | et              | '0' = Bit is cl                | eared                          | x = Bit is un   | known             |  |  |

| bit 7        | IRXIP: CAN<br>1 = High pri<br>0 = Low prio                                                                                     |                                               | essage Rece     | ived Interrup   | ot Priority bit                |                                |                 |                   |  |  |

| bit 6        | <b>WAKIP:</b> CA<br>1 = High pri<br>0 = Low price                                                                              |                                               | y Wake-up In    | terrupt Prior   | ity bit                        |                                |                 |                   |  |  |

| bit 5        | ERRIP: CAI<br>1 = High pri<br>0 = Low pric                                                                                     |                                               | or Interrupt P  | riority bit     |                                |                                |                 |                   |  |  |