#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | ECANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 8x12b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f26k80-e-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Peripheral Highlights:

- Five CCP/ECCP modules:

- Four Capture/Compare/PWM (CCP) modules

- One Enhanced Capture/Compare/PWM (ECCP) module

- Five 8/16-Bit Timer/Counter modules:

- Timer0: 8/16-bit timer/counter with 8-bit programmable prescaler

- Timer1, Timer3: 16-bit timer/counter

- Timer2, Timer4: 8-bit timer/counter

- Two Analog Comparators

- Configurable Reference Clock Output

- Charge Time Measurement Unit (CTMU):

- Capacitance measurement

- Time measurement with 1 ns typical resolution

- Integrated voltage reference

- High-Current Sink/Source 25 mA/25 mA (PORTB and PORTC)

- · Up to Four External Interrupts

- One Master Synchronous Serial Port (MSSP) module:

- 3/4-wire SPI (supports all four SPI modes)

- $I^2C^{TM}$  Master and Slave modes

- Two Enhanced Addressable USART modules:

LIN/J2602 support

- Auto-Baud Detect (ABD)

- 12-Bit A/D Converter with up to 11 Channels:

- Auto-acquisition and Sleep operation

- Differential Input mode of operation

- Data Signal Modulator module:

- Select modulator and carrier sources from various module outputs

- Integrated Voltage Reference

#### **TABLE 1-4:** PIC18F2XK80 I/O DESCRIPTIONS

|                                   | Pin N | umber                   |             |                    |                                                                                                                           |  |  |  |

|-----------------------------------|-------|-------------------------|-------------|--------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                          | QFN   | SSOP/<br>SPDIP<br>/SOIC | Pin<br>Type | Buffer<br>Type     | Description                                                                                                               |  |  |  |

| MCLR/RE3                          | 26    | 1                       |             |                    |                                                                                                                           |  |  |  |

| MCLR                              |       |                         | Ι           | ST                 | Master Clear (input) or programming voltage (input). This pin is an active-low Reset to the device.                       |  |  |  |

| RE3                               |       |                         | Ι           | ST                 | General purpose, input only pin.                                                                                          |  |  |  |

| OSC1/CLKIN/RA7                    | 6     | 9                       |             |                    |                                                                                                                           |  |  |  |

| OSC1                              |       |                         | I           | ST                 | Oscillator crystal input.                                                                                                 |  |  |  |

| CLKIN                             |       |                         | I           | CMOS               | External clock source input. Always associated with pin<br>function, OSC1. (See related OSC1/CLKI, OSC2/CLKO<br>pins.)    |  |  |  |

| RA7                               |       |                         | I/O         | ST/<br>CMOS        | General purpose I/O pin.                                                                                                  |  |  |  |

| OSC2/CLKOUT/RA6                   | 7     | 10                      |             |                    |                                                                                                                           |  |  |  |

| OSC2                              |       |                         | 0           | —                  | Oscillator crystal output.<br>Connects to crystal or resonator in Crystal Oscillator mode.                                |  |  |  |

| CLKOUT                            |       |                         | 0           | —                  | In certain oscillator modes, OSC2 pin outputs CLKO, wh has 1/4 the frequency of OSC1 and denotes the instructicycle rate. |  |  |  |

| RA6                               |       |                         | I/O         | ST/<br>CMOS        | General purpose I/O pin.                                                                                                  |  |  |  |

| Legend: CMOS = CMOS<br>ST = Schmi |       |                         |             | output<br>MOS leve | $I^2 C^{TM} = I^2 C/SMBus input buffer$<br>els Analog = Analog input                                                      |  |  |  |

L = Input

Ρ = Power

= Output 0

#### 2.2 Power Supply Pins

#### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

#### 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ .

### 2.3 Master Clear (MCLR) Pin

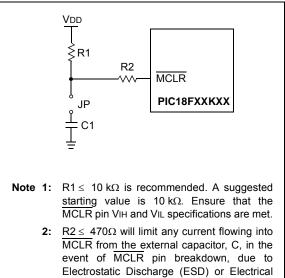

The MCLR pin provides two specific device functions: Device Reset, and Device Programming and Debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

#### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

Overstress (EOS). Ensure that the MCLR pin

VIH and VIL specifications are met.

### 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

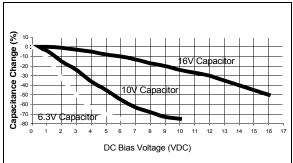

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R), or -20%/+80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex:  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%$ . Due to the extreme temperature tolerance, a 10  $\mu$ F nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal regulator if the application must operate over a wide temperature range.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

A typical DC bias voltage vs. capacitance graph for X7R type and Y5V type capacitors is shown in Figure 2-4.

#### FIGURE 2-4: DC BIAS VOLTAGE vs. CAPACITANCE CHARACTERISTICS

When selecting a ceramic capacitor to be used with the internal voltage regulator, it is suggested to select a high-voltage rating, so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at 16V for the 2.5V core voltage. Suggested capacitors are shown in Table 2-1.

#### 2.5 ICSP Pins

The PGC and PGD pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100 $\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGC and PGD pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGCx/PGDx pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 30.0 "Development Support"**.

| R/W-0           | R/W-0                                                | R/W-0                      | R/W-0                   | R/W-0                                             | R/W-0            | R/W-0           | R/W-0        |

|-----------------|------------------------------------------------------|----------------------------|-------------------------|---------------------------------------------------|------------------|-----------------|--------------|

| INTSRC          | PLLEN                                                | TUN5                       | TUN4                    | TUN3                                              | TUN2             | TUN1            | TUN0         |

| bit 7           |                                                      |                            |                         |                                                   |                  |                 | bit 0        |

| Legend:         |                                                      |                            |                         |                                                   |                  |                 |              |

| R = Readable    | bit                                                  | W = Writable               | bit                     | U = Unimpler                                      | nented bit, read | l as '0'        |              |

| -n = Value at I | POR                                                  | '1' = Bit is set           |                         | '0' = Bit is clea                                 |                  | x = Bit is unkn | iown         |

| bit 7           | 1 = 31.25 kH                                         | z device clock is          | derived from            | y Source Selec<br>16 MHz INTOSC<br>ITOSC 31 kHz ( | source (divide-  |                 | I, HF-INTOSC |

| bit 6           |                                                      | luency Multiplie<br>nabled |                         |                                                   | , ,              |                 |              |

| bit 5-0         | 011111 = Ma<br>•<br>0000001<br>000000 = Ce<br>111111 | aximum frequer<br>•<br>•   | ncy<br>; fast RC oscill | requency Tunir                                    | -                | d frequency     |              |

#### REGISTER 3-3: OSCTUNE: OSCILLATOR TUNING REGISTER

| EXAMPLE 7-3: | WRITING TO FLASH PROGRAM MEMORY (CONTINUED) |

|--------------|---------------------------------------------|

| PROGRAM_MEMORY |       |         |       |                                 |

|----------------|-------|---------|-------|---------------------------------|

|                | BSF   | EECON1, | EEPGD | ; point to Flash program memory |

|                | BCF   | EECON1, | CFGS  | ; access Flash program memory   |

|                | BSF   | EECON1, | WREN  | ; enable write to memory        |

|                | BCF   | INTCON, | GIE   | ; disable interrupts            |

|                | MOVLW | 55h     |       |                                 |

| Required       | MOVWF | EECON2  |       | ; write 55h                     |

| Sequence       | MOVLW | 0AAh    |       |                                 |

|                | MOVWF | EECON2  |       | ; write OAAh                    |

|                | BSF   | EECON1, | WR    | ; start program (CPU stall)     |

|                | BSF   | INTCON, | GIE   | ; re-enable interrupts          |

|                | BCF   | EECON1, | WREN  | ; disable write to memory       |

|                |       |         |       |                                 |

#### 7.5.2 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

### 7.5.3 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed if needed. If the write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation, the user can check the WRERR bit and rewrite the location(s) as needed.

#### 7.5.4 PROTECTION AGAINST SPURIOUS WRITES

To protect against spurious writes to Flash program memory, the write initiate sequence must also be followed. See **Section 28.0** "**Special Features of the CPU**" for more detail.

#### 7.6 Flash Program Operation During Code Protection

See Section 28.6 "Program Verification and Code Protection" for details on code protection of Flash program memory.

| Name    | Bit 7                                                 | Bit 6          | Bit 5                 | Bit 4           | Bit 3         | Bit 2          | Bit 1         | Bit 0   |  |  |

|---------|-------------------------------------------------------|----------------|-----------------------|-----------------|---------------|----------------|---------------|---------|--|--|

| TBLPTRU | _                                                     | _              | bit 21 <sup>(1)</sup> | Program Mer     | nory Table Po | inter Upper By | /te (TBLPTR<  | 20:16>) |  |  |

| TBPLTRH | Program Memory Table Pointer High Byte (TBLPTR<15:8>) |                |                       |                 |               |                |               |         |  |  |

| TBLPTRL | Program Me                                            | mory Table Po  | ointer Low            | Byte (TBLPT     | R<7:0>)       |                |               |         |  |  |

| TABLAT  | Program Memory Table Latch                            |                |                       |                 |               |                |               |         |  |  |

| INTCON  | GIE/GIEH                                              | PEIE/GIEL      | TMR0IE                | INT0IE          | RBIE          | TMR0IF         | <b>INT0IF</b> | RBIF    |  |  |

| EECON2  | EEPROM Co                                             | ontrol Registe | r 2 (not a p          | ohysical regist | ter)          |                |               |         |  |  |

| EECON1  | EEPGD                                                 | CFGS           | _                     | FREE            | WRERR         | WREN           | WR            | RD      |  |  |

| IPR4    | TMR4IP                                                | EEIP           | CMP2IP                | CMP1IP          | _             | CCP5IP         | CCP4IP        | CCP3IP  |  |  |

| PIR4    | TMR4IF                                                | EEIF           | CMP2IF                | CMP1IF          |               | CCP5IF         | CCP4IF        | CCP3IF  |  |  |

| PIE4    | TMR4IE                                                | EEIE           | CMP2IE                | CMP1IE          |               | CCP5IE         | CCP4IE        | CCP3IE  |  |  |

#### TABLE 7-2: REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

Legend: — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

**Note 1:** Bit 21 of the TBLPTRU allows access to the device Configuration bits.

### REGISTER 10-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2

| R/W-0  | U-0 | U-0 | U-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0   |

|--------|-----|-----|-----|-------|--------|--------|---------|

| OSCFIF | —   | —   | —   | BCLIF | HLVDIF | TMR3IF | TMR3GIF |

| bit 7  |     |     |     |       |        |        | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | <b>OSCFIF:</b> Oscillator Fail Interrupt Flag bit<br>1 = Device oscillator failed, clock input has changed to INTOSC (bit must be cleared in software)<br>0 = Device clock is operating |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-4 | Unimplemented: Read as '0'                                                                                                                                                              |

| bit 3   | BCLIF: Bus Collision Interrupt Flag bit                                                                                                                                                 |

|         | <ul> <li>1 = A bus collision occurred (bit must be cleared in software)</li> <li>0 = No bus collision occurred</li> </ul>                                                               |

| bit 2   | HLVDIF: High/Low-Voltage Detect Interrupt Flag bit                                                                                                                                      |

|         | <ul> <li>1 = A low-voltage condition occurred (bit must be cleared in software)</li> <li>0 = The device voltage is above the regulator's low-voltage trip point</li> </ul>              |

| bit 1   | TMR3IF: TMR3 Overflow Interrupt Flag bit                                                                                                                                                |

|         | <ul> <li>1 = TMR3 register overflowed (bit must be cleared in software)</li> <li>0 = TMR3 register did not overflow</li> </ul>                                                          |

| bit 0   | <ul> <li>TMR3GIF: TMR3 Gate Interrupt Flag bit</li> <li>1 = Timer gate interrupt occurred (bit must be cleared in software)</li> <li>0 = No timer gate interrupt occurred</li> </ul>    |

| U-0                          | U-0                                                                           | R-0                                                                                             | R-0             | R/W-0               | R/W-0           | R/W-0            | U-0 |  |  |  |  |  |  |

|------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------|---------------------|-----------------|------------------|-----|--|--|--|--|--|--|

| _                            | _                                                                             | RC2IF                                                                                           | TX2IF           | CTMUIF              | CCP2IF          | CCP1IF           | _   |  |  |  |  |  |  |

| oit 7                        |                                                                               |                                                                                                 |                 |                     |                 |                  | bit |  |  |  |  |  |  |

|                              |                                                                               |                                                                                                 |                 |                     |                 |                  |     |  |  |  |  |  |  |

| <b>Legend:</b><br>R = Readal | ble bit                                                                       | W = Writable                                                                                    | hit             | U = Unimpler        | nented bit rea  | 1 as '0'         |     |  |  |  |  |  |  |

| -n = Value a                 |                                                                               | '1' = Bit is set                                                                                | 510             | '0' = Bit is clea   |                 | x = Bit is unkno | own |  |  |  |  |  |  |

|                              |                                                                               |                                                                                                 |                 |                     |                 |                  | -   |  |  |  |  |  |  |

| bit 7-6                      | Unimplemen                                                                    | ted: Read as '                                                                                  | )'              |                     |                 |                  |     |  |  |  |  |  |  |

| bit 5                        | RC2IF: EUSA                                                                   | ARTx Receive I                                                                                  | nterrupt Flag b | oit                 |                 |                  |     |  |  |  |  |  |  |

|                              |                                                                               |                                                                                                 |                 | 62, is full (cleare | d when RCRE     | G2 is read)      |     |  |  |  |  |  |  |

|                              |                                                                               | SARTx receive b                                                                                 |                 |                     |                 |                  |     |  |  |  |  |  |  |

| bit 4                        |                                                                               | RTx Transmit I                                                                                  |                 |                     |                 |                  | 、   |  |  |  |  |  |  |

|                              |                                                                               | SARTX transmit                                                                                  |                 | 32, is empty (cle   | eared when 1    | REG2 is written  | )   |  |  |  |  |  |  |

| bit 3                        |                                                                               | MU Interrupt Fla                                                                                |                 |                     |                 |                  |     |  |  |  |  |  |  |

|                              |                                                                               | •                                                                                               | •               | ared in software    | e)              |                  |     |  |  |  |  |  |  |

|                              |                                                                               | U interrupt occu                                                                                |                 |                     | ,               |                  |     |  |  |  |  |  |  |

| bit 2                        | CCP2IF: CCF                                                                   | P2 Interrupt Fla                                                                                | g bit           |                     |                 |                  |     |  |  |  |  |  |  |

|                              | Capture mod                                                                   |                                                                                                 |                 |                     |                 |                  |     |  |  |  |  |  |  |

|                              |                                                                               |                                                                                                 |                 | red (must be cle    | eared in softwa | ire)             |     |  |  |  |  |  |  |

|                              |                                                                               | 0 = No TMR1/TMR3 register capture occurred<br><u>Compare mode:</u>                              |                 |                     |                 |                  |     |  |  |  |  |  |  |

|                              | 1 = A TMR1/TMR3 register compare match occurred (must be cleared in software) |                                                                                                 |                 |                     |                 |                  |     |  |  |  |  |  |  |

|                              |                                                                               | 0 = No TMR1/TMR3 register compare match occurred                                                |                 |                     |                 |                  |     |  |  |  |  |  |  |

|                              | <u>PWM mode:</u><br>Unused in thi                                             | o modo                                                                                          |                 |                     |                 |                  |     |  |  |  |  |  |  |

| bit 1                        |                                                                               | S mode.<br>CP1 Interrupt FI                                                                     | aa hit          |                     |                 |                  |     |  |  |  |  |  |  |

|                              |                                                                               | -                                                                                               | ay bit          |                     |                 |                  |     |  |  |  |  |  |  |

|                              |                                                                               | <u>Capture mode:</u><br>1 = A TMR1/TMR3 register capture occurred (must be cleared in software) |                 |                     |                 |                  |     |  |  |  |  |  |  |

|                              | 0 = No TMR                                                                    | 0 = No TMR1/TMR3 register capture occurred                                                      |                 |                     |                 |                  |     |  |  |  |  |  |  |

|                              | Compare mo                                                                    |                                                                                                 |                 |                     |                 | <i>a</i> )       |     |  |  |  |  |  |  |

|                              |                                                                               | 1 MR3 register<br>1/TMR3 registe                                                                |                 | ch occurred (mu     | st be cleared i | n software)      |     |  |  |  |  |  |  |

|                              | PWM mode:                                                                     | in thir to registe                                                                              |                 |                     |                 |                  |     |  |  |  |  |  |  |

|                              | Unused in thi                                                                 | s mode.                                                                                         |                 |                     |                 |                  |     |  |  |  |  |  |  |

|                              |                                                                               |                                                                                                 |                 |                     |                 |                  |     |  |  |  |  |  |  |

#### REGISTER 10-6: PIR3: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 3

|         |       |       | -                   |                     | -      | -      | -      |        |

|---------|-------|-------|---------------------|---------------------|--------|--------|--------|--------|

| Name    | Bit 7 | Bit 6 | Bit 5               | Bit 4               | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

| PORTG   |       | _     |                     | RG4                 | RG3    | RG2    | RG1    | RG0    |

| TRISG   | —     | —     | _                   | TRISG4              | TRISG3 | TRISG2 | TRISG1 | TRISG0 |

| PADCFG1 | RDPU  | REPU  | RFPU <sup>(1)</sup> | RGPU <sup>(1)</sup> |        |        |        | CTMUDS |

TABLE 11-14:

SUMMARY OF REGISTERS ASSOCIATED WITH PORTG

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PORTG.

Note 1: These bits are unimplemented on 28-pin devices; read as '0'.

#### 18.1 CTMU Registers

The control registers for the CTMU are:

- CTMUCONH

- CTMUCONL

- CTMUICON

The CTMUCONH and CTMUCONL registers (Register 18-1 and Register 18-2) contain control bits for configuring the CTMU module edge source selection, edge source polarity selection, edge sequencing, A/D trigger, analog circuit capacitor discharge and enables. The CTMUICON register (Register 18-3) has bits for selecting the current source range and current source trim.

#### REGISTER 18-1: CTMUCONH: CTMU CONTROL HIGH REGISTER

| R/W-0  | U-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0    | R/W-0   | R/W-0  |

|--------|-----|----------|-------|-------|----------|---------|--------|

| CTMUEN | _   | CTMUSIDL | TGEN  | EDGEN | EDGSEQEN | IDISSEN | CTTRIG |

| bit 7  |     |          |       |       |          |         | bit 0  |

|        |     |          |       |       |          |         |        |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| hit | t 7 | CTMUEN: CTMU Enable bit                                                                                                              |

|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------|

|     |     | 1 = Module is enabled                                                                                                                |

|     |     | 0 = Module is disabled                                                                                                               |

|     |     |                                                                                                                                      |

| bit | t 6 | Unimplemented: Read as '0'                                                                                                           |

| bit | t 5 | CTMUSIDL: Stop in Idle Mode bit                                                                                                      |

|     |     | <ul><li>1 = Discontinues module operation when device enters Idle mode</li><li>0 = Continues module operation in Idle mode</li></ul> |

| bit | t 4 | TGEN: Time Generation Enable bit                                                                                                     |

|     |     | 1 = Enables edge delay generation                                                                                                    |

|     |     | 0 = Disables edge delay generation                                                                                                   |

| bit | t 3 | EDGEN: Edge Enable bit                                                                                                               |

|     |     | 1 = Edges are not blocked                                                                                                            |

|     |     | 0 = Edges are blocked                                                                                                                |

| bit | t 2 | ESGSEQEN: Edge Sequence Enable bit                                                                                                   |

|     |     | 1 = Edge 1 event must occur before Edge 2 event can occur                                                                            |

|     |     | 0 = No edge sequence is needed                                                                                                       |

| bit | t 1 | IDISSEN: Analog Current Source Control bit                                                                                           |

|     |     | 1 = Analog current source output is grounded                                                                                         |

|     |     | 0 = Analog current source output is not grounded                                                                                     |

| bit | t 0 | CTTRIG: CTMU Special Event Trigger bit                                                                                               |

|     |     | 1 = CTMU Special Event Trigger is enabled                                                                                            |

|     |     | 0 = CTMU Special Event Trigger is disabled                                                                                           |

|     |     |                                                                                                                                      |

### 19.3 Compare Mode

In Compare mode, the 16-bit CCPRx register value is constantly compared against the Timer register pair value selected in the CCPTMR register. When a match occurs, the CCPx pin can be:

- Driven high

- Driven low

- Toggled (high-to-low or low-to-high)

- Unchanged (that is, reflecting the state of the I/O latch)

The action on the pin is based on the value of the mode select bits (CCPxM<3:0>). At the same time, the interrupt flag bit, CCPxIF, is set.

Figure 19-2 gives the Compare mode block diagram

#### 19.3.1 CCP PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the appropriate TRIS bit.

| Note: | Clearing the CCPxCON register will force  |

|-------|-------------------------------------------|

|       | the corresponding CCPx compare output     |

|       | latch (depending on device configuration) |

|       | to the default low level. This is not the |

|       | PORTx data latch.                         |

#### 19.3.2 TIMER1/3 MODE SELECTION

If the CCPx module is using the compare feature in conjunction with any of the Timer1/3 timers, the timers must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the compare operation may not work.

Note: Details of the timer assignments for the CCPx modules are given in Table 19-2.

#### 19.3.3 SOFTWARE INTERRUPT MODE

When the Generate Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPx pin is not affected. Only a CCP interrupt is generated, if enabled, and the CCPxIE bit is set.

#### 19.3.4 SPECIAL EVENT TRIGGER

All CCP modules are equipped with a Special Event Trigger. This is an internal hardware signal generated in Compare mode to trigger actions by other modules. The Special Event Trigger is enabled by selecting the Compare Special Event Trigger mode bits (CCPxM<3:0> = 1011).

For either CCPx module, the Special Event Trigger resets the Timer register pair for whichever timer resource is currently assigned as the module's time base. This allows the CCPRx registers to serve as a programmable Period register for either timer.

#### 21.3.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register 1 (SSPCON1)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON1 and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON1 register is readable and writable. The lower 6 bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write.

SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together, create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not double-buffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

#### REGISTER 21-1: SSPSTAT: MSSP STATUS REGISTER (SPI MODE)

| -             |                                                                      |                                      |                  | <b>\</b> -        | ,                          |                 |             |

|---------------|----------------------------------------------------------------------|--------------------------------------|------------------|-------------------|----------------------------|-----------------|-------------|

| R/W-0         | R/W-0                                                                | R-0                                  | R-0              | R-0               | R-0                        | R-0             | R-0         |

| SMP           | CKE <sup>(1)</sup>                                                   | D/A                                  | Р                | S                 | R/W                        | UA              | BF          |

| bit 7         | •                                                                    |                                      |                  |                   |                            |                 | bit (       |

|               |                                                                      |                                      |                  |                   |                            |                 |             |

| Legend:       |                                                                      |                                      |                  |                   |                            |                 |             |

| R = Readabl   | e bit                                                                | W = Writable                         | bit              | U = Unimplen      | nented bit, rea            | d as '0'        |             |

| -n = Value at | POR                                                                  | '1' = Bit is set                     |                  | '0' = Bit is cle  | ared                       | x = Bit is unkr | nown        |

|               |                                                                      |                                      |                  |                   |                            |                 |             |

| bit 7         | SMP: Samp                                                            |                                      |                  |                   |                            |                 |             |

|               | SPI Master r                                                         |                                      |                  |                   |                            |                 |             |

|               |                                                                      | ta is sampled at<br>ta is sampled at |                  |                   | 2                          |                 |             |

|               | SPI Slave m                                                          |                                      |                  | data output tint  |                            |                 |             |

|               |                                                                      | e cleared when                       | SPI is used in   | Slave mode.       |                            |                 |             |

| bit 6         | CKE: SPI CI                                                          | lock Select bit <sup>(1)</sup>       |                  |                   |                            |                 |             |

|               |                                                                      | t occurs on trans                    |                  |                   |                            |                 |             |

|               |                                                                      | t occurs on trans                    | sition from Idle | e to active clock | state                      |                 |             |

| bit 5         | D/A: Data/A                                                          |                                      |                  |                   |                            |                 |             |

|               |                                                                      | ™ mode only.                         |                  |                   |                            |                 |             |

| bit 4         | P: Stop bit                                                          |                                      | 1.10.1.1.1.1.1.1 |                   |                            |                 |             |

| L:1 0         |                                                                      | mode only. This                      | bit is cleared   | when the MSSF     | <sup>2</sup> module is dis | abled; SSPEN    | is cleared. |

| bit 3         | S: Start bit<br>Used in I <sup>2</sup> C                             | modo only                            |                  |                   |                            |                 |             |

| bit 2         |                                                                      | Write Information                    | , hit            |                   |                            |                 |             |

|               |                                                                      |                                      |                  |                   |                            |                 |             |

| bit 1         | Used in I <sup>2</sup> C mode only.<br><b>UA:</b> Update Address bit |                                      |                  |                   |                            |                 |             |

| ~             | Used in I <sup>2</sup> C                                             |                                      |                  |                   |                            |                 |             |

| bit 0         |                                                                      | ull Status bit (Re                   | eceive mode o    | only)             |                            |                 |             |

|               |                                                                      | is complete, SS                      |                  | <i>,</i>          |                            |                 |             |

|               |                                                                      | is not complete                      |                  | empty             |                            |                 |             |

| Note 1: P     | olarity of clock                                                     | state is set by th                   | ne CKP bit (S    | SPCON1<4>)        |                            |                 |             |

|               |                                                                      |                                      |                  |                   |                            |                 |             |

Note 1: Polarity of clock state is set by the CKP bit (SSPCON1<4>).

#### 21.4.10 I<sup>2</sup>C<sup>™</sup> MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address, is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification Parameter 106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification Parameter 107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared; if not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 21-23).

After the write to the SSPBUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF flag is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 21.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

#### 21.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur) after 2 TcY after the SSPBUF write. If SSPBUF is rewritten within 2 TcY, the WCOL bit is set and SSPBUF is updated. This may result in a corrupted transfer. The user should verify that the WCOL bit is clear after each write to SSPBUF to ensure the transfer is correct. In all cases, WCOL must be cleared in software.

#### 21.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge ( $\overline{ACK} = 0$ ) and is set when the slave does not Acknowledge ( $\overline{ACK} = 1$ ). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

#### 21.4.11 I<sup>2</sup>C<sup>™</sup> MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

| Note: | The MSSP module must be in an inactive  |

|-------|-----------------------------------------|

|       | state before the RCEN bit is set or the |

|       | RCEN bit will be disregarded.           |

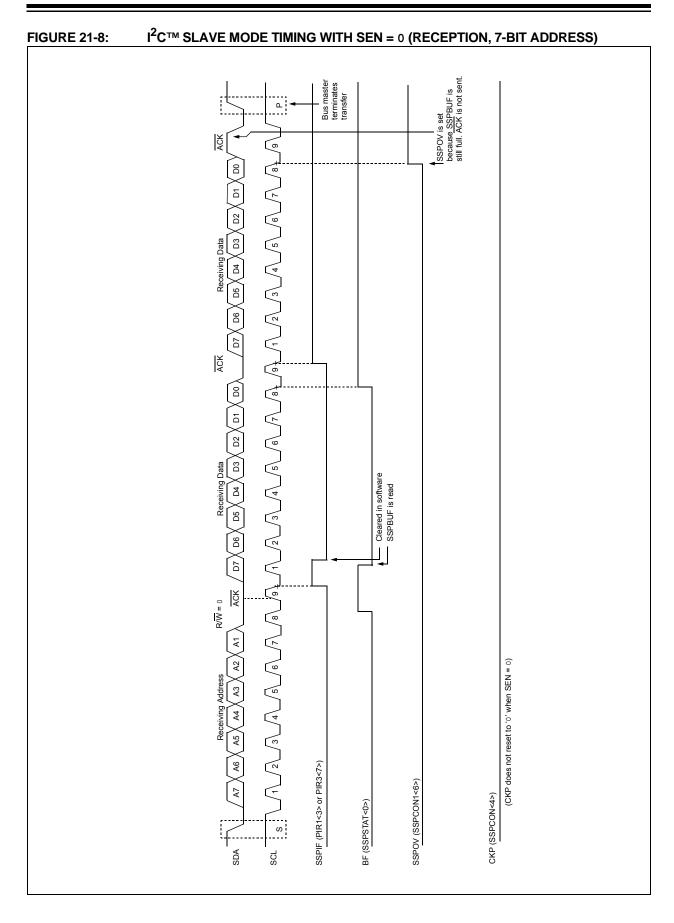

The Baud Rate Generator begins counting, and on each rollover, the state of the SCL pin changes (high-to-low/low-to-high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

#### 21.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

#### 21.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 21.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

#### 27.2.3 DEDICATED CAN RECEIVE BUFFER REGISTERS

This section shows the dedicated CAN Receive Buffer registers with their associated control registers.

#### REGISTER 27-13: RXB0CON: RECEIVE BUFFER 0 CONTROL REGISTER

| Mode 0     | R/C-0                                   | R/W-0            | R/W-0                               | U-0           | R-0             | R/W-0             | R-0                  | R-0          |

|------------|-----------------------------------------|------------------|-------------------------------------|---------------|-----------------|-------------------|----------------------|--------------|

| wode u     | RXFUL <sup>(1)</sup>                    | RXM1             | RXM0                                | _             | RXRTRRO         | RXB0DBEN          | JTOFF <sup>(2)</sup> | FILHIT0      |

|            | T                                       |                  |                                     |               |                 |                   |                      |              |

| Mode 1,2   | R/C-0                                   | R/W-0            | R-0                                 | R-0           | R-0             | R-0               | R-0                  | R-0          |

|            | RXFUL <sup>(1)</sup>                    | RXM1             | RTRRO                               | FILHITF4      | FILHIT3         | FILHIT2           | FILHIT1              | FILHIT0      |

|            | bit 7                                   |                  |                                     |               |                 |                   |                      | bit 0        |

| Legend:    |                                         |                  | C = Clearabl                        | e bit         |                 |                   |                      |              |

| R = Read   | able bit                                |                  | W = Writable                        | e bit         | U = Unimple     | emented bit, re   | ad as '0'            |              |

| -n = Value | e at POR                                |                  | '1' = Bit is se                     | et            | '0' = Bit is c  | leared            | x = Bit is un        | known        |

|            |                                         |                  | (1)                                 |               |                 |                   |                      |              |

| bit 7      | RXFUL: Rec                              |                  |                                     |               |                 |                   |                      |              |

|            |                                         |                  | ns a received n<br>n to receive a r | •             | 0               |                   |                      |              |

| bit 6,6-5  | Mode 0:                                 | bullet is oper   | I to receive a r                    | iew messag    | C               |                   |                      |              |

| bit 0,0-5  |                                         | Receive Buffe    | er Mode bit 1 (d                    | combines wi   | th RXM0 to f    | orm RXM<1:0       | > bits, see bi       | t 5)         |

|            |                                         |                  | s (including th                     |               |                 |                   |                      | ,            |

|            |                                         |                  | essages with e                      |               |                 |                   |                      | 1'           |

|            |                                         |                  | essages with                        |               |                 |                   |                      | )'           |

|            |                                         | e all valid mes  | ssages as per                       | the EXIDEN    | bit in the RX   | FnSIDL regist     | er                   |              |

|            | <u>Mode 1, 2:</u><br><b>RXM1</b> : Rece | ive Ruffer Mo    | de hit 1                            |               |                 |                   |                      |              |

|            |                                         |                  | (including tho                      | se with erro  | rs): accentan   | ce filters are ic | inored               |              |

|            |                                         |                  | ages as per a                       |               |                 |                   | linered              |              |

| bit 5      | Mode 0:                                 |                  | •                                   | ·             |                 |                   |                      |              |

|            | RXM0: Rece                              | ive Buffer Mo    | ode bit 0 (comb                     | oines with R  | XM1 to form I   | RXM<1:0>bits      | , see bit 6)         |              |

|            | <u>Mode 1, 2:</u>                       |                  |                                     |               |                 | <i>,</i>          |                      |              |

|            |                                         |                  | ission Request                      |               | eived Messag    | je (read-only)    |                      |              |

|            |                                         |                  | n request is rea<br>n request is no |               |                 |                   |                      |              |

| bit 4      | Mode 0:                                 |                  |                                     |               |                 |                   |                      |              |

| DIC 4      | Unimplemer                              | nted: Read as    | <b>s</b> '0'                        |               |                 |                   |                      |              |

|            | Mode 1, 2:                              |                  |                                     |               |                 |                   |                      |              |

|            | FILHIT<4:0>                             |                  |                                     |               |                 |                   |                      |              |

|            |                                         | pines with oth   | er bits to form                     | filter accept | ance bits<4:0   | )>.               |                      |              |

| bit 3      | Mode 0:                                 | Domoto Tron      | ominaian Dagu                       | oot hit for D | agained Maa     | and (read on      | h. A)                |              |

|            |                                         |                  | smission Requ                       |               | eceived ivies   | sage (read-on     | iy)                  |              |

|            |                                         |                  | n request is rea<br>n request is no |               |                 |                   |                      |              |

|            | Mode 1, 2:                              |                  |                                     |               |                 |                   |                      |              |

|            | FILHIT<4:0>                             | : Filter Hit bit | 3                                   |               |                 |                   |                      |              |

|            | This bit comb                           | pines with oth   | er bits to form                     | filter accept | ance bits<4:0   | )>.               |                      |              |

| Note 1:    | This bit is set                         | by the CAN r     | nodule upon re                      | eceiving a m  | essage and      | must be cleare    | ed by softwar        | e after the  |

|            | buffer is read.                         | As long as F     | RXFUL is set, r                     | no new mes    | sage will be lo | baded and the     | buffer will be       | e considered |

|            | full. After clea                        |                  |                                     | R5 bit, RXB   | DIF, can be cl  | eared. If RXB0    | IF is cleared        | , but RXFUL  |

| •          | is not cleared,<br>This bit allows      |                  | -                                   |               |                 |                   |                      |              |

|            |                                         | e ino samo fili  | ior ilimn tanla t                   |               | succusi and F   |                   |                      |              |

2: This bit allows the same filter jump table for both RXB0CON and RXB1CON.

#### REGISTER 28-3: CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h)

| U-0   | R/P-1                  | R/P-1                  | R/P-1                | R/P-1                | R/P-1                 | R/P-1                 | R/P-1                 |

|-------|------------------------|------------------------|----------------------|----------------------|-----------------------|-----------------------|-----------------------|

| _     | BORPWR1 <sup>(1)</sup> | BORPWR0 <sup>(1)</sup> | BORV1 <sup>(1)</sup> | BORV0 <sup>(1)</sup> | BOREN1 <sup>(2)</sup> | BOREN0 <sup>(2)</sup> | PWRTEN <sup>(2)</sup> |

| bit 7 |                        |                        |                      |                      |                       |                       | bit 0                 |

| Legend:           | P = Programmable bit |                            |                    |

|-------------------|----------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                     |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-5 | BORPWR<1:0>: BORMV Power-Level bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                             |

|         | <ul> <li>11 = ZPBORVMV instead of BORMV is selected</li> <li>10 = BORMV is set to a high-power level</li> </ul>                                                                                                                                                                                                                                                |

|         | 01 = BORMV is set to a medium power level<br>00 = BORMV is set to a low-power level                                                                                                                                                                                                                                                                            |

| bit 4-3 | BORV<1:0>: Brown-out Reset Voltage bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                         |

|         | 11 = BVDD is set to 1.8V<br>10 = BVDD is set to 2.0V<br>01 = BVDD is set to 2.7V<br>00 = BVDD is set to 3.0V                                                                                                                                                                                                                                                   |

| bit 2-1 | BOREN<1:0>: Brown-out Reset Enable bits <sup>(2)</sup>                                                                                                                                                                                                                                                                                                         |

|         | <ul> <li>11 = Brown-out Reset is enabled in hardware only (SBOREN is disabled)</li> <li>10 = Brown-out Reset is enabled in hardware only and disabled in Sleep mode (SBOREN is disabled)</li> <li>01 = Brown-out Reset is enabled and controlled by software (SBOREN is enabled)</li> <li>00 = Brown-out Reset is disabled in hardware and software</li> </ul> |

| bit 0   | <b>PWRTEN:</b> Power-up Timer Enable bit <sup>(2)</sup>                                                                                                                                                                                                                                                                                                        |

|         | 1 = PWRT disabled<br>0 = PWRT enabled                                                                                                                                                                                                                                                                                                                          |

| Note 1: | For the specifications, see Section 31.1 "DC Characteristics: Supply Voltage PIC18F66K80 Family<br>(Industrial/Extended)".                                                                                                                                                                                                                                     |

2: The Power-up Timer is decoupled from Brown-out Reset, allowing these features to be independently controlled.

| RETFIE Return from Interrupt |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                 |                                           |                                             |  |

|------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------------------|--|

| Synta                        | ax:                                         | RETFIE {s                                                                                                                                                                                                                                                                                                                                                                                                       | ;}                                        |                                             |  |

| Oper                         | ands:                                       | $s \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                   |                                           |                                             |  |

| Oper                         | ation:                                      | $(TOS) \rightarrow PC,$<br>$1 \rightarrow GIE/GIEH \text{ or PEIE/GIEL};$<br>if s = 1,<br>$(WS) \rightarrow W,$<br>$(STATUSS) \rightarrow STATUS,$<br>$(BSRS) \rightarrow BSR,$<br>PCLATU, PCLATH are unchanged                                                                                                                                                                                                 |                                           |                                             |  |

| Statu                        | s Affected:                                 | GIE/GIEH,                                                                                                                                                                                                                                                                                                                                                                                                       | PEIE/GIEL.                                |                                             |  |

| Enco                         | ding:                                       | 0000                                                                                                                                                                                                                                                                                                                                                                                                            | 0000 000                                  | 01 000s                                     |  |

| Desc                         | ription:                                    | Return from interrupt. Stack is popped<br>and Top-of-Stack (TOS) is loaded into<br>the PC. Interrupts are enabled by<br>setting either the high or low-priority<br>Global Interrupt Enable bit. If 's' = 1, th<br>contents of the shadow registers WS,<br>STATUSS and BSRS are loaded into<br>their corresponding registers W,<br>STATUS and BSR. If 's' = 0, no update<br>of these registers occurs (default). |                                           |                                             |  |

| Word                         | ls:                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                               | ,                                         | ()                                          |  |