Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

:XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | ECANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6К х 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x12b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN-S (6x6)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f26k80-h-mm |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.1.3 CLOCK TRANSITIONS AND STATUS INDICATORS

The length of the transition between clock sources is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable. The HF-INTOSC and MF-INTOSC are termed as INTOSC in this chapter.

Three bits indicate the current clock source and its status, as shown in Table 4-2. The three bits are:

- OSTS (OSCCON<3>)

- HFIOFS (OSCCON<2>)

- SOSCRUN (OSCCON2<6>)

TABLE 4-2: SYSTEM CLOCK INDICATOR

| Main Clock Source                                      | OSTS | HFIOFS or<br>MFIOFS | SOSCRUN |

|--------------------------------------------------------|------|---------------------|---------|

| Primary Oscillator                                     | 1    | 0                   | 0       |

| INTOSC (HF-INTOSC<br>or MF-INTOSC)                     | 0    | 1                   | 0       |

| Secondary Oscillator                                   | 0    | 0                   | 1       |

| MF-INTOSC or<br>HF-INTOSC as Primary<br>Clock Source   | 1    | 1                   | 0       |

| LF-INTOSC is<br>Running or INTOSC is<br>Not Yet Stable | 0    | 0                   | 0       |

When the OSTS bit is set, the primary clock is providing the device clock. When the HFIOFS or MFIOFS bit is set, the INTOSC output is providing a stable clock source to a divider that actually drives the device clock. When the SOSCRUN bit is set, the SOSC oscillator is providing the clock. If none of these bits are set, either the LF-INTOSC clock source is clocking the device or the INTOSC source is not yet stable.

If the internal oscillator block is configured as the primary clock source by the FOSC<3:0> Configuration bits (CONFIG1H<3:0>). Then, the OSTS and HFIOFS or MFIOFS bits can be set when in PRI\_RUN or PRI\_IDLE mode. This indicates that the primary clock (INTOSC output) is generating a stable output. Entering another INTOSC power-managed mode at the same frequency would clear the OSTS bit.

- Note 1: Caution should be used when modifying a single IRCF bit. At a lower VDD, it is possible to select a higher clock speed than is supportable by that VDD. Improper device operation may result if the VDD/ Fosc specifications are violated.

- 2: Executing a SLEEP instruction does not necessarily place the device into Sleep mode. It acts as the trigger to place the controller into either the Sleep mode, or one of the Idle modes, depending on the setting of the IDLEN bit.

#### 4.1.4 MULTIPLE SLEEP COMMANDS

The power-managed mode that is invoked with the SLEEP instruction is determined by the setting of the IDLEN bit at the time the instruction is executed. If another SLEEP instruction is executed, the device will enter the power-managed mode specified by IDLEN at that time. If IDLEN has changed, the device will enter the new power-managed mode specified by the new setting.

#### 4.2 Run Modes

In the Run modes, clocks to both the core and peripherals are active. The difference between these modes is the clock source.

#### 4.2.1 PRI\_RUN MODE

The PRI\_RUN mode is the normal, full-power execution mode of the microcontroller. This is also the default mode upon a device Reset, unless Two-Speed Start-up is enabled. (For details, see **Section 28.4 "Two-Speed Start-up"**.) In this mode, the OSTS bit is set. The HFIOFS or MFIOFS bit may be set if the internal oscillator block is the primary clock source. (See **Section 3.2 "Control Registers"**.)

#### 4.2.2 SEC\_RUN MODE

The SEC\_RUN mode is the compatible mode to the "clock-switching" feature offered in other PIC18 devices. In this mode, the CPU and peripherals are clocked from the SOSC oscillator. This enables lower power consumption while retaining a high-accuracy clock source.

SEC\_RUN mode is entered by setting the SCS<1:0> bits to '01'. The device clock source is switched to the SOSC oscillator (see Figure 4-1), the primary oscillator is shut down, the SOSCRUN bit (OSCCON2<6>) is set and the OSTS bit is cleared.

| Note: | The SOSC oscillator can be enabled by setting the SOSCGO bit (OSCCON2<3>). If this bit is set, the clock switch to the SEC_RUN mode can switch immediately |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | once SCS<1:0> are set to '01'.                                                                                                                             |

On transitions from SEC\_RUN mode to PRI\_RUN mode, the peripherals and CPU continue to be clocked from the SOSC oscillator while the primary clock is started. When the primary clock becomes ready, a clock switch back to the primary clock occurs (see Figure 4-2). When the clock switch is complete, the SOSCRUN bit is cleared, the OSTS bit is set and the primary clock is providing the clock. The IDLEN and SCSx bits are not affected by the wake-up and the SOSC oscillator continues to run.

If the IRCFx bits and the INTSRC bit are all clear, the INTOSC output (HF-INTOSC/MF-INTOSC) is not enabled and the HFIOFS and MFIOFS bits will remain clear. There will be no indication of the current clock source. The LF-INTOSC source is providing the device clocks.

If the IRCFx bits are changed from all clear (thus, enabling the INTOSC output) or if INTSRC or MFIOSEL is set, the HFIOFS or MFIOFS bit is set after the INTOSC output becomes stable. For details, see Table 4-3.

| IRCF<2:0> | INTSRC | MFIOSEL | Status of MFIOFS or HFIOFS when INTOSC is Stable     |

|-----------|--------|---------|------------------------------------------------------|

| 000       | 0      | х       | MFIOFS = 0, HFIOFS = 0 and clock source is LF-INTOSC |

| 000       | 1      | 0       | MFIOFS = 0, HFIOFS = 1 and clock source is HF-INTOSC |

| 000       | 1      | 1       | MFIOFS = 1, HFIOFS = 0 and clock source is MF-INTOSC |

| Non-Zero  | x      | 0       | MFIOFS = 0, HFIOFS = 1 and clock source is HF-INTOSC |

| Non-Zero  | x      | 1       | MFIOFS = 1, HFIOFS = 0 and clock source is MF-INTOSC |

#### TABLE 4-3: INTERNAL OSCILLATOR FREQUENCY STABILITY BITS

Clocks to the device continue while the INTOSC source stabilizes after an interval of TIOBST (Parameter 39, Table 31-11).

If the IRCFx bits were previously at a non-zero value, or if INTSRC was set before setting SCS1 and the INTOSC source was already stable, the HFIOFS or MFIOFS bit will remain set. On transitions from RC\_RUN mode to PRI\_RUN mode, the device continues to be clocked from the INTOSC multiplexer while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 4-4). When the clock switch is complete, the HFIOFS or MFIOFS bit is cleared, the OSTS bit is set and the primary clock is providing the device clock. The IDLEN and SCSx bits are not affected by the switch. The LF-INTOSC source will continue to run if either the WDT or the Fail-Safe Clock Monitor (FSCM) is enabled.

#### 6.1.2 PROGRAM COUNTER

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide and contained in three separate 8-bit registers.

The low byte, known as the PCL register, is both readable and writable. The high byte, or PCH register, contains the PC<15:8> bits and is not directly readable or writable. Updates to the PCH register are performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCU register are performed through the PCLATU register.

The contents of PCLATH and PCLATU are transferred to the Program Counter by any operation that writes PCL. Similarly, the upper two bytes of the Program Counter are transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 6.1.5.1 "Computed** GOTO").

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the Least Significant bit (LSb) of PCL is fixed to a value of '0'. The PC increments by two to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the Program Counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the Program Counter.

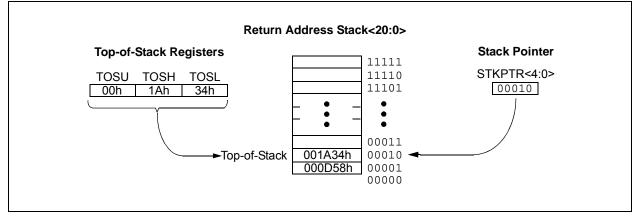

#### 6.1.3 RETURN ADDRESS STACK

The return address stack enables execution of any combination of up to 31 program calls and interrupts. The PC is pushed onto the stack when a CALL or RCALL instruction is executed or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or a RETFIE instruction. The value is also pulled off the stack on ADDULNK and SUBULNK instructions if the extended instruction set is enabled. PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions.

The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer, STKPTR. The stack space is not part of either program or data space. The Stack Pointer is readable and writable and the address on the top of the stack is readable and writable through the Top-of-Stack (TOS) Special Function Registers. Data can also be pushed to, or popped from the stack, using these registers.

A CALL type instruction causes a push onto the stack. The Stack Pointer is first incremented and the location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction following the CALL). A RETURN type instruction causes a pop from the stack. The contents of the location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The Stack Pointer is initialized to '00000' after all Resets. There is no RAM associated with the location corresponding to a Stack Pointer value of '00000'; this is only a Reset value. Status bits indicate if the stack is full, has overflowed or has underflowed.

#### 6.1.3.1 Top-of-Stack Access

Only the top of the return address stack is readable and writable. A set of three registers, TOSU:TOSH:TOSL, holds the contents of the stack location pointed to by the STKPTR register (Figure 6-3). This allows users to implement a software stack, if necessary. After a CALL, RCALL or interrupt (or ADDULNK and SUBULNK instructions, if the extended instruction set is enabled), the software can read the pushed value by reading the TOSU:TOSH:TOSL registers. These values can be placed on a user-defined software stack. At return time, the software can return these values to TOSU:TOSH:TOSL and do a return.

While accessing the stack, users must disable the Global Interrupt Enable bits to prevent inadvertent stack corruption.

#### FIGURE 6-3: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

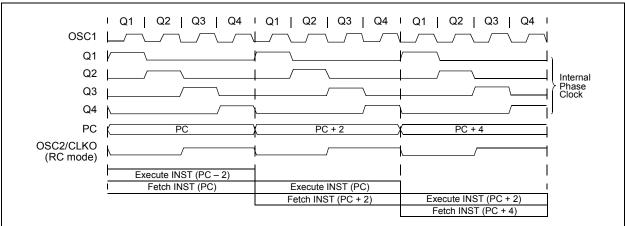

#### 6.2 PIC18 Instruction Cycle

#### 6.2.1 CLOCKING SCHEME

The microcontroller clock input, whether from an internal or external source, is internally divided by four to generate four non-overlapping quadrature clocks (Q1, Q2, Q3 and Q4). Internally, the Program Counter is incremented on every Q1, with the instruction fetched from the program memory and latched into the Instruction Register (IR) during Q4.

The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 6-4.

#### 6.2.2 INSTRUCTION FLOW/PIPELINING

An "Instruction Cycle" consists of four Q cycles, Q1 through Q4. The instruction fetch and execute are pipelined in such a manner that a fetch takes one instruction cycle, while the decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction (such as GOTO) causes the Program Counter to change, two cycles are required to complete the instruction. (See Example 6-3.)

A fetch cycle begins with the Program Counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle, Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 6-4: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 6-3: INSTRUCTION PIPELINE FLOW

| r                           | Гсү0    | TCY1      | TCY2      | TCY3      | TCY4        | TCY5          |

|-----------------------------|---------|-----------|-----------|-----------|-------------|---------------|

| 1. MOVLW 55h Fe             | etch 1  | Execute 1 |           |           | •           |               |

| 2. MOVWF PORTB              |         | Fetch 2   | Execute 2 |           | _           |               |

| 3. BRA SUB_1                |         |           | Fetch 3   | Execute 3 |             |               |

| 4. BSF PORTA, BIT3 (Force   | ed NOP) |           |           | Fetch 4   | Flush (NOP) |               |

| 5. Instruction @ address SU | JB_1    |           |           |           | Fetch SUB_1 | Execute SUB_1 |

|                             |         |           |           |           |             |               |

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

#### 6.3 Data Memory Organization

| Note: | The operation of some aspects of data    |

|-------|------------------------------------------|

|       | memory are changed when the PIC18        |

|       | extended instruction set is enabled. See |

|       | Section 6.6 "Data Memory and the         |

|       | Extended Instruction Set" for more       |

|       | information.                             |

The data memory in PIC18 devices is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4,096 bytes of data memory. The memory space is divided into 16 banks that contain 256 bytes each.

Figure 6-6 and Figure 6-7 show the data memory organization for the devices.

The data memory contains Special Function Registers (SFRs) and General Purpose Registers (GPRs). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratchpad operations in the user's application. Any read of an unimplemented location will read as '0's.

The instruction set and architecture allow operations across all banks. The entire data memory may be accessed by Direct, Indirect or Indexed Addressing modes. Addressing modes are discussed later in this section.

To ensure that commonly used registers (select SFRs and select GPRs) can be accessed in a single cycle, PIC18 devices implement an Access Bank. This is a 256-byte memory space that provides fast access to select SFRs and the lower portion of GPR Bank 0 without using the Bank Select Register. For details on the Access RAM, see **Section 6.3.2 "Access Bank"**.

#### 6.3.1 BANK SELECT REGISTER

Large areas of data memory require an efficient addressing scheme to make rapid access to any address possible. Ideally, this means that an entire address does not need to be provided for each read or write operation. For PIC18 devices, this is accomplished with a RAM banking scheme. This divides the memory space into 16 contiguous banks of 256 bytes. Depending on the instruction, each location can be addressed directly by its full 12-bit address, or an eight-bit, low-order address and a four-bit Bank Pointer.

Most instructions in the PIC18 instruction set make use of the Bank Pointer, known as the Bank Select Register (BSR). This SFR holds the four Most Significant bits of a location's address. The instruction itself includes the eight Least Significant bits. Only the four lower bits of the BSR are implemented (BSR<3:0>). The upper four bits are unused and always read as '0', and cannot be written to. The BSR can be loaded directly by using the MOVLB instruction.

The value of the BSR indicates the bank in data memory. The eight bits in the instruction show the location in the bank and can be thought of as an offset from the bank's lower boundary. The relationship between the BSR's value and the bank division in data memory is shown in Figure 6-7.

Since up to 16 registers may share the same low-order address, the user must always be careful to ensure that the proper bank is selected before performing a data read or write. For example, writing what should be program data to an eight-bit address of F9h while the BSR is 0Fh, will end up resetting the Program Counter.

While any bank can be selected, only those banks that are actually implemented can be read or written to. Writes to unimplemented banks are ignored, while reads from unimplemented banks will return '0's. Even so, the STATUS register will still be affected as if the operation was successful. The data memory map in Figure 6-6 indicates which banks are implemented.

In the core PIC18 instruction set, only the MOVFF instruction fully specifies the 12-bit address of the source and target registers. When this instruction executes, it ignores the BSR completely. All other instructions include only the low-order address as an operand and must use either the BSR or the Access Bank to locate their target registers.

| R/W-0         | R/W-0                          | R/W-0            | R/W-0            | U-0              | R/W-0            | R/W-0           | R/W-0  |

|---------------|--------------------------------|------------------|------------------|------------------|------------------|-----------------|--------|

| TMR4IE        | EEIE                           | CMP2IE           | CMP1IE           | —                | CCP5IE           | CCP4IE          | CCP3IE |

| bit 7         |                                |                  |                  |                  |                  | •<br>•          | bit 0  |

|               |                                |                  |                  |                  |                  |                 |        |

| Legend:       |                                |                  |                  |                  |                  |                 |        |

| R = Readable  | e bit                          | W = Writable     | bit              | U = Unimple      | mented bit, read | d as '0'        |        |

| -n = Value at | POR                            | '1' = Bit is set |                  | '0' = Bit is cle | eared            | x = Bit is unkr | nown   |

| L:1 7         |                                |                  | to my unt Elon b | :4               |                  |                 |        |

| bit 7         | 1 = Interrupt                  | R4 Overflow In   | terrupt Flag b   | il il            |                  |                 |        |

|               | 0 = Interrupt                  |                  |                  |                  |                  |                 |        |

| bit 6         | •                              | EDATA/Flash      | Nrite Operatio   | on Interrupt Fla | a bit            |                 |        |

|               | 1 = Interrupt                  |                  |                  |                  | 5                |                 |        |

|               | 0 = Interrupt                  | is disabled      |                  |                  |                  |                 |        |

| bit 5         | CMP2IE: CM                     | P2 Interrupt Fl  | ag bit           |                  |                  |                 |        |

|               | 1 = Interrupt                  |                  |                  |                  |                  |                 |        |

|               | 0 = Interrupt                  |                  |                  |                  |                  |                 |        |

| bit 4         |                                | P1 Interrupt Fl  | ag bit           |                  |                  |                 |        |

|               | 1 = Interrupt<br>0 = Interrupt |                  |                  |                  |                  |                 |        |

| bit 3         | •                              | ted: Read as '   | 0'               |                  |                  |                 |        |

| bit 2         | -                              | P5 Interrupt Fla |                  |                  |                  |                 |        |

|               | 1 = Interrupt                  | •                | 3                |                  |                  |                 |        |

|               | 0 = Interrupt                  |                  |                  |                  |                  |                 |        |

| bit 1         | CCP4IE: CCI                    | P4 Interrupt Fla | ag bit           |                  |                  |                 |        |

|               | 1 = Interrupt                  |                  |                  |                  |                  |                 |        |

|               | 0 = Interrupt                  |                  |                  |                  |                  |                 |        |

| bit 0         |                                | P3 Interrupt Fla | ag bits          |                  |                  |                 |        |

|               | 1 = Interrupt                  |                  |                  |                  |                  |                 |        |

|               | 0 = Interrupt                  |                  |                  |                  |                  |                 |        |

#### REGISTER 10-12: PIE4: PERIPHERAL INTERRUPT ENABLE REGISTER 4

#### **10.9 Context Saving During Interrupts**

During interrupts, the return PC address is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the Fast Return Stack. If a fast return from interrupt is not used (see **Section 6.3 "Data Memory Organization"**), the user may need to save the WREG, STATUS and BSR registers on entry to the Interrupt Service Routine (ISR). Depending on the user's application, other registers also may need to be saved.

Example 10-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

#### EXAMPLE 10-1: SAVING STATUS, WREG AND BSR REGISTERS IN RAM

| MOVWF<br>MOVFF<br>;<br>; USER<br>; | W_TEMP<br>STATUS, STATUS_TEMP<br>BSR, BSR_TEMP<br>ISR CODE | ; W_TEMP is in virtual bank<br>; STATUS_TEMP located anywhere<br>; BSR_TMEP located anywhere |

|------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| MOVFF                              | BSR_TEMP, BSR                                              | ; Restore BSR                                                                                |

| MOVF                               | W_TEMP, W                                                  | ; Restore WREG                                                                               |

| MOVFF                              | STATUS_TEMP, STATUS                                        | ; Restore STATUS                                                                             |

#### TABLE 10-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name    | Bit 7    | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0   |

|---------|----------|-----------|---------|---------|---------|---------|--------|---------|

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF  | INT0IF | RBIF    |

| INTCON2 | RBPU     | INTEDG0   | INTEDG1 | INTEDG2 | INTEDG3 | TMR0IP  | INT3IP | RBIP    |

| INTCON3 | INT2IP   | INT1IP    | INT3IE  | INT2IE  | INT1IE  | INT3IF  | INT2IF | INT1IF  |

| PIR1    | PSPIP    | ADIF      | RC1IF   | TX1IF   | SSPIF   | TMR1GIF | TMR2IF | TMR1IF  |

| PIR2    | OSCFIF   | —         | _       | _       | BCLIF   | HLVDIF  | TMR3IF | TMR3GIF |

| PIR3    | —        | —         | RC2IF   | TX2IF   | CTMUIF  | CCP2IF  | CCP1IF | —       |

| PIR4    | TMR4IF   | EEIF      | CMP2IF  | CMP1IF  | —       | CCP5IF  | CCP4IF | CCP3IF  |

| PIR5    | IRXIF    | WAKIF     | ERRIF   | TXB2IF  | TXB1IF  | TXB0IF  | RXB1IF | RXB0IF  |

| PIE1    | PSPIE    | ADIE      | RC1IE   | TX1IE   | SSPIE   | TMR1GIE | TMR2IE | TMR1IE  |

| PIE2    | OSCFIE   | —         | _       | _       | BCLIE   | HLVDIE  | TMR3IE | TMR3GIE |

| PIE3    | —        | —         | RC2IE   | TX2IE   | CTMUIE  | CCP2IE  | CCP1IE |         |

| PIE4    | TMR4IE   | EEIE      | CCP2IE  | CMP1IE  | —       | CCP5IE  | CCP4IE | CCP3IE  |

| PIE5    | IRXIE    | WAKIE     | ERRIE   | TXB2IE  | TXB1IE  | TXB0IE  | RXB1IE | RXB0IE  |

| IPR1    | PSPIP    | ADIP      | RC1IP   | TX1IP   | SSPIP   | TMR1GIP | TMR2IP | TMR1IP  |

| IPR2    | OSCFIP   | _         | _       | _       | BCLIP   | HLVDIP  | TMR3IP | TMR3GIP |

| IPR3    | _        | _         | RC2IP   | TX2IP   | CTMUIP  | CCP2IP  | CCP1IP |         |

| IPR4    | TMR4IP   | EEIP      | CMP2IP  | CMP1IP  | —       | CCP5IP  | CCP4IP | CCP3IP  |

| IPR5    | IRXIP    | WAKIP     | ERRIP   | TXB2IP  | TXB1IP  | TXB0IP  | RXB1IP | RXB0IP  |

| RCON    | IPEN     | SBOREN    | CM      | RI      | TO      | PD      | POR    | BOR     |

Legend: Shaded cells are not used by the interrupts.

| Pin Name    | Function               | TRIS<br>Setting | I/O | I/O Type | Description                                                                            |  |  |

|-------------|------------------------|-----------------|-----|----------|----------------------------------------------------------------------------------------|--|--|

| RE5/CANTX   | RE5 <sup>(1)</sup>     | 0               | 0   | DIG      | LATE<5> data output.                                                                   |  |  |

|             |                        | 1               | Ι   | ST       | PORTE<5> data input.                                                                   |  |  |

|             | CANTX <sup>(1,2)</sup> | 0               | 0   | DIG      | CAN bus TX.                                                                            |  |  |

| RE6/RX2/DT2 | RE6 <sup>(1)</sup>     | 0               | 0   | DIG      | LATE<6> data output.                                                                   |  |  |

|             |                        | 1               | Ι   | ST       | PORTE<6> data input.                                                                   |  |  |

|             | RX2 <sup>(1)</sup>     | 1               | Ι   | ST       | Asynchronous serial receive data input (EUSARTx module).                               |  |  |

|             | DT2 <sup>(1)</sup>     | 1               | 0   | DIG      | DIG Synchronous serial data output (EUSARTx module); takes priority port data.         |  |  |

|             |                        | 1               | I   | ST       | Synchronous serial data input (EUSARTx module); user must configure as an input.       |  |  |

| RE7/TX2/CK2 | RE7 <sup>(1)</sup>     | 0               | 0   | DIG      | LATE<7> data output.                                                                   |  |  |

|             |                        | 1               | Ι   | ST       | PORTE<7> data input.                                                                   |  |  |

|             | TX2 <sup>(1)</sup>     | 0               | 0   |          |                                                                                        |  |  |

|             | CK2 <sup>(1)</sup>     | 0               | 0   | DIG      | Synchronous serial clock output (EUSARTx module); user must configure as an input.     |  |  |

|             |                        | 1               | Ι   | ST       | Synchronous serial clock input (EUSARTx module); user must config-<br>ure as an input. |  |  |

#### TABLE 11-9: PORTE FUNCTIONS (CONTINUED)

Legend: O = Output, I = Input, ANA = Analog Signal, DIG = CMOS Output, ST = Schmitt Trigger Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option)

Note 1: These bits are unavailable for 40 and 44-pin devices (PIC18F4XK0).

2: This is the alternate pin assignment for CANRX and CANTX on 64-pin devices (PIC18F6XK80) when the CANMX Configuration bit is cleared.

| Name    | Bit 7              | Bit 6              | Bit 5               | Bit 4               | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|---------|--------------------|--------------------|---------------------|---------------------|--------|--------|--------|--------|

| PORTE   | RE7 <sup>(1)</sup> | RE6 <sup>(1)</sup> | RE5 <sup>(1)</sup>  | RE4 <sup>(1)</sup>  | RE3    | RE2    | RE1    | RE0    |

| LATE    | LATE7              | LATE6              | LATE5               | LATE4               | —      | LATE2  | LATE1  | LATE0  |

| TRISE   | TRISE7             | TRISE6             | TRISE5              | TRISE4              | —      | TRISE2 | TRISE1 | TRISE0 |

| PADCFG1 | RDPU               | REPU               | RFPU <sup>(1)</sup> | RGPU <sup>(1)</sup> | _      |        | _      | CTMUDS |

| ANCON0  | ANSEL7             | ANSEL6             | ANSEL5              | ANSEL4              | ANSEL3 | ANSEL2 | ANSEL1 | ANSEL0 |

Legend: Shaded cells are not used by PORTE.

Note 1: These bits are unimplemented on 44-pin devices, read as '0'.

### 16.0 TIMER3 MODULE

The Timer3 timer/counter modules incorporate these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable eight-bit registers (TMR3H and TMR3L)

- Selectable clock source (internal or external) with device clock or SOSC oscillator internal options

- Interrupt-on-overflow

Γ.

Module Reset on ECCP Special Event Trigger

A simplified block diagram of the Timer3 module is shown in Figure 16-1.

The Timer3 module is controlled through the T3CON register (Register 16-1). It also selects the clock source options for the ECCP modules. (For more information, see Section 20.1.1 "ECCP Module and Timer Resources".)

The Fosc clock source should not be used with the ECCP capture/compare features. If the timer will be used with the capture or compare features, always select one of the other timer clocking options.

#### REGISTER 16-1: T3CON: TIMER3 CONTROL REGISTER

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0 | R/W-0  |

|---------|---------|---------|---------|--------|--------|-------|--------|

| TMR3CS1 | TMR3CS0 | T3CKPS1 | T3CKPS0 | SOSCEN | T3SYNC | RD16  | TMR3ON |

| bit 7   |         |         |         |        |        |       | bit 0  |

| Legend:    |            |                                                                   |                                                                |                                |

|------------|------------|-------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------|

| R = Reada  | able bit   | W = Writable bit                                                  | U = Unimplemented bit,                                         | , read as '0'                  |

| -n = Value | at POR     | '1' = Bit is set                                                  | '0' = Bit is cleared                                           | x = Bit is unknown             |

| bit 7-6    |            | <1:0>: Timer3 Clock Source                                        |                                                                |                                |

|            |            |                                                                   | n pin or oscillator, depending o                               | on the SOSCEN bit:             |

|            | SOSCEN     |                                                                   |                                                                |                                |

|            |            | lock is from T3CKI pin (on th                                     | ne rising edge).                                               |                                |

|            | SOSCEN     |                                                                   | unation bit the cleak accuracies                               |                                |

|            |            | DSCO or an internal digital cl                                    | Iration bit, the clock source is e                             | either a crystal oscillator on |

|            |            | erx clock source is system clo                                    |                                                                |                                |

|            |            | rx clock source is instruction                                    |                                                                |                                |

| bit 5-4    | T3CKPS<    | :1:0>: Timer3 Input Clock Pre                                     | escale Select bits                                             |                                |

|            | 11 = 1:8 F | Prescale value                                                    |                                                                |                                |

|            |            | Prescale value                                                    |                                                                |                                |

|            |            | Prescale value                                                    |                                                                |                                |

|            |            | Prescale value                                                    |                                                                |                                |

| bit 3      |            | SOSC Oscillator Enable bit                                        |                                                                |                                |

|            |            | c is enabled and available for<br>c is disabled and available for |                                                                |                                |

| bit 2      |            | Timer3 External Clock Input<br>le if the device clock comes f     |                                                                |                                |

|            |            | R3CS<1:0> = 10:                                                   | ,                                                              |                                |

|            | 1 = Does   | not synchronize external cloo                                     | ck input                                                       |                                |

|            | 0 = Synch  | ronizes external clock input                                      |                                                                |                                |

|            |            | R3CS<1:0> = 0x:                                                   |                                                                |                                |

|            |            | ignored; Timer3 uses the inte                                     |                                                                |                                |

| bit 1      |            | Bit Read/Write Mode Enable                                        |                                                                |                                |

|            |            | es register read/write of Time<br>es register read/write of Time  | er3 in one 16-bit operation<br>er3 in two eight-bit operations |                                |

| bit 0      | TMR3ON:    | : Timer3 On bit                                                   |                                                                |                                |

|            | 1 = Enable |                                                                   |                                                                |                                |

|            | 0 = Stops  | Timer3                                                            |                                                                |                                |

Note 1: The Fosc clock source should not be selected if the timer will be used with the ECCP capture/compare features.

|              | DAMA                 | DAMA              | D/M/ O           | DAALO           | DAMO             | DAMO     |       |

|--------------|----------------------|-------------------|------------------|-----------------|------------------|----------|-------|

| R/W-0        | R/W-0                | R/W-0             | R/W-0            | R/W-0           | R/W-0            | R/W-0    | R/W-0 |

| ITRIM5       | ITRIM4               | ITRIM3            | ITRIM2           | ITRIM1          | ITRIM0           | IRNG1    | IRNG0 |

| bit 7        |                      |                   |                  |                 |                  |          | bit 0 |

| Legend:      |                      |                   |                  |                 |                  |          |       |

| R = Readab   | le bit               | W = Writable      | bit              | U = Unimpler    | nented bit, read | d as '0' |       |

| -n = Value a | It POR               | '1' = Bit is set  | '0' = Bit is cle |                 | x = Bit is unkr  | nown     |       |

|              |                      |                   |                  |                 |                  |          |       |

| bit 7-2      | ITRIM<5:0>:          | Current Source    | e Trim bits      |                 |                  |          |       |

|              | 011111 <b>= Ma</b>   | aximum positive   | e change (+62    | % typ.) from no | minal current    |          |       |

|              | 011110               |                   |                  |                 |                  |          |       |

|              | •                    |                   |                  |                 |                  |          |       |

|              | •                    |                   |                  |                 |                  |          |       |

|              | 000001 = Mii         | nimum positive    | change (+2%      | typ.) from nom  | inal current     |          |       |

|              |                      |                   | 0 (              | d by IRNG<1:0>  |                  |          |       |

|              | 111111 <b>= Mi</b>   | nimum negativ     | e change (-2%    | typ.) from nom  | inal current     |          |       |

|              | •                    |                   |                  |                 |                  |          |       |

|              | •                    |                   |                  |                 |                  |          |       |

|              | 100010               |                   |                  |                 |                  |          |       |

|              |                      | aximum negativ    | e change (-62    | % typ.) from no | minal current    |          |       |

| bit 1-0      |                      | Current Source    | <b>.</b> .       |                 |                  |          |       |

|              | 11 = 100 x Ba        |                   |                  | <b>-</b>        |                  |          |       |

|              | 10 = 10 x Bas        |                   |                  |                 |                  |          |       |

|              | 01 <b>= Base C</b> ι | urrent level (0.5 | 55 μA nominal)   | )               |                  |          |       |

|              | 0.0 - 0.0000         | a aumaa ia dia ah | مامط             |                 |                  |          |       |

#### REGISTER 18-3: CTMUICON: CTMU CURRENT CONTROL REGISTER

00 =Current source is disabled

|       |                       |            |                             |                       | SYNC       | = 0, BRGH                   | <b>i =</b> 0, BRG     | 16 = 1     |                             |                       |            |                             |

|-------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD  | Fosc                  | = 64.000   | MHz                         | Fosc = 40.000 MHz     |            |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             |

| (K)   | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3   | 0.300                 | 0.00       | 13332                       | 0.300                 | 0.00       | 8332                        | 0.300                 | 0.02       | 4165                        | 0.300                 | 0.02       | 2082                        |

| 1.2   | 1.200                 | 0.00       | 3332                        | 1.200                 | 0.02       | 2082                        | 1.200                 | -0.03      | 1041                        | 1.200                 | -0.03      | 520                         |

| 2.4   | 2.400                 | 0.00       | 1666                        | 2.402                 | 0.06       | 1040                        | 2.399                 | -0.03      | 520                         | 2.404                 | 0.16       | 259                         |

| 9.6   | 9.592                 | -0.08      | 416                         | 9.615                 | 0.16       | 259                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16       | 64                          |

| 19.2  | 19.417                | 1.13       | 207                         | 19.231                | 0.16       | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73       | 31                          |

| 57.6  | 59.701                | 3.65       | 68                          | 58.140                | 0.94       | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36      | 10                          |

| 115.2 | 121.212               | 5.22       | 34                          | 113.636               | -1.36      | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51       | 4                           |

#### TABLE 22-4: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|              |                       |            |                             |                       | SYNC       | = 0, BRGH                   | I = 0, BRG            | <b>616 =</b> 1 |                             |                       |            |                             |

|--------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|----------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fos                   | c = 8.000  | MHz                         | Fosc = 4.000 MHz      |            |                             | Fosc = 2.000 MHz      |                |                             | Fosc = 1.000 MHz      |            |                             |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | 0.300                 | -0.04      | 1665                        | 0.300                 | 0.04       | 832                         | 0.300                 | -0.16          | 415                         | 0.300                 | -0.16      | 207                         |

| 1.2          | 1.201                 | -0.16      | 415                         | 1.202                 | 0.16       | 207                         | 1.201                 | -0.16          | 103                         | 1.201                 | -0.16      | 51                          |

| 2.4          | 2.403                 | -0.16      | 207                         | 2.404                 | 0.16       | 103                         | 2.403                 | -0.16          | 51                          | 2.403                 | -0.16      | 25                          |

| 9.6          | 9.615                 | -0.16      | 51                          | 9.615                 | 0.16       | 25                          | 9.615                 | -0.16          | 12                          | _                     | _          | _                           |

| 19.2         | 19.230                | -0.16      | 25                          | 19.231                | 0.16       | 12                          | —                     | _              | _                           | —                     | _          | _                           |

| 57.6         | 55.555                | 3.55       | 8                           | 62.500                | 8.51       | 3                           | —                     | _              | _                           | —                     | _          | _                           |

| 115.2        | —                     | —          | _                           | 125.000               | 8.51       | 1                           | _                     | —              |                             | _                     | —          | _                           |

|              |                       |            |                             | SYNC = 0              | , BRGH =   | = 1, BRG16                  | = 1 or SY             | NC = 1,    | BRG16 = 1                   |                       |            |                             |

|--------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Foso                  | = 64.000   | MHz                         | Fosc = 40.000 MHz     |            |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | 0.300                 | 0.00       | 53332                       | 0.300                 | 0.00       | 33332                       | 0.300                 | 0.00       | 16665                       | 0.300                 | 0.00       | 8332                        |

| 1.2          | 1.200                 | 0.00       | 13332                       | 1.200                 | 0.00       | 8332                        | 1.200                 | 0.02       | 4165                        | 1.200                 | 0.02       | 2082                        |

| 2.4          | 2.400                 | 0.00       | 6666                        | 2.400                 | 0.02       | 4165                        | 2.400                 | 0.02       | 2082                        | 2.402                 | 0.06       | 1040                        |

| 9.6          | 9.598                 | -0.02      | 1666                        | 9.606                 | 0.06       | 1040                        | 9.596                 | -0.03      | 520                         | 9.615                 | 0.16       | 259                         |

| 19.2         | 19.208                | 0.04       | 832                         | 19.193                | -0.03      | 520                         | 19.231                | 0.16       | 259                         | 19.231                | 0.16       | 129                         |

| 57.6         | 57.348                | -0.44      | 278                         | 57.803                | 0.35       | 172                         | 57.471                | -0.22      | 86                          | 58.140                | 0.94       | 42                          |

| 115.2        | 115.108               | -0.08      | 138                         | 114.943               | -0.22      | 86                          | 116.279               | 0.94       | 42                          | 113.636               | -1.36      | 21                          |

|       |                       |            |                             | SYNC = 0              | , BRGH :   | = 1, BRG16                  | = 1 or SY             | 'NC = 1,   | BRG16 = 1                   |                       |            |                             |

|-------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD  | Fost                  | c = 8.000  | MHz                         | Fosc = 4.000 MHz      |            |                             | Fosc = 2.000 MHz      |            |                             | Fosc = 1.000 MHz      |            |                             |

| (K)   | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3   | 0.300                 | -0.01      | 6665                        | 0.300                 | 0.01       | 3332                        | 0.300                 | -0.04      | 1665                        | 0.300                 | -0.04      | 832                         |

| 1.2   | 1.200                 | -0.04      | 1665                        | 1.200                 | 0.04       | 832                         | 1.201                 | -0.16      | 415                         | 1.201                 | -0.16      | 207                         |

| 2.4   | 2.400                 | -0.04      | 832                         | 2.404                 | 0.16       | 415                         | 2.403                 | -0.16      | 207                         | 2.403                 | -0.16      | 103                         |

| 9.6   | 9.615                 | -0.16      | 207                         | 9.615                 | 0.16       | 103                         | 9.615                 | -0.16      | 51                          | 9.615                 | -0.16      | 25                          |

| 19.2  | 19.230                | -0.16      | 103                         | 19.231                | 0.16       | 51                          | 19.230                | -0.16      | 25                          | 19.230                | -0.16      | 12                          |

| 57.6  | 57.142                | 0.79       | 34                          | 58.824                | 2.12       | 16                          | 55.555                | 3.55       | 8                           | —                     | _          | _                           |

| 115.2 | 117.647               | -2.12      | 16                          | 111.111               | -3.55      | 8                           | —                     | _          | —                           | —                     | _          | —                           |

| Name   | Bit 7                 | Bit 6                 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0  |

|--------|-----------------------|-----------------------|---------|---------|---------|---------|---------|--------|

| INTCON | GIE/GIEH              | PEIE/GIEL             | TMR0IE  | INT0IE  | RBIE    | TMR0IF  | INT0IF  | RBIF   |

| PIR1   | PSPIF                 | ADIF                  | RC1IF   | TX1IF   | SSPIF   | TMR1GIF | TMR2IF  | TMR1IF |

| PIE1   | PSPIE                 | ADIE                  | RC1IE   | TX1IE   | SSPIE   | TMR1GIE | TMR2IE  | TMR1IE |

| IPR1   | PSPIP                 | ADIP                  | RC1IP   | TX1IP   | SSPIP   | TMR1GIP | TMR2IP  | TMR1IP |

| ADRESH | A/D Result            | Register High         | n Byte  |         |         |         |         |        |

| ADRESL | A/D Result            | Register Low          | Byte    |         |         |         |         |        |

| ADCON0 | —                     | CHS4                  | CHS3    | CHS2    | CHS1    | CHS0    | GO/DONE | ADON   |

| ADCON1 | TRIGSEL1              | TRIGSEL0              | VCFG1   | VCFG0   | VNCFG   | CHSN2   | CHSN1   | CHSN0  |

| ADCON2 | ADFM                  |                       | ACQT2   | ACQT1   | ACQT0   | ADCS2   | ADCS1   | ADCS0  |

| ANCON0 | ANSEL7                | ANSEL6                | ANSEL5  | ANSEL4  | ANSEL3  | ANSEL2  | ANSEL1  | ANSEL0 |

| ANCON1 | —                     | ANSEL14               | ANSEL13 | ANSEL12 | ANSEL11 | ANSEL10 | ANSEL9  | ANSEL8 |

| PORTA  | RA7 <sup>(1)</sup>    | RA6 <sup>(1)</sup>    | RA5     | _       | RA3     | RA2     | RA1     | RA0    |

| TRISA  | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | TRISA5  | _       | TRISA3  | TRISA2  | TRISA1  | TRISA0 |

| PORTB  | RB7                   | RB6                   | RB5     | RB4     | RB3     | RB2     | RB1     | RB0    |

| TRISB  | TRISB7                | TRISB6                | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0 |

| PORTE  | RE7                   | RE6                   | RE5     | RE4     | RE3     | _       | RE1     | RE0    |

| TRISE  | TRISE7                | TRISE6                | TRISE5  | TRISE4  | _       | TRISE2  | TRISE1  | TRISE0 |

| PMD1   | PSPMD                 | CTMUMD                | ADCMD   | TMR4MD  | TMR3MD  | TMR2MD  | TMR1MD  | TMR0MD |

| TABLE 23-2: | <b>REGISTERS ASSOCIATED WITH THE A/D MODULE</b> |

|-------------|-------------------------------------------------|

|-------------|-------------------------------------------------|

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

**Note 1:** These bits are available only in certain oscillator modes when the FOSC2 Configuration bit = 0. If that Configuration bit is cleared, this signal is not implemented.

### REGISTER 27-24:BnSIDH: TX/RX BUFFER 'n' STANDARD IDENTIFIER REGISTERS,<br/>HIGH BYTE IN RECEIVE MODE $[0 \le n \le 5, TXnEN (BSEL0<n>) = 0]^{(1)}$

| R-x                     | R-x  | R-x          | R-x  | R-x          | R-x              | R-x    | R-x   |

|-------------------------|------|--------------|------|--------------|------------------|--------|-------|

| SID10                   | SID9 | SID8         | SID7 | SID6         | SID5             | SID4   | SID3  |

| bit 7                   | ·    |              |      | · · ·        |                  |        | bit 0 |

|                         |      |              |      |              |                  |        |       |

|                         |      |              |      |              |                  |        |       |

| Legend:                 |      |              |      |              |                  |        |       |

| Legend:<br>R = Readable | bit  | W = Writable | bit  | U = Unimplen | nented bit, read | as '0' |       |

bit 7-0 **SID<10:3>:** Standard Identifier bits (if EXIDE (BnSIDL<3>) = 0) Extended Identifier bits, EID<28:21> (if EXIDE = 1).

Note 1: These registers are available in Mode 1 and 2 only.

####

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID10 | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 7 | •     |       |       | •     |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 **SID<10:3>:** Standard Identifier bits (if EXIDE (BnSIDL<3>) = 0) Extended Identifier bits, EID<28:21> (if EXIDE = 1).

Note 1: These registers are available in Mode 1 and 2 only.

## REGISTER 27-35: BnDLC: TX/RX BUFFER 'n' DATA LENGTH CODE REGISTERS IN TRANSMIT MODE $[0 \le n \le 5, TXnEN (BSEL<n>) = 1]^{(1)}$

| U-0        | R/W-x                                                        | U-0              | U-0           | R/W-x            | R/W-x            | R/W-x          | R/W-x |  |

|------------|--------------------------------------------------------------|------------------|---------------|------------------|------------------|----------------|-------|--|

| _          | TXRTR                                                        | —                | _             | DLC3             | DLC2             | DLC1           | DLC0  |  |

| bit 7      |                                                              |                  |               |                  | •                |                | bit 0 |  |

|            |                                                              |                  |               |                  |                  |                |       |  |

| Legend:    |                                                              |                  |               |                  |                  |                |       |  |

| R = Reada  | ble bit                                                      | W = Writable k   | oit           | U = Unimplei     | mented bit, read | l as '0'       |       |  |

| -n = Value | at POR                                                       | '1' = Bit is set |               | '0' = Bit is cle | ared             | x = Bit is unk | nown  |  |

|            |                                                              |                  |               |                  |                  |                |       |  |

| bit 7      | Unimplemen                                                   | ted: Read as '0  | )'            |                  |                  |                |       |  |

| bit 6      | TXRTR: Tran                                                  | smitter Remote   | Transmission  | n Request bit    |                  |                |       |  |

|            | 1 = Transmitted message will have the RTR bit set            |                  |               |                  |                  |                |       |  |

|            | 0 = Transmitt                                                | ed message wil   | I have the RT | R bit cleared    |                  |                |       |  |

| bit 5-4    | Unimplemen                                                   | ted: Read as '0  | )'            |                  |                  |                |       |  |

| bit 3-0    | <b>DLC&lt;3:0&gt;:</b> D                                     | ata Length Cod   | le bits       |                  |                  |                |       |  |

|            | 1111-1001 =                                                  | Reserved         |               |                  |                  |                |       |  |

|            |                                                              | length = 8 bytes |               |                  |                  |                |       |  |

|            |                                                              | length = 7 bytes |               |                  |                  |                |       |  |

|            | 0110 = Data length = 6 bytes                                 |                  |               |                  |                  |                |       |  |

|            | 0101 = Data length = 5 bytes<br>0100 = Data length = 4 bytes |                  |               |                  |                  |                |       |  |

|            | 0011 = Data length = 3  bytes                                |                  |               |                  |                  |                |       |  |

|            | 0010 = Data length = 2  bytes                                |                  |               |                  |                  |                |       |  |

|            | 0001 = Data length = 1 byte                                  |                  |               |                  |                  |                |       |  |

|            | 0000 = Data length = 0 bytes                                 |                  |               |                  |                  |                |       |  |

|            |                                                              |                  |               |                  |                  |                |       |  |

**Note 1:** These registers are available in Mode 1 and 2 only.

### REGISTER 27-36: BSEL0: BUFFER SELECT REGISTER 0<sup>(1)</sup>

| R/W-0  | R/W-0  | R/W-0         | R/W-0  | R/W-0  | R/W-0         | U-0 | U-0   |

|--------|--------|---------------|--------|--------|---------------|-----|-------|

| B5TXEN | B4TXEN | <b>B3TXEN</b> | B2TXEN | B1TXEN | <b>B0TXEN</b> | —   | —     |

| bit 7  |        |               |        | •      |               |     | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-2 **B<5:0>TXEN:** Buffer 5 to Buffer 0 Transmit Enable bits 1 = Buffer is configured in Transmit mode 0 = Buffer is configured in Receive mode

bit 1-0 Unimplemented: Read as '0'

**Note 1:** These registers are available in Mode 1 and 2 only.

## REGISTER 27-42: RXMnSIDL: RECEIVE ACCEPTANCE MASK 'n' STANDARD IDENTIFIER MASK REGISTERS, LOW BYTE [0 $\leq$ n $\leq$ 1]

| R/W-x | R/W-x | R/W-x | U-0 | R/W-0                 | U-0 | R/W-x | R/W-x |

|-------|-------|-------|-----|-----------------------|-----|-------|-------|

| SID2  | SID1  | SID0  | _   | EXIDEN <sup>(1)</sup> |     | EID17 | EID16 |

| bit 7 |       |       |     |                       |     |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 SID<2:0>: Standard Identifier Mask bits or Extended Identifier Mask bits (EID<2 | :0:18>) |

|-----------------------------------------------------------------------------------------|---------|

|-----------------------------------------------------------------------------------------|---------|

| bit 4   | Unimplemented: Read as '0'                                                                                                                                            |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | Mode 0:<br>Unimplemented: Read as '0'                                                                                                                                 |

|         | Mode 1, 2:<br>EXIDEN: Extended Identifier Filter Enable Mask bit <sup>(1)</sup>                                                                                       |

|         | <ul> <li>1 = Messages selected by the EXIDEN bit in RXFnSIDL will be accepted</li> <li>0 = Both standard and extended identifier messages will be accepted</li> </ul> |

| bit 2   | Unimplemented: Read as '0'                                                                                                                                            |

| bit 1-0 | EID<17:16>: Extended Identifier Mask bits                                                                                                                             |

Note 1: This bit is available in Mode 1 and 2 only.

### REGISTER 27-43: RXMnEIDH: RECEIVE ACCEPTANCE MASK 'n' EXTENDED IDENTIFIER MASK REGISTERS, HIGH BYTE [0 $\le$ n $\le$ 1]

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID15 | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-0 EID<15:8>: Extended Identifier Mask bits

## REGISTER 27-44: RXMnEIDL: RECEIVE ACCEPTANCE MASK 'n' EXTENDED IDENTIFIER MASK REGISTERS, LOW BYTE [0 $\leq$ n $\leq$ 1]

| R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|-------------|-------|-------|-------|-------|-------|-------|-------|

| EID7        | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 bit 0 |       |       |       |       |       |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-0 EID<7:0>: Extended Identifier Mask bits

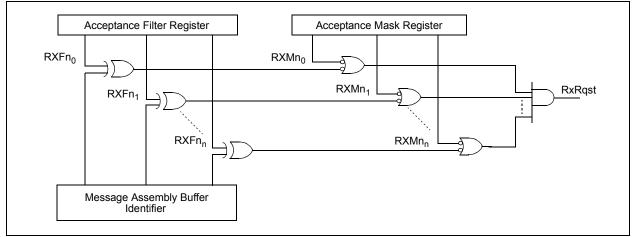

In Mode 1 and 2, there are an additional 10 acceptance filters, RXF6-RXF15, creating a total of 16 available filters. RXF15 can be used either as an acceptance filter or acceptance mask register. Each of these acceptance filters can be individually enabled or disabled by setting or clearing the RXFENn bit in the RXFCONn register. Any of these 16 acceptance filters can be dynamically associated with any of the receive buffers. Actual association is made by setting the appropriate bits in the RXFBCONn register. Each RXFBCONn register contains a nibble for each filter. This nibble can be used to associate a specific filter to any of available receive buffers. User firmware may associate more than one filter to any one specific receive buffer.

In addition to dynamic filter to buffer association, in Mode 1 and 2, each filter can also be dynamically associated to available Acceptance Mask registers. The FILn\_m bits in the MSELn register can be used to link a specific acceptance filter to an acceptance mask register. As with filter to buffer association, one can also associate more than one mask to a specific acceptance filter.

When a filter matches and a message is loaded into the receive buffer, the filter number that enabled the message reception is loaded into the FILHIT bit(s). In Mode 0 for RXB1, the RXB1CON register contains the FILHIT<2:0> bits. They are coded as follows:

- 101 = Acceptance Filter 5 (RXF5)

- 100 = Acceptance Filter 4 (RXF4)

- 011 = Acceptance Filter 3 (RXF3)

- 010 = Acceptance Filter 2 (RXF2)

- 001 = Acceptance Filter 1 (RXF1)

- 000 = Acceptance Filter 0 (RXF0)

Note: '000' and '001' can only occur if the RXB0DBEN bit is set in the RXB0CON register, allowing RXB0 messages to rollover into RXB1. The coding of the RXB0DBEN bit enables these three bits to be used similarly to the FILHIT bits and to distinguish a hit on filter, RXF0 and RXF1, in either RXB0 or after a rollover into RXB1.

- 111 = Acceptance Filter 1 (RXF1)

- 110 = Acceptance Filter 0 (RXF0)

- 001 = Acceptance Filter 1 (RXF1)

- 000 = Acceptance Filter 0 (RXF0)

If the RXB0DBEN bit is clear, there are six codes corresponding to the six filters. If the RXB0DBEN bit is set, there are six codes corresponding to the six filters, plus two additional codes corresponding to RXF0 and RXF1 filters, that rollover into RXB1.

In Mode 1 and 2, each buffer control register contains 5 bits of filter hit bits (FILHIT<4:0>). A binary value of '0' indicates a hit from RXF0 and 15 indicates RXF15.

If more than one acceptance filter matches, the FILHIT bits will encode the binary value of the lowest numbered filter that matched. In other words, if filter RXF2 and filter RXF4 match, FILHIT will be loaded with the value for RXF2. This essentially prioritizes the acceptance filters with a lower number filter having higher priority. Messages are compared to filters in ascending order of filter number.

The mask and filter registers can only be modified when the PIC18F66K80 family devices are in Configuration mode.

#### FIGURE 27-3: MESSAGE ACCEPTANCE MASK AND FILTER OPERATION

© 2010-2012 Microchip Technology Inc.

ADD W to f

$\mathsf{ADDWF} \quad \ \ f\left\{,d\left\{,a\right\}\right\}$

#### 29.1.1 STANDARD INSTRUCTION SET

| ADDLW                                                       | ADD Litera                        | al to W        | ADDWF                          |               |                                                 |

|-------------------------------------------------------------|-----------------------------------|----------------|--------------------------------|---------------|-------------------------------------------------|

| Syntax:                                                     | ADDLW                             | k              | Syntax:                        |               |                                                 |

| Operands:                                                   | $0 \le k \le 255$                 | 5              | Operands:                      |               |                                                 |

| Operation:                                                  | (W) + k $\rightarrow$             | W              |                                |               |                                                 |

| Status Affected:                                            | N, OV, C, [                       | DC, Z          | Operation:                     |               |                                                 |

| Encoding:                                                   | 0000                              | 1111           | Operation:<br>Status Affected: |               |                                                 |

| Description:                                                | The conter<br>8-bit literal<br>W. |                | Encoding                       |               |                                                 |

| Words:                                                      | 1                                 |                |                                |               |                                                 |

| Cycles:                                                     | 1                                 |                |                                |               |                                                 |

| Q Cycle Activity:                                           |                                   |                |                                |               |                                                 |

| Q1                                                          | Q2                                | Q3             |                                | Q4            | 1                                               |

| Decode                                                      | Read<br>literal 'k'               | Proces<br>Data | is N                           | Write to<br>W |                                                 |

| Example:<br>Before Instruc<br>W =<br>After Instructi<br>W = | ction<br>10h                      | 15h            |                                |               |                                                 |

|                                                             |                                   |                |                                |               | Words:                                          |

|                                                             |                                   |                |                                |               | Cycles:                                         |

|                                                             |                                   |                |                                |               | Q Cycle Activity:<br>Q1                         |

|                                                             |                                   |                |                                |               | Decode                                          |