Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | ECANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.6K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 8x12b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f26k80-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

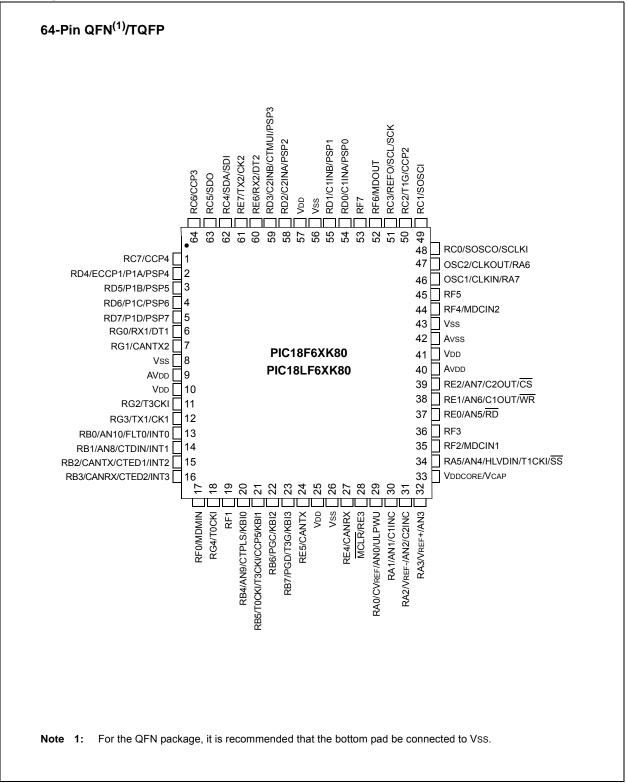

## **Pin Diagrams (Continued)**

|                            | Pin N | umber                   |             |                |                                                 |

|----------------------------|-------|-------------------------|-------------|----------------|-------------------------------------------------|

| Pin Name                   | QFN   | SSOP/<br>SPDIP<br>/SOIC | Pin<br>Type | Buffer<br>Type | Description                                     |

| RC7/CANRX/RX1/DT1/<br>CCP4 | 15    | 18                      |             |                |                                                 |

| RC7                        |       |                         | I/O         | ST/<br>CMOS    | Digital I/O.                                    |

| CANRX                      |       |                         | Ι           | ST             | CAN bus RX.                                     |

| RX1                        |       |                         | Ι           | ST             | EUSART asynchronous receive.                    |

| DT1                        |       |                         | I/O         | ST             | EUSART synchronous data. (See related TX2/CK2.) |

| CCP4                       |       |                         | I/O         | ST<br>CMOS     | Capture 4 input/Compare 4 output/PWM4 output.   |

| Vss                        | 5     | 8                       | Р           |                |                                                 |

| Vss                        |       |                         |             |                | Ground reference for logic and I/O pins.        |

| Vss                        | 16    | 19                      |             |                |                                                 |

| Vss                        |       |                         |             |                | Ground reference for logic and I/O pins.        |

| Vddcore/Vcap               | 3     | 6                       | Р           |                |                                                 |

| VDDCORE                    |       |                         |             |                | External filter capacitor connection.           |

| VCAP                       |       |                         |             |                | External filter capacitor connection            |

| Vdd                        | 17    | 20                      | Р           |                |                                                 |

| Vdd                        |       |                         |             |                | Positive supply for logic and I/O pins.         |

## TABLE 1-4: PIC18F2XK80 I/O DESCRIPTIONS (CONTINUED)

ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

0

= Output

I = Input

P = Power

© 2010-2012 Microchip Technology Inc.

| Pin Name                                                               | Pin<br>Num  | Pin<br>Type | Buffer<br>Type | Description                                                                             |  |  |  |

|------------------------------------------------------------------------|-------------|-------------|----------------|-----------------------------------------------------------------------------------------|--|--|--|

| RD6/P1C/PSP6                                                           | 4           |             |                |                                                                                         |  |  |  |

| RD6                                                                    |             | I/O         | ST/<br>CMOS    | Digital I/O.                                                                            |  |  |  |

| P1C                                                                    |             | 0           | CMOS           | Enhanced PWM1 Output C.                                                                 |  |  |  |

| PSP6                                                                   |             | I/O         | ST/<br>CMOS    | Parallel Slave Port data.                                                               |  |  |  |

| RD7/P1D/PSP7                                                           | 5           |             |                |                                                                                         |  |  |  |

| RD7                                                                    |             | I/O         | ST/<br>CMOS    | Digital I/O.                                                                            |  |  |  |

| P1D                                                                    |             | 0           | CMOS           | Enhanced PWM1 Output D.                                                                 |  |  |  |

| PSP7                                                                   |             | I/O         | ST/<br>CMOS    | Parallel Slave Port data.                                                               |  |  |  |

| Legend: I <sup>2</sup> C™ = I <sup>2</sup> C<br>ST = Schr<br>I = Input | nitt Trigge | -           |                | CMOS = CMOS compatible input or output<br>OS levels Analog = Analog input<br>O = Output |  |  |  |

| TABLE 1-6: PIC18F6XK80 PINOUT I/O DESCRIPTIONS (CONTINUED | )) |

|-----------------------------------------------------------|----|

|-----------------------------------------------------------|----|

I = Input P = Power

## REGISTER 10-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2

| R/W-0  | U-0 | U-0 | U-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0   |

|--------|-----|-----|-----|-------|--------|--------|---------|

| OSCFIF | —   | —   | —   | BCLIF | HLVDIF | TMR3IF | TMR3GIF |

| bit 7  |     |     |     |       |        |        | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | <b>OSCFIF:</b> Oscillator Fail Interrupt Flag bit<br>1 = Device oscillator failed, clock input has changed to INTOSC (bit must be cleared in software)<br>0 = Device clock is operating |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-4 | Unimplemented: Read as '0'                                                                                                                                                              |

| bit 3   | BCLIF: Bus Collision Interrupt Flag bit                                                                                                                                                 |

|         | <ul> <li>1 = A bus collision occurred (bit must be cleared in software)</li> <li>0 = No bus collision occurred</li> </ul>                                                               |

| bit 2   | HLVDIF: High/Low-Voltage Detect Interrupt Flag bit                                                                                                                                      |

|         | <ul> <li>1 = A low-voltage condition occurred (bit must be cleared in software)</li> <li>0 = The device voltage is above the regulator's low-voltage trip point</li> </ul>              |

| bit 1   | TMR3IF: TMR3 Overflow Interrupt Flag bit                                                                                                                                                |

|         | <ul> <li>1 = TMR3 register overflowed (bit must be cleared in software)</li> <li>0 = TMR3 register did not overflow</li> </ul>                                                          |

| bit 0   | <ul> <li>TMR3GIF: TMR3 Gate Interrupt Flag bit</li> <li>1 = Timer gate interrupt occurred (bit must be cleared in software)</li> <li>0 = No timer gate interrupt occurred</li> </ul>    |

## 13.0 TIMER0 MODULE

The Timer0 module incorporates the following features:

- Software selectable operation as a timer or counter in both 8-bit or 16-bit modes

- · Readable and writable registers

- Dedicated 8-bit, software programmable

prescaler

- Selectable clock source (internal or external)

- · Edge select for external clock

- Interrupt-on-overflow

The T0CON register (Register 13-1) controls all aspects of the module's operation, including the prescale selection. It is both readable and writable.

Figure 13-1 provides a simplified block diagram of the Timer0 module in 8-bit mode. Figure 13-2 provides a simplified block diagram of the Timer0 module in 16-bit mode.

#### REGISTER 13-1: TOCON: TIMER0 CONTROL REGISTER

| R/W-1  | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|--------|-------|-------|-------|-------|-------|-------|

| TMR00N | T08BIT | TOCS  | T0SE  | PSA   | T0PS2 | T0PS1 | T0PS0 |

| bit 7  |        |       |       |       |       |       | bit 0 |

| Legend:    |                   |                                                                             |                               |                    |  |  |  |  |  |  |

|------------|-------------------|-----------------------------------------------------------------------------|-------------------------------|--------------------|--|--|--|--|--|--|

| R = Reada  | able bit          | W = Writable bit                                                            | U = Unimplemented bit         | , read as '0'      |  |  |  |  |  |  |

| -n = Value | at POR            | '1' = Bit is set                                                            | '0' = Bit is cleared          | x = Bit is unknown |  |  |  |  |  |  |

|            |                   |                                                                             |                               |                    |  |  |  |  |  |  |

| bit 7      | TMR0ON            | : Timer0 On/Off Control bit                                                 |                               |                    |  |  |  |  |  |  |

|            |                   | les Timer0                                                                  |                               |                    |  |  |  |  |  |  |

|            | 0 = Stops         | Timer0                                                                      |                               |                    |  |  |  |  |  |  |

| bit 6      | <b>T08BIT</b> : 7 | Timer0 8-Bit/16-Bit Control bit                                             |                               |                    |  |  |  |  |  |  |

|            | 1 = Timer         | 0 is configured as an 8-bit tin                                             | ner/counter                   |                    |  |  |  |  |  |  |

|            | 0 = Timer         | 0 is configured as a 16-bit tin                                             | ner/counter                   |                    |  |  |  |  |  |  |

| bit 5      | TOCS: Tir         | ner0 Clock Source Select bit                                                |                               |                    |  |  |  |  |  |  |

|            | 1 = Trans         | itions on T0CKI pin                                                         |                               |                    |  |  |  |  |  |  |

|            | 0 = Intern        | al instruction cycle clock (CL                                              | KO)                           |                    |  |  |  |  |  |  |

| bit 4      | TOSE: Tir         | ner0 Source Edge Select bit                                                 |                               |                    |  |  |  |  |  |  |

|            | 1 = Increi        | ments on high-to-low transitio                                              | n on T0CKI pin                |                    |  |  |  |  |  |  |

|            | 0 = Increi        | ments on low-to-high transitic                                              | n on T0CKI pin                |                    |  |  |  |  |  |  |

| bit 3      | PSA: Tim          | er0 Prescaler Assignment bit                                                | t                             |                    |  |  |  |  |  |  |

|            | 1 = Timer         | 1 = Timer0 prescaler is not assigned; Timer0 clock input bypasses prescaler |                               |                    |  |  |  |  |  |  |

|            | 0 = Timer         | 0 prescaler is assigned; Time                                               | er0 clock input comes from pr | escaler output     |  |  |  |  |  |  |

| bit 2-0    | T0PS<2:0          | )>: Timer0 Prescaler Select b                                               | pits                          |                    |  |  |  |  |  |  |

|            | 111 <b>= 1</b> :2 | 256 Prescale value                                                          |                               |                    |  |  |  |  |  |  |

|            | 110 <b>= 1</b> :1 | 28 Prescale value                                                           |                               |                    |  |  |  |  |  |  |

|            | 101 <b>= 1</b> :6 | 4 Prescale value                                                            |                               |                    |  |  |  |  |  |  |

|            |                   | 2 Prescale value                                                            |                               |                    |  |  |  |  |  |  |

|            |                   | 6 Prescale value                                                            |                               |                    |  |  |  |  |  |  |

|            |                   | Prescale value                                                              |                               |                    |  |  |  |  |  |  |

|            |                   | Prescale value<br>Prescale value                                            |                               |                    |  |  |  |  |  |  |

|            | 000 = 1:2         |                                                                             |                               |                    |  |  |  |  |  |  |

|            |                   |                                                                             |                               |                    |  |  |  |  |  |  |

## 14.4 Timer1 16-Bit Read/Write Mode

Timer1 can be configured for 16-bit reads and writes. When the RD16 control bit (T1CON<1>) is set, the address for TMR1H is mapped to a buffer register for the high byte of Timer1. A read from TMR1L loads the contents of the high byte of Timer1 into the Timer1 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer1 must also take place through the TMR1H Buffer register. The Timer1 high byte is updated with the contents of TMR1H when a write occurs to TMR1L. This allows a user to write all 16 bits at once to both the high and low bytes of Timer1.

The high byte of Timer1 is not directly readable or writable in this mode. All reads and writes must take place through the Timer1 High Byte Buffer register. Writes to TMR1H do not clear the Timer1 prescaler. The prescaler is only cleared on writes to TMR1L.

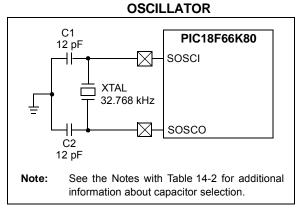

## 14.5 SOSC Oscillator

An on-chip crystal oscillator circuit is incorporated between pins, SOSCI (input) and SOSCO (amplifier output). It can be enabled one of these ways:

- Setting the SOSCEN bit in either the T1CON or T3CON register (TxCON<3>)

- Setting the SOSCGO bit in the OSCCON2 register (OSCCON2<3>)

- Setting the SCSx bits to secondary clock source in the OSCCON register (OSCCON<1:0> = 01)

The SOSCGO bit is used to warm up the SOSC so that it is ready before any peripheral requests it.

The oscillator is a low-power circuit rated for 32 kHz crystals. It will continue to run during all powermanaged modes. The circuit for a typical low-power oscillator is depicted in Figure 14-2. Table 14-2 provides the capacitor selection for the SOSC oscillator.

The user must provide a software time delay to ensure proper start-up of the SOSC oscillator.

## FIGURE 14-2: EXTERNAL COMPONENTS FOR THE SOSC

# TABLE 14-2: CAPACITOR SELECTION FOR THE TIMER OSCILLATOR<sup>(2,3,4,5)</sup>

|                                                                                                                                                                     |                                                                                                                                                                                                     | -                    | -                    |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|--|--|--|--|--|

| Oscillator<br>Type                                                                                                                                                  | Freq.                                                                                                                                                                                               | C1                   | C2                   |  |  |  |  |  |

| LP                                                                                                                                                                  | 32 kHz                                                                                                                                                                                              | 12 pF <sup>(1)</sup> | 12 pF <sup>(1)</sup> |  |  |  |  |  |

| <b>Note 1:</b> Microchip suggests these values as a startin point in validating the oscillator circuit.                                                             |                                                                                                                                                                                                     |                      |                      |  |  |  |  |  |

| t                                                                                                                                                                   | <ol> <li>Higher capacitance increases the stability or<br/>the oscillator, but also increases the start-up<br/>time.</li> </ol>                                                                     |                      |                      |  |  |  |  |  |

| C<br>r                                                                                                                                                              | <ol> <li>Since each resonator/crystal has its own<br/>characteristics, the user should consult the<br/>resonator/crystal manufacturer for appropriate<br/>values of external components.</li> </ol> |                      |                      |  |  |  |  |  |

| <ul> <li>Capacitor values are for design guidance onl<br/>Values listed would be typical of a CL = 10 p<br/>rated crystal, when SOSCSEL&lt;1:0&gt; = 11.</li> </ul> |                                                                                                                                                                                                     |                      |                      |  |  |  |  |  |

|                                                                                                                                                                     | ncorrect capacit<br>juency not meet                                                                                                                                                                 |                      |                      |  |  |  |  |  |

The SOSC crystal oscillator drive level is determined based on the SOSCSELx (CONFIG1L<4:3>) Configuration bits. The Higher Drive Level mode.

based on the SOSCSELx (CONFIG1L<4:3>) Configuration bits. The Higher Drive Level mode, SOSCSEL<1:0> = 11, is intended to drive a wide variety of 32.768 kHz crystals with a variety of Load Capacitance (CL) ratings.

The Lower Drive Level mode is highly optimized for extremely low-power consumption. It is not intended to drive all types of 32.768 kHz crystals. In the Low Drive Level mode, the crystal oscillator circuit may not work correctly if excessively large discrete capacitors are placed on the SOSCO and SOSCI pins. This mode is designed to work only with discrete capacitances of approximately 3 pF-10 pF on each pin.

Crystal manufacturers usually specify a CL (Load Capacitance) rating for their crystals. This value is related to, but not necessarily the same as, the values that should be used for C1 and C2 in Figure 14-2.

### 16.1 Timer3 Gate Control Register

The Timer3 Gate Control register (T3GCON), provided in Register 14-2, is used to control the Timer3 gate.

#### REGISTER 16-2: T3GCON: TIMER3 GATE CONTROL REGISTER<sup>(1)</sup>

| R/W-0         | R/W-0                              | R/W-0           | R/W-0                             | R/W-0                                      | R-x                                   | R/W-0           | R/W-0         |  |  |  |

|---------------|------------------------------------|-----------------|-----------------------------------|--------------------------------------------|---------------------------------------|-----------------|---------------|--|--|--|

| TMR3GE        | T3GPOL                             | T3GTM           | T3GSPM                            | T3GGO/T3DONE                               | T3GVAL                                | T3GSS1          | T3GSS0        |  |  |  |

| bit 7         |                                    |                 |                                   | · · ·                                      |                                       |                 | bit 0         |  |  |  |

|               |                                    |                 |                                   |                                            |                                       |                 |               |  |  |  |

| Legend:       | a h:t                              |                 | . L.:4                            |                                            | l hit read as (                       | 0,              |               |  |  |  |

| R = Readable  |                                    | W = Writable    |                                   | U = Unimplemented                          | i bit, read as                        |                 |               |  |  |  |

| -n = Value at | PUK                                | '1' = Bit is se | el                                | '0' = Bit is cleared                       |                                       | x = Bit is unkr | IOWII         |  |  |  |

| bit 7         | TMR3GE: Ti                         | mer3 Gate Er    | nable bit                         |                                            |                                       |                 |               |  |  |  |

|               | If TMR3ON =                        | <u>= 0:</u>     |                                   |                                            |                                       |                 |               |  |  |  |

|               | This bit is ign                    |                 |                                   |                                            |                                       |                 |               |  |  |  |

|               | If TMR3ON =                        |                 | tralled by the                    | Timor? gata function                       |                                       |                 |               |  |  |  |

|               |                                    |                 |                                   | Timer3 gate function<br>gate function      |                                       |                 |               |  |  |  |

| bit 6         | T3GPOL: Tir                        | -               |                                   | gate failettett                            |                                       |                 |               |  |  |  |

|               |                                    |                 |                                   | counts when gate is h                      | igh)                                  |                 |               |  |  |  |

|               | 0 = Timer3 g                       | ate is active-l | ow (Timer3 co                     | ounts when gate is low                     | w)                                    |                 |               |  |  |  |

| bit 5         | T3GTM: Timer3 Gate Toggle Mode bit |                 |                                   |                                            |                                       |                 |               |  |  |  |

|               |                                    |                 | node is enable                    |                                            | · · · · · · · · · · · · · · · · · · · |                 |               |  |  |  |

|               |                                    |                 | node is disabi<br>es on every ris | ed and toggle flip-flop<br>sing edge       | o is cleared                          |                 |               |  |  |  |

| bit 4         | -                                  |                 | ngle Pulse Mo                     |                                            |                                       |                 |               |  |  |  |

|               |                                    |                 | •                                 | enabled and is contro                      | lling Timer3 g                        | ate             |               |  |  |  |

|               | 0 = Timer3 G                       | ate Single P    | ulse mode is o                    | disabled                                   |                                       |                 |               |  |  |  |

| bit 3         |                                    |                 | -                                 | Pulse Acquisition Stat                     |                                       |                 |               |  |  |  |

|               |                                    |                 |                                   | quisition is ready, wa                     |                                       |                 |               |  |  |  |

|               |                                    | •               |                                   | quisition has complet<br>3GSPM is cleared. | ted or has not                        | been started    |               |  |  |  |

| bit 2         |                                    | -               | rrent State bit                   |                                            |                                       |                 |               |  |  |  |

| 5.1.2         |                                    |                 |                                   | k gate that could be p                     | provided to TM                        | R3H:TMR3L.      | Unaffected by |  |  |  |

|               | Timerx Gate                        |                 |                                   | 5                                          |                                       |                 | ,             |  |  |  |

| bit 1-0       | T3GSS<1:0>                         | : Timer3 Gat    | e Source Sele                     | ect bits                                   |                                       |                 |               |  |  |  |

|               | 11 = Compar                        |                 |                                   |                                            |                                       |                 |               |  |  |  |

|               | 10 = Compare 10 = TMD4 t           |                 |                                   |                                            |                                       |                 |               |  |  |  |

|               | 01 = TMR4 t<br>00 = Timer3         |                 | ουιραι                            |                                            |                                       |                 |               |  |  |  |

|               | Watchdog Ti                        |                 |                                   |                                            |                                       |                 |               |  |  |  |

### REGISTER 18-2: CTMUCONL: CTMU CONTROL LOW REGISTER

| R/W-0         | R/W-0          | R/W-0                                              | R/W-0           | R/W-0             | R/W-0           | R/W-0           | R/W-0    |  |  |  |  |  |

|---------------|----------------|----------------------------------------------------|-----------------|-------------------|-----------------|-----------------|----------|--|--|--|--|--|

| EDG2POL       | EDG2SEL1       | EDG2SEL0                                           | EDG1POL         | EDG1SEL1          | EDG1SEL0        | EDG2STAT        | EDG1STAT |  |  |  |  |  |

| bit 7         |                |                                                    |                 |                   |                 |                 | bit 0    |  |  |  |  |  |

|               |                |                                                    |                 |                   |                 |                 |          |  |  |  |  |  |

| Legend:       |                |                                                    |                 |                   |                 |                 |          |  |  |  |  |  |

| R = Readabl   | e bit          | W = Writable b                                     | bit             | U = Unimplem      | ented bit, read | 1 as '0'        |          |  |  |  |  |  |

| -n = Value at | POR            | '1' = Bit is set                                   |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown     |  |  |  |  |  |

|               |                |                                                    |                 |                   |                 |                 |          |  |  |  |  |  |

| bit 7         | EDG2POL: E     | dge 2 Polarity S                                   | Select bit      |                   |                 |                 |          |  |  |  |  |  |

|               |                | programmed f                                       |                 |                   |                 |                 |          |  |  |  |  |  |

|               | 0 = Edge 2 is  | programmed for                                     | or a negative e | edge response     |                 |                 |          |  |  |  |  |  |

| bit 6-5       |                | :0>: Edge 2 Sou                                    | urce Select bit | S                 |                 |                 |          |  |  |  |  |  |

|               | 11 = CTED1 pin |                                                    |                 |                   |                 |                 |          |  |  |  |  |  |

|               |                | 10 = CTED2 pin<br>01 = ECCP1 Special Event Trigger |                 |                   |                 |                 |          |  |  |  |  |  |

|               |                | pecial Event Tri                                   |                 |                   |                 |                 |          |  |  |  |  |  |

| bit 4         | EDG1POL: E     | dge 1 Polarity S                                   | Select bit      |                   |                 |                 |          |  |  |  |  |  |

|               | 1 = Edge 1 is  | programmed f                                       | or a positive e | dge response      |                 |                 |          |  |  |  |  |  |

|               | 0 = Edge 1 is  | s programmed f                                     | or a negative e | edge response     |                 |                 |          |  |  |  |  |  |

| bit 3-2       | EDG1SEL<1:     | :0>: Edge 1 Sou                                    | urce Select bit | s                 |                 |                 |          |  |  |  |  |  |

|               | 11 = CTED1     |                                                    |                 |                   |                 |                 |          |  |  |  |  |  |

|               | 10 = CTED2     |                                                    |                 |                   |                 |                 |          |  |  |  |  |  |

|               |                | Special Event T<br>pecial Event Tri                | 00              |                   |                 |                 |          |  |  |  |  |  |

| bit 1         |                | Edge 2 Status b                                    |                 |                   |                 |                 |          |  |  |  |  |  |

|               |                | vent has occurr                                    |                 |                   |                 |                 |          |  |  |  |  |  |

|               | Ų              | vent has not oc                                    |                 |                   |                 |                 |          |  |  |  |  |  |

| bit 0         | •              | Edge 1 Status b                                    |                 |                   |                 |                 |          |  |  |  |  |  |

|               |                | vent has occurr                                    |                 |                   |                 |                 |          |  |  |  |  |  |

|               | 0 = Edge 1 e   |                                                    |                 |                   |                 |                 |          |  |  |  |  |  |

| TABLE 19-5 |               |                        |               |          |          |         | <b>D</b> 14 | <b>D</b> '' 0 |

|------------|---------------|------------------------|---------------|----------|----------|---------|-------------|---------------|

| Name       | Bit 7         | Bit 6                  | Bit 5         | Bit 4    | Bit 3    | Bit 2   | Bit 1       | Bit 0         |

| INTCON     | GIE/GIEH      | PEIE/GIEL              | TMR0IE        | INT0IE   | RBIE     | TMR0IF  | INT0IF      | RBIF          |

| RCON       | IPEN          | SBOREN                 | CM            | RI       | TO       | PD      | POR         | BOR           |

| PIR3       | —             | —                      | RC2IF         | TX2IF    | CTMUIF   | CCP2IF  | CCP1IF      | —             |

| PIE3       | —             | —                      | RC2IE         | TX2IE    | CTMUIE   | CCP2IE  | CCP1IE      | —             |

| IPR3       | _             | _                      | RC2IP         | TX2IP    | CTMUIP   | CCP2IP  | CCP1IP      | _             |

| PIR4       | TMR4IF        | EEIF                   | CMP2IF        | CMP1IF   | —        | CCP5IF  | CCP4IF      | CCP3IF        |

| PIE4       | TMR4IE        | EEIE                   | CMP2IE        | CMP1IE   | —        | CCP5IE  | CCP4IE      | CCP3IE        |

| IPR4       | TMR4IP        | EEIP                   | CMP2IP        | CMP1IP   | —        | CCP5IP  | CCP4IP      | CCP3IP        |

| TRISB      | TRISB7        | TRISB6                 | TRISB5        | TRISB4   | TRISB3   | TRISB2  | TRISB1      | TRISB0        |

| TRISC      | TRISC7        | TRISC6                 | TRISC5        | TRISC4   | TRISC3   | TRISC2  | TRISC1      | TRISC0        |

| TMR2       | Timer2 Reg    | ister                  |               |          |          |         |             |               |

| TMR4       | Timer4 Reg    | ister                  |               |          |          |         |             |               |

| PR2        | Timer2 Peri   | Timer2 Period Register |               |          |          |         |             |               |

| PR4        | Timer4 Peri   | od Register            |               |          |          |         |             |               |

| T2CON      | —             | T2OUTPS3               | T2OUTPS2      | T2OUTPS1 | T2OUTPS0 | TMR2ON  | T2CKPS1     | T2CKPS0       |

| T4CON      | —             | T4OUTPS3               | T4OUTPS2      | T4OUTPS1 | T4OUTPS0 | TMR4ON  | T4CKPS1     | T4CKPS0       |

| CCPR2L     | Capture/Co    | mpare/PWM              | Register 2 Lo | ow Byte  |          |         |             |               |

| CCPR2H     | Capture/Co    | mpare/PWM              | Register 2 H  | igh Byte |          |         |             |               |

| CCPR3L     | Capture/Co    | mpare/PWM              | Register 3 Lo | ow Byte  |          |         |             |               |

| CCPR3H     | Capture/Co    | mpare/PWM              | Register 3 H  | igh Byte |          |         |             |               |

| CCPR4L     | Capture/Co    | mpare/PWM              | Register 4 Lo | ow Byte  |          |         |             |               |

| CCPR4H     | Capture/Co    | mpare/PWM              | Register 4 H  | igh Byte |          |         |             |               |

| CCPR5L     | Capture/Co    | mpare/PWM              | Register 5 Lo | ow Byte  |          |         |             |               |

| CCPR5H     | Capture/Co    | mpare/PWM              | Register 5 H  | igh Byte |          |         |             |               |

| CCP2CON    | —             | _                      | DC2B1         | DC2B0    | CCP2M3   | CCP2M2  | CCP2M1      | CCP2M0        |

| CCP3CON    | —             | _                      | DC3B1         | DC3B0    | CCP3M3   | CCP3M2  | CCP3M1      | CCP3M0        |

| CCP4CON    | —             | _                      | DC4B1         | DC4B0    | CCP4M3   | CCP4M2  | CCP4M1      | CCP4M0        |

| CCP5CON    | —             | —                      | DC5B1         | DC5B0    | CCP5M3   | CCP5M2  | CCP5M1      | CCP5M0        |

| CCPTMRS    | _             | —                      | —             | C5TSEL   | C4TSEL   | C3TSEL  | C2TSEL      | C1TSEL        |

| PMD0       | CCP5MD        | CCP4MD                 | CCP3MD        | CCP2MD   | CCP1MD   | UART2MD | UART1MD     | SSPMD         |

|            | · = unimpleme |                        |               |          |          |         |             | 225N          |

### TABLE 19-5: REGISTERS ASSOCIATED WITH PWM AND TIMERS

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PWM or Timer2/4.

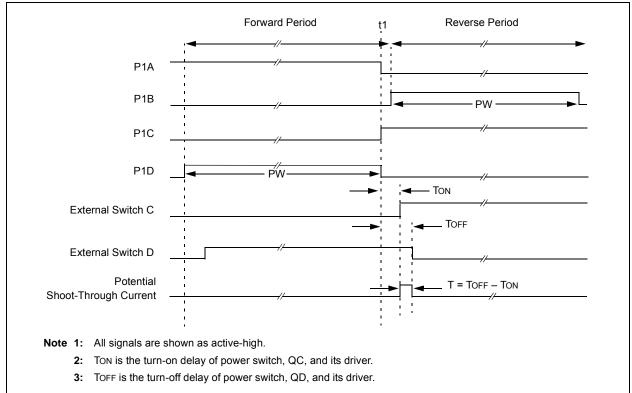

#### FIGURE 20-11: EXAMPLE OF PWM DIRECTION CHANGE AT NEAR 100% DUTY CYCLE

#### 20.4.3 START-UP CONSIDERATIONS

When any PWM mode is used, the application hardware must use the proper external pull-up and/or pull-down resistors on the PWM output pins.

| Note: | When the microcontroller is released from Reset, all of the I/O pins are in the |

|-------|---------------------------------------------------------------------------------|

|       | high-impedance state. The external                                              |

|       | circuits must keep the power switch                                             |

|       | devices in the OFF state until the micro-                                       |

|       | controller drives the I/O pins with the                                         |

|       | proper signal levels or activates the PWM                                       |

|       | output(s).                                                                      |

The CCP1M<1:0> bits of the CCP1CON register allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (P1A/P1C and P1B/P1D). The PWM output polarities must be selected before the PWM pin output drivers are enabled. Changing the polarity configuration while the PWM pin output drivers are enabled is not recommended since it may result in damage to the application circuits.

The P1A, P1B, P1C and P1D output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pin output drivers at the same time as the Enhanced PWM modes may cause damage to the application circuit. The Enhanced PWM modes must be enabled in the proper Output mode and complete a full PWM cycle before enabling the PWM pin output drivers. The completion of a full PWM cycle is indicated by the TMR2IF or TMR4IF bit of the PIR1 or PIR4 register being set as the second PWM period begins.

#### 20.4.4 ENHANCED PWM AUTO-SHUTDOWN MODE

The PWM mode supports an Auto-Shutdown mode that will disable the PWM outputs when an external shutdown event occurs. Auto-Shutdown mode places the PWM output pins into a predetermined state. This mode is used to help prevent the PWM from damaging the application.

The auto-shutdown sources are selected using the ECCP1AS<2:0> bits (ECCP1AS<6:4>). A shutdown event may be generated by:

- A logic '0' on the pin that is assigned the FLT0 input function

- Comparator C1

- Comparator C2

- · Setting the ECCP1ASE bit in firmware

## 21.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

### 21.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be devices such as serial EEPROMs, shift registers, display drivers and A/D Converters. The MSSP module can operate in either of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

- Full Master mode

- Slave mode (with general address call)

The  $\mathrm{I}^2\mathrm{C}$  interface supports the following modes in hardware:

- Master mode

- · Multi-Master mode

- Slave mode with 5-bit and 7-bit address masking (with address masking for both 10-bit and 7-bit addressing)

## 21.2 Control Registers

The MSSP module has three associated control registers. These include a status register (SSPSTAT) and two control registers (SSPCON1 and SSPCON2). The use of these registers and their individual configuration bits differ significantly depending on whether the MSSP module is operated in SPI or  $I^2C$  mode.

Additional details are provided under the individual sections.

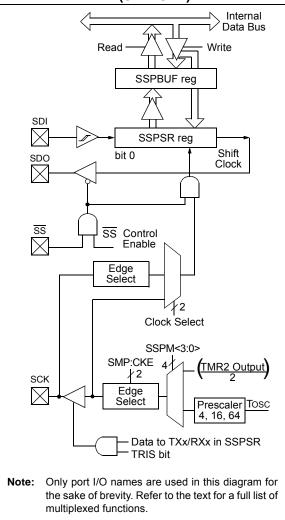

## 21.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDA/SDI

- Serial Clock (SCK) RC3/REF0/SCL/SCK

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS) – RA5/AN4/C2INB/ HLVDIN/T1CKI/SS/CTMU1

Figure 21-1 shows the block diagram of the MSSP module when operating in SPI mode.

#### FIGURE 21-1:

#### MSSP BLOCK DIAGRAM (SPI MODE)

#### 21.3.9 OPERATION IN POWER-MANAGED MODES

In SPI Master mode, module clocks may be operating at a different speed than when in full-power mode; in the case of the Sleep mode, all clocks are halted.

In Idle modes, a clock is provided to the peripherals. That clock can be from the primary clock source, the secondary clock (SOSC oscillator) or the INTOSC source. See **Section 3.3** "**Clock Sources and Oscillator Switching**" for additional information.

In most cases, the speed that the master clocks SPI data is not important; however, this should be evaluated for each system.

If MSSP interrupt is enabled, it can wake the controller from Sleep mode, or one of the Idle modes, when the master completes sending data. If an exit from Sleep or Idle mode is not desired, MSSP interrupts should be disabled.

If the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the device wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in any power-managed mode and data to be shifted into the SPI Transmit/Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set, and if enabled, will wake the device.

## 21.3.10 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 21.3.11 BUS MODE COMPATIBILITY

Table 21-1 shows the compatibility between the standard SPI modes, and the states of the CKP and CKE control bits.

| Standard SPI Mode | Control Bits State |     |  |  |  |

|-------------------|--------------------|-----|--|--|--|

| Terminology       | СКР                | CKE |  |  |  |

| 0, 0              | 0                  | 1   |  |  |  |

| 0, 1              | 0                  | 0   |  |  |  |

| 1, 0              | 1                  | 1   |  |  |  |

| 1, 1              | 1                  | 0   |  |  |  |

#### TABLE 21-1: SPI BUS MODES

There is also an SMP bit which controls when the data is sampled.

| Name    | Bit 7                                 | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1   | Bit 0  |

|---------|---------------------------------------|-----------|--------|--------|--------|---------|---------|--------|

| INTCON  | GIE/GIEH                              | PEIE/GIEL | TMR0IE | INT0IE | RBIE   | TMR0IF  | INT0IF  | RBIF   |

| PIR1    | PSPIF                                 | ADIF      | RC1IF  | TX1IF  | SSPIF  | TMR1GIF | TMR2IF  | TMR1IF |

| PIE1    | PSPIE                                 | ADIE      | RC1IE  | TX1IE  | SSPIE  | TMR1GIE | TMR2IE  | TMR1IE |

| IPR1    | PSPIP                                 | ADIP      | RC1IP  | TX1IP  | SSPIP  | TMR1GIP | TMR2IP  | TMR1IP |

| TRISA   | TRISA7                                | TRISA6    | TRISA5 |        | TRISA3 | TRISA2  | TRISA1  | TRISA0 |

| TRISC   | TRISC7                                | TRISC6    | TRISC5 | TRISC4 | TRISC3 | TRISC2  | TRISC1  | TRISC0 |

| SSPBUF  | MSSP Receive Buffer/Transmit Register |           |        |        |        |         |         |        |

| SSPCON1 | WCOL                                  | SSPOV     | SSPEN  | CKP    | SSPM3  | SSPM2   | SSPM1   | SSPM0  |

| SSPSTAT | SMP                                   | CKE       | D/Ā    | Р      | S      | R/W     | UA      | BF     |

| ODCON   | SSPOD                                 | CCP5OD    | CCP4OD | CCP3OD | CCP2OD | CCP10D  | U2OD    | U10D   |

| PMD0    | CCP5MD                                | CCP4MD    | CCP3MD | CCP2MD | CCP1MD | UART2MD | UART1MD | SSPMD  |

#### TABLE 21-2: REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: Shaded cells are not used by the MSSP module in SPI mode.

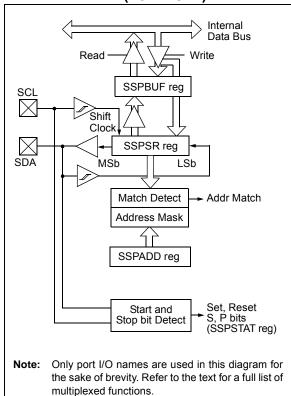

## 21.4 I<sup>2</sup>C Mode

The MSSP module in  $I^2C$  mode fully implements all master and slave functions (including general call support), and provides interrupts on Start and Stop bits in hardware to determine a free bus (multi-master function). The MSSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer:

- Serial Clock (SCL) RC3/REFO/SCL/SCK

- Serial Data (SDA) RC4/SDA/SDI

The user must configure these pins as inputs by setting the associated TRIS bits.

#### FIGURE 21-7: MSSP BLOCK DIAGRAM (I<sup>2</sup>C™ MODE)

### 21.4.1 REGISTERS

The MSSP module has seven registers for  ${\rm I}^2{\rm C}$  operation. These are:

- MSSP Control Register 1 (SSPCON1)

- MSSP Control Register 2 (SSPCON2)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

- MSSP Address Register (SSPADD)

- I<sup>2</sup>C Slave Address Mask Register (SSPMSK)

SSPCON1, SSPCON2 and SSPSTAT are the control and status registers in I<sup>2</sup>C mode operation. The SSPCON1 and SSPCON2 registers are readable and writable. The lower 6 bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write.

SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

SSPADD contains the slave device address when the MSSP is configured in I<sup>2</sup>C Slave mode. When the MSSP is configured in Master mode, all eight bits of SSPADD act as the Baud Rate Generator reload value.

SSPMSK holds the slave address mask value when the module is configured for 7-Bit Address Masking mode. While it is a separate register, it shares the same SFR address as SSPADD; it is only accessible when the SSPM<3:0> bits are specifically set to permit access. Additional details are provided in Section 21.4.3.4 "7-Bit Address Masking Mode".

In receive operations, SSPSR and SSPBUF together, create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not double-buffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

### 21.4.2 OPERATION

The MSSP module functions are enabled by setting the MSSP Enable bit, SSPEN (SSPCON1<5>).

The SSPCON1 register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON1<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Master mode, clock

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Firmware Controlled Master mode, slave is Idle

Selection of any I<sup>2</sup>C mode with the SSPEN bit set forces the SCL and SDA pins to be open-drain, provided these pins are programmed as inputs by setting the appropriate TRISC bit. To ensure proper operation of the module, pull-up resistors must be provided externally to the SCL and SDA pins.

#### 21.4.3 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The MSSP module will override the input state with the output data when required (slave-transmitter).

The  $I^2C$  Slave mode hardware will always generate an interrupt on an address match. Address masking will allow the hardware to generate an interrupt for more than one address (up to 31 in 7-bit addressing and up to 63 in 10-bit addressing). Through the mode select bits, the user can also choose to interrupt on Start and Stop bits.

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overrightarrow{ACK}$ ) pulse and load the SSPBUF register with the received value currently in the SSPSR register.

Any combination of the following conditions will cause the MSSP module not to give this ACK pulse:

- The Buffer Full bit, BF (SSPSTAT<0>), was set before the transfer was received.

- The overflow bit, SSPOV (SSPCON1<6>), was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit, SSPIF, is set. The BF bit is cleared by reading the SSPBUF register, while bit, SSPOV, is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, are shown in timing Parameter 100 and Parameter 101.

### 21.4.3.1 Addressing

Once the MSSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8 bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register, SSPSR<7:1>, is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- 1. The SSPSR register value is loaded into the SSPBUF register.

- 2. The Buffer Full bit, BF, is set.

- 3. An ACK pulse is generated.

- 4. The MSSP Interrupt Flag bit, SSPIF, is set (and interrupt is generated, if enabled) on the falling edge of the ninth SCL pulse.

In 10-Bit Addressing mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. The  $R/\overline{W}$  (SSPSTAT<2>) bit must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '11110 A9 A8 0', where 'A9' and 'A8' are the two MSbs of the address. The sequence of events for 10-bit addressing is as follows, with Steps 7 through 9 for the slave-transmitter:

- 1. Receive first (high) byte of address (bits, SSPIF, BF and UA, are set on address match).

- 2. Update the SSPADD register with second (low) byte of address (clears bit, UA, and releases the SCL line).

- 3. Read the SSPBUF register (clears bit, BF) and clear flag bit, SSPIF.

- 4. Receive second (low) byte of address (bits, SSPIF, BF and UA, are set).

- 5. Update the SSPADD register with the first (high) byte of address. If match releases SCL line, this will clear bit, UA.

- 6. Read the SSPBUF register (clears bit, BF) and clear flag bit SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (bits, SSPIF and BF, are set).

- 9. Read the SSPBUF register (clears bit, BF) and clear flag bit, SSPIF.

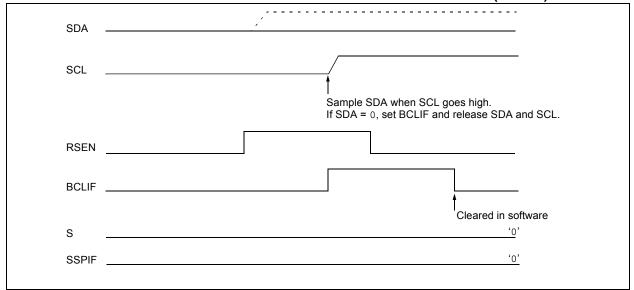

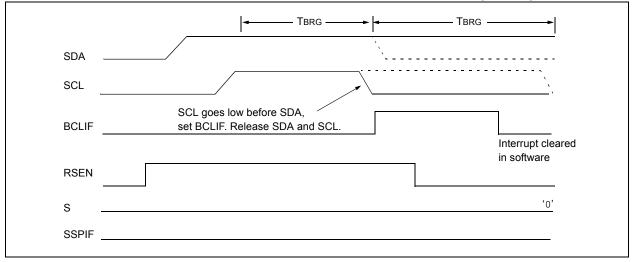

## 21.4.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from a low level to a high level.

- SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 21-31). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition (see Figure 21-32).

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

FIGURE 21-31: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

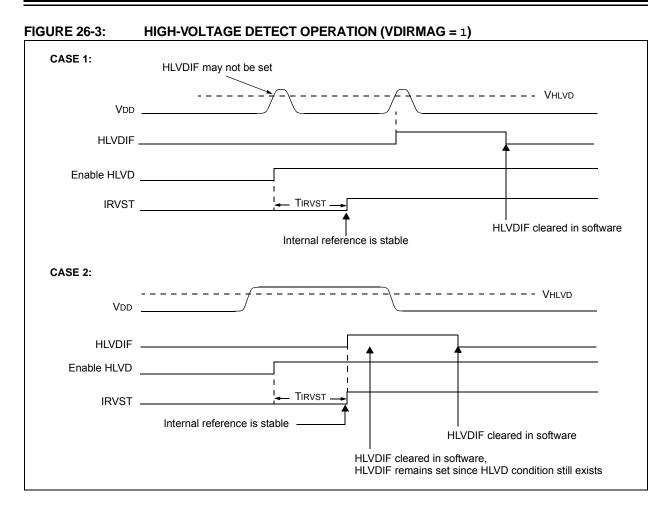

## 26.5 Applications

In many applications, it is desirable to detect a drop below, or rise above, a particular voltage threshold. For example, the HLVD module could be periodically enabled to detect Universal Serial Bus (USB) attach or detach. This assumes the device is powered by a lower voltage source than the USB when detached. An attach would indicate a high-voltage detect from, for example, 3.3V to 5V (the voltage on USB) and vice versa for a detach. This feature could save a design a few extra components and an attach signal (input pin).

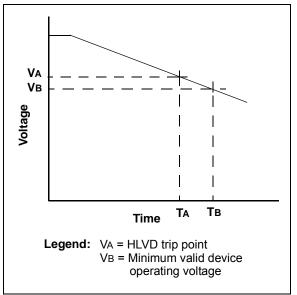

For general battery applications, Figure 26-4 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage, VA, the HLVD logic generates an interrupt at time, TA. The interrupt could cause the execution of an ISR, which would allow the application to perform "house-keeping tasks" and a controlled shutdown before the device voltage exits the valid operating range at TB. This would give the application a time window, represented by the difference between TA and TB, to safely exit.

#### TYPICAL LOW-VOLTAGE DETECT APPLICATION

| Byte-oriented file register operations                                                                                                                                                                                                                | Example Instruction  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| <u>15 10 9 8 7 0</u>                                                                                                                                                                                                                                  |                      |

| OPCODE d a f (FILE #)                                                                                                                                                                                                                                 | ADDWF MYREG, W, B    |

| <ul> <li>d = 0 for result destination to be WREG register</li> <li>d = 1 for result destination to be file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul> |                      |

| Byte to Byte move operations (2-word)                                                                                                                                                                                                                 |                      |

| <u>15 12 11 0</u>                                                                                                                                                                                                                                     |                      |

| OPCODE f (Source FILE #)                                                                                                                                                                                                                              | MOVFF MYREG1, MYREG2 |

| 15 12 11 0                                                                                                                                                                                                                                            |                      |

| 1111 f (Destination FILE #)                                                                                                                                                                                                                           |                      |

| f = 12-bit file register address                                                                                                                                                                                                                      |                      |

| Bit-oriented file register operations                                                                                                                                                                                                                 |                      |

| 15 12 11 9 8 7 0                                                                                                                                                                                                                                      |                      |

| OPCODE b (BIT #) a f (FILE #)                                                                                                                                                                                                                         | BSF MYREG, bit, B    |

| <ul> <li>b = 3-bit position of bit in file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul>                                                                 |                      |

| Literal operations                                                                                                                                                                                                                                    |                      |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE k (literal)                                                                                                                                                                                                                                    | MOVLW 7Fh            |

| k = 8-bit immediate value                                                                                                                                                                                                                             |                      |

| Control operations                                                                                                                                                                                                                                    |                      |

|                                                                                                                                                                                                                                                       |                      |

| CALL, GOTO and Branch operations<br>15 8 7 0                                                                                                                                                                                                          |                      |

| OPCODE n<7:0> (literal)                                                                                                                                                                                                                               | GOTO Label           |

| 15 12 11 0                                                                                                                                                                                                                                            |                      |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                |                      |

| n = 20-bit immediate value                                                                                                                                                                                                                            |                      |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE S n<7:0> (literal)                                                                                                                                                                                                                             | CALL MYFUNC          |

| 15 12 11 0                                                                                                                                                                                                                                            |                      |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                |                      |

| S = Fast bit                                                                                                                                                                                                                                          |                      |

| 15 11 10 0                                                                                                                                                                                                                                            |                      |

| OPCODE n<10:0> (literal)                                                                                                                                                                                                                              | BRA MYFUNC           |

|                                                                                                                                                                                                                                                       |                      |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE n<7:0> (literal)                                                                                                                                                                                                                               | BC MYFUNC            |

| Mnemonic, |                                 | Description                              | 0          | 16-Bit Instruction Word |               |      | Status |                 |             |

|-----------|---------------------------------|------------------------------------------|------------|-------------------------|---------------|------|--------|-----------------|-------------|

| Opera     | nds                             | Description                              | Cycles     | MSb                     |               |      | LSb    | Affected        | Notes       |

| BYTE-OR   | BYTE-ORIENTED OPERATIONS        |                                          |            |                         |               |      |        |                 |             |

| ADDWF     | f, d, a                         | Add WREG and f                           | 1          | 0010                    | 01da          | ffff | ffff   | C, DC, Z, OV, N | 1, 2        |

| ADDWFC    | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010                    | 00da          | ffff | ffff   | C, DC, Z, OV, N | 1, 2        |

| ANDWF     | f, d, a                         | AND WREG with f                          | 1          | 0001                    | 01da          | ffff | ffff   | Z, N            | 1,2         |

| CLRF      | f, a                            | Clear f                                  | 1          | 0110                    | 101a          | ffff | ffff   | Z               | 2           |

| COMF      | f, d, a                         | Complement f                             | 1          | 0001                    | 11da          | ffff | ffff   | Z, N            | 1, 2        |

| CPFSEQ    | f, a                            | Compare f with WREG, Skip =              | 1 (2 or 3) | 0110                    | 001a          | ffff | ffff   | None            | 4           |

| CPFSGT    | f, a                            | Compare f with WREG, Skip >              | 1 (2 or 3) | 0110                    | 010a          | ffff | ffff   | None            | 4           |

| CPFSLT    | f, a                            | Compare f with WREG, Skip <              | 1 (2 or 3) | 0110                    | 000a          | ffff | ffff   | None            | 1, 2        |

| DECF      | f, d, a                         | Decrement f                              | 1          | 0000                    | 01da          | ffff | ffff   | C, DC, Z, OV, N | 1, 2, 3, 4  |

| DECFSZ    | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010                    | 11da          | ffff | ffff   | None            | 1, 2, 3, 4  |

| DCFSNZ    | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 11da          | ffff | ffff   | None            | 1, 2        |

| INCF      | f, d, a                         | Increment f                              | 1          | 0010                    | 10da          | ffff | ffff   | C, DC, Z, OV, N | 1, 2, 3, 4  |

| INCFSZ    | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011                    | 11da          | ffff | ffff   | None            | 4           |

| INFSNZ    | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 10da          | ffff | ffff   | None            | 1, 2        |

| IORWF     | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001                    | 00da          | ffff | ffff   | Z, N            | 1, 2        |

| MOVF      | f, d, a                         | Move f                                   | 1          | 0101                    | 00da          | ffff | ffff   | Z, N            | 1           |

| MOVFF     | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          | 1100                    | ffff          | ffff | ffff   | None            |             |

|           | 0 u                             | f <sub>d</sub> (destination) 2nd word    |            | 1111                    | ffff          | ffff | ffff   |                 |             |

| MOVWF     | f, a                            | Move WREG to f                           | 1          | 0110                    | 111a          | ffff | ffff   | None            |             |

| MULWF     | f, a                            | Multiply WREG with f                     | 1          | 0000                    | 001a          | ffff | ffff   | None            | 1, 2        |

| NEGF      | f, a                            | Negate f                                 | 1          | 0110                    | 110a          | ffff | ffff   | C, DC, Z, OV, N |             |

| RLCF      | f, d, a                         | Rotate Left f through Carry              | 1          | 0011                    | 01da          | ffff | ffff   | C, Z, N         | 1, 2        |

| RLNCF     | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100                    | 01da          | ffff | ffff   | Z, N            |             |

| RRCF      | f, d, a                         | Rotate Right f through Carry             | 1          | 0011                    | 00da          | ffff | ffff   | C, Z, N         |             |

| RRNCF     | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100                    | 00da          | ffff | ffff   | Z, N            |             |

| SETF      | f, a                            | Set f                                    | 1          | 0110                    | 100a          | ffff | ffff   | None            | 1, 2        |

| SUBFWB    | f, d, a                         | Subtract f from WREG with<br>Borrow      | 1          | 0101                    | 01da          | ffff | ffff   | C, DC, Z, OV, N |             |

| SUBWF     | f, d, a                         | Subtract WREG from f                     | 1          | 0101                    | 11da          | ffff | ffff   | C, DC, Z, OV, N | 1, 2        |

| SUBWFB    |                                 | Subtract WREG from f with<br>Borrow      | 1          |                         | 10da          | ffff | ffff   | C, DC, Z, OV, N | -           |

| SWAPF     | f, d, a                         | Swap Nibbles in f                        | 1          | 0011                    | 10da          | ffff | ffff   | None            | 4           |

| TSTFSZ    | f. a                            | Test f, Skip if 0                        | 1 (2 or 3) |                         | 011a          | ffff | ffff   | None            | 4<br>1, 2   |

| XORWF     | , -                             | Exclusive OR WREG with f                 | 1 (2 01 3) |                         | 1011a<br>10da |      | ffff   |                 | ı, <b>∠</b> |