#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | ECANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.6К х 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x12b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f26k80t-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R), or -20%/+80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex:  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%$ . Due to the extreme temperature tolerance, a 10  $\mu$ F nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal regulator if the application must operate over a wide temperature range.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

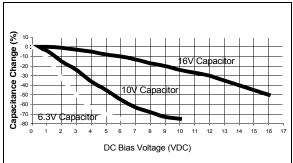

A typical DC bias voltage vs. capacitance graph for X7R type and Y5V type capacitors is shown in Figure 2-4.

### FIGURE 2-4: DC BIAS VOLTAGE vs. CAPACITANCE CHARACTERISTICS

When selecting a ceramic capacitor to be used with the internal voltage regulator, it is suggested to select a high-voltage rating, so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at 16V for the 2.5V core voltage. Suggested capacitors are shown in Table 2-1.

# 2.5 ICSP Pins

The PGC and PGD pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100 $\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGC and PGD pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGCx/PGDx pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 30.0 "Development Support"**.

If the IRCFx bits and the INTSRC bit are all clear, the INTOSC output (HF-INTOSC/MF-INTOSC) is not enabled and the HFIOFS and MFIOFS bits will remain clear. There will be no indication of the current clock source. The LF-INTOSC source is providing the device clocks.

If the IRCFx bits are changed from all clear (thus, enabling the INTOSC output) or if INTSRC or MFIOSEL is set, the HFIOFS or MFIOFS bit is set after the INTOSC output becomes stable. For details, see Table 4-3.

| IRCF<2:0> | INTSRC | MFIOSEL | Status of MFIOFS or HFIOFS when INTOSC is Stable     |

|-----------|--------|---------|------------------------------------------------------|

| 000       | 0      | х       | MFIOFS = 0, HFIOFS = 0 and clock source is LF-INTOSC |

| 000       | 1      | 0       | MFIOFS = 0, HFIOFS = 1 and clock source is HF-INTOSC |

| 000       | 1      | 1       | MFIOFS = 1, HFIOFS = 0 and clock source is MF-INTOSC |

| Non-Zero  | x      | 0       | MFIOFS = 0, HFIOFS = 1 and clock source is HF-INTOSC |

| Non-Zero  | x      | 1       | MFIOFS = 1, HFIOFS = 0 and clock source is MF-INTOSC |

## TABLE 4-3: INTERNAL OSCILLATOR FREQUENCY STABILITY BITS

Clocks to the device continue while the INTOSC source stabilizes after an interval of TIOBST (Parameter 39, Table 31-11).

If the IRCFx bits were previously at a non-zero value, or if INTSRC was set before setting SCS1 and the INTOSC source was already stable, the HFIOFS or MFIOFS bit will remain set. On transitions from RC\_RUN mode to PRI\_RUN mode, the device continues to be clocked from the INTOSC multiplexer while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 4-4). When the clock switch is complete, the HFIOFS or MFIOFS bit is cleared, the OSTS bit is set and the primary clock is providing the device clock. The IDLEN and SCSx bits are not affected by the switch. The LF-INTOSC source will continue to run if either the WDT or the Fail-Safe Clock Monitor (FSCM) is enabled.

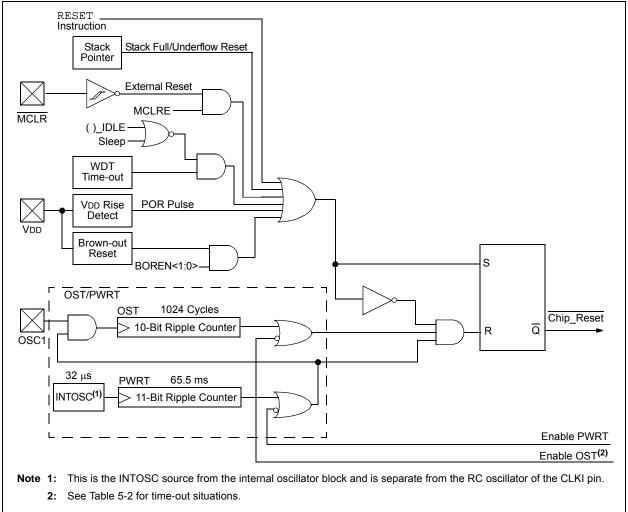

# 5.0 RESET

The PIC18F66K80 family devices differentiate between various kinds of Reset:

- a) Power-on Reset (POR)

- b) MCLR Reset during Normal Operation

- c) MCLR Reset during Power-Managed modes

- d) Watchdog Timer (WDT) Reset (during execution)

- e) Configuration Mismatch (CM) Reset

- f) Programmable Brown-out Reset (BOR)

- g) RESET Instruction

- h) Stack Full Reset

- i) Stack Underflow Reset

This section discusses Resets generated by MCLR, POR and BOR, and covers the operation of the various start-up timers. Stack Reset events are covered in Section 6.1.3.4 "Stack Full and Underflow Resets". WDT Resets are covered in Section 28.2 "Watchdog Timer (WDT)". A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 5-1.

# 5.1 RCON Register

Device Reset events are tracked through the RCON register (Register 5-1). The lower five bits of the register indicate that a specific Reset event has occurred. In most cases, these bits can only be cleared by the event and must be set by the application after the event. The state of these flag bits, taken together, can be read to indicate the type of Reset that just occurred. This is described in more detail in **Section 5.7** "**Reset State of Registers**".

The RCON register also has control bits for setting interrupt priority (IPEN) and software control of the BOR (SBOREN). Interrupt priority is discussed in **Section 10.0 "Interrupts"**. BOR is covered in **Section 5.4 "Brown-out Reset (BOR)"**.

# FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

| TABLE 5-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |                    |             |                                          |                                                                  |                                    |                      |  |  |  |

|--------------------------------------------------------------------|--------------------|-------------|------------------------------------------|------------------------------------------------------------------|------------------------------------|----------------------|--|--|--|

| Register                                                           | Applicable Devices |             | Power-on<br>Reset,<br>Brown-out<br>Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via<br>WDT<br>or Interrupt |                      |  |  |  |

| CCPTMRS                                                            | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | 0 0000                                                           | x xxxx                             | u uuuu               |  |  |  |

| TRISG                                                              | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | 1 1111                                                           | 1 1111                             | u uuuu               |  |  |  |

| TRISF                                                              | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | 1111 1111                                                        | 1111 1111                          | uuuu uuuu            |  |  |  |

| TRISE                                                              | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | 1111 -111                                                        | 1111 -111                          | uuuu -uuu            |  |  |  |

| TRISD                                                              | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | 1111 1111                                                        | 1111 1111                          | uuuu uuuu            |  |  |  |

| TRISC                                                              | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | 1111 1111                                                        | 1111 1111                          | uuuu uuuu            |  |  |  |

| TRISB                                                              | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | 1111 1111                                                        | 1111 1111                          | uuuu uuuu            |  |  |  |

| TRISA <sup>(5)</sup>                                               | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | 111- 1111 <b>(5)</b>                                             | 111- 1111 <b>(5)</b>               | uuu- uuuu <b>(5)</b> |  |  |  |

| ODCON                                                              | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | 0000 0000                                                        | 0000 0000                          | uuuu uuuu            |  |  |  |

| SLRCON                                                             | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | -000 0000                                                        | -111 1111                          | -111 1111            |  |  |  |

| LATG                                                               | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | x xxxx                                                           | x xxxx                             | u uuuu               |  |  |  |

| LATF                                                               | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | xxxx xxxx                                                        | xxxx -xxx                          | uuuu -uuu            |  |  |  |

| LATE                                                               | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | xxxx -xxx                                                        | xxxx xxxx                          | uuuu uuuu            |  |  |  |

| LATD                                                               | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | xxxx xxxx                                                        | xxxx xxxx                          | uuuu uuuu            |  |  |  |

| LATC                                                               | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | xxxx xxxx                                                        | xxxx xxxx                          | uuuu uuuu            |  |  |  |

| LATB                                                               | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | xxxx xxxx                                                        | xxxx xxxx                          | uuuu uuuu            |  |  |  |

| LATA <sup>(5)</sup>                                                | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | xxx- xxxx <sup>(5)</sup>                                         | xxx- xxxx(5)                       | uuu- uuuu <b>(5)</b> |  |  |  |

| T4CON                                                              | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | -000 0000                                                        | -000 0000                          | -uuu uuuu            |  |  |  |

| TMR4                                                               | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | 0000 0000                                                        | 0000 0000                          | uuuu uuuu            |  |  |  |

| PORTG                                                              | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | x xxxx                                                           | x xxxx                             | u uuuu               |  |  |  |

| PORTF                                                              | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | xxxx xxxx                                                        | xxxx xxxx                          | uuuu uuuu            |  |  |  |

| PORTE                                                              | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | xxxx xxxx                                                        | XXXX XXXX                          | uuuu uuuu            |  |  |  |

| PORTD                                                              | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | xxxx xxxx                                                        | XXXX XXXX                          | uuuu uuuu            |  |  |  |

| PORTC                                                              | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | xxxx xxxx                                                        | xxxx xxxx                          | uuuu uuuu            |  |  |  |

| PORTB                                                              | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | xxxx xxxx                                                        | xxxx xxxx                          | uuuu uuuu            |  |  |  |

| PORTA <sup>(5)</sup>                                               | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | xxx- xxxx <sup>(5)</sup>                                         | xxx- xxxx <sup>(5)</sup>           | uuu- uuuu <b>(5)</b> |  |  |  |

| EECON1                                                             | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | xx-0 x000                                                        | uu-0 u000                          | uu-u uuuu            |  |  |  |

| EECON2                                                             | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | 0000 0000                                                        | 0000 0000                          | uuuu uuuu            |  |  |  |

| SPBRGH1                                                            | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | 0000 0000                                                        | 0000 0000                          | uuuu uuuu            |  |  |  |

| SPBRGH2                                                            | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | 0000 0000                                                        | 0000 0000                          | uuuu uuuu            |  |  |  |

| SPBRG2                                                             | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | 0000 0000                                                        | 0000 0000                          | uuuu uuuu            |  |  |  |

| RCREG2                                                             | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | 0000 0000                                                        | 0000 0000                          | uuuu uuuu            |  |  |  |

| TXREG2                                                             | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | 0000 0000                                                        | 0000 0000                          | uuuu uuuu            |  |  |  |

| IPR5                                                               | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | 1111 1111                                                        | 1111 1111                          | uuuu uuuu            |  |  |  |

| PIR5                                                               | PIC18F2XK80        | PIC18F4XK80 | PIC18F6XK80                              | 0000 0000                                                        | 0000 0000                          | uuuu uuuu            |  |  |  |

# TABLE 5-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged; x = unknown; - = unimplemented bit, read as '0'; q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 5-3 for Reset value for specific conditions.

5: Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read as '0'.

| Addr. | File Name     | Bit 7                        | Bit 6                           | Bit 5           | Bit 4          | Bit 3          | Bit 2          | Bit 1           | Bit 0        | Value on<br>POR, BOR<br>on page |

|-------|---------------|------------------------------|---------------------------------|-----------------|----------------|----------------|----------------|-----------------|--------------|---------------------------------|

| FFFh  | TOSU          | —                            | —                               | —               | Top-of-Stack   | Upper Byte (T  | OS<20:16>)     |                 |              | 88                              |

| FFEh  | TOSH          | Top-of-Stack                 | High Byte (TC                   | S<15:8>)        | •              |                |                |                 |              | 88                              |

| FFDh  | TOSL          | Top-of-Stack                 | Low Byte (TO                    | S<7:0>)         |                |                |                |                 |              | 88                              |

| FFCh  | STKPTR        | STKFUL                       | STKUNF                          | —               | SP4            | SP3            | SP2            | SP1             | SP0          | 88                              |

| FFBh  | PCLATU        | _                            | _                               | Bit 21          | Holding Regi   | ster for PC<20 | ):16>          |                 |              | 88                              |

| FFAh  | PCLATH        | Holding Regi                 | ster for PC<15                  | 5:8>            |                |                |                |                 |              | 88                              |

| FF9h  | PCL           | PC Low Byte                  | (PC<7:0>)                       |                 |                |                |                |                 |              | 88                              |

| FF8h  | TBLPTRU       | —                            | _                               | Bit 21          | Program Mer    | mory Table Po  | inter Upper By | /te (TBLPTR<    | 20:16>)      | 88                              |

| FF7h  | TBLPTRH       | Program Mer                  | nory Table Po                   | inter High Byte | (TBLPTR<15     | :8>)           |                |                 |              | 88                              |

| FF6h  | TBLPTRL       | Program Mer                  | nory Table Po                   | inter Low Byte  | (TBLPTR<7:0    | >)             |                |                 |              | 88                              |

| FF5h  | TABLAT        | Program Mer                  | nory Table Lat                  | ch              |                |                |                |                 |              | 88                              |

| FF4h  | PRODH         | Product Regi                 | ster High Byte                  |                 |                |                |                |                 |              | 88                              |

| FF3h  | PRODL         | Product Regi                 | ster Low Byte                   |                 |                |                |                |                 |              | 88                              |

| FF2h  | INTCON        | GIE/GIEH                     | PEIE/GIEL                       | TMR0IE          | <b>INTOIE</b>  | RBIE           | TMR0IF         | <b>INT0IF</b>   | RBIF         | 88                              |

| FF1h  | INTCON2       | RBPU                         | INTEDG0                         | INTEDG1         | INTEDG2        | INTEDG3        | TMR0IP         | INT3IP          | RBIP         | 88                              |

| FF0h  | INTCON3       | INT2IP                       | INT1IP                          | INT3IE          | INT2IE         | INT1IE         | INT3IF         | INT2IF          | INT1IF       | 88                              |

| FEFh  | INDF0         | Uses content                 | s of FSR0 to a                  | address data m  | emory – value  | e of FSR0 not  | changed (not   | a physical regi | ister)       | 88                              |

| FEEh  | POSTINC0      | Uses content                 | s of FSR0 to a                  | address data m  | emory – value  | e of FSR0 post | t-incremented  | (not a physica  | l register)  | 88                              |

| FEDh  | POSTDEC0      | Uses content                 | s of FSR0 to a                  | address data m  | emory – value  | e of FSR0 post | t-decremented  | I (not a physic | al register) | 88                              |

| FECh  | PREINC0       | Uses content                 | s of FSR0 to a                  | address data m  | emory – value  | e of FSR0 pre- | incremented (  | not a physical  | register)    | 88                              |

| FEBh  | PLUSW0        | Uses content<br>value of FSR |                                 | address data m  | emory – value  | e of FSR0 pre- | incremented (  | not a physical  | register) –  | 88                              |

| FEAh  | FSR0H         | _                            | —                               | —               | _              | Indirect Data  | Memory Addr    | ess Pointer 0   | High Byte    | 88                              |

| FE9h  | FSR0L         | Indirect Data                | Memory Addr                     | ess Pointer 0 L | ow Byte        |                |                |                 |              | 88                              |

| FE8h  | WREG          | Working Reg                  | ister                           |                 |                |                |                |                 |              | 88                              |

| FE7h  | INDF1         | Uses content                 | s of FSR1 to a                  | address data m  | emory – value  | of FSR1 not    | changed (not   | a physical reg  | ister)       | 88                              |

| FE6h  | POSTINC1      | Uses content                 | s of FSR1 to a                  | address data m  | emory – value  | e of FSR1 post | t-incremented  | (not a physica  | l register)  | 88                              |

| FE5h  | POSTDEC1      | Uses content                 | s of FSR1 to a                  | address data m  | emory – value  | e of FSR1 post | t-decremented  | l (not a physic | al register) | 88                              |

| FE4h  | PREINC1       | Uses content                 | s of FSR1 to a                  | address data m  | emory – value  | of FSR1 pre-   | incremented (  | not a physical  | register)    | 88                              |

| FE3h  | PLUSW1        | Uses content<br>value of FSR |                                 | address data m  | emory – value  | e of FSR1 pre- | incremented (  | not a physical  | register) –  | 88                              |

| FE2h  | FSR1H         | _                            | _                               | _               | _              | Indirect Data  | Memory Addr    | ess Pointer 1   | High Byte    | 88                              |

| FE1h  | FSR1L         | Indirect Data                | Memory Addr                     | ess Pointer 1 L | ow Byte        |                |                |                 |              | 88                              |

| FE0h  | BSR           | _                            | _                               | _               | _              | Bank Select    | Register       |                 |              | 88                              |

| FDFh  | INDF2         | Uses content                 | s of FSR2 to a                  | address data m  | iemory – value | e of FSR2 not  | changed (not   | a physical reg  | ister)       | 88                              |

| FDEh  | POSTINC2      | Uses content                 | s of FSR2 to a                  | address data m  | emory – value  | e of FSR2 post | t-incremented  | (not a physica  | l register)  | 89                              |

| FDDh  | POSTDEC2      | Uses content                 | s of FSR2 to a                  | address data m  | emory – value  | e of FSR2 post | t-decremented  | l (not a physic | al register) | 89                              |

| FDCh  | PREINC2       | Uses content                 | s of FSR2 to a                  | address data m  | iemory – value | e of FSR2 pre- | incremented (  | not a physical  | register)    | 89                              |

| FDBh  | PLUSW2        |                              | s of FSR2 to a<br>2 offset by W | address data m  | iemory – value | e of FSR2 pre- | incremented (  | not a physical  | register) –  | 89                              |

| FDAh  | FSR2H         | _                            | _                               | _               | _              | Indirect Data  | Memory Addr    | ess Pointer 2   | High Byte    | 89                              |

| FD9h  | FSR2L         | Indirect Data                | Memory Addr                     | ess Pointer 2 L | ow Byte        |                |                |                 |              | 89                              |

| FD8h  | STATUS        |                              | —                               | _               | Ν              | OV             | Z              | DC              | С            | 89                              |

| FD7h  | TMR0H         | Timer0 Regis                 | ter High Byte                   |                 |                |                |                |                 |              | 89                              |

| FD6h  | TMR0L         | Timer0 Regis                 | ter Low Byte                    |                 |                |                |                |                 |              | 89                              |

| FD5h  | TOCON         | TMR0ON                       | T08BIT                          | TOCS            | TOSE           | PSA            | T0PS2          | T0PS1           | T0PS0        | 89                              |

| FD4h  | Unimplemented |                              |                                 |                 |                |                |                |                 |              | _                               |

| FD3h  | OSCCON        | IDLEN                        | IRCF2                           | IRCF1           | IRCF0          | OSTS           | HFIOFS         | SCS1            | SCS0         | 89                              |

| FD2h  | OSCCON2       | —                            | SOSCRUN                         | —               | SOSCDRV        | SOSCGO         | —              | MFIOFS          | MFIOSEL      | 89                              |

| FD1h  | WDTCON        | REGSLP                       | _                               | ULPLVL          | SRETEN         | —              | ULPEN          | ULPSINK         | SWDTEN       | 89                              |

|       |               | 1                            |                                 | CM              | RI             | TO             | PD             | POR             | BOR          | +                               |

| TABLE 6-2: | PIC18F66K80 FAMILY REGISTER FILE SUMMARY |

|------------|------------------------------------------|

|            |                                          |

# 10.5 RCON Register

The RCON register contains bits used to determine the cause of the last Reset or wake-up from Idle or Sleep modes. RCON also contains the bit that enables interrupt priorities (IPEN).

## REGISTER 10-19: RCON: RESET CONTROL REGISTER

| R/W-0 | R/W-1  | R/W-1 | R/W-1 | R-1 | R-1 | R/W-0 | R/W-0 |

|-------|--------|-------|-------|-----|-----|-------|-------|

| IPEN  | SBOREN | CM    | RI    | TO  | PD  | POR   | BOR   |

| bit 7 |        |       |       |     |     |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | IPEN: Interrupt Priority Enable bit                                                         |

|-------|---------------------------------------------------------------------------------------------|

|       | 1 = Enables priority levels on interrupts                                                   |

|       | <ul><li>0 = Disables priority levels on interrupts (PIC16CXXX Compatibility mode)</li></ul> |

| bit 6 | SBOREN: Software BOR Enable bit                                                             |

|       | For details of bit operation, see Register 5-1.                                             |

| bit 5 | CM: Configuration Mismatch Flag bit                                                         |

|       | 1 = A Configuration Mismatch Reset has not occurred                                         |

|       | 0 = A Configuration Mismatch Reset has occurred (must be subsequently set in software)      |

| bit 4 | RI: RESET Instruction Flag bit                                                              |

|       | For details of bit operation, see Register 5-1.                                             |

| bit 3 | TO: Watchdog Timer Time-out Flag bit                                                        |

|       | For details of bit operation, see Register 5-1.                                             |

| bit 2 | PD: Power-Down Detection Flag bit                                                           |

|       | For details of bit operation, see Register 5-1.                                             |

| bit 1 | POR: Power-on Reset Status bit                                                              |

|       | For details of bit operation, see Register 5-1.                                             |

| bit 0 | BOR: Brown-out Reset Status bit                                                             |

|       | For details of bit operation, see Register 5-1.                                             |

|       |                                                                                             |

# **19.1 CCP Module Configuration**

Each Capture/Compare/PWM module is associated with a control register (generically, CCPxCON) and a data register (CCPRx). The data register, in turn, is comprised of two 8-bit registers: CCPRxL (low byte) and CCPRxH (high byte). All registers are both readable and writable.

#### 19.1.1 CCP MODULES AND TIMER RESOURCES

The CCP modules utilize Timers, 1 through 4, varying with the selected mode. Various timers are available to the CCP modules in Capture, Compare or PWM modes, as shown in Table 19-1.

#### TABLE 19-1: CCP MODE – TIMER RESOURCE

| CCP Mode | Timer Resource   |

|----------|------------------|

| Capture  | Timer1 or Timer3 |

| Compare  | Timer of Timers  |

| PWM      | Timer2 or Timer4 |

The assignment of a particular timer to a module is determined by the Timer to CCP enable bits in the CCPTMRS register (see Register 19-2). All of the modules may be active at once and may share the same timer resource if they are configured to operate in the same mode (Capture/Compare or PWM) at the same time.

The CCPTMRS register selects the timers for CCP modules, 2, 3, 4 and 5. The possible configurations are shown in Table 19-2.

# TABLE 19-2: TIMER ASSIGNMENTS FOR CCP MODULES 2, 3, 4 AND 5

|           | CCPTMRS Register            |             |        |                             |      |      |      |             |        |                             |             |  |  |  |

|-----------|-----------------------------|-------------|--------|-----------------------------|------|------|------|-------------|--------|-----------------------------|-------------|--|--|--|

| CCP2 CCP3 |                             |             |        |                             |      | CCP4 |      |             |        | CCP5                        |             |  |  |  |

| C2TSEL    | Capture/<br>Compare<br>Mode | PWM<br>Mode | C3TSEL | Capture/<br>Compare<br>Mode |      |      |      | PWM<br>Mode | C5TSEL | Capture/<br>Compare<br>Mode | PWM<br>Mode |  |  |  |

| 0         | TMR1                        | TMR2        | 0      | TMR1                        | TMR2 | 0    | TMR1 | TMR2        | 0 0    | TMR1                        | TMR2        |  |  |  |

| 1         | TMR3                        | TMR4        | 1      | TMR3                        | TMR4 | 1    | TMR3 | TMR4        | 0 1    | TMR3                        | TMR4        |  |  |  |

## 19.1.2 OPEN-DRAIN OUTPUT OPTION

When operating in Output mode (the Compare or PWM modes), the drivers for the CCPx pins can be optionally configured as open-drain outputs. This feature allows the voltage level on the pin to be pulled to a higher level through an external pull-up resistor and allows the output to communicate with external circuits without the need for additional level shifters.

The open-drain output option is controlled by the CCPxOD bits (ODCON<6:2>). Setting the appropriate bit configures the pin for the corresponding module for open-drain operation.

#### 21.3.4 **ENABLING SPI I/O**

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON1<5>), must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, reinitialize the SSPCON registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- · SDI is automatically controlled by the SPI module

- SDO must have the TRISC<5> bit cleared

- SCK (Master mode) must have the TRISC<3> bit cleared

- SCK (Slave mode) must have the TRISC<3> bit set

- SS must have the TRISA<5> bit set

Any serial port function that is not desired may be overridden by programming the corresponding Data Direction (TRIS) register to the opposite value.

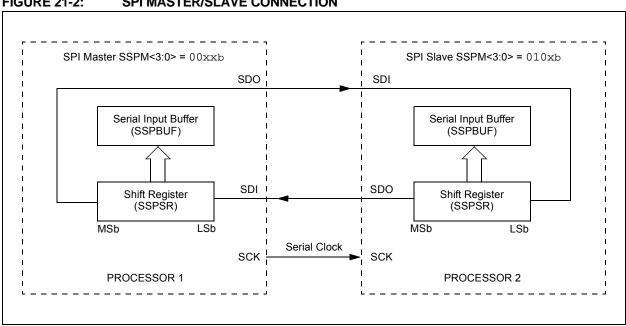

#### 21.3.5 TYPICAL CONNECTION

Figure 21-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- · Master sends data Slave sends dummy data

- Master sends data Slave sends data

- · Master sends dummy data Slave sends data

#### **FIGURE 21-2:** SPI MASTER/SLAVE CONNECTION

| <b>IGURE 21-5:</b>             | SPI N             | IODE W      | AVEFO                                              | RM (SLA       | VE MO                     | DE WITH | CKE =            | 0)                                    |                   |                                              |                 |

|--------------------------------|-------------------|-------------|----------------------------------------------------|---------------|---------------------------|---------|------------------|---------------------------------------|-------------------|----------------------------------------------|-----------------|

| <br>SS<br>Opilonsi             | ( .               |             |                                                    |               |                           |         |                  |                                       |                   |                                              |                 |

| 80%<br>{CKP = 0<br>CXE = 0}    | :<br>:<br>:<br>:X |             | ,<br>                                              | ·             | ·                         |         |                  |                                       |                   | ·<br>·                                       | :<br>:<br>:<br> |

| - VAR 20)<br>- ROR             | ·<br>·            | :<br>:<br>: | (<br>(<br>() () () () () () () () () () () () () ( | ,<br>,<br>, , | ;<br>;<br>; , ,           |         | (<br>(<br>(      | ;<br>;<br>;                           | 2<br>2<br>3       | ,<br>,<br>,                                  |                 |

| 2508<br>(CRE = 5<br>(CRE = 5)  | 2<br>5<br>5       |             |                                                    |               |                           |         |                  | · · · · · · · · · · · · · · · · · · · |                   |                                              |                 |

| Verlie en<br>Sisteration       |                   |             | 5<br>2<br>7<br>7                                   | :<br>d        | *<br>\$******<br>\$<br>\$ |         | 5<br>2<br>7<br>7 | :<br>::<br>:<br>:                     | *<br>.5<br>1<br>1 | :<br>:                                       | ,<br>           |

| \$6 <b>x</b> 3                 |                   | Kana ta     |                                                    | N 88.8        |                           | X68.3   | X 88.0           |                                       |                   |                                              |                 |

| SD:<br>(S3:82 = 33)            |                   |             |                                                    |               |                           |         |                  |                                       |                   | Mygeeneerine<br>E C                          | :<br>:<br>:     |

| ingasi<br>Serrecia             | ·<br>·<br>·       |             |                                                    | . 4.          |                           | <i></i> |                  | :<br>. <i>B</i> e                     | :<br>:<br>:       | 49.                                          |                 |

| (3367 = 6)                     |                   |             |                                                    | *<br>*        | ,<br>,<br>,               |         | 5<br>2<br>5      |                                       | * :<br>* :        | :<br>:<br>:///////////////////////////////// |                 |

| - S-SPHF<br>Britanupî<br>Filag | ;<br>;<br>;<br>;  |             | s<br>2<br>2                                        | :<br>:<br>:   | <<br>;<br>;<br>;          |         | 5<br>2<br>2<br>2 | :<br>:<br>::                          |                   | ilia<br>A Stend Col                          | . Produce       |

| 355 <b>0</b> 355 65            | 2<br>1            | *<br>:      |                                                    | ;<br>,        | :                         |         | i<br>i           | ;<br>,                                |                   | ) († Next Ox<br>Fritter Ox                   |                 |

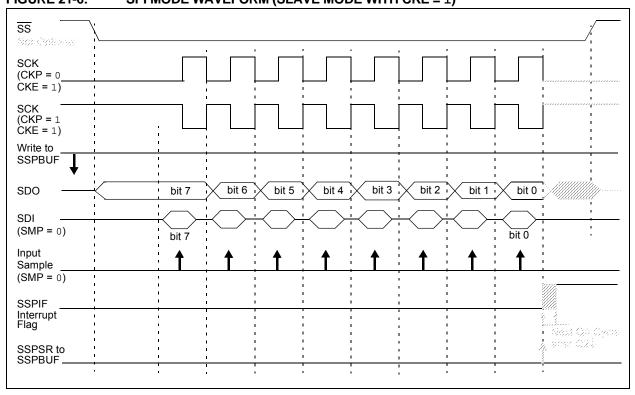

# FIGURE 21-6: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

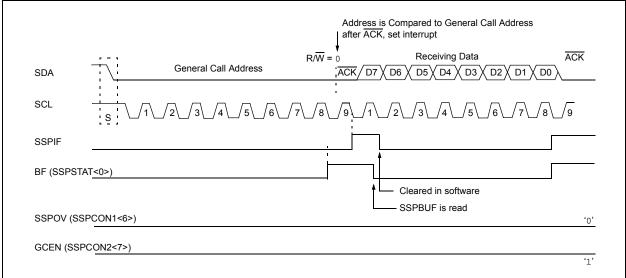

### 21.4.5 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all '0's with R/W = 0.

The general call address is recognized when the General Call Enable bit, GCEN, is enabled (SSPCON2<7> set). Following a Start bit detect, eight bits are shifted into the SSPSR and the address is compared against the SSPADD. It is also compared to the general call address and fixed in hardware.

If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF flag bit is set (eighth bit), and on the falling edge of the ninth bit (ACK bit), the SSPIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF. The value can be used to determine if the address was device-specific or a general call address.

In 10-Bit Addressing mode, the SSPADD is required to be updated for the second half of the address to match and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when the GCEN bit is set, while the slave is configured in 10-Bit Addressing mode, then the second half of the address is not necessary, the UA bit will not be set and the slave will begin receiving data after the Acknowledge (Figure 21-17).

# 27.0 ECAN MODULE

PIC18F66K80 family devices contain an Enhanced Controller Area Network (ECAN) module. The ECAN module is fully backward compatible with the CAN module available in PIC18CXX8 and PIC18FXX8 devices and the ECAN module in PIC18Fxx80 devices.

The Controller Area Network (CAN) module is a serial interface which is useful for communicating with other peripherals or microcontroller devices. This interface, or protocol, was designed to allow communications within noisy environments.

The ECAN module is a communication controller, implementing the CAN 2.0A or B protocol as defined in the BOSCH specification. The module will support CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system; however, the CAN specification is not covered within this data sheet. Refer to the BOSCH CAN specification for further details.

The module features are as follows:

- Implementation of the CAN protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- DeviceNet<sup>™</sup> data bytes filter support

- · Standard and extended data frames

- 0-8 bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Fully backward compatible with the PIC18XXX8 CAN module

- · Three modes of operation:

- Mode 0 Legacy mode

- Mode 1 Enhanced Legacy mode with DeviceNet support

- Mode 2 FIFO mode with DeviceNet support

- Support for remote frames with automated handling

Double-buffered receiver with two prioritized

- received message storage buffers

- Six buffers programmable as RX and TX message buffers

- 16 full (standard/extended identifier) acceptance filters that can be linked to one of four masks

- Two full acceptance filter masks that can be assigned to any filter

- One full acceptance filter that can be used as either an acceptance filter or acceptance filter mask

- Three dedicated transmit buffers with application specified prioritization and abort capability

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- · Programmable clock source

- Programmable link to timer module for time-stamping and network synchronization

- Low-power Sleep mode

# 27.1 Module Overview

The CAN bus module consists of a protocol engine and message buffering and control. The CAN protocol engine automatically handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the two receive registers.

The CAN module supports the following frame types:

- Standard Data Frame

- Extended Data Frame

- Remote Frame

- Error Frame

- Overload Frame Reception

The CAN module uses the RB2/CANTX and RB3/ CANRX pins to interface with the CAN bus. The CANTX and CANRX pins can be placed on alternate I/O pins by setting the CANMX (CONFIG3H<0>) Configuration bit.

For the PIC18F2XK80 and PIC18F4XK80, the alternate pin locations are RC6/CANTX and RC7/CANRX. For the PIC18F6XK80, the alternate pin locations are RE4/CANRX and RE5/CANTX.

In normal mode, the CAN module automatically overrides the appropriate TRIS bit for CANTX. The user must ensure that the appropriate TRIS bit for CANRX is set.

## 27.1.1 MODULE FUNCTIONALITY

The CAN bus module consists of a protocol engine, message buffering and control (see Figure 27-1). The protocol engine can best be understood by defining the types of data frames to be transmitted and received by the module.

The following sequence illustrates the necessary initialization steps before the ECAN module can be used to transmit or receive a message. Steps can be added or removed depending on the requirements of the application.

- 1. Initial LAT and TRIS bits for RX and TX CAN.

- 2. Ensure that the ECAN module is in Configuration mode.

- 3. Select ECAN Operational mode.

- 4. Set up the Baud Rate registers.

- 5. Set up the Filter and Mask registers.

- 6. Set the ECAN module to normal mode or any other mode required by the application logic.

# REGISTER 27-23: BnCON: TX/RX BUFFER 'n' CONTROL REGISTERS IN TRANSMIT MODE $[0 \le n \le 5, TXnEN (BSEL0<n>) = 1]^{(1)}$

| R/W-0               | ) R-0                                                                           | R-0                                                    | R-0                                            | R/W-0                           | R/W-0                    | R/W-0                 | R/W-0                 |

|---------------------|---------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------|---------------------------------|--------------------------|-----------------------|-----------------------|

| TXBIF <sup>(</sup>  |                                                                                 | TXLARB <sup>(3)</sup>                                  | TXERR <sup>(3)</sup>                           | TXREQ <sup>(2,4)</sup>          | RTREN                    | TXPRI1 <sup>(5)</sup> | TXPRI0 <sup>(5)</sup> |

| bit 7               |                                                                                 |                                                        |                                                |                                 |                          |                       | bit C                 |

| Legend:             |                                                                                 |                                                        |                                                |                                 |                          |                       |                       |

| R = Read            | able bit                                                                        | W = Writable                                           | bit                                            | U = Unimplen                    | nented bit, read         | d as '0'              |                       |

| -n = Value          | e at POR                                                                        | '1' = Bit is set                                       |                                                | '0' = Bit is clea               | ared                     | x = Bit is unkr       | nown                  |

| bit 7               | TXBIF: Trans                                                                    | mit Buffer Inter                                       | rupt Flag bit <sup>(3</sup>                    | )                               |                          |                       |                       |

|                     |                                                                                 | ge was success<br>age was transm                       |                                                | ed                              |                          |                       |                       |

| bit 6               | 1 = Message                                                                     | smission Aborto<br>was aborted<br>was not aborte       |                                                | 3)                              |                          |                       |                       |

| bit 5               | 1 = Message                                                                     | ansmission Los<br>lost arbitration<br>did not lose arl | while being s                                  | ent                             |                          |                       |                       |

| bit 4               | 1 = A bus err                                                                   | ismission Error<br>or occurred wh<br>or did not occu   | ile the messag                                 | ge was being s                  |                          |                       |                       |

| bit 3               | <b>TXREQ:</b> Trar<br>1 = Requests                                              | nsmit Request S<br>sending a mes<br>cally cleared wh   | Status bit <sup>(2,4)</sup><br>ssage; clears t | the TXABT, TX                   | LARB and TXE             | ERR bits              |                       |

| bit 2               | <b>RTREN:</b> Auto<br>1 = When a r                                              | omatic Remote                                          | Transmission<br>sion request i                 | Request Enab<br>is received, TX | le bit<br>REQ will be au | itomatically set      |                       |

| bit 1-0             | <b>TXPRI&lt;1:0&gt;:</b><br>11 = Priority  <br>10 = Priority  <br>01 = Priority | Transmit Prior<br>Level 3 (highes<br>Level 2           | ty bits <sup>(5)</sup><br>t priority)          |                                 |                          |                       |                       |

| Note 1:<br>2:<br>3: | These registers ar<br>Clearing this bit in<br>This bit is automat               | software while<br>ically cleared w                     | the bit is set v<br>hen TXREQ i                | will request a m<br>is set.     | C C                      |                       |                       |

4: While TXREQ is set or a transmission is in progress, Transmit Buffer registers remain read-only.

5: These bits set the order in which the Transmit Buffer register will be transferred. They do not alter the CAN message identifier.

# **REGISTER 27-59: TXBIE: TRANSMIT BUFFERS INTERRUPT ENABLE REGISTER<sup>(1)</sup>**

| U-0   | U-0 | U-0 | R/W-0                 | R/W-0                                              | R/W-0 | U-0 | U-0   |

|-------|-----|-----|-----------------------|----------------------------------------------------|-------|-----|-------|

| —     | —   |     | TXB2IE <sup>(2)</sup> | TXB2IE <sup>(2)</sup> TXB1IE <sup>(2)</sup> TXB0II |       |     | —     |

| bit 7 |     |     |                       |                                                    |       |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | Unimplemented: Read as '0'                                                                                      |

|---------|-----------------------------------------------------------------------------------------------------------------|

| bit 4-2 | TXB2IE:TXB0IE: Transmit Buffer 2-0 Interrupt Enable bits <sup>(2)</sup>                                         |

|         | <ul> <li>1 = Transmit buffer interrupt is enabled</li> <li>0 = Transmit buffer interrupt is disabled</li> </ul> |

| bit 1-0 | Unimplemented: Read as '0'                                                                                      |

**Note 1:** This register is available in Mode 1 and 2 only.

**2:** TXBnIE in PIE5 register must be set to get an interrupt.

# **REGISTER 27-60: BIE0: BUFFER INTERRUPT ENABLE REGISTER 0<sup>(1)</sup>**

| R/W-0                 | R/W-0                 |

|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|-----------------------|-----------------------|

| B5IE <sup>(2)</sup> | B4IE <sup>(2)</sup> | B3IE <sup>(2)</sup> | B2IE <sup>(2)</sup> | B1IE <sup>(2)</sup> | B0IE <sup>(2)</sup> | RXB1IE <sup>(2)</sup> | RXB0IE <sup>(2)</sup> |

| bit 7               |                     |                     |                     |                     |                     |                       | bit 0                 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-2 B<5:0>IE: Programmable Transmit/Receive Buffer 5-0 Interrupt Enable bits<sup>(2)</sup>

| 1 = | Interrupt is enabled |  |

|-----|----------------------|--|

| -   |                      |  |

0 = Interrupt is disabled

bit 1-0 RXB<1:0>IE: Dedicated Receive Buffer 1-0 Interrupt Enable bits<sup>(2)</sup>

- 1 = Interrupt is enabled

- 0 = Interrupt is disabled

Note 1: This register is available in Mode 1 and 2 only.

2: Either TXBnIE or RXBnIE, in the PIE5 register, must be set to get an interrupt.

NOTES:

| R/C-1                                     | R/C-1         | U-0              | U-0                 | U-0                                     | U-0 | U-0 | U-0   |  |

|-------------------------------------------|---------------|------------------|---------------------|-----------------------------------------|-----|-----|-------|--|

| CPD                                       | CPB           | —                | _                   | —                                       | —   | _   | —     |  |

| bit 7                                     | L             |                  |                     |                                         |     |     | bit 0 |  |

|                                           |               |                  |                     |                                         |     |     |       |  |

| Legend:                                   |               | C = Clearable    | bit                 |                                         |     |     |       |  |

| R = Readable                              | e bit         | W = Writable     | bit                 | U = Unimplemented bit, read as '0'      |     |     |       |  |

| -n = Value at                             | POR           | '1' = Bit is set |                     | '0' = Bit is cleared x = Bit is unknown |     |     | nown  |  |

|                                           |               |                  |                     |                                         |     |     |       |  |

| bit 7                                     | CPD: Data El  | EPROM Code       | Protection bit      |                                         |     |     |       |  |

|                                           | 1 = Data EEF  | ROM is not co    | de-protected        |                                         |     |     |       |  |

|                                           | 0 = Data EEF  | PROM is code-p   | protected           |                                         |     |     |       |  |

| bit 6 CPB: Boot Block Code Protection bit |               |                  | ection bit          |                                         |     |     |       |  |

|                                           |               | k is not code-p  |                     |                                         |     |     |       |  |

|                                           | 0 = Boot bloc | k is code-prote  | cted <sup>(1)</sup> |                                         |     |     |       |  |

| bit 5-0                                   | Unimplemen    | ted: Read as '   | 0'                  |                                         |     |     |       |  |

# REGISTER 28-8: CONFIG5H: CONFIGURATION REGISTER 5 HIGH (BYTE ADDRESS 300009h)

Note 1: For the memory size of the blocks, see Figure 28-6. The boot block size changes with BBSIZ0.

# 30.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows<sup>®</sup> programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

# 30.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

# 30.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 31.1 DC Characteristics: Supply Voltage PIC18F66K80 Family (Industrial/Extended)

| PIC18F66K80 Family<br>(Industrial, Extended) |        |                                                                                                                                                       | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array} $ |                          |                              |             |                                                       |  |

|----------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------|-------------|-------------------------------------------------------|--|

| Param<br>No.                                 | Symbol | Characteristic                                                                                                                                        | Min                                                                                                                                                                                                                                                          | Тур                      | Мах                          | Units       | Conditions                                            |  |

| D001                                         | Vdd    | Supply Voltage                                                                                                                                        | 1.8<br>1.8                                                                                                                                                                                                                                                   |                          | 3.6<br>5.5                   | V<br>V      | For LF devices<br>For F devices                       |  |

| D001C                                        | AVdd   | Analog Supply Voltage                                                                                                                                 | VDD - 0.3                                                                                                                                                                                                                                                    |                          | VDD + 0.3                    | V           |                                                       |  |

| D001D                                        | AVss   | Analog Ground Potential                                                                                                                               | Vss – 0.3                                                                                                                                                                                                                                                    | _                        | Vss + 0.3                    | V           |                                                       |  |

| D002                                         | Vdr    | RAM Data Retention<br>Voltage <sup>(1)</sup>                                                                                                          | 1.5                                                                                                                                                                                                                                                          | _                        | —                            | V           |                                                       |  |

| D003                                         | Vpor   | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal                                                                                      | —                                                                                                                                                                                                                                                            | _                        | 0.7                          | V           | See Section 5.3 "Power-on<br>Reset (POR)" for details |  |

| D004                                         | Svdd   | <b>VDD Rise Rate</b><br>to Ensure Internal<br>Power-on Reset Signal                                                                                   | 0.05                                                                                                                                                                                                                                                         | _                        | _                            | V/ms        | See Section 5.3 "Power-on<br>Reset (POR)" for details |  |

| D005                                         | Bvdd   | Brown-out Reset Voltage<br>(High, Medium and<br>Low-Power mode<br>BORV<1:0> = 11 <sup>(2)</sup><br>BORV<1:0> = 10<br>BORV<1:0> = 01<br>BORV<1:0> = 00 | 1.69<br>1.88<br>2.53<br>2.82                                                                                                                                                                                                                                 | 1.8<br>2.0<br>2.7<br>3.0 | 1.91<br>2.12<br>2.86<br>3.18 | V<br>V<br>V |                                                       |  |

Note 1: This is the limit to which VDD can be lowered in Sleep mode, or during a device Reset, without losing RAM data.

2: Device will operate normally until Brown-out Reset occurs, even though VDD may be below VDDMIN.

# 31.2 DC Characteristics: Power-Down and Supply Current PIC18F66K80 Family (Industrial/Extended)

| PIC18F66K80 Family<br>(Industrial/Extended) |                    |                      | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |       |        |                    |  |  |  |

|---------------------------------------------|--------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|--------------------|--|--|--|

| Param<br>No.                                | Device             | Тур                  | Max                                                                                                                                                                                                                                                            | Units | Conc   | litions            |  |  |  |

|                                             | Power-Down Current | (IPD) <sup>(1)</sup> |                                                                                                                                                                                                                                                                |       |        |                    |  |  |  |

|                                             | PIC18LFXXK80       | 8                    | 400                                                                                                                                                                                                                                                            | nA    | -40°C  |                    |  |  |  |

|                                             |                    | 13                   | 500                                                                                                                                                                                                                                                            | nA    | +25°C  | VDD = 1.8V         |  |  |  |

|                                             |                    | 35                   | 750                                                                                                                                                                                                                                                            | nA    | +60°C  | (Sleep mode)       |  |  |  |

|                                             |                    | 218                  | 980                                                                                                                                                                                                                                                            | nA    | +85°C  | Regulator Disabled |  |  |  |

|                                             |                    | 3                    | 6                                                                                                                                                                                                                                                              | μA    | +125°C |                    |  |  |  |

|                                             | PIC18LFXXK80       | 14                   | 500                                                                                                                                                                                                                                                            | nA    | -40°C  |                    |  |  |  |

|                                             |                    | 34                   | 600                                                                                                                                                                                                                                                            | nA    | +25°C  | VDD = 3.3V         |  |  |  |