#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 64MHz                                                                     |

| Connectivity               | ECANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 35                                                                        |

| Program Memory Size        | 64KB (32K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.6K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x12b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f46k80-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| R/W-0           | R/W-0                                                | R/W-0                      | R/W-0                   | R/W-0                                             | R/W-0            | R/W-0           | R/W-0        |

|-----------------|------------------------------------------------------|----------------------------|-------------------------|---------------------------------------------------|------------------|-----------------|--------------|

| INTSRC          | PLLEN                                                | TUN5                       | TUN4                    | TUN3                                              | TUN2             | TUN1            | TUN0         |

| bit 7           |                                                      |                            |                         |                                                   |                  |                 | bit 0        |

| Legend:         |                                                      |                            |                         |                                                   |                  |                 |              |

| R = Readable    | bit                                                  | W = Writable               | bit                     | U = Unimpler                                      | nented bit, read | l as '0'        |              |

| -n = Value at I | POR                                                  | '1' = Bit is set           |                         | '0' = Bit is clea                                 |                  | x = Bit is unkn | iown         |

| bit 7           | 1 = 31.25 kH                                         | z device clock is          | derived from            | y Source Selec<br>16 MHz INTOSC<br>ITOSC 31 kHz ( | source (divide-  |                 | I, HF-INTOSC |

| bit 6           |                                                      | luency Multiplie<br>nabled |                         |                                                   | , ,              |                 |              |

| bit 5-0         | 011111 = Ma<br>•<br>0000001<br>000000 = Ce<br>111111 | aximum frequer<br>•<br>•   | ncy<br>; fast RC oscill | requency Tunir                                    | -                | d frequency     |              |

#### REGISTER 3-3: OSCTUNE: OSCILLATOR TUNING REGISTER

#### 3.6.3 INTERNAL OSCILLATOR OUTPUT FREQUENCY AND TUNING

The internal oscillator block is calibrated at the factory to produce an INTOSC output frequency of 16 MHz. It can be adjusted in the user's application by writing to TUN<5:0> (OSCTUNE<5:0>) in the OSCTUNE register (Register 3-3).

When the OSCTUNE register is modified, the INTOSC (HF-INTOSC and MF-INTOSC) frequency will begin shifting to the new frequency. The oscillator will require some time to stabilize. Code execution continues during this shift and there is no indication that the shift has occurred.

The LF-INTOSC oscillator operates independently of the HF-INTOSC or the MF-INTOSC source. Any changes in the HF-INTOSC or the MF-INTOSC source, across voltage and temperature, are not necessarily reflected by changes in LF-INTOSC or vice versa. The frequency of LF-INTOSC is not affected by OSCTUNE.

#### 3.6.4 INTOSC FREQUENCY DRIFT

The INTOSC frequency may drift as VDD or temperature changes and can affect the controller operation in a variety of ways. It is possible to adjust the INTOSC frequency by modifying the value in the OSCTUNE register. Depending on the device, this may have no effect on the LF-INTOSC clock source frequency.

Tuning INTOSC requires knowing when to make the adjustment, in which direction it should be made, and in some cases, how large a change is needed. Three compensation techniques are shown here.

### 3.6.4.1 Compensating with the EUSARTx

An adjustment may be required when the EUSARTx begins to generate framing errors or receives data with errors while in Asynchronous mode. Framing errors indicate that the device clock frequency is too high. To adjust for this, decrement the value in OSCTUNE to reduce the clock frequency. On the other hand, errors in data may suggest that the clock speed is too low. To compensate, increment OSCTUNE to increase the clock frequency.

### 3.6.4.2 Compensating with the Timers

This technique compares device clock speed to some reference clock. Two timers may be used; one timer is clocked by the peripheral clock, while the other is clocked by a fixed reference source, such as the SOSC oscillator.

Both timers are cleared, but the timer clocked by the reference generates interrupts. When an interrupt occurs, the internally clocked timer is read and both timers are cleared. If the internally clocked timer value is much greater than expected, then the internal oscillator block is running too fast. To adjust for this, decrement the OSCTUNE register.

### 3.6.4.3 Compensating with the CCP Module in Capture Mode

A CCP module can use free-running Timer1 (or Timer3), clocked by the internal oscillator block and an external event with a known period (i.e., AC power frequency). The time of the first event is captured in the CCPRxH:CCPRxL registers and is recorded for use later. When the second event causes a capture, the time of the first event is subtracted from the time of the second event. Since the period of the external event is known, the time difference between events can be calculated.

If the measured time is much greater than the calculated time, the internal oscillator block is running too fast. To compensate, decrement the OSCTUNE register. If the measured time is much less than the calculated time, the internal oscillator block is running too slow. To compensate, increment the OSCTUNE register.

### 3.7 Reference Clock Output

In addition to the Fosc/4 clock output, in certain oscillator modes, the device clock in the PIC18F66K80 family can also be configured to provide a reference clock output signal to a port pin. This feature is available in all oscillator configurations and allows the user to select a greater range of clock submultiples to drive external devices in the application.

This reference clock output is controlled by the REFOCON register (Register 3-4). Setting the ROON bit (REFOCON<7>) makes the clock signal available on the REFO (RC3) pin. The RODIV<3:0> bits enable the selection of 16 different clock divider options.

The ROSSLP and ROSEL bits (REFOCON<5:4>) control the availability of the reference output during Sleep mode. The ROSEL bit determines if the oscillator on OSC1 and OSC2, or the current system clock source, is used for the reference clock output. The ROSSLP bit determines if the reference source is available on RE3 when the device is in Sleep mode.

To use the reference clock output in Sleep mode, both the ROSSLP and ROSEL bits must be set. The device clock must also be configured for an EC or HS mode. If not, the oscillator on OSC1 and OSC2 will be powered down when the device enters Sleep mode. Clearing the ROSEL bit allows the reference output frequency to change as the system clock changes during any clock switches.

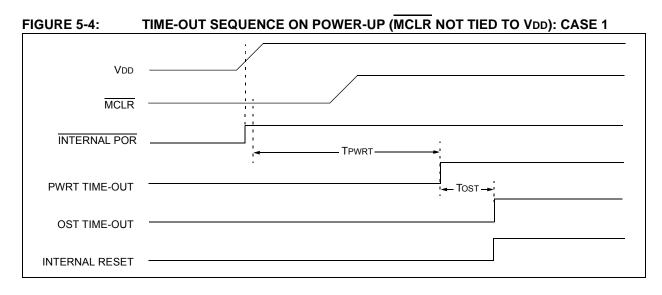

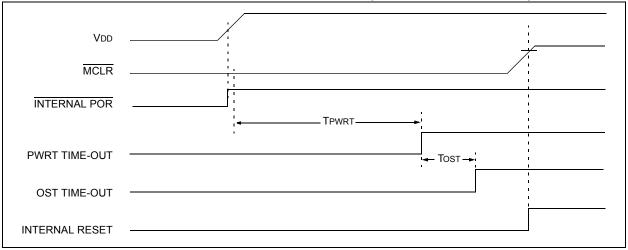

FIGURE 5-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

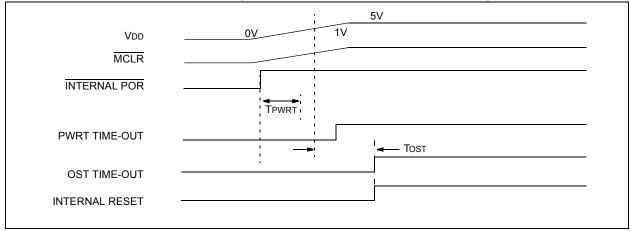

FIGURE 5-6: SLOW RISE TIME (MCLR TIED TO VDD, VDD RISE > TPWRT)

### 6.6 Data Memory and the Extended Instruction Set

Enabling the PIC18 extended instruction set (XINST Configuration bit = 1) significantly changes certain aspects of data memory and its addressing. Using the Access Bank for many of the core PIC18 instructions introduces a new addressing mode for the data memory space. This mode also alters the behavior of Indirect Addressing using FSR2 and its associated operands.

What does not change is just as important. The size of the data memory space is unchanged, as well as its linear addressing. The SFR map remains the same. Core PIC18 instructions can still operate in both Direct and Indirect Addressing mode. Inherent and literal instructions do not change at all. Indirect Addressing with FSR0 and FSR1 also remains unchanged.

#### 6.6.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of Indirect Addressing using the FSR2 register pair and its associated file operands. Under the proper conditions, instructions that use the Access Bank – that is, most bit-oriented and byte-oriented instructions – can invoke a form of Indexed Addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset or the Indexed Literal Offset mode.

When using the extended instruction set, this addressing mode requires the following:

- Use of the Access Bank ('a' = 0)

- A file address argument that is less than or equal to 5Fh

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in Direct Addressing) or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

#### 6.6.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use Direct Addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte-oriented and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte-oriented and bit-oriented instructions are not affected if they do not use the Access Bank (Access RAM bit = 1), or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled is shown in Figure 6-9.

Those who desire to use byte-oriented or bit-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 29.2.1** "Extended Instruction Syntax".

### FIGURE 6-9: COMPARING ADDRESSING OPTIONS FOR BIT-ORIENTED AND BYTE-ORIENTED INSTRUCTIONS (EXTENDED INSTRUCTION SET ENABLED)

**EXAMPLE INSTRUCTION:** ADDWF, f, d, a (Opcode: 0010 01da ffff ffff)

### When a = 0 and $f \ge 60h$ :

The instruction executes in Direct Forced mode. 'f' is interpreted as a location in the Access RAM between 060h and FFFh. This is the same as locations, F60h to FFFh, (Bank 15) of data memory.

Locations below 060h are not available in this addressing mode.

#### When a = 0 and $f \le 5Fh$ :

The instruction executes in Indexed Literal Offset mode. 'f' is interpreted as an offset to the address value in FSR2. The two are added together to obtain the address of the target register for the instruction. The address can be anywhere in the data memory space.

Note that in this mode, the correct syntax is now: ADDWF [k], d where 'k' is the same as 'f'.

#### When a = 1 (all values of f):

The instruction executes in Direct mode (also known as Direct Long mode). 'f' is interpreted as a location in one of the 16 banks of the data memory space. The bank is designated by the Bank Select Register (BSR). The address can be in any implemented bank in the data memory space.

### **10.0 INTERRUPTS**

Members of the PIC18F66K80 family of devices have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a high-priority level or a low-priority level. The high-priority interrupt vector is at 0008h and the low-priority interrupt vector is at 0018h. High-priority interrupt events will interrupt any low-priority interrupts that may be in progress.

The registers for controlling interrupt operation are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2, PIR3, PIR4 and PIR5

- PIE1, PIE2, PIE3, PIE4 and PIE5

- IPR1, IPR2, IPR3, IPR4 and IPR5

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit Indicating that an interrupt event occurred

- Enable bit Enabling program execution to branch to the interrupt vector address when the flag bit is set

- **Priority bit** Specifying high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits that enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate Global Interrupt Enable bit are set, the interrupt will vector immediately to address 0008h or 0018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit that enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit that enables/disables all interrupt sources. All interrupts branch to address 0008h in Compatibility mode.

When an interrupt is responded to, the Global Interrupt Enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a low-priority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine (ISR), the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used) that re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding enable bit or the GIE bit.

**Note:** Do not use the MOVFF instruction to modify any of the Interrupt Control registers while **any** interrupt is enabled. Doing so may cause erratic microcontroller behavior.

### REGISTER 10-13: PIE5: PERIPHERAL INTERRUPT ENABLE REGISTER 5

| R/W-0         | R/W-0                                | R/W-0             | R/W-0            | R/W-0            | R/W-0           | R/W-0           | R/W-0              |

|---------------|--------------------------------------|-------------------|------------------|------------------|-----------------|-----------------|--------------------|

| IRXIE         | WAKIE                                | ERRIE             | TXB2IE           | TXB1IE           | TXB0IE          | RXB1IE          | RXB0IE/<br>FIFOFIE |

| bit 7         |                                      | -                 |                  |                  |                 |                 | bit C              |

| Legend:       |                                      |                   |                  |                  |                 |                 |                    |

| R = Readable  | e bit                                | W = Writable      | bit              | U = Unimpler     | mented bit, rea | ad as '0'       |                    |

| -n = Value at | POR                                  | '1' = Bit is set  |                  | '0' = Bit is cle | ared            | x = Bit is unki | nown               |

| bit 7         | IRXIE: Invali<br>1 = Interrupt       | d Message Rec     | eived Interrup   | ot Flag bit      |                 |                 |                    |

|               | 0 = Interrupt                        |                   |                  |                  |                 |                 |                    |

| bit 6         | •                                    | Wake-up Activ     | itv Interrupt FI | aq bit           |                 |                 |                    |

|               | 1 = Interrupt<br>0 = Interrupt       | t is enabled      |                  |                  |                 |                 |                    |

| bit 5         | ERRIE: Erro                          | or Interrupt Flag | bit (multiple s  | ources in the (  | COMSTAT regi    | ister)          |                    |

|               | 1 = Interrupt<br>0 = Interrupt       | t is enabled      |                  |                  | -               | ·               |                    |

| bit 4         | TXB2IE: Tra                          | nsmit Buffer 2 I  | nterrupt Flag I  | bit              |                 |                 |                    |

|               | 1 = Interrupt<br>0 = Interrupt       |                   |                  |                  |                 |                 |                    |

| bit 3         | TXB1IE: Tra                          | nsmit Buffer 1 I  | nterrupt Flag I  | bit              |                 |                 |                    |

|               | 1 = Interrupt<br>0 = Interrupt       |                   |                  |                  |                 |                 |                    |

| bit 2         | TXB0IE: Tra                          | nsmit Buffer 0 I  | nterrupt Flag I  | bit              |                 |                 |                    |

|               | 1 = Interrupt<br>0 = Interrupt       |                   |                  |                  |                 |                 |                    |

| bit 1         | RXB1IE: Re                           | ceive Buffer 1 I  | nterrupt Flag b  | bit              |                 |                 |                    |

|               | 1 = Interrupt<br>0 = Interrupt       |                   |                  |                  |                 |                 |                    |

| bit 0         | Bit operation<br>Mode 0:             | is dependent c    | n the selected   | d mode:          |                 |                 |                    |

|               | <b>RXB0IE</b> : Red<br>1 = Interrupt |                   | nterrupt Flag b  | bit              |                 |                 |                    |

|               | 0 = Interrupt                        | t is disabled     |                  |                  |                 |                 |                    |

|               | Mode 1:<br>Unimplemer                | nted: Read as '   | 0'               |                  |                 |                 |                    |

|               | Mode 2:                              |                   |                  |                  |                 |                 |                    |

|               |                                      | O Full Interrup   | t Flag bit       |                  |                 |                 |                    |

|               | 1 = Interrupt                        |                   |                  |                  |                 |                 |                    |

|               | 0 = Interrupt                        |                   |                  |                  |                 |                 |                    |

NOTES:

## 18.9 Measuring Temperature with the CTMU Module

The CTMU, along with an internal diode, can be used to measure the temperature. The A/D can be connected to the internal diode and the CTMU module can

source the current to the diode. The A/D reading will reflect the temperature. With the increase, the A/D readings will go low. This can be used for low-cost temperature measurement applications.

### EXAMPLE 18-6: ROUTINE FOR TEMPERATURE MEASUREMENT USING INTERNAL DIODE

| <pre>// Initialize CTMU CTMUICON = 0x03; CTMUCONHbits.CTMUEN = 1; CTMUCONLbits.EDG1STAT = 1;</pre> |                                                                                            |

|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| <pre>// Initialize ADC ADCON0 = 0xE5; ADCON1 = 0x00; ADCON2 = 0xBE;</pre>                          | // Enable ADC and connect to Internal diode                                                |

| ADCONObits.GO = 1;<br>while(ADCONObits.GO);<br>Temp = ADRES;                                       | <pre>// Start conversion // Read ADC results (inversely proportional to temperature)</pre> |

Note: The temperature diode is not calibrated or standardized; the user must calibrate the diode to their application.

| R/W-0        | U-0                                                                                                      | R/W-0                     | R/W-0         | R/W-0                    | R/W-0            | R/W-0           | R/W-0 |

|--------------|----------------------------------------------------------------------------------------------------------|---------------------------|---------------|--------------------------|------------------|-----------------|-------|

| ADFM         | _                                                                                                        | ACQT2                     | ACQT1         | ACQT0                    | ADCS2            | ADCS1           | ADCS0 |

| bit 7        |                                                                                                          |                           |               | ·                        |                  |                 | bit 0 |

|              |                                                                                                          |                           |               |                          |                  |                 |       |

| Legend:      |                                                                                                          |                           |               |                          |                  |                 |       |

| R = Readat   |                                                                                                          | W = Writable              | bit           | •                        | nented bit, read |                 |       |

| -n = Value a | at POR                                                                                                   | '1' = Bit is set          |               | '0' = Bit is clea        | ared             | x = Bit is unkr | lown  |

| bit 7        | ADFM: A/D R                                                                                              | esult Format S            | elect bit     |                          |                  |                 |       |

|              | 1 = Right justi<br>0 = Left justifie                                                                     |                           |               |                          |                  |                 |       |

| bit 6        | Unimplement                                                                                              | ted: Read as '            | )'            |                          |                  |                 |       |

| bit 5-3      | ACQT<2:0>:                                                                                               | A/D Acquisitior           | n Time Select | bits                     |                  |                 |       |

|              | 111 = 20 TAD<br>110 = 16 TAD<br>101 = 12 TAD<br>100 = 8 TAD<br>011 = 6 TAD<br>010 = 4 TAD<br>001 = 2 TAD |                           |               |                          |                  |                 |       |

|              | 000 = 0 TAD <sup>(1</sup>                                                                                |                           |               |                          |                  |                 |       |

| bit 2-0      | 111 = FRC (cl<br>110 = Fosc/6<br>101 = Fosc/1<br>100 = Fosc/4                                            | 6<br>ock derived fro<br>2 | m A/D RC osc  | sillator) <sup>(1)</sup> |                  |                 |       |

#### REGISTER 23-3: ADCON2: A/D CONTROL REGISTER 2

**Note 1:** If the A/D FRC clock source is selected, a delay of one TCY (instruction cycle) is added before the A/D clock starts. This allows the SLEEP instruction to be executed before starting a conversion.

### 23.3 A/D Acquisition Requirements

For the A/D Converter to meet its specified accuracy, the Charge Holding (CHOLD) capacitor must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 23-5. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD).

The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 2.5 k $\Omega$ . After the analog input channel is selected or changed, the channel must be sampled for at least the minimum acquisition time before starting a conversion.

**Note:** When the conversion is started, the holding capacitor is disconnected from the input pin.

To calculate the minimum acquisition time, Equation 23-1 can be used. This equation assumes that 1/2 LSb error is used (1,024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

Equation 23-3 shows the calculation of the minimum required acquisition time, TACQ. This calculation is based on the following application system assumptions:

| CHOLD            | =      | 25 pF                              |

|------------------|--------|------------------------------------|

| Rs               | =      | 2.5 kΩ                             |

| Conversion Error | $\leq$ | 1/2 LSb                            |

| Vdd              | =      | $3V \rightarrow Rss = 2 \ k\Omega$ |

| Temperature      | =      | 85°C (system max.)                 |

#### EQUATION 23-1: ACQUISITION TIME

| TACQ | = | Amplifier Settling Time + Holding Capacitor Charging Time + Temperature Coefficient |

|------|---|-------------------------------------------------------------------------------------|

|      | = | TAMP + TC + TCOFF                                                                   |

#### EQUATION 23-2: A/D MINIMUM CHARGING TIME

$VHOLD = (VREF - (VREF/2048)) \cdot (1 - e^{(-TC/CHOLD(RIC + RSS + RS))})$ or  $TC = -(CHOLD)(RIC + RSS + RS) \ln(1/2048)$

#### EQUATION 23-3: CALCULATING THE MINIMUM REQUIRED ACQUISITION TIME

| TACQ    | =       | TAMP + TC + TCOFF                                                                                                                             |

|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| TAMP    | =       | 0.2 μs                                                                                                                                        |

| TCOFF   | =       | (Temp – 25°C)(0.02 μs/°C)<br>(85°C – 25°C)(0.02 μs/°C)<br>1.2 μs                                                                              |

| Tempera | ature c | coefficient is only required for temperatures $> 25^{\circ}$ C. Below $25^{\circ}$ C, TCOFF = 0 ms.                                           |

| Тс      | =       | -(ChOLD)(RIC + Rss + Rs) ln(1/2048) $\mu$ s<br>-(25 pF) (1 k $\Omega$ + 2 k $\Omega$ + 2.5 k $\Omega$ ) ln(0.0004883) $\mu$ s<br>1.05 $\mu$ s |

| TACQ    | =       | 0.2 μs + 1.05 μs + 1.2 μs<br>2.45 μs                                                                                                          |

| Mode 0           | R-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R-0                                                                                                                                                     | R-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R-0      | R-0                                                                                                                                                                                  | R-0                           | R-0                                                                                                                                                                                                                                                                                                                 | U-0                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| vioae u          | OPMODE2 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | OPMODE1 <sup>(1)</sup>                                                                                                                                  | OPMODE0 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _        | ICODE2                                                                                                                                                                               | ICODE1                        | ICODE0                                                                                                                                                                                                                                                                                                              | —                       |

|                  | R-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R-0                                                                                                                                                     | R-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R-0      | R-0                                                                                                                                                                                  | R-0                           | R-0                                                                                                                                                                                                                                                                                                                 | R-0                     |

| Node 1,2         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | OPMODE1 <sup>(1)</sup>                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | EICODE4  | EICODE3                                                                                                                                                                              | EICODE2                       | EICODE1                                                                                                                                                                                                                                                                                                             | EICODE                  |

|                  | bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                                                                                                                                                                      |                               |                                                                                                                                                                                                                                                                                                                     | bi                      |

| Legend:          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                                                                                                                                                                      |                               |                                                                                                                                                                                                                                                                                                                     |                         |

| R = Readab       | le bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                         | W = Writable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | U = Unimp                                                                                                                                                                            | lemented bit                  | read as '0                                                                                                                                                                                                                                                                                                          |                         |

| -n = Value a     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                         | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | '0' = Bit is o                                                                                                                                                                       |                               | x = Bit is u                                                                                                                                                                                                                                                                                                        |                         |

| bit 7-5          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                         | Iode Status bits <sup>(*</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1)       |                                                                                                                                                                                      |                               |                                                                                                                                                                                                                                                                                                                     |                         |

|                  | 111 = Reserve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                                                                                                                                                                      |                               |                                                                                                                                                                                                                                                                                                                     |                         |

|                  | 110 = Reserve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                                                                                                                                                                      |                               |                                                                                                                                                                                                                                                                                                                     |                         |

|                  | 101 = Reserve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                                                                                                                                                                      |                               |                                                                                                                                                                                                                                                                                                                     |                         |

|                  | 100 = Configur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                                                                                                                                                                      |                               |                                                                                                                                                                                                                                                                                                                     |                         |

|                  | 011 = Listen O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nly mode                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                                                                                                                                                                      |                               |                                                                                                                                                                                                                                                                                                                     |                         |

|                  | 010 = Loopbac                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                                                                                                                                                                      |                               |                                                                                                                                                                                                                                                                                                                     |                         |

|                  | 001 = Disable/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                                                                                                                                                                      |                               |                                                                                                                                                                                                                                                                                                                     |                         |

|                  | 000 <b>= Normal</b> r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | mode                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                                                                                                                                                                      |                               |                                                                                                                                                                                                                                                                                                                     |                         |

| bit 4            | Mode 0:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                                                                                                                                                                      |                               |                                                                                                                                                                                                                                                                                                                     |                         |

|                  | Unimplemente                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ed: Read as '0                                                                                                                                          | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |                                                                                                                                                                                      |                               |                                                                                                                                                                                                                                                                                                                     |                         |

| bit 3-1,4-0      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | nterrupt Code                                                                                                                                           | bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                                                                                                                                                                                      |                               |                                                                                                                                                                                                                                                                                                                     |                         |