Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | ECANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 35                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.6K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                 |

| Data Converters            | A/D 11x12b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f46k80t-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

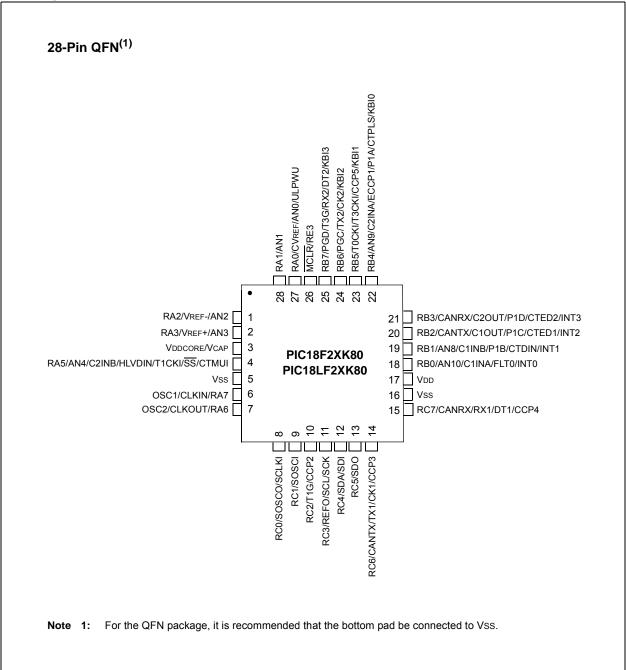

#### **Pin Diagrams**

| R/W-0        | U-0                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                            | R/W-0                                                                                                                                                                                      | R/W-0                  | R/W-0           | R/W-0           | R/W-0      |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------|-----------------|------------|

| ROON         |                                                                                                                                                                                  | ROSSLP                                                                                                                                                                                                                           | ROSEL <sup>(1)</sup>                                                                                                                                                                       | RODIV3                 | RODIV2          | RODIV1          | RODIV0     |

| bit 7        |                                                                                                                                                                                  |                                                                                                                                                                                                                                  |                                                                                                                                                                                            |                        |                 |                 | bit        |

| Legend:      |                                                                                                                                                                                  |                                                                                                                                                                                                                                  |                                                                                                                                                                                            |                        |                 |                 |            |

| R = Readat   | ole bit                                                                                                                                                                          | W = Writable                                                                                                                                                                                                                     | bit                                                                                                                                                                                        | U = Unimplen           | nented bit, rea | d as '0'        |            |

| -n = Value a | at POR                                                                                                                                                                           | '1' = Bit is set                                                                                                                                                                                                                 |                                                                                                                                                                                            | '0' = Bit is cle       | ared            | x = Bit is unkr | nown       |

| bit 7        | ROON: Refer                                                                                                                                                                      | ence Oscillator                                                                                                                                                                                                                  | Output Enabl                                                                                                                                                                               | le bit                 |                 |                 |            |

|              | 1 = Reference                                                                                                                                                                    | e oscillator outp<br>e oscillator outp                                                                                                                                                                                           | out is available                                                                                                                                                                           |                        |                 |                 |            |

| bit 6        | Unimplemen                                                                                                                                                                       | ted: Read as '                                                                                                                                                                                                                   | D'                                                                                                                                                                                         |                        |                 |                 |            |

| bit 5        | ROSSLP: Re                                                                                                                                                                       | ference Oscilla                                                                                                                                                                                                                  | tor Output Sto                                                                                                                                                                             | p in Sleep bit         |                 |                 |            |

|              |                                                                                                                                                                                  | e oscillator con<br>e oscillator is di                                                                                                                                                                                           |                                                                                                                                                                                            |                        |                 |                 |            |

| bit 4        | ROSEL: Refe                                                                                                                                                                      | erence Oscillato                                                                                                                                                                                                                 | or Source Sele                                                                                                                                                                             | ect bit <sup>(1)</sup> |                 |                 |            |

|              |                                                                                                                                                                                  | scillator (EC or<br>lock is used as                                                                                                                                                                                              |                                                                                                                                                                                            |                        |                 | ck switching of | the device |

| bit 3-0      | RODIV<3:0>                                                                                                                                                                       | Reference Os                                                                                                                                                                                                                     | cillator Divisor                                                                                                                                                                           | Select bits            |                 |                 |            |

|              |                                                                                                                                                                                  | clock value div                                                                                                                                                                                                                  |                                                                                                                                                                                            |                        |                 |                 |            |

|              | 1110 <b>= Base</b>                                                                                                                                                               |                                                                                                                                                                                                                                  |                                                                                                                                                                                            |                        |                 |                 |            |

|              | 1101 <b>= Base</b>                                                                                                                                                               | clock value div                                                                                                                                                                                                                  | ided by 8,192                                                                                                                                                                              |                        |                 |                 |            |

|              | 1101 <b>= Base</b><br>1100 <b>= Base</b>                                                                                                                                         | clock value div<br>clock value div                                                                                                                                                                                               | ided by 8,192<br>ided by 4,096                                                                                                                                                             |                        |                 |                 |            |

|              | 1101 = Base<br>1100 = Base<br>1011 = Base                                                                                                                                        | clock value div                                                                                                                                                                                                                  | ided by 8,192<br>ided by 4,096<br>ided by 2,048                                                                                                                                            |                        |                 |                 |            |

|              | 1101 = Base<br>1100 = Base<br>1011 = Base<br>1010 = Base<br>1001 = Base                                                                                                          | clock value div<br>clock value div<br>clock value div<br>clock value div<br>clock value div                                                                                                                                      | ided by 8,192<br>ided by 4,096<br>ided by 2,048<br>ided by 1,024<br>ided by 512                                                                                                            |                        |                 |                 |            |

|              | 1101 = Base<br>1100 = Base<br>1011 = Base<br>1010 = Base<br>1001 = Base<br>1000 = Base                                                                                           | clock value div<br>clock value div<br>clock value div<br>clock value div<br>clock value div<br>clock value div                                                                                                                   | ided by 8,192<br>ided by 4,096<br>ided by 2,048<br>ided by 1,024<br>ided by 512<br>ided by 256                                                                                             |                        |                 |                 |            |

|              | 1101 = Base<br>1100 = Base<br>1011 = Base<br>1010 = Base<br>1001 = Base<br>1000 = Base<br>0111 = Base                                                                            | clock value div<br>clock value div<br>clock value div<br>clock value div<br>clock value div<br>clock value div<br>clock value div                                                                                                | ided by 8,192<br>ided by 4,096<br>ided by 2,048<br>ided by 1,024<br>ided by 512<br>ided by 256<br>ided by 128                                                                              |                        |                 |                 |            |

|              | 1101 = Base<br>1100 = Base<br>1011 = Base<br>1010 = Base<br>1001 = Base<br>0111 = Base<br>0110 = Base                                                                            | clock value div<br>clock value div<br>clock value div<br>clock value div<br>clock value div<br>clock value div                                                                                                                   | ided by 8,192<br>ided by 4,096<br>ided by 2,048<br>ided by 1,024<br>ided by 512<br>ided by 256<br>ided by 128<br>ided by 64                                                                |                        |                 |                 |            |

|              | 1101 = Base<br>1100 = Base<br>1011 = Base<br>1010 = Base<br>1001 = Base<br>0111 = Base<br>0110 = Base<br>0101 = Base<br>0101 = Base                                              | clock value div<br>clock value div                    | ided by 8,192<br>ided by 4,096<br>ided by 2,048<br>ided by 1,024<br>ided by 512<br>ided by 256<br>ided by 128<br>ided by 64<br>ided by 32<br>ided by 16                                    |                        |                 |                 |            |

|              | 1101 = Base<br>1100 = Base<br>1011 = Base<br>1010 = Base<br>1001 = Base<br>0111 = Base<br>0110 = Base<br>0101 = Base<br>0101 = Base<br>0101 = Base                               | clock value div<br>clock value div | ided by $8,192$<br>ided by $4,096$<br>ided by $2,048$<br>ided by $1,024$<br>ided by $512$<br>ided by $256$<br>ided by $128$<br>ided by $64$<br>ided by $32$<br>ided by $16$<br>ided by $8$ |                        |                 |                 |            |

|              | 1101 = Base<br>1100 = Base<br>1011 = Base<br>1010 = Base<br>1001 = Base<br>0111 = Base<br>0110 = Base<br>0101 = Base<br>0101 = Base<br>0101 = Base<br>0011 = Base<br>0011 = Base | clock value div<br>clock value div                    | ided by 8,192<br>ided by 4,096<br>ided by 2,048<br>ided by 1,024<br>ided by 512<br>ided by 256<br>ided by 128<br>ided by 64<br>ided by 32<br>ided by 16<br>ided by 8<br>ided by 4          |                        |                 |                 |            |

#### REGISTER 3-4: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

**Note 1:** For ROSEL (REFOCON<4>), the primary oscillator is available only when configured as the default via the FOSCx settings. This is regardless of whether the device is in Sleep mode.

If the IRCFx bits and the INTSRC bit are all clear, the INTOSC output (HF-INTOSC/MF-INTOSC) is not enabled and the HFIOFS and MFIOFS bits will remain clear. There will be no indication of the current clock source. The LF-INTOSC source is providing the device clocks.

If the IRCFx bits are changed from all clear (thus, enabling the INTOSC output) or if INTSRC or MFIOSEL is set, the HFIOFS or MFIOFS bit is set after the INTOSC output becomes stable. For details, see Table 4-3.

| IRCF<2:0> | INTSRC | MFIOSEL | Status of MFIOFS or HFIOFS when INTOSC is Stable     |

|-----------|--------|---------|------------------------------------------------------|

| 000       | 0      | х       | MFIOFS = 0, HFIOFS = 0 and clock source is LF-INTOSC |

| 000       | 1      | 0       | MFIOFS = 0, HFIOFS = 1 and clock source is HF-INTOSC |

| 000       | 1      | 1       | MFIOFS = 1, HFIOFS = 0 and clock source is MF-INTOSC |

| Non-Zero  | x      | 0       | MFIOFS = 0, HFIOFS = 1 and clock source is HF-INTOSC |

| Non-Zero  | x      | 1       | MFIOFS = 1, HFIOFS = 0 and clock source is MF-INTOSC |

#### TABLE 4-3: INTERNAL OSCILLATOR FREQUENCY STABILITY BITS

Clocks to the device continue while the INTOSC source stabilizes after an interval of TIOBST (Parameter 39, Table 31-11).

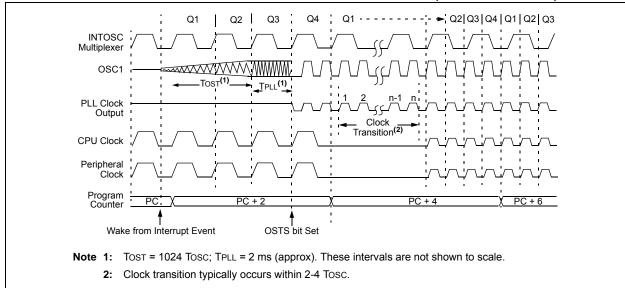

If the IRCFx bits were previously at a non-zero value, or if INTSRC was set before setting SCS1 and the INTOSC source was already stable, the HFIOFS or MFIOFS bit will remain set. On transitions from RC\_RUN mode to PRI\_RUN mode, the device continues to be clocked from the INTOSC multiplexer while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 4-4). When the clock switch is complete, the HFIOFS or MFIOFS bit is cleared, the OSTS bit is set and the primary clock is providing the device clock. The IDLEN and SCSx bits are not affected by the switch. The LF-INTOSC source will continue to run if either the WDT or the Fail-Safe Clock Monitor (FSCM) is enabled.

# 4.4.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator block using the INTOSC multiplexer. This mode provides controllable power conservation during Idle periods.

From RC\_RUN, this mode is entered by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, first set IDLEN, then set the SCS1 bit and execute SLEEP. To maintain software compatibility with future devices, it is recommended that SCS0 also be cleared, though its value is ignored. The INTOSC multiplexer may be used to select a higher clock frequency by modifying the IRCFx bits before executing the SLEEP instruction. When the clock source is switched to the INTOSC multiplexer, the primary oscillator is shut down and the OSTS bit is cleared.

If the IRCFx bits are set to any non-zero value, or the INTSRC/MFIOSEL bit is set, the INTOSC output is enabled. The HFIOFS/MFIOFS bits become set, after the INTOSC output becomes stable, after an interval of TIOBST (Parameter 38, Table 31-11). For information on the HFIOFS/MFIOFS bits, see Table 4-3.

Clocks to the peripherals continue while the INTOSC source stabilizes. The HFIOFS/MFIOFS bits will remain set if the IRCFx bits were previously at a non-zero value or if INTSRC was set before the SLEEP instruction was executed and the INTOSC source was already stable. If the IRCFx bits and INTSRC are all clear, the INTOSC output will not be enabled, the HFIOFS/MFIOFS bits will remain clear and there will be no indication of the current clock source.

When a wake event occurs, the peripherals continue to be clocked from the INTOSC multiplexer. After a delay of TCSD (Parameter 38, Table 31-11) following the wake event, the CPU begins executing code clocked by the INTOSC multiplexer. The IDLEN and SCSx bits are not affected by the wake-up. The INTOSC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

## 4.5 Selective Peripheral Module Control

Idle mode allows users to substantially reduce power consumption by stopping the CPU clock. Even so, peripheral modules still remain clocked, and thus, consume power. There may be cases where the application needs what this mode does not provide: the allocation of power resources to the CPU processing with minimal power consumption from the peripherals.

PIC18F66K80 family devices address this requirement by allowing peripheral modules to be selectively disabled, reducing or eliminating their power consumption. This can be done with two control bits:

- Peripheral Enable bit, generically named XXXEN Located in the respective module's main control register

- Peripheral Module Disable (PMD) bit, generically named, XXXMD – Located in one of the PMDx Control registers (PMD0, PMD1 or PMD2)

Disabling a module by clearing its XXXEN bit disables the module's functionality, but leaves its registers available to be read and written to. This reduces power consumption, but not by as much as the second approach.

Most peripheral modules have an enable bit.

In contrast, setting the PMD bit for a module disables all clock sources to that module, reducing its power consumption to an absolute minimum. In this state, the control and status registers associated with the peripheral are also disabled, so writes to those registers have no effect and read values are invalid. Many peripheral modules have a corresponding PMD bit.

There are three PMD registers in PIC18F66K80 family devices: PMD0, PMD1 and PMD2. These registers have bits associated with each module for disabling or enabling a particular peripheral.

| TABLE 5-4:  | ABLE 5-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |                 |             |                                          |                                                                  |                                    |  |  |

|-------------|-------------------------------------------------------------------|-----------------|-------------|------------------------------------------|------------------------------------------------------------------|------------------------------------|--|--|

| Register    | A                                                                 | pplicable Devic | es          | Power-on<br>Reset,<br>Brown-out<br>Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via<br>WDT<br>or Interrupt |  |  |

| PMD1        | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | 0000 0000                                | 0000 0000                                                        | uuuu uuuu                          |  |  |

| PMD2        | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | 0000                                     | 0000                                                             | uuuu                               |  |  |

| PADCFG1     | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | 00000                                    | 00000                                                            | uuuuu                              |  |  |

| CTMUCONH    | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | 0-00 0000                                | 0-00 0000                                                        | u-uu uuuu                          |  |  |

| CTMUCONL    | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | 0000 0000                                | 0000 0000                                                        | uuuu uuuu                          |  |  |

| CTMUICON    | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | 0000 0000                                | 0000 0000                                                        | uuuu uuuu                          |  |  |

| CCPR2H      | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | xxxx xxxx                                                        | uuuu uuuu                          |  |  |

| CCPR2L      | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | xxxx xxxx                                                        | uuuu uuuu                          |  |  |

| CCP2CON     | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | 00 0000                                  | 00 0000                                                          | uu uuuu                            |  |  |

| CCPR3H      | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | xxxx xxxx                                                        | uuuu uuuu                          |  |  |

| CCPR3L      | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | xxxx xxxx                                                        | uuuu uuuu                          |  |  |

| CCP3CON     | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | 00 0000                                  | 00 0000                                                          | uu uuuu                            |  |  |

| CCPR4H      | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | xxxx xxxx                                                        | uuuu uuuu                          |  |  |

| CCPR4L      | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | xxxx xxxx                                                        | uuuu uuuu                          |  |  |

| CCP4CON     | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | 00 0000                                  | 00 0000                                                          | uu uuuu                            |  |  |

| CCPR5H      | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | xxxx xxxx                                                        | uuuu uuuu                          |  |  |

| CCPR5L      | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | xxxx xxxx                                                        | uuuu uuuu                          |  |  |

| CCP5CON     | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | 00 0000                                  | 00 0000                                                          | uu uuuu                            |  |  |

| PSPCON      | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | 0000                                     | 0000                                                             | uuuu                               |  |  |

| MDCON       | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | 0010 00                                  | 0010 00                                                          | uuuu uu                            |  |  |

| MDSRC       | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | 0 xxxx                                   | 0 xxxx                                                           | u uuuu                             |  |  |

| MDCARH      | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | 0xx- xxxx                                | 0xx- xxxx                                                        | uuu- uuuu                          |  |  |

| MDCARL      | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | 0xx- xxxx                                | 0xx- xxxx                                                        | uuu- uuuu                          |  |  |

| CANCON_RO0  | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | 1000 0000                                | 1000 0000                                                        | uuuu uuuu                          |  |  |

| CANSTAT_RO0 | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | 1000 0000                                | 1000 0000                                                        | uuuu uuuu                          |  |  |

| RXB1D7      | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |

| RXB1D6      | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |

| RXB1D5      | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |

| RXB1D4      | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |

| RXB1D3      | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |

| RXB1D2      | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |

| RXB1D1      | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |

| RXB1D0      | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |  |  |

| RXB1DLC     | PIC18F2XK80                                                       | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | xxxx xxxx                          |  |  |

#### TABLE 5-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Legend: u = unchanged; x = unknown; - = unimplemented bit, read as '0'; q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 5-3 for Reset value for specific conditions.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read as '0'.

#### 10.4 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are six Peripheral Interrupt Priority registers (IPR1 through IPR6). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit (RCON<7>) be set.

#### REGISTER 10-14: IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1

| R/W-1                  | R/W-1                                                                        | R/W-1            | R/W-1            | R/W-1              | R/W-1            | R/W-1           | R/W-1  |

|------------------------|------------------------------------------------------------------------------|------------------|------------------|--------------------|------------------|-----------------|--------|

| PSPIP                  | ADIP                                                                         | RC1IP            | TX1IP            | SSPIP              | TMR1GIP          | TMR2IP          | TMR1IP |

| bit 7                  |                                                                              |                  |                  |                    |                  |                 | bit 0  |

|                        |                                                                              |                  |                  |                    |                  |                 |        |

| Legend:<br>R = Readabl | lo bit                                                                       | W = Writable     | hit              | II – Unimplon      | nented bit, read | 1 00 '0'        |        |

| -n = Value at          |                                                                              | '1' = Bit is set |                  | '0' = Bit is clea  |                  | x = Bit is unkr |        |

|                        | IFOR                                                                         | I - DILIS SEL    |                  |                    | areu             |                 | 101011 |

| bit 7                  | PSPIP: Parall                                                                | el Slave Port F  | Read/Write Inte  | errupt Priority bi | t                |                 |        |

|                        | 1 = High prio<br>0 = Low prior                                               |                  |                  |                    |                  |                 |        |

| bit 6                  |                                                                              | onverter Interru | pt Priority bit  |                    |                  |                 |        |

|                        | 1 = High prio<br>0 = Low prior                                               | •                |                  |                    |                  |                 |        |

| bit 5                  | •                                                                            | RTx Receive I    | nterrunt Priorit | v hit              |                  |                 |        |

| bit o                  | 1 = High prio                                                                |                  |                  | y on               |                  |                 |        |

|                        | 0 = Low prior                                                                |                  |                  |                    |                  |                 |        |

| bit 4                  | TX1IP: EUSA                                                                  | RTx Transmit     | nterrupt Priorit | ty bit             |                  |                 |        |

|                        | 1 = High prio<br>0 = Low prior                                               | •                |                  |                    |                  |                 |        |

| bit 3                  | •                                                                            | •                | Serial Port In   | terrupt Priority   | hit              |                 |        |

| Sit 0                  | 1 = High prio                                                                | •                |                  | ton up trinonty i  |                  |                 |        |

|                        | 0 = Low prior                                                                | ity              |                  |                    |                  |                 |        |

| bit 2                  | TMR1GIP: Tir                                                                 | mer1 Gate Inte   | rrupt Priority b | it                 |                  |                 |        |

|                        | 1 = High prio<br>0 = Low prior                                               | ,                |                  |                    |                  |                 |        |

| bit 1                  | •                                                                            | -                | h Interrunt Pri  | ority hit          |                  |                 |        |

|                        | <b>TMR2IP:</b> TMR2 to PR2 Match Interrupt Priority bit<br>1 = High priority |                  |                  |                    |                  |                 |        |

|                        | 0 = Low prior                                                                | •                |                  |                    |                  |                 |        |

| bit 0                  | TMR1IP: TMF                                                                  | R1 Overflow Inf  | errupt Priority  | bit                |                  |                 |        |

|                        | 1 = High prio                                                                |                  |                  |                    |                  |                 |        |

|                        | 0 = Low prior                                                                | цу               |                  |                    |                  |                 |        |

| Pin Name                 | Function             | TRIS<br>Setting | I/O | I/O Type | Description                                                                                                      |

|--------------------------|----------------------|-----------------|-----|----------|------------------------------------------------------------------------------------------------------------------|

| RB0/AN10/C1INA           | RB0                  | 0               | 0   | DIG      | LATB<0> data output.                                                                                             |

| FLT0/INT0                |                      | 1               | Ι   | ST       | PORTB<0> data input; weak pull-up when RBPU bit is cleared.                                                      |

|                          | AN10                 | 1               | Ι   | ANA      | A/D Input Channel 10 and Comparator C1+ input. Default input configuration on POR.                               |

|                          | C1INA <sup>(1)</sup> | 1               | Ι   | ANA      | Comparator 1 Input A.                                                                                            |

|                          | FLT0                 | х               | Ι   | ST       | Enhanced PWM Fault input for ECCPx.                                                                              |

|                          | INT0                 | 1               | Ι   | ST       | External Interrupt 0 input.                                                                                      |

| RB1/AN8/C1INB/           | RB1                  | 0               | 0   | DIG      | LATB<1> data output.                                                                                             |

| P1B/CTDIN/INT1           |                      | 1               | Ι   | ST       | PORTB<1> data input; weak pull-up when RBPU bit is cleared.                                                      |

|                          | AN8                  | 1               | I   | ANA      | A/D Input Channel 8 and Comparator C2+ input. Default input configuration on POR; not affected by analog output. |

|                          | C1INB <sup>(1)</sup> | 1               | Ι   | ANA      | Comparator 1 Input B.                                                                                            |

|                          | P1B <sup>(1)</sup>   | 0               | 0   | DIG      | ECCP1 PWM Output B. May be configured for tri-state during<br>Enhanced PWM shutdown events.                      |

|                          | CTDIN                | 1               | Ι   | ST       | CTMU pulse delay input.                                                                                          |

|                          | INT1                 | 1               | Ι   | ST       | External Interrupt 1 input.                                                                                      |

| RB2/CANTX/C1OUT/         | RB2                  | 0               | 0   | DIG      | LATB<2> data output.                                                                                             |

| P1C/CTED1/INT2           |                      | 1               | Ι   | ST       | PORTB<2> data input; weak pull-up when RBPU bit is cleared.                                                      |

|                          | CANTX <sup>(2)</sup> | 0               | 0   | DIG      | CAN bus TX.                                                                                                      |

|                          | C10UT <sup>(1)</sup> | 0               | 0   | DIG      | Comparator 1 output; takes priority over port data.                                                              |

|                          | P1C <sup>(1)</sup>   | 0               | 0   | DIG      | ECCP1 PWM Output C. May be configured for tri-state during<br>Enhanced PWM.                                      |

|                          | CTED1                | х               | Ι   | ST       | CTMU Edge 1 input.                                                                                               |

|                          | INT2                 | 1               | Ι   | ST       | External Interrupt 2.                                                                                            |

| RB3/CANRX/               | RB3                  | 0               | 0   | DIG      | LATB<3> data output.                                                                                             |

| C2OUT/P1D/<br>CTED2/INT3 |                      | 1               | Ι   | ST       | PORTB<3> data input; weak pull-up when RBPU bit is cleared.                                                      |

| CTED2/INTS               | CANRX <sup>(2)</sup> | 1               | Ι   | ST       | CAN bus RX.                                                                                                      |

|                          | C2OUT <sup>(1)</sup> | х               | -   | ST       | CTMU Edge 2 input.                                                                                               |

|                          | P1D <sup>(1)</sup>   | 0               | 0   | DIG      | ECCP1 PWM Output D. May be configured for tri-state during<br>Enhanced PWM.                                      |

|                          | CTED2                | х               | Ι   | ST       | CTMU Edge 2 input.                                                                                               |

|                          | INT3                 | 1               | Ι   | ST       | External Interrupt 3 input.                                                                                      |

## TABLE 11-3: PORTB FUNCTIONS

Legend: O = Output; I = Input; ANA = Analog Signal; DIG = CMOS Output; ST = Schmitt Trigger Buffer Input; x = Don't care (TRIS bit does not affect port direction or is overridden for this option)

**Note 1:** This pin assignment is only available for 28-pin devices (PIC18F2XK80).

2: This is the default pin assignment for CANRX and CANTX when the CANMX Configuration bit is set.

3: This is the default pin assignment for TOCKI when the TOCKMX Configuration bit is set.

4: This is the default pin assignment for T3CKI for 28, 40 and 44-pin devices. This is the alternate pin assignment for T3CKI for 64-pin devices when T3CKMX is cleared.

| Pin Name    | Function               | TRIS<br>Setting | I/O | I/O Type | Description                                                                            |

|-------------|------------------------|-----------------|-----|----------|----------------------------------------------------------------------------------------|

| RE5/CANTX   | RE5 <sup>(1)</sup>     | 0               | 0   | DIG      | LATE<5> data output.                                                                   |

|             |                        | 1               | Ι   | ST       | PORTE<5> data input.                                                                   |

|             | CANTX <sup>(1,2)</sup> | 0               | 0   | DIG      | CAN bus TX.                                                                            |

| RE6/RX2/DT2 | RE6 <sup>(1)</sup>     | 0               | 0   | DIG      | LATE<6> data output.                                                                   |

|             |                        | 1               | Ι   | ST       | PORTE<6> data input.                                                                   |

|             | RX2 <sup>(1)</sup>     | 1               | Ι   | ST       | Asynchronous serial receive data input (EUSARTx module).                               |

|             | DT2 <sup>(1)</sup>     | 1               | 0   | DIG      | Synchronous serial data output (EUSARTx module); takes priority over port data.        |

|             |                        | 1               | I   | ST       | Synchronous serial data input (EUSARTx module); user must configure as an input.       |

| RE7/TX2/CK2 | RE7 <sup>(1)</sup>     | 0               | 0   | DIG      | LATE<7> data output.                                                                   |

|             |                        | 1               | Ι   | ST       | PORTE<7> data input.                                                                   |

|             | TX2 <sup>(1)</sup>     | 0               | 0   | DIG      | Asynchronous serial data output (EUSARTx module); takes priority over port data.       |

|             | CK2 <sup>(1)</sup>     | 0               | 0   | DIG      | Synchronous serial clock output (EUSARTx module); user must configure as an input.     |

|             |                        | 1               | Ι   | ST       | Synchronous serial clock input (EUSARTx module); user must config-<br>ure as an input. |

## TABLE 11-9: PORTE FUNCTIONS (CONTINUED)

Legend: O = Output, I = Input, ANA = Analog Signal, DIG = CMOS Output, ST = Schmitt Trigger Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option)

Note 1: These bits are unavailable for 40 and 44-pin devices (PIC18F4XK0).

2: This is the alternate pin assignment for CANRX and CANTX on 64-pin devices (PIC18F6XK80) when the CANMX Configuration bit is cleared.

| Name    | Bit 7              | Bit 6              | Bit 5               | Bit 4               | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|---------|--------------------|--------------------|---------------------|---------------------|--------|--------|--------|--------|

| PORTE   | RE7 <sup>(1)</sup> | RE6 <sup>(1)</sup> | RE5 <sup>(1)</sup>  | RE4 <sup>(1)</sup>  | RE3    | RE2    | RE1    | RE0    |

| LATE    | LATE7              | LATE6              | LATE5               | LATE4               | —      | LATE2  | LATE1  | LATE0  |

| TRISE   | TRISE7             | TRISE6             | TRISE5              | TRISE4              | —      | TRISE2 | TRISE1 | TRISE0 |

| PADCFG1 | RDPU               | REPU               | RFPU <sup>(1)</sup> | RGPU <sup>(1)</sup> | _      |        | _      | CTMUDS |

| ANCON0  | ANSEL7             | ANSEL6             | ANSEL5              | ANSEL4              | ANSEL3 | ANSEL2 | ANSEL1 | ANSEL0 |

Legend: Shaded cells are not used by PORTE.

Note 1: These bits are unimplemented on 44-pin devices, read as '0'.

#### **REGISTER 11-5: PSPCON: PARALLEL SLAVE PORT CONTROL REGISTER**

| R-0   | R-0 | R/W-0 | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-------|---------|-----|-----|-----|-------|

| IBF   | OBF | IBOV  | PSPMODE | _   | —   | —   |       |

| bit 7 |     |       |         |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | <b>IBF:</b> Input Buffer Full Status bit<br>1 = A word has been received and is waiting to be read by the CPU<br>0 = No word has been received          |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | <b>OBF:</b> Output Buffer Full Status bit                                                                                                               |

|         | <ul> <li>1 = The output buffer still holds a previously written word</li> <li>0 = The output buffer has been read</li> </ul>                            |

| bit 5   | IBOV: Input Buffer Overflow Detect bit                                                                                                                  |

|         | <ul> <li>1 = A write occurred when a previously input word had not been read (must be cleared in software)</li> <li>0 = No overflow occurred</li> </ul> |

| bit 4   | PSPMODE: Parallel Slave Port Mode Select bit                                                                                                            |

|         | 1 = Parallel Slave Port mode<br>0 = General Purpose I/O mode                                                                                            |

| bit 3-0 | Unimplemented: Read as '0'                                                                                                                              |

#### FIGURE 11-4: PARALLEL SLAVE PORT WRITE WAVEFORMS

|              | Q1   Q2   Q3   Q4 Q1   Q2   Q3   Q4 Q1   Q2   Q3   Q4 |

|--------------|-------------------------------------------------------|

| CS           |                                                       |

| WR           |                                                       |

| RD -         |                                                       |

| PORTD<7:0> — |                                                       |

| IBF          |                                                       |

| OBF —        |                                                       |

| PSPIF        |                                                       |

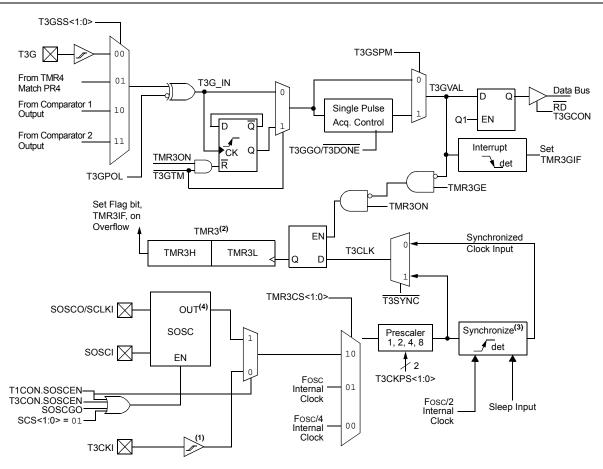

# 16.2 Timer3 Operation

Timer3 can operate in these modes:

- Timer

- Synchronous Counter

- · Asynchronous Counter

- · Timer with Gated Control

#### FIGURE 16-1: TIMER3 BLOCK DIAGRAM

Note 1: ST Buffer is high-speed type when using T3CKI.

- 2: Timer3 registers increment on rising edge.

- 3: Synchronization does not operate while in Sleep.

- 4: The output of SOSC is determined by the SOSCSEL<1:0> Configuration bits.

The operating mode is determined by the clock select bits, TMR3CSx (T3CON<7:6>). When the TMR3CSx bits are cleared (= 00), Timer3 increments on every internal instruction cycle (Fosc/4). When TMR3CSx = 01, the Timer3 clock source is the system clock (Fosc), and when it is '10', Timer3 works as a counter from the external clock from the T3CKI pin (on the rising edge after the first falling edge) or the SOSC oscillator.

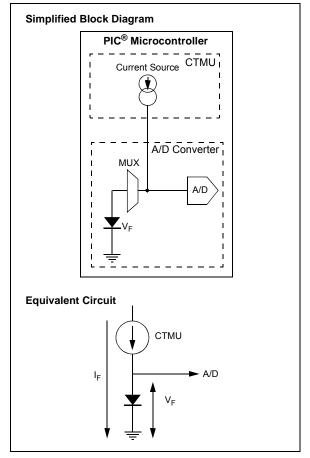

# 18.7 Measuring Temperature with the CTMU

The constant current source provided by the CTMU module can be used for low-cost temperature measurement by exploiting a basic property of common and inexpensive diodes. An on-chip temperature sense diode is provided on A/D Channel 29 to further simplify design and cost.

#### 18.7.1 BASIC PRINCIPAL

We can show that the forward voltage ( $V_F$ ) of a P-N junction, such as a diode, is an extension of the equation for the junction's thermal voltage:

$$V_{\rm F} = \frac{kT}{q} \ln \left(1 - \frac{I_{\rm F}}{I_{\rm S}}\right)$$

where k is the Boltzmann constant ( $1.38 \times 10^{-23}$  J K<sup>-1</sup>), T is the absolute junction temperature in kelvin, q is the electron charge ( $1.6 \times 10^{-19}$  C), I<sub>F</sub> is the forward current applied to the diode and I<sub>S</sub> is the diode's characteristic saturation current, which varies between devices.

Since k and q are physical constants, and  $I_S$  is a constant for the device, this only leaves T and  $I_F$  as independent variables. If  $I_F$  is held constant, it follows from the equation that  $V_F$  will vary as a function of T. As the natural log term of the equation will always be negative, the temperature will be negatively proportional to  $V_F$ . In other words, as temperature increases,  $V_F$  decreases.

By using the CTMU's current source to provide a constant  $I_F$ , it becomes possible to calculate the temperature by measuring the  $V_F$  across the diode.

#### 18.7.2 IMPLEMENTATION

To implement this theory, all that is needed is to connect a regular junction diode to one of the microcontroller's A/D pins (Figure 18-2). The A/D channel multiplexer is shared by the CTMU and the A/D. To perform a measurement, the multiplexer is configured to select the pin connected to the diode. The CTMU current source is then turned on and an A/D conversion is performed on the channel. As shown in the equivalent circuit diagram, the diode is driven by the CTMU at  $I_F$ . The resulting  $V_F$  across the diode is measured by the A/D. A code snippet is shown in Example 18-5.

#### FIGURE 18-4: CTMU TEMPERATURE MEASUREMENT CIRCUIT

#### EXAMPLE 18-5: ROUTINE FOR TEMPERATURE MEASUREMENT USING INTERNAL DIODE

| <pre>// Initialize CTMU CTMUICON = 0x03; CTMUCONHbits.CTMUEN = 1; CTMUCONLbits.EDG1STAT = 1;</pre> |                                                                                    |

|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| // Initialize ADC $ADCON0 = 0x75;$                                                                 | // Enable ADC and connect to Internal diode                                        |

| $ADCON1 = 0 \times 00;$                                                                            | // Enable Abe and connect to Internal drote                                        |

| $ADCON2 = 0 \times BE;$                                                                            | //Right Justified                                                                  |

| ADCON0bits.GO = 1;<br>while(ADCON0bits.G0);                                                        | // Start conversion                                                                |

| Temp = ADRES;                                                                                      | // Read ADC results (inversely proportional to temperature)                        |

| <b>Note:</b> The temperature diode is not ca                                                       | alibrated or standardized; the user must calibrate the diode to their application. |

#### 21.3.9 OPERATION IN POWER-MANAGED MODES

In SPI Master mode, module clocks may be operating at a different speed than when in full-power mode; in the case of the Sleep mode, all clocks are halted.

In Idle modes, a clock is provided to the peripherals. That clock can be from the primary clock source, the secondary clock (SOSC oscillator) or the INTOSC source. See **Section 3.3** "**Clock Sources and Oscillator Switching**" for additional information.

In most cases, the speed that the master clocks SPI data is not important; however, this should be evaluated for each system.

If MSSP interrupt is enabled, it can wake the controller from Sleep mode, or one of the Idle modes, when the master completes sending data. If an exit from Sleep or Idle mode is not desired, MSSP interrupts should be disabled.

If the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the device wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in any power-managed mode and data to be shifted into the SPI Transmit/Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set, and if enabled, will wake the device.

# 21.3.10 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 21.3.11 BUS MODE COMPATIBILITY

Table 21-1 shows the compatibility between the standard SPI modes, and the states of the CKP and CKE control bits.

| Standard SPI Mode | Control Bits State |     |  |  |  |

|-------------------|--------------------|-----|--|--|--|

| Terminology       | СКР                | CKE |  |  |  |

| 0, 0              | 0                  | 1   |  |  |  |

| 0, 1              | 0                  | 0   |  |  |  |

| 1, 0              | 1                  | 1   |  |  |  |

| 1, 1              | 1                  | 0   |  |  |  |

#### TABLE 21-1: SPI BUS MODES

There is also an SMP bit which controls when the data is sampled.

| Name    | Bit 7     | Bit 6           | Bit 5        | Bit 4  | Bit 3  | Bit 2   | Bit 1   | Bit 0  |

|---------|-----------|-----------------|--------------|--------|--------|---------|---------|--------|

| INTCON  | GIE/GIEH  | PEIE/GIEL       | TMR0IE       | INT0IE | RBIE   | TMR0IF  | INT0IF  | RBIF   |

| PIR1    | PSPIF     | ADIF            | RC1IF        | TX1IF  | SSPIF  | TMR1GIF | TMR2IF  | TMR1IF |

| PIE1    | PSPIE     | ADIE            | RC1IE        | TX1IE  | SSPIE  | TMR1GIE | TMR2IE  | TMR1IE |

| IPR1    | PSPIP     | ADIP            | RC1IP        | TX1IP  | SSPIP  | TMR1GIP | TMR2IP  | TMR1IP |

| TRISA   | TRISA7    | TRISA6          | TRISA5       |        | TRISA3 | TRISA2  | TRISA1  | TRISA0 |

| TRISC   | TRISC7    | TRISC6          | TRISC5       | TRISC4 | TRISC3 | TRISC2  | TRISC1  | TRISC0 |

| SSPBUF  | MSSP Rece | eive Buffer/Tra | ansmit Regis | ter    |        |         |         |        |

| SSPCON1 | WCOL      | SSPOV           | SSPEN        | CKP    | SSPM3  | SSPM2   | SSPM1   | SSPM0  |

| SSPSTAT | SMP       | CKE             | D/Ā          | Р      | S      | R/W     | UA      | BF     |

| ODCON   | SSPOD     | CCP5OD          | CCP4OD       | CCP3OD | CCP2OD | CCP10D  | U2OD    | U10D   |

| PMD0    | CCP5MD    | CCP4MD          | CCP3MD       | CCP2MD | CCP1MD | UART2MD | UART1MD | SSPMD  |

#### TABLE 21-2: REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: Shaded cells are not used by the MSSP module in SPI mode.

#### EXAMPLE 27-3: TRANSMITTING A CAN MESSAGE USING BANKED METHOD

```

; Need to transmit Standard Identifier message 123h using TXBO buffer.

; To successfully transmit, CAN module must be either in Normal or Loopback mode.

; TXBO buffer is not in access bank. And since we want banked method, we need to make sure

; that correct bank is selected.

BANKSEL TXB0CON

; One BANKSEL in beginning will make sure that we are

; in correct bank for rest of the buffer access.

; Now load transmit data into TXB0 buffer.

MOVLW MY_DATA_BYTE1

; Load first data byte into buffer

MOVWF TXB0D0

; Compiler will automatically set "BANKED" bit

; Load rest of data bytes - up to 8 bytes into TXBO buffer.

. . .

; Load message identifier

MOVLW 60H

; Load SID2:SID0, EXIDE = 0

MOVWF TXB0SIDL

MOVLW 24H

; Load SID10:SID3

MOVWF TXB0SIDH

; No need to load TXB0EIDL:TXB0EIDH, as we are transmitting Standard Identifier Message only.

; Now that all data bytes are loaded, mark it for transmission.

MOVLW B'00001000'

; Normal priority; Request transmission

MOVWF TXB0CON

; If required, wait for message to get transmitted

BTFSC TXB0CON, TXREQ

; Is it transmitted?

BRA

$-2

; No. Continue to wait...

; Message is transmitted.

```

| Mode 0                                                                                                                                                                                     | R/C-0                                   | R/W-0            | R/W-0                               | U-0            | R-0            | R/W-0           | R-0            | R-0     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------|-------------------------------------|----------------|----------------|-----------------|----------------|---------|

| Mode 0                                                                                                                                                                                     | RXFUL <sup>(1)</sup>                    | RXM1             | RXM0                                |                | RXRTRRO        | FILHIT2         | FILHIT1        | FILHIT0 |

|                                                                                                                                                                                            | -                                       |                  |                                     |                |                |                 |                |         |

| Mode 1,2                                                                                                                                                                                   | R/C-0                                   | R/W-0            | R-0                                 | R-0            | R-0            | R-0             | R-0            | R-0     |

|                                                                                                                                                                                            | RXFUL <sup>(1)</sup>                    | RXM1             | RTRRO                               | FILHIT4        | FILHIT3        | FILHIT2         | FILHIT1        | FILHIT0 |

|                                                                                                                                                                                            | bit 7                                   |                  |                                     |                |                |                 |                | bit (   |

| Legend:                                                                                                                                                                                    |                                         |                  | C = Clearabl                        | e bit          |                |                 |                |         |

| R = Readable bit $W = Writable bit$ $U = Unimplemented bit, read as '0'R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'W = Writable bitW = Writable bitW = Writable bit$ |                                         |                  |                                     |                |                |                 |                |         |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown                                                                                                                 |                                         |                  |                                     |                |                |                 | known          |         |

| L:1 7                                                                                                                                                                                      | RXFUL: Rece                             |                  |                                     |                |                |                 |                |         |

| bit 7                                                                                                                                                                                      |                                         |                  |                                     |                |                |                 |                |         |

|                                                                                                                                                                                            |                                         |                  | is a received n<br>i to receive a r |                | е              |                 |                |         |

| bit 6-5, 6                                                                                                                                                                                 | Mode 0:                                 |                  |                                     |                |                |                 |                |         |

|                                                                                                                                                                                            |                                         |                  | er Mode bit 1 (d                    |                |                |                 |                | t 5)    |

|                                                                                                                                                                                            |                                         |                  | s (including th<br>essages with e   |                |                |                 |                | 1'      |

|                                                                                                                                                                                            |                                         |                  | essages with                        |                |                |                 |                |         |

|                                                                                                                                                                                            |                                         |                  | sages as per                        |                |                |                 |                |         |

|                                                                                                                                                                                            | <u>Mode 1, 2:</u><br><b>RXM1:</b> Recei | ve Buffer Mo     | de hit                              |                |                |                 |                |         |

|                                                                                                                                                                                            |                                         |                  | (including tho                      | se with erro   | rs): acceptanc | e filters are i | anored         |         |

|                                                                                                                                                                                            |                                         |                  | ages as per a                       |                |                |                 | gnored         |         |

| bit 5                                                                                                                                                                                      | Mode 0:                                 |                  |                                     |                |                |                 |                |         |

|                                                                                                                                                                                            |                                         | Receive Buffe    | er Mode bit 0 (o                    | combines wi    | th RXM1 to fo  | orm RXM<1:0     | > bits, see bi | t 6)    |

|                                                                                                                                                                                            | Mode 1, 2:<br>RTRRO: Ren                | note Transmi     | ssion Request                       | hit for Rece   | eived Messag   | e (read-only)   |                |         |

|                                                                                                                                                                                            |                                         |                  | request is rec                      |                |                |                 |                |         |

|                                                                                                                                                                                            |                                         |                  | request is no                       |                |                |                 |                |         |

| bit 4                                                                                                                                                                                      | Mode 0:                                 |                  |                                     |                |                |                 |                |         |

|                                                                                                                                                                                            | FILHIT24: Fil<br>Mode 1. 2:             | ter Hit bit 4    |                                     |                |                |                 |                |         |