#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | ECANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 35                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.6K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                 |

| Data Converters            | A/D 11x12b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

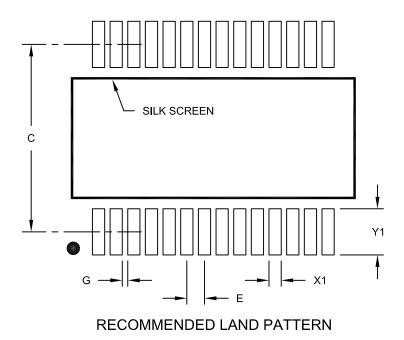

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f46k80t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

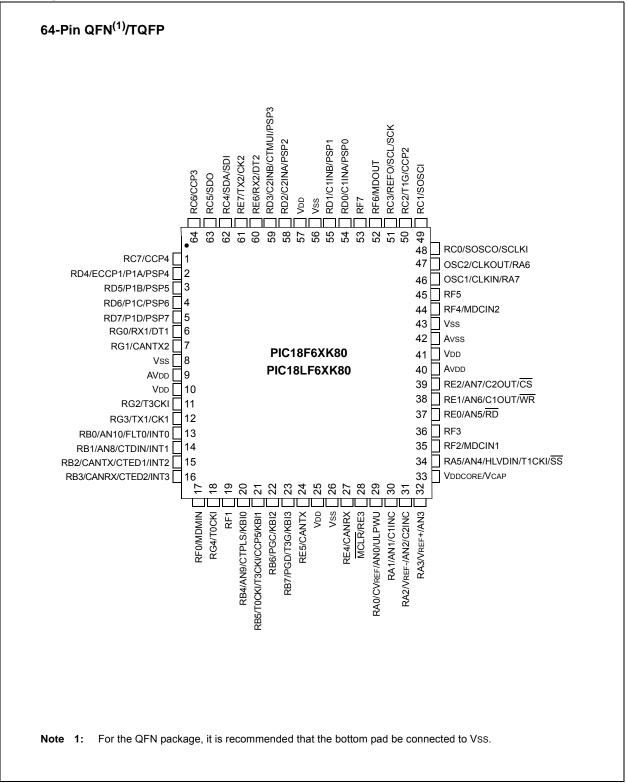

## **Pin Diagrams (Continued)**

## TABLE 1-3: DEVICE FEATURES FOR THE PIC18F6XK80 (64-PIN DEVICES)

| Features                             | PIC18F65K80                                                                        | PIC18F66K80                   |  |  |

|--------------------------------------|------------------------------------------------------------------------------------|-------------------------------|--|--|

| Operating Frequency                  | DC – 64 MHz                                                                        |                               |  |  |

| Program Memory (Bytes)               | 32K                                                                                | 64K                           |  |  |

| Program Memory (Instructions)        | 16,384                                                                             | 32,768                        |  |  |

| Data Memory (Bytes)                  | 3                                                                                  | .6K                           |  |  |

| Interrupt Sources                    |                                                                                    | 32                            |  |  |

| I/O Ports                            | Ports A, B, C, D, E, F, G                                                          |                               |  |  |

| Parallel Communications              | Parallel Slave Port (PSP)                                                          |                               |  |  |

| Timers                               | Five                                                                               |                               |  |  |

| Comparators                          | Тwo                                                                                |                               |  |  |

| CTMU                                 | Ŋ                                                                                  | /es                           |  |  |

| Capture/Compare/PWM (CCP)<br>Modules | F                                                                                  | our                           |  |  |

| Enhanced CCP (ECCP) Modules          | C                                                                                  | Dne                           |  |  |

| DSM                                  | Yes                                                                                | Yes                           |  |  |

| Serial Communications                | One MSSP and Two Enh                                                               | anced USARTs (EUSART)         |  |  |

| 12-Bit Analog-to-Digital Module      | Eleven Input Channels                                                              |                               |  |  |

| Resets (and Delays)                  | POR, BOR, RESET Instruction, Stack Full, Stack Underflow, MCLR,<br>WDT (PWRT, OST) |                               |  |  |

| Instruction Set                      | 75 Instructions, 83 with Exte                                                      | ended Instruction Set Enabled |  |  |

| Packages                             | 64-Pin QF                                                                          | N and TQFP                    |  |  |

## 4.1.3 CLOCK TRANSITIONS AND STATUS INDICATORS

The length of the transition between clock sources is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable. The HF-INTOSC and MF-INTOSC are termed as INTOSC in this chapter.

Three bits indicate the current clock source and its status, as shown in Table 4-2. The three bits are:

- OSTS (OSCCON<3>)

- HFIOFS (OSCCON<2>)

- SOSCRUN (OSCCON2<6>)

TABLE 4-2:

SYSTEM CLOCK INDICATOR

| Main Clock Source                                      | OSTS | HFIOFS or<br>MFIOFS | SOSCRUN |

|--------------------------------------------------------|------|---------------------|---------|

| Primary Oscillator                                     | 1    | 0                   | 0       |

| INTOSC (HF-INTOSC<br>or MF-INTOSC)                     | 0    | 1                   | 0       |

| Secondary Oscillator                                   | 0    | 0                   | 1       |

| MF-INTOSC or<br>HF-INTOSC as Primary<br>Clock Source   | 1    | 1                   | 0       |

| LF-INTOSC is<br>Running or INTOSC is<br>Not Yet Stable | 0    | 0                   | 0       |

When the OSTS bit is set, the primary clock is providing the device clock. When the HFIOFS or MFIOFS bit is set, the INTOSC output is providing a stable clock source to a divider that actually drives the device clock. When the SOSCRUN bit is set, the SOSC oscillator is providing the clock. If none of these bits are set, either the LF-INTOSC clock source is clocking the device or the INTOSC source is not yet stable.

If the internal oscillator block is configured as the primary clock source by the FOSC<3:0> Configuration bits (CONFIG1H<3:0>). Then, the OSTS and HFIOFS or MFIOFS bits can be set when in PRI\_RUN or PRI\_IDLE mode. This indicates that the primary clock (INTOSC output) is generating a stable output. Entering another INTOSC power-managed mode at the same frequency would clear the OSTS bit.

- Note 1: Caution should be used when modifying a single IRCF bit. At a lower VDD, it is possible to select a higher clock speed than is supportable by that VDD. Improper device operation may result if the VDD/ Fosc specifications are violated.

- 2: Executing a SLEEP instruction does not necessarily place the device into Sleep mode. It acts as the trigger to place the controller into either the Sleep mode, or one of the Idle modes, depending on the setting of the IDLEN bit.

## 4.1.4 MULTIPLE SLEEP COMMANDS

The power-managed mode that is invoked with the SLEEP instruction is determined by the setting of the IDLEN bit at the time the instruction is executed. If another SLEEP instruction is executed, the device will enter the power-managed mode specified by IDLEN at that time. If IDLEN has changed, the device will enter the new power-managed mode specified by the new setting.

## 4.2 Run Modes

In the Run modes, clocks to both the core and peripherals are active. The difference between these modes is the clock source.

## 4.2.1 PRI\_RUN MODE

The PRI\_RUN mode is the normal, full-power execution mode of the microcontroller. This is also the default mode upon a device Reset, unless Two-Speed Start-up is enabled. (For details, see **Section 28.4 "Two-Speed Start-up"**.) In this mode, the OSTS bit is set. The HFIOFS or MFIOFS bit may be set if the internal oscillator block is the primary clock source. (See **Section 3.2 "Control Registers"**.)

## 4.2.2 SEC\_RUN MODE

The SEC\_RUN mode is the compatible mode to the "clock-switching" feature offered in other PIC18 devices. In this mode, the CPU and peripherals are clocked from the SOSC oscillator. This enables lower power consumption while retaining a high-accuracy clock source.

SEC\_RUN mode is entered by setting the SCS<1:0> bits to '01'. The device clock source is switched to the SOSC oscillator (see Figure 4-1), the primary oscillator is shut down, the SOSCRUN bit (OSCCON2<6>) is set and the OSTS bit is cleared.

| Note: | The SOSC oscillator can be enabled by setting the SOSCGO bit (OSCCON2<3>). If this bit is set, the clock switch to the SEC_RUN mode can switch immediately |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | once SCS<1:0> are set to '01'.                                                                                                                             |

On transitions from SEC\_RUN mode to PRI\_RUN mode, the peripherals and CPU continue to be clocked from the SOSC oscillator while the primary clock is started. When the primary clock becomes ready, a clock switch back to the primary clock occurs (see Figure 4-2). When the clock switch is complete, the SOSCRUN bit is cleared, the OSTS bit is set and the primary clock is providing the clock. The IDLEN and SCSx bits are not affected by the wake-up and the SOSC oscillator continues to run.

## 6.1.2 PROGRAM COUNTER

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide and contained in three separate 8-bit registers.

The low byte, known as the PCL register, is both readable and writable. The high byte, or PCH register, contains the PC<15:8> bits and is not directly readable or writable. Updates to the PCH register are performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCU register are performed through the PCLATU register.

The contents of PCLATH and PCLATU are transferred to the Program Counter by any operation that writes PCL. Similarly, the upper two bytes of the Program Counter are transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 6.1.5.1 "Computed** GOTO").

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the Least Significant bit (LSb) of PCL is fixed to a value of '0'. The PC increments by two to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the Program Counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the Program Counter.

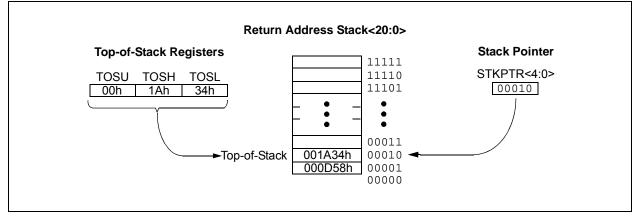

## 6.1.3 RETURN ADDRESS STACK

The return address stack enables execution of any combination of up to 31 program calls and interrupts. The PC is pushed onto the stack when a CALL or RCALL instruction is executed or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or a RETFIE instruction. The value is also pulled off the stack on ADDULNK and SUBULNK instructions if the extended instruction set is enabled. PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions.

The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer, STKPTR. The stack space is not part of either program or data space. The Stack Pointer is readable and writable and the address on the top of the stack is readable and writable through the Top-of-Stack (TOS) Special Function Registers. Data can also be pushed to, or popped from the stack, using these registers.

A CALL type instruction causes a push onto the stack. The Stack Pointer is first incremented and the location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction following the CALL). A RETURN type instruction causes a pop from the stack. The contents of the location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The Stack Pointer is initialized to '00000' after all Resets. There is no RAM associated with the location corresponding to a Stack Pointer value of '00000'; this is only a Reset value. Status bits indicate if the stack is full, has overflowed or has underflowed.

## 6.1.3.1 Top-of-Stack Access

Only the top of the return address stack is readable and writable. A set of three registers, TOSU:TOSH:TOSL, holds the contents of the stack location pointed to by the STKPTR register (Figure 6-3). This allows users to implement a software stack, if necessary. After a CALL, RCALL or interrupt (or ADDULNK and SUBULNK instructions, if the extended instruction set is enabled), the software can read the pushed value by reading the TOSU:TOSH:TOSL registers. These values can be placed on a user-defined software stack. At return time, the software can return these values to TOSU:TOSH:TOSL and do a return.

While accessing the stack, users must disable the Global Interrupt Enable bits to prevent inadvertent stack corruption.

## FIGURE 6-3: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

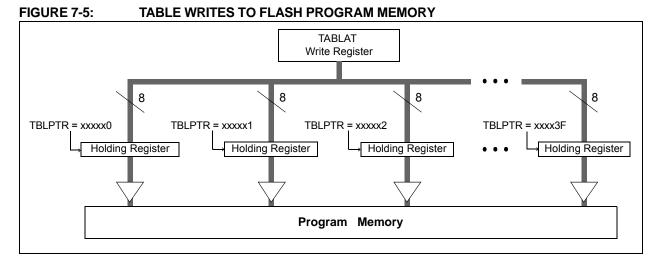

## 7.5 Writing to Flash Program Memory

The programming blocks are 32 words or 64 bytes.

Word or byte programming is not supported.

Table writes are used internally to load the holding registers needed to program the Flash memory. There are 64 holding registers for programming by the table writes.

Since the Table Latch (TABLAT) is only a single byte, the TBLWT instruction may need to be executed 64 times for each programming operation. All of the table write operations will essentially be short writes because only the holding registers are written. At the end of updating the 64 or 128 holding registers, the EECON1 register must be written to in order to start the programming operation with a long write.

The long write is necessary for programming the internal Flash. Instruction execution is halted while in a long write cycle. The long write is terminated by the internal programming timer. The EEPROM on-chip timer controls the write time. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device.

Note: The default value of the holding registers on device Resets and after write operations is FFh. A write of FFh to a holding register does not modify that byte. This means that individual bytes of program memory may be modified, provided that the change does not attempt to change any bit from a '0' to a '1'. When modifying individual bytes, it is not necessary to load all 64 holding registers before executing a write operation.

## 7.5.1 FLASH PROGRAM MEMORY WRITE SEQUENCE

The sequence of events for programming an internal program memory location should be:

- 1. Read the 64 bytes into RAM.

- 2. Update the data values in RAM as necessary.

- 3. Load the Table Pointer register with the address being erased.

- 4. Execute the row erase procedure.

- 5. Load the Table Pointer register with the address of the first byte being written.

- 6. Write the 64 bytes into the holding registers with auto-increment.

- 7. Set the EECON1 register for the write operation:

- Set the EEPGD bit to point to program memory

- · Clear the CFGS bit to access program memory

- · Set the WREN to enable byte writes

- 8. Disable the interrupts.

- 9. Write 55h to EECON2.

- 10. Write 0AAh to EECON2.

- Set the WR bit. This will begin the write cycle. The CPU will stall for the duration of the write for Tiw (see Parameter D133A).

- 12. Re-enable the interrupts.

- 13. Verify the memory (table read).

An example of the required code is shown in Example 7-3 on the following page.

Note: Before setting the WR bit, the Table Pointer address needs to be within the intended address range of the 64 bytes in the holding register.

| Name    | Bit 7       | Bit 6          | Bit 5   | Bit 4   | Bit 3            | Bit 2   | Bit 1  | Bit 0   |

|---------|-------------|----------------|---------|---------|------------------|---------|--------|---------|

| INTCON  | GIE/GIEH    | PEIE/GIEL      | TMR0IE  | INT0IE  | RBIE             | TMR0IF  | INT0IF | RBIF    |

| PIR1    | PSPIF       | ADIF           | RC1IF   | TX1IF   | SSPIF            | TMR1GIF | TMR2IF | TMR1IF  |

| PIE1    | PSPIE       | ADIE           | RC1IE   | TX1IE   | SSPIE            | TMR1GIE | TMR2IE | TMR1IE  |

| IPR1    | PSPIP       | ADIP           | RC1IP   | TX1IP   | SSPIP            | TMR1GIP | TMR2IP | TMR1IP  |

| TMR1L   | Timer1 Regi | ster Low Byte  | 9       |         |                  |         |        |         |

| TMR1H   | Timer1 Regi | ster High Byte | е       |         |                  |         |        |         |

| T1CON   | TMR1CS1     | TMR1CS0        | T1CKPS1 | T1CKPS0 | SOSCEN           | T1SYNC  | RD16   | TMR10N  |

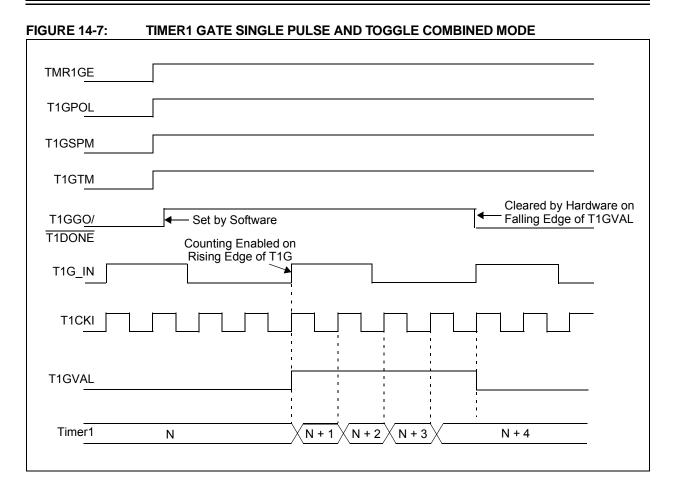

| T1GCON  | TMR1GE      | T1GPOL         | T1GTM   | T1GSPM  | T1GGO/<br>T1DONE | T1GVAL  | T1GSS1 | T1GSS0  |

| OSCCON2 | _           | SOSCRUN        | _       | SOSCDRV | SOSCGO           |         | MFIOFS | MFIOSEL |

| PMD1    | PSPMD       | CTMUMD         | ADCMD   | TMR4MD  | TMR3MD           | TMR2MD  | TMR1MD | TMR0MD  |

Legend: Shaded cells are not used by the Timer1 module.

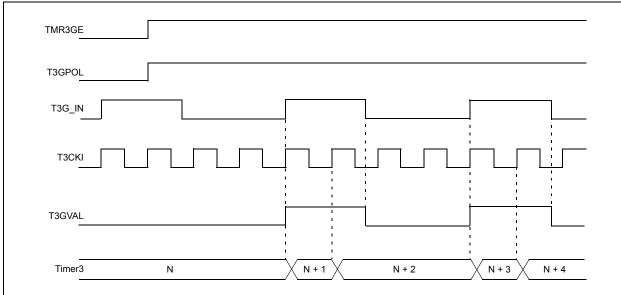

## 16.5 Timer3 Gates

Timer3 can be configured to count freely or the count can be enabled and disabled using the Timer3 gate circuitry. This is also referred to as the Timer3 gate count enable.

The Timer3 gate can also be driven by multiple selectable sources.

## 16.5.1 TIMER3 GATE COUNT ENABLE

The Timer3 Gate Enable mode is enabled by setting the TMR3GE bit (TxGCON<7>). The polarity of the Timer3 Gate Enable mode is configured using the T3GPOL bit (T3GCON<6>).

When Timer3 Gate Enable mode is enabled, Timer3 will increment on the rising edge of the Timer3 clock source. When Timer3 Gate Enable mode is disabled, no incrementing will occur and Timer3 will hold the current count. See Figure 16-2 for timing details.

## TABLE 16-1: TIMER3 GATE ENABLE SELECTIONS

| T3CLK <sup>(†)</sup> | T3GPOL<br>(T3GCON<6>) | T3G Pin | Timer3<br>Operation |

|----------------------|-----------------------|---------|---------------------|

| 1                    | 0                     | 0       | Counts              |

| $\uparrow$           | 0                     | 1       | Holds Count         |

| $\uparrow$           | 1                     | 0       | Holds Count         |

| $\uparrow$           | 1                     | 1       | Counts              |

† The clock on which TMR3 is running. For more information, see T3CLK in Figure 16-1.

## FIGURE 16-2: TIMER3 GATE COUNT ENABLE MODE

## REGISTER 21-3: SSPSTAT: MSSP STATUS REGISTER (I<sup>2</sup>C<sup>™</sup> MODE)

| R/W-0      | R/W-0                                      | R-0                             | R-0                          | R-0              | R-0                  | R-0               | R-0      |  |  |  |  |

|------------|--------------------------------------------|---------------------------------|------------------------------|------------------|----------------------|-------------------|----------|--|--|--|--|

| SMP        | CKE                                        | D/A                             | P <sup>(1)</sup>             | S <sup>(1)</sup> | R/W <sup>(2,3)</sup> | UA                | BF       |  |  |  |  |

| bit 7      |                                            | - 1                             | 1                            |                  | •                    |                   | bit C    |  |  |  |  |

|            |                                            |                                 |                              |                  |                      |                   |          |  |  |  |  |

| Legend:    |                                            |                                 |                              |                  |                      |                   |          |  |  |  |  |

| R = Reada  | able bit                                   | W = Writable                    | bit                          | U = Unimple      | mented bit, read     | as '0'            |          |  |  |  |  |

| -n = Value | at POR                                     | '1' = Bit is set                | t                            | '0' = Bit is cle | eared                | x = Bit is unkr   | nown     |  |  |  |  |

|            |                                            |                                 |                              |                  |                      |                   |          |  |  |  |  |

| bit 7      |                                            | Rate Control bit                |                              |                  |                      |                   |          |  |  |  |  |

|            |                                            | <u>Slave mode:</u>              | abled for Stand              | lard Speed mo    | de (100 kHz and      | 1 MHz)            |          |  |  |  |  |

|            |                                            | ite control is ena              |                              |                  |                      | 1 1011 12)        |          |  |  |  |  |

| bit 6      | CKE: SMBu                                  |                                 | 0                            | I V              | ,                    |                   |          |  |  |  |  |

|            | In Master or                               | Slave mode:                     |                              |                  |                      |                   |          |  |  |  |  |

|            |                                            | SMBus specific                  |                              |                  |                      |                   |          |  |  |  |  |

|            |                                            | s SMBus specifi                 | c inputs                     |                  |                      |                   |          |  |  |  |  |

| bit 5      | D/A: Data/A                                |                                 |                              |                  |                      |                   |          |  |  |  |  |

|            | In Master m<br>Reserved.                   | In Master mode:<br>Reserved     |                              |                  |                      |                   |          |  |  |  |  |

|            | In Slave mo                                | de:                             |                              |                  |                      |                   |          |  |  |  |  |

|            |                                            | s that the last by              | te received or               | transmitted wa   | as data              |                   |          |  |  |  |  |

|            |                                            | s that the last by              | te received or               | transmitted wa   | as address           |                   |          |  |  |  |  |

| bit 4      | P: Stop bit <sup>(1</sup>                  | )                               |                              |                  |                      |                   |          |  |  |  |  |

|            |                                            | s that a Stop bit               |                              | ected last       |                      |                   |          |  |  |  |  |

| bit 3      | 0 = Stop bit<br>S: Start bit <sup>(1</sup> | was not detecte                 | ulasi                        |                  |                      |                   |          |  |  |  |  |

| DILS       |                                            | ,<br>s that a Start bit         | has been dete                | acted last       |                      |                   |          |  |  |  |  |

|            |                                            | was not detecte                 |                              |                  |                      |                   |          |  |  |  |  |

| bit 2      | R/W: Read/                                 | Write Informatio                | n bit <sup>(2,3)</sup>       |                  |                      |                   |          |  |  |  |  |

|            | In Slave mo                                | <u>de:</u>                      |                              |                  |                      |                   |          |  |  |  |  |

|            | 1 <b>= Read</b>                            |                                 |                              |                  |                      |                   |          |  |  |  |  |

|            | 0 = Write                                  |                                 |                              |                  |                      |                   |          |  |  |  |  |

|            | <u>In Master m</u><br>1 = Transmi          | <u>ode:</u><br>t is in progress |                              |                  |                      |                   |          |  |  |  |  |

|            |                                            | t is not in progre              | ss                           |                  |                      |                   |          |  |  |  |  |

| bit 1      | UA: Update                                 | Address bit (10                 | -Bit Slave mod               | le only)         |                      |                   |          |  |  |  |  |

|            | 1 = Indicate                               | s that the user n               | eeds to update               | e the address i  | n the SSPADD r       | egister           |          |  |  |  |  |

|            | 0 = Address                                | does not need                   | to be updated                |                  |                      |                   |          |  |  |  |  |

| bit 0      |                                            | ull Status bit                  |                              |                  |                      |                   |          |  |  |  |  |

|            | In Transmit                                |                                 |                              |                  |                      |                   |          |  |  |  |  |

|            | 1 = SSPBUI<br>0 = SSPBUI                   |                                 |                              |                  |                      |                   |          |  |  |  |  |

|            | In Receive r                               |                                 |                              |                  |                      |                   |          |  |  |  |  |

|            |                                            | F is full (does no              | t include the $\overline{A}$ | KCK and Stop t   | oits)                |                   |          |  |  |  |  |

|            | 0 = SSPBUI                                 | F is empty (does                | s not include th             | ACK and Sto      | op bits)             |                   |          |  |  |  |  |

| Note 1:    | This bit is cleare                         | ed on Reset and                 | when SSPEN                   | is cleared.      |                      |                   |          |  |  |  |  |

| 2:         |                                            |                                 |                              |                  | ess match. This b    | oit is only valid | from the |  |  |  |  |

|            | address match t                            |                                 |                              |                  |                      | -                 |          |  |  |  |  |

|            |                                            |                                 |                              |                  |                      |                   |          |  |  |  |  |

3: ORing this bit with SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSP is in Active mode.

| R/W-0      | R/W-0                                  | R/W-0                                                                                                                      | R/W-0          | R/W-0                | R/W-0                  | R/W-0                | R/W-0                |  |  |

|------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------|----------------------|------------------------|----------------------|----------------------|--|--|

| WCOL       | SSPOV                                  | SSPEN <sup>(1)</sup>                                                                                                       | CKP            | SSPM3 <sup>(2)</sup> | SSPM2 <sup>(2)</sup>   | SSPM1 <sup>(2)</sup> | SSPM0 <sup>(2)</sup> |  |  |

| bit 7      | I                                      |                                                                                                                            |                |                      |                        |                      | bit 0                |  |  |

| Legend:    |                                        |                                                                                                                            |                |                      |                        |                      |                      |  |  |

| R = Reada  | able bit                               | W = Writable                                                                                                               | bit            | U = Unimplen         | nented bit, read       | d as '0'             |                      |  |  |

| -n = Value | at POR                                 | '1' = Bit is set                                                                                                           |                | '0' = Bit is clea    |                        | x = Bit is unkr      | nown                 |  |  |

|            |                                        |                                                                                                                            |                |                      |                        |                      |                      |  |  |

| bit 7      | WCOL: Write                            | e Collision Dete                                                                                                           | ct bit         |                      |                        |                      |                      |  |  |

|            | In Master Tra                          |                                                                                                                            |                |                      |                        |                      |                      |  |  |

|            |                                        | to the SSPBUR                                                                                                              |                |                      |                        | nditions were i      | not valid for a      |  |  |

|            | 0 = No collis                          | sion to be starte                                                                                                          | ea (must be ci | eared in softwar     | e)                     |                      |                      |  |  |

|            | In Slave Trar                          |                                                                                                                            |                |                      |                        |                      |                      |  |  |

|            |                                        | PBUF register is                                                                                                           | written while  | it is still transm   | itting the previ       | ous word (mus        | t be cleared in      |  |  |

|            | software                               | ,                                                                                                                          |                |                      |                        |                      |                      |  |  |

|            | 0 = No collis                          |                                                                                                                            |                |                      |                        |                      |                      |  |  |

|            | In Receive m<br>This is a "dor         | node (Master or                                                                                                            | Slave modes    | <u>):</u>            |                        |                      |                      |  |  |

| bit 6      |                                        | ceive Overflow li                                                                                                          | ndicator hit   |                      |                        |                      |                      |  |  |

|            | In Receive m                           |                                                                                                                            |                |                      |                        |                      |                      |  |  |

|            |                                        | received while                                                                                                             | the SSPBUF     | register is still h  | olding the prev        | vious byte (mus      | t be cleared in      |  |  |

|            | software                               | /                                                                                                                          |                |                      |                        |                      |                      |  |  |

|            | 0 = No over                            |                                                                                                                            |                |                      |                        |                      |                      |  |  |

|            | <u>In Transmit n</u><br>This is a "dor | <u>node:</u><br>n't care" bit in Tr                                                                                        | ansmit mode    |                      |                        |                      |                      |  |  |

| bit 5      |                                        | ster Synchronou                                                                                                            |                |                      |                        |                      |                      |  |  |

| bit 0      |                                        | the serial port a                                                                                                          |                |                      | CL pins as the         | serial port pins     |                      |  |  |

|            |                                        | serial port and                                                                                                            |                |                      |                        |                      |                      |  |  |

| bit 4      | CKP: SCK R                             | elease Control                                                                                                             | bit            |                      |                        |                      |                      |  |  |

|            | In Slave mod                           |                                                                                                                            |                |                      |                        |                      |                      |  |  |

|            |                                        | 1 = Releases clock                                                                                                         |                |                      |                        |                      |                      |  |  |

|            |                                        | 0 = Holds clock low (clock stretch), used to ensure data setup time<br>In Master mode:                                     |                |                      |                        |                      |                      |  |  |

|            | Unused in th                           |                                                                                                                            |                |                      |                        |                      |                      |  |  |

| bit 3-0    | SSPM<3:0>:                             | : Master Synchr                                                                                                            | onous Serial I | Port Mode Selec      | ct bits <sup>(2)</sup> |                      |                      |  |  |

|            | 1111 = I <sup>2</sup> C S              | Slave mode, 10-                                                                                                            | bit address wi | th Start and Sto     | p bit interrupts       |                      |                      |  |  |

|            |                                        | Slave mode, 7-b                                                                                                            |                |                      |                        | nabled               |                      |  |  |

|            |                                        | Firmware Contro                                                                                                            |                |                      |                        |                      |                      |  |  |

|            |                                        | I SSPMSK regis                                                                                                             |                |                      |                        |                      |                      |  |  |

|            |                                        | 1000 = I <sup>2</sup> C Master mode, clock = Fosc/(4 * (SSPADD + 1))<br>0111 = I <sup>2</sup> C Slave mode, 10-bit address |                |                      |                        |                      |                      |  |  |

|            | 0110 = I <sup>2</sup> C S              | Slave mode, 7-b                                                                                                            | it address     |                      |                        |                      |                      |  |  |

| Note 1:    | When enabled, t                        | he SDA and SC                                                                                                              | L pins must b  | e configured as      | inputs.                |                      |                      |  |  |

| 2:         | Bit combinations                       |                                                                                                                            |                | -                    | -                      | ed in SPI mode       | e only.              |  |  |

| 3:         | When SSPM<3:0                          |                                                                                                                            |                |                      |                        |                      | •                    |  |  |

|            | SSPMSK registe                         |                                                                                                                            |                |                      |                        |                      |                      |  |  |

| 4:         | This mode is only                      | y available whe                                                                                                            | n 7-Bit Addres | s Masking mod        | e is selected (N       | ASSPMSK Cor          | figuration bit       |  |  |

|            | is '1').                               |                                                                                                                            |                |                      |                        |                      |                      |  |  |

## REGISTER 21-4: SSPCON1: MSSP CONTROL REGISTER 1 (I<sup>2</sup>C<sup>™</sup> MODE)

| R/W-0        | R/W-0                             | R/W-0                                                                                                                                         | R/W-0                | R/W-0                       | R/W-0              | R/W-0               | R/W-0              |  |  |

|--------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------|--------------------|---------------------|--------------------|--|--|

| GCEN         | ACKSTAT                           | ACKDT <sup>(1)</sup>                                                                                                                          | ACKEN <sup>(2)</sup> | RCEN <sup>(2)</sup>         | PEN <sup>(2)</sup> | RSEN <sup>(2)</sup> | SEN <sup>(2)</sup> |  |  |

| bit 7        |                                   |                                                                                                                                               |                      |                             |                    |                     | bit                |  |  |

|              |                                   |                                                                                                                                               |                      |                             |                    |                     |                    |  |  |

| Legend:      | 1- 1-14                           |                                                                                                                                               | L .1                 |                             |                    | -l (O)              |                    |  |  |

| R = Readab   |                                   | W = Writable                                                                                                                                  |                      | •                           | nented bit, read   |                     |                    |  |  |

| -n = Value a | IT POR                            | '1' = Bit is set                                                                                                                              |                      | '0' = Bit is clea           | ared               | x = Bit is unkn     | own                |  |  |

| bit 7        | GCEN: Gene                        | eral Call Enable                                                                                                                              | bit                  |                             |                    |                     |                    |  |  |

|              | Unused in M                       |                                                                                                                                               |                      |                             |                    |                     |                    |  |  |

| bit 6        | ACKSTAT: A                        | cknowledge Sta                                                                                                                                | itus bit (Mastei     | r Transmit mod              | e only)            |                     |                    |  |  |

|              |                                   | ACKSTAT: Acknowledge Status bit (Master Transmit mode only)<br>1 = Acknowledge was not received from slave                                    |                      |                             |                    |                     |                    |  |  |

|              | 0 = Acknowle                      | edge was receiv                                                                                                                               | ed from slave        |                             |                    |                     |                    |  |  |

| bit 5        | ACKDT: Ack                        | nowledge Data                                                                                                                                 | bit (Master Re       | ceive mode onl              | y) <sup>(1)</sup>  |                     |                    |  |  |

|              | 1 = Not Ackn                      |                                                                                                                                               |                      |                             |                    |                     |                    |  |  |

|              | 0 = Acknowle                      | •                                                                                                                                             |                      | (2)                         |                    |                     |                    |  |  |

| bit 4        |                                   | ACKEN: Acknowledge Sequence Enable bit <sup>(2)</sup><br>1 = Initiates Acknowledge sequence on SDA and SCL pins and transmits ACKDT data bit; |                      |                             |                    |                     |                    |  |  |

|              |                                   | ically cleared by                                                                                                                             |                      | SDA and St                  | JE pins and        | transmits ACK       | DI Uala D          |  |  |

|              |                                   | edge sequence                                                                                                                                 |                      |                             |                    |                     |                    |  |  |

| bit 3        | RCEN: Rece                        | vive Enable bit (                                                                                                                             | Master Receive       | e mode only) <sup>(2)</sup> |                    |                     |                    |  |  |

|              |                                   | Receive mode f                                                                                                                                | or l <sup>2</sup> C™ |                             |                    |                     |                    |  |  |

|              | 0 = Receive                       |                                                                                                                                               | (2)                  |                             |                    |                     |                    |  |  |

| bit 2        |                                   | ondition Enable                                                                                                                               |                      |                             |                    |                     |                    |  |  |

|              |                                   | Stop condition o                                                                                                                              | n SDA and SC         | L pins; automa              | tically cleared    | by hardware         |                    |  |  |

| bit 1        | •                                 | = Stop condition is Idle<br>SEN: Repeated Start Condition Enable bit <sup>(2)</sup>                                                           |                      |                             |                    |                     |                    |  |  |

|              |                                   |                                                                                                                                               |                      |                             | ns: automatica     | ally cleared by h   | ardware            |  |  |

|              |                                   | d Start condition                                                                                                                             |                      |                             | ,                  |                     |                    |  |  |

| bit 0        | SEN: Start C                      | ondition Enable                                                                                                                               | bit <sup>(2)</sup>   |                             |                    |                     |                    |  |  |

|              | 1 = Initiates \$<br>0 = Start con | Start condition o<br>dition Idle                                                                                                              | n SDA and SC         | L pins; automa              | tically cleared    | by hardware         |                    |  |  |

| Note 1: ⊺    | he value that wi                  | II be transmitted                                                                                                                             | when the user        | · initiates an Acl          | knowledge seq      | uence at the end    | d of a receive     |  |  |

| <b>2:</b> If | f the I <sup>2</sup> C module     | he I <sup>2</sup> C module is active, these bits may not be set (no spooling) and the SSPBUF may not be written to                            |                      |                             |                    |                     |                    |  |  |

2: If the I<sup>2</sup>C module is active, these bits may not be set (no spooling) and the SSPBUF may not be written to (or writes to the SSPBUF are disabled).

| R/W-0       | R/W-0                                                                                                                                                | R/W-0                                  | R/W-0             | R/W-0             | R-0           | R-0             | R-x         |  |  |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------|-------------------|---------------|-----------------|-------------|--|--|--|--|

| SPEN        | RX9                                                                                                                                                  | SREN                                   | CREN              | ADDEN             | FERR          | OERR            | RX9D        |  |  |  |  |

| oit 7       |                                                                                                                                                      |                                        |                   |                   |               |                 | bit         |  |  |  |  |

|             |                                                                                                                                                      |                                        |                   |                   |               |                 |             |  |  |  |  |

| _egend:     |                                                                                                                                                      |                                        |                   |                   |               |                 |             |  |  |  |  |

| R = Readab  | le bit                                                                                                                                               | W = Writable                           |                   | U = Unimplem      |               | d as '0'        |             |  |  |  |  |

| n = Value a | t POR                                                                                                                                                | '1' = Bit is set                       |                   | '0' = Bit is clea | ired          | x = Bit is unkn | iown        |  |  |  |  |

| L:1 7       |                                                                                                                                                      | l Dort Enchlo hi                       |                   |                   |               |                 |             |  |  |  |  |

| bit 7       |                                                                                                                                                      | Il Port Enable bi<br>ort is enabled (c |                   | /DTv and TXv/C    | Ky nine as sa | rial nort nins) |             |  |  |  |  |

|             |                                                                                                                                                      | ort is disabled (h                     |                   |                   |               |                 |             |  |  |  |  |

| oit 6       | <b>RX9:</b> 9-Bit R                                                                                                                                  | eceive Enable b                        | bit               |                   |               |                 |             |  |  |  |  |

|             |                                                                                                                                                      | 9-bit reception                        |                   |                   |               |                 |             |  |  |  |  |

|             |                                                                                                                                                      | 8-bit reception                        |                   |                   |               |                 |             |  |  |  |  |

| bit 5       | •                                                                                                                                                    | e Receive Enab                         | le bit            |                   |               |                 |             |  |  |  |  |

|             | Asynchronou<br>Don't care.                                                                                                                           | <u>is mode</u> .                       |                   |                   |               |                 |             |  |  |  |  |

|             |                                                                                                                                                      | s mode – Maste                         | <u>r:</u>         |                   |               |                 |             |  |  |  |  |

|             |                                                                                                                                                      | single receive                         |                   |                   |               |                 |             |  |  |  |  |

|             |                                                                                                                                                      | s single receive<br>eared after recep  | otion is comple   | te.               |               |                 |             |  |  |  |  |

|             |                                                                                                                                                      | <u>s mode – Slave:</u>                 |                   |                   |               |                 |             |  |  |  |  |

|             | Don't care.                                                                                                                                          |                                        |                   |                   |               |                 |             |  |  |  |  |

| bit 4       |                                                                                                                                                      | inuous Receive                         | Enable bit        |                   |               |                 |             |  |  |  |  |

|             | <u>Asynchronou</u><br>1 = Enables                                                                                                                    |                                        |                   |                   |               |                 |             |  |  |  |  |

|             | 0 = Disables                                                                                                                                         |                                        |                   |                   |               |                 |             |  |  |  |  |

|             | Synchronous mode:                                                                                                                                    |                                        |                   |                   |               |                 |             |  |  |  |  |

|             | <ul> <li>1 = Enables continuous receive until enable bit, CREN, is cleared (CREN overrides SREN)</li> <li>0 = Disables continuous receive</li> </ul> |                                        |                   |                   |               |                 |             |  |  |  |  |

| bit 3       |                                                                                                                                                      | dress Detect En                        |                   |                   |               |                 |             |  |  |  |  |

|             |                                                                                                                                                      | us mode 9-Bit (F                       |                   |                   |               |                 |             |  |  |  |  |

|             | 1 = Enables address detection; enables interrupt and loads the receive buffer when RSR<8> is set                                                     |                                        |                   |                   |               |                 |             |  |  |  |  |

|             | 0 = Disables address detection; all bytes are received and the ninth bit can be used as a parity bit<br><u>Asynchronous mode 9-Bit (RX9 = 0)</u> :   |                                        |                   |                   |               |                 |             |  |  |  |  |

|             | Don't care.                                                                                                                                          |                                        | <u>(79 = 0)</u> . |                   |               |                 |             |  |  |  |  |

| bit 2       | FERR: Fram                                                                                                                                           | ing Error bit                          |                   |                   |               |                 |             |  |  |  |  |

|             | <ul> <li>1 = Framing error (can be cleared by reading the RCREGx register and receiving next valid byte)</li> <li>0 = No framing error</li> </ul>    |                                        |                   |                   |               |                 | valid byte) |  |  |  |  |

| bit 1       | OERR: Over                                                                                                                                           | run Error bit                          |                   |                   |               |                 |             |  |  |  |  |

|             |                                                                                                                                                      | error (can be c                        | eared by clear    | ing bit, CREN)    |               |                 |             |  |  |  |  |

| bit 0       | 0 = No over                                                                                                                                          |                                        | - 4 -             |                   |               |                 |             |  |  |  |  |

|             | <b>RX9D:</b> 9th bit of Received Data                                                                                                                |                                        |                   |                   |               |                 |             |  |  |  |  |

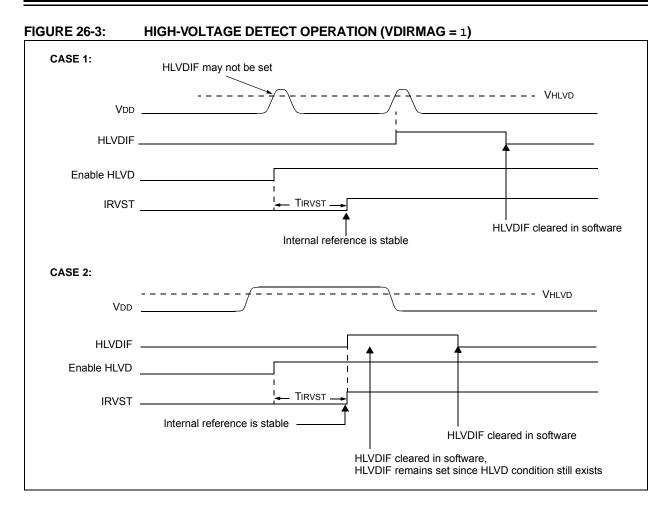

## 26.5 Applications

In many applications, it is desirable to detect a drop below, or rise above, a particular voltage threshold. For example, the HLVD module could be periodically enabled to detect Universal Serial Bus (USB) attach or detach. This assumes the device is powered by a lower voltage source than the USB when detached. An attach would indicate a high-voltage detect from, for example, 3.3V to 5V (the voltage on USB) and vice versa for a detach. This feature could save a design a few extra components and an attach signal (input pin).

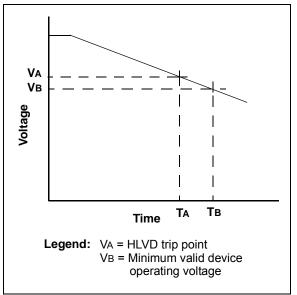

For general battery applications, Figure 26-4 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage, VA, the HLVD logic generates an interrupt at time, TA. The interrupt could cause the execution of an ISR, which would allow the application to perform "house-keeping tasks" and a controlled shutdown before the device voltage exits the valid operating range at TB. This would give the application a time window, represented by the difference between TA and TB, to safely exit.

#### TYPICAL LOW-VOLTAGE DETECT APPLICATION

## EXAMPLE 27-2: WIN AND ICODE BITS USAGE IN INTERRUPT SERVICE ROUTINE TO ACCESS TX/RX BUFFERS (CONTINUED)

| ErrorInter | rupt                      |                                        |

|------------|---------------------------|----------------------------------------|

| BCF        | PIR3, ERRIF               | ; Clear the interrupt flag             |

|            |                           | ; Handle error.                        |

| RETFIE     |                           |                                        |

| TXB2Interr | rupt                      |                                        |

| BCF        | PIR3, TXB2IF              | ; Clear the interrupt flag             |

| GOTO       | AccessBuffer              |                                        |

| TXBlInterr | rupt                      |                                        |

| BCF        | PIR3, TXB1IF              | ; Clear the interrupt flag             |

| GOTO       | AccessBuffer              |                                        |

| TXB0Interr | rupt                      |                                        |

| BCF        | PIR3, TXB0IF              | ; Clear the interrupt flag             |

| GOTO       | AccessBuffer              |                                        |

| RXB1Interr | rupt                      |                                        |

| BCF        | PIR3, RXB1IF              | ; Clear the interrupt flag             |

| GOTO       | Accessbuffer              |                                        |

| RXB0Interr | rupt                      |                                        |

| BCF        | PIR3, RXB0IF              | ; Clear the interrupt flag             |

| GOTO       | AccessBuffer              |                                        |

| AccessBuff | er                        | ; This is either TX or RX interrupt    |

| ; Copy     | CANSTAT.ICODE bits to CA  | NCON.WIN bits                          |

| MOVF       | TempCANCON, W             | ; Clear CANCON.WIN bits before copying |

|            |                           | ; new ones.                            |

| ANDLW      | B'11110001'               | ; Use previously saved CANCON value to |

|            |                           | ; make sure same value.                |

| MOVWF      | TempCANCON                | ; Copy masked value back to TempCANCON |

| MOVF       | TempCANSTAT, W            | ; Retrieve ICODE bits                  |

| ANDLW      | B'00001110'               | ; Use previously saved CANSTAT value   |

|            |                           | ; to make sure same value.             |

| IORWF      | TempCANCON                | ; Copy ICODE bits to WIN bits.         |

| MOVFF      | TempCANCON, CANCON        | ; Copy the result to actual CANCON     |

| ; Acce     | ss current buffer…        |                                        |

| ; User     | code                      |                                        |

| ; Rest     | ore CANCON.WIN bits       |                                        |

| MOVF       | CANCON, W                 | ; Preserve current non WIN bits        |

| ANDLW      | B'11110001'               |                                        |

| IORWF      | TempCANCON                | ; Restore original WIN bits            |

| ; Do n     | ot need to restore CANSTA | T - it is read-only register.          |

| ; Retu     | rn from interrupt or chec | k for another module interrupt source  |

| 1          |                           |                                        |

| R/W-0                                                                | R/W-0                        | R/W-0             | R/W-0          | R/W-0            | R/W-1  | R/W-0           | R/W-1  |

|----------------------------------------------------------------------|------------------------------|-------------------|----------------|------------------|--------|-----------------|--------|

| FIL7_1                                                               | FIL7_0                       | FIL6_1            | FIL6_0         | FIL5_1           | FIL5_0 | FIL4_1          | FIL4_0 |

| bit 7                                                                |                              |                   |                | •                |        |                 | bit 0  |

|                                                                      |                              |                   |                |                  |        |                 |        |

| Legend:                                                              |                              |                   |                |                  |        |                 |        |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                              |                   |                |                  |        |                 |        |

| -n = Value at I                                                      | POR                          | '1' = Bit is set  |                | '0' = Bit is cle | ared   | x = Bit is unkr | nown   |

|                                                                      |                              |                   |                |                  |        |                 |        |

| bit 7-6                                                              | FIL7_<1:0>:                  | Filter 7 Select I | oits 1 and 0   |                  |        |                 |        |

|                                                                      | 11 = No mas                  |                   |                |                  |        |                 |        |

|                                                                      | 10 = Filter 15               |                   |                |                  |        |                 |        |

|                                                                      | 01 = Accepta<br>00 = Accepta |                   |                |                  |        |                 |        |

| bit 5-4                                                              |                              | Filter 6 Select I | nite 1 and 0   |                  |        |                 |        |

| bit 5-4                                                              | 11 = No mas                  |                   |                |                  |        |                 |        |

|                                                                      | 10 = Filter 15               |                   |                |                  |        |                 |        |

|                                                                      | 01 = Accepta                 | nce Mask 1        |                |                  |        |                 |        |

|                                                                      | 00 = Accepta                 | nce Mask 0        |                |                  |        |                 |        |

| bit 3-2                                                              | FIL5_<1:0>:                  | Filter 5 Select I | oits 1 and 0   |                  |        |                 |        |

|                                                                      | 11 = No mas                  |                   |                |                  |        |                 |        |

|                                                                      | 10 = Filter 15               |                   |                |                  |        |                 |        |

|                                                                      | 01 = Accepta<br>00 = Accepta |                   |                |                  |        |                 |        |

| bit 1-0                                                              | •                            | Filter 4 Select I | nite 1 and $0$ |                  |        |                 |        |

|                                                                      | 11 = No mas                  |                   |                |                  |        |                 |        |

|                                                                      | 10 = Filter 15               |                   |                |                  |        |                 |        |

|                                                                      | 01 = Accepta                 | nce Mask 1        |                |                  |        |                 |        |

|                                                                      | 00 = Accepta                 | nce Mask 0        |                |                  |        |                 |        |

|                                                                      |                              |                   |                |                  |        |                 |        |

## REGISTER 27-49: MSEL1: MASK SELECT REGISTER 1<sup>(1)</sup>

**Note 1:** This register is available in Mode 1 and 2 only.

| Mode 0     | R/W-0                                               | R/W-0                                                                                                             | R/W-0                                     | R/W-0          | R/W-0                 | R/W-0                 | R/W-0         | R/W-0    |

|------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------|-----------------------|-----------------------|---------------|----------|

|            | IRXIE                                               | WAKIE                                                                                                             | ERRIE                                     | TXB2IE         | TXB1IE <sup>(1)</sup> | TXB0IE <sup>(1)</sup> | RXB1IE        | RXB0IE   |

|            | R/W-0                                               | R/W-0                                                                                                             | R/W-0                                     | R/W-0          | R/W-0                 | R/W-0                 | R/W-0         | R/W-0    |

| Mode 1     | IRXIE                                               | WAKIE                                                                                                             | ERRIE                                     | TXBnIE         | TXB1IE <sup>(1)</sup> | TXB0IE <sup>(1)</sup> | RXBnIE        | FIFOWMIE |

|            | bit 7                                               |                                                                                                                   |                                           |                |                       |                       |               | bit C    |

| Legend:    |                                                     |                                                                                                                   |                                           |                |                       |                       |               |          |