Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| 2014                       |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | ECANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.6K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x12b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN-S (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26k80-i-mm |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| R/W-0                | R/W-0        | R/W-0                              | R/W-0            | R/W-0            | R/W-0            | R/W-0            | R/W-0    |

|----------------------|--------------|------------------------------------|------------------|------------------|------------------|------------------|----------|

| PSPMD <sup>(1)</sup> | CTMUMD       | ADCMD                              | TMR4MD           | TMR3MD           | TMR2MD           | TMR1MD           | TMR0MD   |

| bit 7                |              |                                    |                  | •                |                  |                  | bit 0    |

| <u> </u>             |              |                                    |                  |                  |                  |                  |          |

| Legend:              |              |                                    |                  |                  |                  |                  |          |

| R = Readable b       |              | W = Writable                       |                  | •                | nented bit, read |                  |          |

| -n = Value at P      | OR           | '1' = Bit is set                   |                  | '0' = Bit is cle | ared             | x = Bit is unkr  | nown     |

| bit 7                | PSPMD: Peri  | pheral Module                      | Disable bit(1)   |                  |                  |                  |          |

|                      |              | -                                  |                  | registers are h  | eld in Reset and | l are not writab |          |

|                      |              | module is enal                     |                  |                  |                  |                  |          |

| bit 6                | CTMUMD: PN   | MD CTMU Disa                       | able bit         |                  |                  |                  |          |

|                      | 1 = The CTM  | IU module is di                    | sabled; all CT   | MU registers a   | are held in Rese | t and are not w  | ritable  |

|                      | 0 = The CTM  | IU module is e                     | nabled           |                  |                  |                  |          |

| bit 5                | ADCMD: A/D   | Module Disab                       | le bit           |                  |                  |                  |          |

|                      |              |                                    |                  | egisters are he  | ld in Reset and  | are not writable | е        |

|                      |              | module is enat                     |                  |                  |                  |                  |          |

| bit 4                |              | IR4MD Disable                      |                  |                  |                  |                  |          |

|                      |              | er4 module is d<br>er4 module is e |                  | ner4 registers   | are held in Res  | et and are not   | writable |

| bit 3                | TMR3MD: TM   | 1R3MD Disable                      | e bit            |                  |                  |                  |          |

|                      | 1 = The Time | er3 module is d                    | isabled; all Tir | ner3 registers   | are held in Res  | et and are not   | writable |

|                      | 0 = The Time | er3 module is e                    | nabled           |                  |                  |                  |          |

| bit 2                | TMR2MD: TM   | IR2MD Disable                      | e bit            |                  |                  |                  |          |

|                      |              | er2 module is d<br>er2 module is e |                  | ner2 registers   | are held in Res  | et and are not   | writable |

| bit 1                | TMR1MD: TM   | IR1MD Disable                      | e bit            |                  |                  |                  |          |

|                      |              |                                    |                  | ner1 registers   | are held in Res  | et and are not   | writable |

|                      |              | er1 module is e                    |                  |                  |                  |                  |          |

| bit 0                | -            | ner0 Module D                      |                  |                  |                  | 4                |          |

|                      |              | r0 module is di<br>r0 module is ei |                  | ieru registers a | are held in Rese | et and are not v | vritable |

|                      |              |                                    |                  |                  |                  |                  |          |

## REGISTER 4-2: PMD1: PERIPHERAL MODULE DISABLE REGISTER 1

Note 1: This bit is unimplemented on 28-pin devices (PIC18F2XK80, PIC18LF2XK80).

#### 6.2.3 INSTRUCTIONS IN PROGRAM MEMORY

The program memory is addressed in bytes. Instructions are stored as two or four bytes in program memory. The Least Significant Byte (LSB) of an instruction word is always stored in a program memory location with an even address (LSB = 0). To maintain alignment with instruction boundaries, the PC increments in steps of two and the LSB will always read '0' (see Section 6.1.2 "Program Counter").

Figure 6-5 shows an example of how instruction words are stored in the program memory.

The CALL and GOTO instructions have the absolute program memory address embedded into the instruction. Since instructions are always stored on word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1> which accesses the desired byte address in program memory. Instruction #2 in Figure 6-5 shows how the instruction, GOTO 0006h, is encoded in the program memory. Program branch instructions, which encode a relative address offset, operate in the same manner. The offset value stored in a branch instruction represents the number of single-word instructions that the PC will be offset by. For more details on the instruction set, see Section 29.0 "Instruction Set Summary".

|                |            |                    | LSB = 1 | LSB = 0 | Word Address $\downarrow$ |

|----------------|------------|--------------------|---------|---------|---------------------------|

|                | Program M  | lemory             |         |         | 000000h                   |

|                | Byte Locat | ions $\rightarrow$ |         |         | 000002h                   |

|                |            |                    |         |         | 000004h                   |

|                |            |                    |         |         | 000006h                   |

| Instruction 1: | MOVLW      | 055h               | 0Fh     | 55h     | 000008h                   |

| Instruction 2: | GOTO       | 0006h              | EFh     | 03h     | 00000Ah                   |

|                |            |                    | F0h     | 00h     | 00000Ch                   |

| Instruction 3: | MOVFF      | 123h, 456h         | C1h     | 23h     | 00000Eh                   |

|                |            |                    | F4h     | 56h     | 000010h                   |

|                |            |                    |         |         | 000012h                   |

|                |            |                    |         |         | 000014h                   |

####

#### 6.2.4 **TWO-WORD INSTRUCTIONS**

The standard PIC18 instruction set has four, two-word instructions: CALL, MOVFF, GOTO and LSFR. In all cases, the second word of the instructions always has '1111' as its four Most Significant bits (MSbs). The other 12 bits are literal data, usually a data memory address.

The use of '1111' in the 4 MSbs of an instruction specifies a special form of NOP. If the instruction is executed in proper sequence, immediately after the first word, the data in the second word is accessed and

used by the instruction sequence. If the first word is skipped for some reason and the second word is executed by itself, a NOP is executed instead. This is necessary for cases when the two-word instruction is preceded by a conditional instruction that changes the PC. Example 6-4 shows how this works.

Note: For information on two-word instructions in the extended instruction set, see Section 6.5 "Program Memory and the Extended Instruction Set".

| EXAMPLE 6-4: | <b>TWO-WORD INSTRUCTIONS</b> |

|--------------|------------------------------|

|              |                              |

| CASE 1:             |                  |                              |

|---------------------|------------------|------------------------------|

| Object Code         | Source Code      |                              |

| 0110 0110 0000 0000 | TSTFSZ REG1      | ; is RAM location 0?         |

| 1100 0001 0010 0011 | MOVFF REG1, REG2 | ; No, skip this word         |

| 1111 0100 0101 0110 |                  | ; Execute this word as a NOP |

| 0010 0100 0000 0000 | ADDWF REG3       | ; continue code              |

| CASE 2:             |                  |                              |

| Object Code         | Source Code      |                              |

| 0110 0110 0000 0000 | TSTFSZ REG1      | ; is RAM location 0?         |

| 1100 0001 0010 0011 | MOVFF REG1, REG2 | ; Yes, execute this word     |

| 1111 0100 0101 0110 |                  | ; 2nd word of instruction    |

| 0010 0100 0000 0000 | ADDWF REG3       | ; continue code              |

© 2010-2012 Microchip Technology Inc.

# FIGURE 6-9: COMPARING ADDRESSING OPTIONS FOR BIT-ORIENTED AND BYTE-ORIENTED INSTRUCTIONS (EXTENDED INSTRUCTION SET ENABLED)

**EXAMPLE INSTRUCTION:** ADDWF, f, d, a (Opcode: 0010 01da ffff ffff)

# When a = 0 and $f \ge 60h$ :

The instruction executes in Direct Forced mode. 'f' is interpreted as a location in the Access RAM between 060h and FFFh. This is the same as locations, F60h to FFFh, (Bank 15) of data memory.

Locations below 060h are not available in this addressing mode.

#### When a = 0 and $f \le 5Fh$ :

The instruction executes in Indexed Literal Offset mode. 'f' is interpreted as an offset to the address value in FSR2. The two are added together to obtain the address of the target register for the instruction. The address can be anywhere in the data memory space.

Note that in this mode, the correct syntax is now: ADDWF [k], d where 'k' is the same as 'f'.

#### When a = 1 (all values of f):

The instruction executes in Direct mode (also known as Direct Long mode). 'f' is interpreted as a location in one of the 16 banks of the data memory space. The bank is designated by the Bank Select Register (BSR). The address can be in any implemented bank in the data memory space.

| Pin Name     | Function           | TRIS<br>Setting | I/O | I/O Type | Description                                                                                |

|--------------|--------------------|-----------------|-----|----------|--------------------------------------------------------------------------------------------|

| RD7/RX2/DT2/ | RD7                | 0               | 0   | DIG      | LATD<7> data output.                                                                       |

| P1D/PSP7     |                    | 1               | Ι   | ST       | PORTD<7> data input.                                                                       |

|              | RX2 <sup>(1)</sup> | 1               | Ι   | ST       | Asynchronous serial receive data input (EUSARTx module).                                   |

|              | DT2 <sup>(1)</sup> | 1               | 0   | DIG      | Synchronous serial data output (EUSARTx module); takes priority over port data.            |

|              |                    | 1               | Ι   | ST       | Synchronous serial data input (EUSARTx module); user must configure as an input.           |

|              | P1D                | 0               | 0   | DIG      | ECCP1 Enhanced PWM output, Channel D. May be configured for tri-state during Enhanced PWM. |

|              | PSP7               | x               | I/O | ST       | Parallel Slave Port data.                                                                  |

# TABLE 11-7: PORTD FUNCTIONS (CONTINUED)

Legend: O = Output; I = Input; ANA = Analog Signal; DIG = CMOS Output; ST = Schmitt Trigger Buffer Input;

x = Don't care (TRIS bit does not affect port direction or is overridden for this option)

**Note 1:** This is the pin assignment for 40 and 44-pin devices (PIC18F4XK80).

### TABLE 11-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

| Name    | Bit 7               | Bit 6               | Bit 5               | Bit 4               | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

|---------|---------------------|---------------------|---------------------|---------------------|---------|---------|--------|--------|

| PORTD   | RD7                 | RD6                 | RD5                 | RD4                 | RD3     | RD2     | RD1    | RD0    |

| LATD    | LATD7               | LATD6               | LATD5               | LATD4               | LATD3   | LATD2   | LATD1  | LATD0  |

| TRISD   | TRISD7              | TRISD6              | TRISD5              | TRISD4              | TRISD3  | TRISD2  | TRISD1 | TRISD0 |

| PADCFG1 | RDPU <sup>(1)</sup> | REPU <sup>(1)</sup> | RFPU <sup>(2)</sup> | RGPU <sup>(2)</sup> | _       | _       | _      | CTMUDS |

| ODCON   | SSPOD               | CCP5OD              | CCP4OD              | CCP3OD              | CCP2OD  | CCP10D  | U2OD   | U10D   |

| ANCON1  | —                   | ANSEL14             | ANSEL13             | ANSEL12             | ANSEL11 | ANSEL10 | ANSEL9 | ANSEL8 |

**Legend:** Shaded cells are not used by PORTD.

Note 1: These bits are unimplemented on 28-pin devices, read as '0'.

2: These bits are unimplemented on 28/40/44-pin devices, read as '0'.

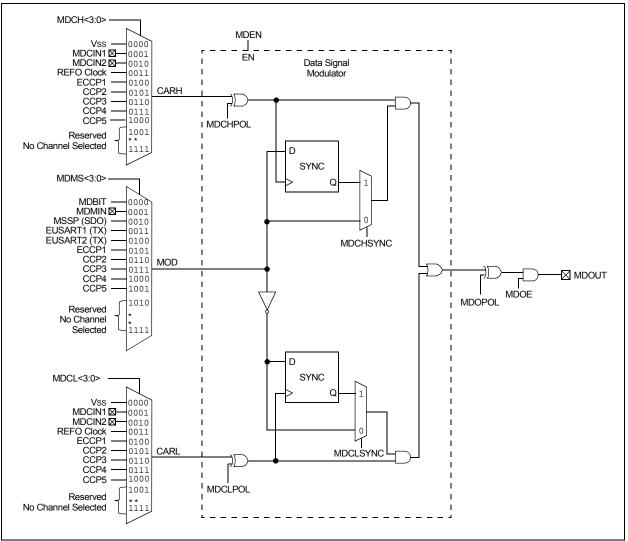

## FIGURE 12-1: SIMPLIFIED BLOCK DIAGRAM OF THE DATA SIGNAL MODULATOR

## REGISTER 12-1: MDCON: MODULATION CONTROL REGISTER

|                |                                            |                  | R/W-0           | R/W-0                          | U-0                       | U-0            | R/W-0 |

|----------------|--------------------------------------------|------------------|-----------------|--------------------------------|---------------------------|----------------|-------|

| MDEN           | MDOE                                       | MDSLR            | MDOPOL          | MDO                            | _                         | _              | MDBIT |

| pit 7          | •                                          |                  | •               | •                              |                           |                | bit 0 |

| egend:         |                                            |                  |                 |                                |                           |                |       |

| R = Readable   | e bit                                      | W = Writable     | bit             | U = Unimpler                   | mented bit, read          | d as '0'       |       |

| n = Value at I | POR                                        | '1' = Bit is set |                 | '0' = Bit is cle               | ared                      | x = Bit is unk | nown  |

| oit 7          | MDEN: Modu                                 | lator Module E   | nable bit       |                                |                           |                |       |

|                | 1 = Modulato<br>0 = Modulato               |                  |                 | ing input signa<br>s no output | lls                       |                |       |

| bit 6          | MDOE: Modu<br>1 = Modulato<br>0 = Modulato | r pin output is  | enabled         | ble bit                        |                           |                |       |

| bit 5          | MDSLR: MDC<br>1 = MDOUT<br>0 = MDOUT       | pin slew rate li | miting is enabl | ed                             |                           |                |       |

| bit 4          | MDOPOL: Mo<br>1 = Modulato<br>0 = Modulato | r output signal  | is inverted     |                                |                           |                |       |

| oit 3          | <b>MDO:</b> Modula<br>Displays the c       |                  | alue of the mo  | odulator modu                  | le. <sup>(2)</sup>        |                |       |

| oit 2-1        | Unimplement                                | ted: Read as '   | 0'              |                                |                           |                |       |

| oit O          | MDBIT: Modu                                |                  | •               |                                |                           |                |       |

|                | Allows softwa                              | re to manually   | set modulatio   | n source input                 | to module. <sup>(1)</sup> |                |       |

2: The modulated output frequency can be greater and asynchronous from the clock that updates this register bit. The bit value may not be valid for higher speed modulator or carrier signals.

## 16.5.2 TIMER3 GATE SOURCE SELECTION

The Timer3 gate source can be selected from one of four different sources. Source selection is controlled by the T3GSS<1:0> bits (T3GCON<1:0>). The polarity for each available source is also selectable and is controlled by the T3GPOL bit (T3GCON<6>).

| TABLE 16-2: | TIMER3 GATE SOURCES |

|-------------|---------------------|

|-------------|---------------------|

| T3GSS<1:0> | Timer3 Gate Source                                    |

|------------|-------------------------------------------------------|

| 00         | Timerx Gate Pin                                       |

| 01         | TMR4 to Match PR4<br>(TMR4 increments to match PR4)   |

| 10         | Comparator 1 Output<br>(comparator logic high output) |

| 11         | Comparator 2 Output<br>(comparator logic high output) |

## 16.5.2.1 T3G Pin Gate Operation

The T3G pin is one source for Timer3 gate control. It can be used to supply an external source to the Timerx gate circuitry.

## 16.5.2.2 Timer4 Match Gate Operation

The TMR4 register will increment until it matches the value in the PR4 register. On the very next increment cycle, TMR4 will be reset to 00h. When this Reset occurs, a low-to-high pulse will automatically be generated and internally supplied to the Timerx gate circuitry. The pulse will remain high for one instruction cycle and will return back to a low state until the next match.

Depending on T3GPOL, Timerx increments differently when TMR4 matches PR4. When T3GPOL = 1, Timer3 increments for a single instruction cycle following a TMR4 match with PR4. When T3GPOL = 0, Timer3 increments continuously, except for the cycle following the match, when the gate signal goes from low-to-high.

### 16.5.2.3 Comparator 1 Output Gate Operation

The output of Comparator 1 can be internally supplied to the Timer3 gate circuitry. After setting up Comparator 1 with the CM1CON register, Timer3 will increment depending on the transitions of the CMP1OUT (CMSTAT<6>) bit.

## 16.5.2.4 Comparator 2 Output Gate Operation

The output of Comparator 2 can be internally supplied to the Timer3 gate circuitry. After setting up Comparator 2 with the CM2CON register, Timer3 will increment depending on the transitions of the CMP2OUT (CMSTAT<7>) bit.

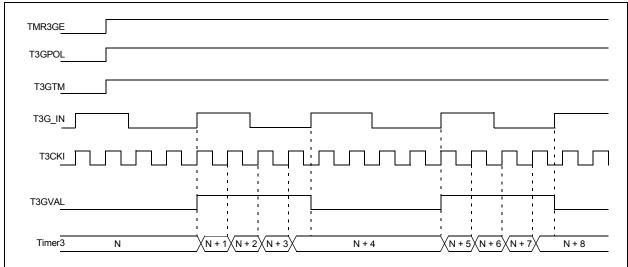

## 16.5.3 TIMER3 GATE TOGGLE MODE

When Timer3 Gate Toggle mode is enabled, it is possible to measure the full cycle length of a Timer3 gate signal, as opposed to the duration of a single level pulse.

The Timer3 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. (For timing details, see Figure 16-3.)

The T3GVAL bit will indicate when the Toggled mode is active and the timer is counting.

Timer3 Gate Toggle mode is enabled by setting the T3GTM bit (T3GCON<5>). When the T3GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

## FIGURE 16-3: TIMER3 GATE TOGGLE MODE

# 20.0 ENHANCED CAPTURE/COMPARE/PWM (ECCP) MODULE

PIC18F66K80 family devices have one Enhanced Capture/Compare/PWM (ECCP) module: ECCP1. These modules contain a 16-bit register, which can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register. These ECCP modules are upward compatible with CCP

ECCP1 is implemented as standard CCP modules with enhanced PWM capabilities. These include:

- Provision for two or four output channels

- Output Steering modes

- · Programmable polarity

- Programmable dead-band control

- Automatic shutdown and restart

The enhanced features are discussed in detail in Section 20.4 "PWM (Enhanced Mode)".

The ECCP1 module uses the control register, CCP1CON. The control registers, CCP2CON through CCP5CON, are for the modules, CCP2 through CCP5.

# 20.4 PWM (Enhanced Mode)

The Enhanced PWM mode can generate a PWM signal on up to four different output pins with up to 10 bits of resolution. It can do this through four different PWM Output modes:

- Single PWM

- Half-Bridge PWM

- Full-Bridge PWM, Forward mode

- Full-Bridge PWM, Reverse mode

To select an Enhanced PWM mode, the P1M bits of the CCP1CON register must be set appropriately.

The PWM outputs are multiplexed with I/O pins and are designated: P1A, P1B, P1C and P1D. The polarity of the PWM pins is configurable and is selected by setting the CCP1M bits in the CCP1CON register appropriately.

Table 20-1 provides the pin assignments for each Enhanced PWM mode.

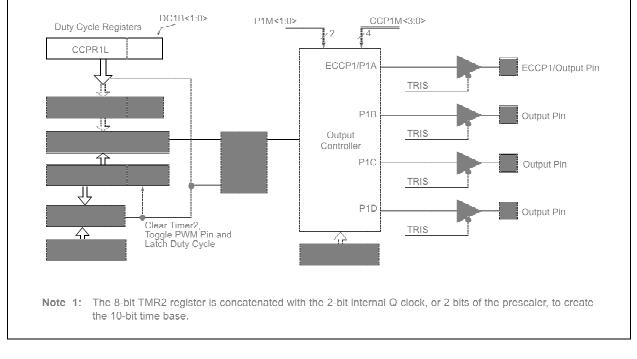

Figure 20-3 provides an example of a simplified block diagram of the Enhanced PWM module.

**Note:** To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

# FIGURE 20-3: EXAMPLE SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODE

Note 1: The TRIS register value for each PWM output must be configured appropriately.2: Any pin not used by an Enhanced PWM mode is available for alternate pin functions.

| ECCP Mode            | P1M<1:0> | P1A                | P1B                | P1C                | P1D                |

|----------------------|----------|--------------------|--------------------|--------------------|--------------------|

| Single               | 00       | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> |

| Half-Bridge          | 10       | Yes                | Yes                | No                 | No                 |

| Full-Bridge, Forward | 01       | Yes                | Yes                | Yes                | Yes                |

| Full-Bridge, Reverse | 11       | Yes                | Yes                | Yes                | Yes                |

#### **TABLE 20-2: EXAMPLE PIN ASSIGNMENTS FOR VARIOUS PWM ENHANCED MODES**

Note 1: Outputs are enabled by pulse steering in Single mode (see Register 20-5).

#### **FIGURE 20-4: EXAMPLE PWM (ENHANCED MODE) OUTPUT RELATIONSHIPS** (ACTIVE-HIGH STATE)

|    | P1M<1:0>        | Signal        | 0        | Pulse Width          | ►                    | PR2 + 1             |

|----|-----------------|---------------|----------|----------------------|----------------------|---------------------|

|    |                 |               | -<br>    | 4                    | Period               |                     |

| 00 | (Single Output) | P1A Modulated |          | Delay <sup>(1)</sup> | Delay <sup>(1)</sup> |                     |

|    |                 | P1A Modulated |          |                      |                      |                     |

| 10 | (Half-Bridge)   | P1B Modulated | ;        |                      |                      |                     |

|    |                 | P1A Active    | ;        |                      |                      | <u></u> і<br>і<br>і |

| 01 | (Full-Bridge,   | P1B Inactive  |          |                      | 1<br>1<br>1          | 1<br>1<br>1         |

| UT | Forward)        | P1C Inactive  | _ ;<br>; |                      | 1<br>1<br>1          | 1<br>               |

|    |                 | P1D Modulated | =ť       |                      | -                    |                     |

|    |                 | P1A Inactive  | ;        |                      | 1<br>1<br>1          | 1<br>1<br>1         |

| 11 | (Full-Bridge,   | P1B Modulated | =        |                      | -j                   | 1<br>1<br>1         |

|    | Reverse)        | P1C Active -  |          |                      |                      |                     |

|    |                 | P1D Inactive  | ;        |                      | 1<br>1               |                     |

Relationships:

Period = 4 \* Tosc \* (PR2 + 1) \* (TMR2 Prescale Value)

Pulse Width = Tosc \* (CCPR1L<7:0>:CCP1CON<5:4>) \* (TMR2 Prescale Value)

Delay = 4 \* Tosc \* (ECCP1DEL<6:0>)

Note 1: Dead-band delay is programmed using the ECCP1DEL register (Section 20.4.6 "Programmable Dead-Band Delay Mode").

# 21.3.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register 1 (SSPCON1)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON1 and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON1 register is readable and writable. The lower 6 bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write.

SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together, create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not double-buffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

# REGISTER 21-1: SSPSTAT: MSSP STATUS REGISTER (SPI MODE)

| -                 |                                                                                                                                                   |                    |                  | <b>X</b> -       | ,                                  |                 |             |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------|------------------|------------------------------------|-----------------|-------------|--|--|

| R/W-0             | R/W-0                                                                                                                                             | R-0                | R-0              | R-0              | R-0                                | R-0             | R-0         |  |  |

| SMP               | CKE <sup>(1)</sup>                                                                                                                                | D/A                | Р                | S                | R/W                                | UA              | BF          |  |  |

| bit 7             |                                                                                                                                                   |                    |                  | ·                |                                    |                 | bit         |  |  |

|                   |                                                                                                                                                   |                    |                  |                  |                                    |                 |             |  |  |

| Legend:           |                                                                                                                                                   |                    |                  |                  |                                    |                 |             |  |  |

| R = Readable bit  |                                                                                                                                                   | W = Writable       | W = Writable bit |                  | U = Unimplemented bit, read as '0' |                 |             |  |  |

| -n = Value at POR |                                                                                                                                                   | '1' = Bit is set   |                  | '0' = Bit is cle | ared                               | x = Bit is unkr | is unknown  |  |  |

|                   |                                                                                                                                                   |                    |                  |                  |                                    |                 |             |  |  |

| bit 7             | SMP: Samp                                                                                                                                         |                    |                  |                  |                                    |                 |             |  |  |

|                   | SPI Master mode:                                                                                                                                  |                    |                  |                  |                                    |                 |             |  |  |

|                   | <ul> <li>1 = Input data is sampled at the end of data output time</li> <li>0 = Input data is sampled at the middle of data output time</li> </ul> |                    |                  |                  |                                    |                 |             |  |  |

|                   | SPI Slave mode:                                                                                                                                   |                    |                  |                  |                                    |                 |             |  |  |

|                   | SMP must be cleared when SPI is used in Slave mode.                                                                                               |                    |                  |                  |                                    |                 |             |  |  |

| bit 6             | CKE: SPI Clock Select bit <sup>(1)</sup>                                                                                                          |                    |                  |                  |                                    |                 |             |  |  |

|                   | 1 = Transmit occurs on transition from active to Idle clock state                                                                                 |                    |                  |                  |                                    |                 |             |  |  |

|                   | 0 = Transmit occurs on transition from Idle to active clock state                                                                                 |                    |                  |                  |                                    |                 |             |  |  |

| bit 5             | D/A: Data/Address bit<br>Used in I <sup>2</sup> C™ mode only.                                                                                     |                    |                  |                  |                                    |                 |             |  |  |

|                   |                                                                                                                                                   | ™ mode only.       |                  |                  |                                    |                 |             |  |  |

| bit 4             | <b>P:</b> Stop bit Used in I <sup>2</sup> C mode only. This bit is cleared when the MSSP module is disabled; SSPEN is cleared.                    |                    |                  |                  |                                    |                 |             |  |  |

| <b>L</b> H 0      |                                                                                                                                                   | mode only. This    | bit is cleared   | when the MSSF    | <sup>2</sup> module is dis         | abled; SSPEN    | is cleared. |  |  |

| bit 3             | <b>S:</b> Start bit                                                                                                                               | modo only          |                  |                  |                                    |                 |             |  |  |

| bit 2             | Used in I <sup>2</sup> C mode only.<br><b>R/W:</b> Read/Write Information bit                                                                     |                    |                  |                  |                                    |                 |             |  |  |

|                   | Used in I <sup>2</sup> C mode only.                                                                                                               |                    |                  |                  |                                    |                 |             |  |  |

| bit 1             | UA: Update Address bit                                                                                                                            |                    |                  |                  |                                    |                 |             |  |  |

| ~                 | Used in I <sup>2</sup> C                                                                                                                          |                    |                  |                  |                                    |                 |             |  |  |

| bit 0             | BF: Buffer Full Status bit (Receive mode only)                                                                                                    |                    |                  |                  |                                    |                 |             |  |  |

|                   | 1 = Receive is complete, SSPBUF is full                                                                                                           |                    |                  |                  |                                    |                 |             |  |  |

|                   |                                                                                                                                                   | is not complete    |                  | empty            |                                    |                 |             |  |  |

| Note 1: P         | olarity of clock                                                                                                                                  | state is set by th | ne CKP bit (S    | SPCON1<4>)       |                                    |                 |             |  |  |

|                   |                                                                                                                                                   |                    |                  |                  |                                    |                 |             |  |  |

Note 1: Polarity of clock state is set by the CKP bit (SSPCON1<4>).

# 25.0 COMPARATOR VOLTAGE REFERENCE MODULE

The comparator voltage reference is a 32-tap resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it may also be used independently of them.

A block diagram of the module is shown in Figure 25-1. The resistor ladder is segmented to provide a range of CVREF values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/VSS or an external voltage reference.

# 25.1 Configuring the Comparator Voltage Reference

The comparator voltage reference module is controlled through the CVRCON register (Register 25-1). The comparator voltage reference provides a range of output voltage with 32 levels.

The CVR<4:0> selection bits (CVRCON<4:0>) offer a range of output voltages. Equation 25-1 shows the how the comparator voltage reference is computed.

# EQUATION 25-1:

$$\frac{\text{If CVRSS} = 1:}{\text{CVREF}} = \left(\text{VREF} + \frac{\text{CVR} < 4:0>}{32}\right) \cdot (\text{VREF} + - \text{VREF})$$

$$\frac{\text{If CVRSS} = 0:}{\text{CVREF}} = \left(\text{AVSS} + \frac{\text{CVR} < 4:0>}{32}\right) \cdot (\text{AVDD} - \text{AVSS})$$

The comparator reference supply voltage can come from either VDD and Vss, or the external VREF+ and VREF- that are multiplexed with RA3 and RA2. The voltage source is selected by the CVRSS bit (CVRCON<5>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output (see Table 31-2 in **Section 31.0 "Electrical Characteristics"**).

# **REGISTER 25-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER**

| R/W-0         | R/W-0                                                                                                                                                                                                                                                              | R/W-0                                                     | R/W-0          | R/W-0                | R/W-0           | R/W-0              | R/W-0 |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------|----------------------|-----------------|--------------------|-------|

| CVREN         | CVROE                                                                                                                                                                                                                                                              | CVRSS                                                     | CVR4           | CVR3                 | CVR2            | CVR1               | CVR0  |

| bit 7         |                                                                                                                                                                                                                                                                    |                                                           |                |                      |                 |                    | bit   |

|               |                                                                                                                                                                                                                                                                    |                                                           |                |                      |                 |                    |       |

| Legend:       |                                                                                                                                                                                                                                                                    |                                                           |                |                      |                 |                    |       |

| R = Readable  | e bit                                                                                                                                                                                                                                                              | W = Writable b                                            | oit            | U = Unimplem         | nented bit, rea | d as '0'           |       |

| -n = Value at | POR                                                                                                                                                                                                                                                                | '1' = Bit is set                                          |                | '0' = Bit is cleared |                 | x = Bit is unknown |       |

| bit 6         | <ul> <li>1 = CVREF circuit powered on</li> <li>0 = CVREF circuit powered down</li> <li>CVROE: Comparator VREF Output Enable bit</li> <li>1 = CVREF voltage level is output on CVREF pin</li> <li>0 = CVREF voltage level is disconnected from CVREF pin</li> </ul> |                                                           |                |                      |                 |                    |       |

| bit 5         | 1 = Compar                                                                                                                                                                                                                                                         | mparator VREF S<br>ator reference so<br>ator reference so | ource, CVRSR   | c = Vref+ – Vr       |                 |                    |       |

| bit 4-0       | <u>When CVRS</u><br>CVREF = (VR<br><u>When CVRS</u>                                                                                                                                                                                                                | EF-) + (CVR<4:0                                           | 0>/32) ● (VREF | + – Vref-)           | :0> ≤ 31 bits   |                    |       |

|               |                                                                                                                                                                                                                                                                    |                                                           |                |                      |                 |                    |       |

| R/W-0           | R/W-0                                            | R/W-0             | R/W-0          | R/W-0                | R/W-1            | R/W-0              | R/W-1  |  |  |

|-----------------|--------------------------------------------------|-------------------|----------------|----------------------|------------------|--------------------|--------|--|--|

| FIL7_1          | FIL7_0                                           | FIL6_1            | FIL6_0         | FIL5_1               | FIL5_0           | FIL4_1             | FIL4_0 |  |  |

| bit 7           | •                                                |                   |                | •                    |                  |                    | bit 0  |  |  |

|                 |                                                  |                   |                |                      |                  |                    |        |  |  |

| Legend:         |                                                  |                   |                |                      |                  |                    |        |  |  |

| R = Readable    | bit                                              | W = Writable      | bit            | U = Unimpler         | nented bit, read | l as '0'           |        |  |  |

| -n = Value at I | POR                                              | '1' = Bit is set  |                | '0' = Bit is cleared |                  | x = Bit is unknown |        |  |  |

|                 |                                                  |                   |                |                      |                  |                    |        |  |  |

| bit 7-6         | FIL7_<1:0>:                                      | Filter 7 Select I | oits 1 and 0   |                      |                  |                    |        |  |  |

|                 | 11 = No mas                                      |                   |                |                      |                  |                    |        |  |  |

|                 | 10 = Filter 15                                   |                   |                |                      |                  |                    |        |  |  |

|                 | 01 = Acceptance Mask 1<br>00 = Acceptance Mask 0 |                   |                |                      |                  |                    |        |  |  |

| bit 5-4         |                                                  | Filter 6 Select I | nite 1 and 0   |                      |                  |                    |        |  |  |

| bit 5-4         | 11 = No mas                                      |                   |                |                      |                  |                    |        |  |  |

|                 | 10 = Filter 15                                   |                   |                |                      |                  |                    |        |  |  |

|                 | 01 = Acceptance Mask 1                           |                   |                |                      |                  |                    |        |  |  |

|                 | 00 = Accepta                                     | nce Mask 0        |                |                      |                  |                    |        |  |  |

| bit 3-2         | FIL5_<1:0>:                                      | Filter 5 Select I | oits 1 and 0   |                      |                  |                    |        |  |  |

|                 | 11 = No mas                                      |                   |                |                      |                  |                    |        |  |  |

|                 | 10 = Filter 15                                   |                   |                |                      |                  |                    |        |  |  |

|                 | 01 = Accepta<br>00 = Accepta                     |                   |                |                      |                  |                    |        |  |  |

| bit 1-0         | •                                                | Filter 4 Select I | nite 1 and $0$ |                      |                  |                    |        |  |  |

| bit 1-0         | 11 = No mas                                      |                   |                |                      |                  |                    |        |  |  |

|                 | 10 = Filter 15                                   |                   |                |                      |                  |                    |        |  |  |

|                 | 01 = Accepta                                     | nce Mask 1        |                |                      |                  |                    |        |  |  |

|                 | 00 = Accepta                                     | nce Mask 0        |                |                      |                  |                    |        |  |  |

|                 |                                                  |                   |                |                      |                  |                    |        |  |  |

# REGISTER 27-49: MSEL1: MASK SELECT REGISTER 1<sup>(1)</sup>

**Note 1:** This register is available in Mode 1 and 2 only.

| R/P-0             | R/P-0                                                                                                                                              | U-0                                                   | U-0                   | R/P-1                                             | R/P-0                | R/P-0                | R/P-0                |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------|---------------------------------------------------|----------------------|----------------------|----------------------|--|--|--|

| IESO              | FCMEN                                                                                                                                              | _                                                     | PLLCFG <sup>(1)</sup> | FOSC3 <sup>(2)</sup>                              | FOSC2 <sup>(2)</sup> | FOSC1 <sup>(2)</sup> | FOSC0 <sup>(2)</sup> |  |  |  |

| bit 7             |                                                                                                                                                    |                                                       |                       |                                                   |                      |                      | bit (                |  |  |  |

| Legend:           |                                                                                                                                                    | P = Program                                           | mable bit             |                                                   |                      |                      |                      |  |  |  |

| R = Reada         | ıble bit                                                                                                                                           | W = Writable                                          |                       | U = Unimpler                                      | mented bit, read     | d as '0'             |                      |  |  |  |

| -n = Value at POR |                                                                                                                                                    | '1' = Bit is set                                      |                       | $0^{\circ}$ = Bit is cleared $x = Bit is unknown$ |                      |                      | nown                 |  |  |  |

|                   |                                                                                                                                                    |                                                       | -                     |                                                   |                      |                      |                      |  |  |  |

| bit 7             | IESO: Interna                                                                                                                                      | al/External Oso                                       | cillator Switchov     | ver bit                                           |                      |                      |                      |  |  |  |

|                   | 1 = Two-Spee                                                                                                                                       | ed Start-up is e                                      | enabled               |                                                   |                      |                      |                      |  |  |  |

|                   | 0 = Two-Spee                                                                                                                                       | ed Start-up is o                                      | lisabled              |                                                   |                      |                      |                      |  |  |  |

| bit 6             | FCMEN: Fail-Safe Clock Monitor Enable bit                                                                                                          |                                                       |                       |                                                   |                      |                      |                      |  |  |  |

|                   | 1 = Fail-Safe Clock Monitor is enabled                                                                                                             |                                                       |                       |                                                   |                      |                      |                      |  |  |  |

|                   | 0 = Fail-Safe                                                                                                                                      | Clock Monitor                                         | is disabled           |                                                   |                      |                      |                      |  |  |  |

| bit 5             | Unimplemen                                                                                                                                         | ted: Read as                                          | '0'                   |                                                   |                      |                      |                      |  |  |  |

| bit 4             | PLLCFG: 4X PLL Enable bit <sup>(1)</sup>                                                                                                           |                                                       |                       |                                                   |                      |                      |                      |  |  |  |

|                   | 1 = Oscillator is multiplied by 4                                                                                                                  |                                                       |                       |                                                   |                      |                      |                      |  |  |  |

|                   |                                                                                                                                                    | is used direct                                        |                       |                                                   |                      |                      |                      |  |  |  |

| bit 3-0           | FOSC<3:0>: Oscillator Selection bits <sup>(2)</sup>                                                                                                |                                                       |                       |                                                   |                      |                      |                      |  |  |  |

|                   | 1101 = EC1, EC oscillator (low power, DC-160 kHz)                                                                                                  |                                                       |                       |                                                   |                      |                      |                      |  |  |  |

|                   | 1100 = EC1IO, EC oscillator with CLKOUT function on RA6 (low power, DC-160 kHz)                                                                    |                                                       |                       |                                                   |                      |                      |                      |  |  |  |

|                   | 1011 = EC2, EC oscillator (medium power, 160 kHz-16 MHz)<br>1010 = EC2IO, EC oscillator with CLKOUT function on RA6 (medium power, 160 kHz-16 MHz) |                                                       |                       |                                                   |                      |                      |                      |  |  |  |

|                   |                                                                                                                                                    | 0101 = EC3, EC oscillator (high power, 16 MHz-64 MHz) |                       |                                                   |                      |                      |                      |  |  |  |

|                   | 0100 = EC3IO, EC oscillator with CLKOUT function on RA6 (high power, 16 MHz-64 MHz)                                                                |                                                       |                       |                                                   |                      |                      |                      |  |  |  |

|                   | 0011 = HS1, HS oscillator (medium power, 4 MHz-16 MHz)                                                                                             |                                                       |                       |                                                   |                      |                      |                      |  |  |  |

|                   | 0010 = HS2, HS oscillator <b>(high power, 16 MHz-25 MHz)</b><br>0001 = XT oscillator                                                               |                                                       |                       |                                                   |                      |                      |                      |  |  |  |

|                   | 0001 = XT  oscillator<br>0000 = LP oscillator                                                                                                      |                                                       |                       |                                                   |                      |                      |                      |  |  |  |

|                   | 0111 = RC, external RC oscillator                                                                                                                  |                                                       |                       |                                                   |                      |                      |                      |  |  |  |

|                   | 0110 = RCIO, external RC oscillator with CKLOUT function on RA6                                                                                    |                                                       |                       |                                                   |                      |                      |                      |  |  |  |

|                   | 1000 = INTIO2, internal RC oscillator                                                                                                              |                                                       |                       |                                                   |                      |                      |                      |  |  |  |

|                   | 1001 = INTI                                                                                                                                        | O1, internal R                                        | C oscillator with     | CLKOUT fun                                        | ction on RA6         |                      |                      |  |  |  |

| Note 1:           | Not valid for the IN                                                                                                                               | TIOx PLL mo                                           | de.                   |                                                   |                      |                      |                      |  |  |  |

| 2:                | INTIO + PLL can b                                                                                                                                  | e enabled only                                        | / by the PLLEN        | hit (OSCTUN                                       | E<6>) Other P        | II modes can b       | e enabled b          |  |  |  |

# REGISTER 28-2: CONFIG1H: CONFIGURATION REGISTER 1 HIGH (BYTE ADDRESS 300001h)

2: INTIO + PLL can be enabled only by the PLLEN bit (OSCTUNE<6>). Other PLL modes can be enabled by either the PLLEN bit or the PLLCFG (CONFIG1H<4>) bit.

| Byte-oriented file register operations                                                                                                                                                                                                                | Example Instruction  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| <u>15 10 9 8 7 0</u>                                                                                                                                                                                                                                  |                      |

| OPCODE d a f (FILE #)                                                                                                                                                                                                                                 | ADDWF MYREG, W, B    |

| <ul> <li>d = 0 for result destination to be WREG register</li> <li>d = 1 for result destination to be file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul> |                      |

| Byte to Byte move operations (2-word)                                                                                                                                                                                                                 |                      |

| <u>15 12 11 0</u>                                                                                                                                                                                                                                     |                      |

| OPCODE f (Source FILE #)                                                                                                                                                                                                                              | MOVFF MYREG1, MYREG2 |

| 15 12 11 0                                                                                                                                                                                                                                            |                      |

| 1111 f (Destination FILE #)                                                                                                                                                                                                                           |                      |

| f = 12-bit file register address                                                                                                                                                                                                                      |                      |

| Bit-oriented file register operations                                                                                                                                                                                                                 |                      |

| 15 12 11 9 8 7 0                                                                                                                                                                                                                                      |                      |

| OPCODE b (BIT #) a f (FILE #)                                                                                                                                                                                                                         | BSF MYREG, bit, B    |

| <ul> <li>b = 3-bit position of bit in file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul>                                                                 |                      |

| Literal operations                                                                                                                                                                                                                                    |                      |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE k (literal)                                                                                                                                                                                                                                    | MOVLW 7Fh            |

| k = 8-bit immediate value                                                                                                                                                                                                                             |                      |

| Control operations                                                                                                                                                                                                                                    |                      |

|                                                                                                                                                                                                                                                       |                      |

| CALL, GOTO and Branch operations<br>15 8 7 0                                                                                                                                                                                                          |                      |

| OPCODE n<7:0> (literal)                                                                                                                                                                                                                               | GOTO Label           |

| 15 12 11 0                                                                                                                                                                                                                                            |                      |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                |                      |

| n = 20-bit immediate value                                                                                                                                                                                                                            |                      |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE S n<7:0> (literal)                                                                                                                                                                                                                             | CALL MYFUNC          |

| 15 12 11 0                                                                                                                                                                                                                                            |                      |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                |                      |

| S = Fast bit                                                                                                                                                                                                                                          |                      |

| 15 11 10 0                                                                                                                                                                                                                                            |                      |

| OPCODE n<10:0> (literal)                                                                                                                                                                                                                              | BRA MYFUNC           |

|                                                                                                                                                                                                                                                       |                      |

| 15 8 7 0                                                                                                                                                                                                                                              |                      |

| OPCODE n<7:0> (literal)                                                                                                                                                                                                                               | BC MYFUNC            |

| XORWF                                                                                                                                                                                                                                                                               | Exclusive OR W with f                                                              |                                                                                                                                                                     |      |                     |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|--|--|--|

| Syntax:                                                                                                                                                                                                                                                                             | XORWF                                                                              | f {,d {,a}}                                                                                                                                                         |      |                     |  |  |  |

| Operands:                                                                                                                                                                                                                                                                           | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$ |                                                                                                                                                                     |      |                     |  |  |  |

| Operation:                                                                                                                                                                                                                                                                          | (W) .XOR. (                                                                        | (f) $\rightarrow$ dest                                                                                                                                              | t    |                     |  |  |  |

| Status Affected:                                                                                                                                                                                                                                                                    | N, Z                                                                               |                                                                                                                                                                     |      |                     |  |  |  |