Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | ECANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.6K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x12b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26k80-i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

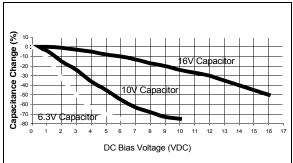

# 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R), or -20%/+80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex:  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%$ . Due to the extreme temperature tolerance, a 10  $\mu$ F nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal regulator if the application must operate over a wide temperature range.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

A typical DC bias voltage vs. capacitance graph for X7R type and Y5V type capacitors is shown in Figure 2-4.

#### FIGURE 2-4: DC BIAS VOLTAGE vs. CAPACITANCE CHARACTERISTICS

When selecting a ceramic capacitor to be used with the internal voltage regulator, it is suggested to select a high-voltage rating, so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at 16V for the 2.5V core voltage. Suggested capacitors are shown in Table 2-1.

# 2.5 ICSP Pins

The PGC and PGD pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100 $\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGC and PGD pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGCx/PGDx pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 30.0 "Development Support"**.

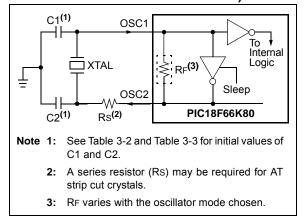

#### 3.5 External Oscillator Modes

#### 3.5.1 CRYSTAL OSCILLATOR/CERAMIC **RESONATORS (HS MODES)**

In HS or HSPLL Oscillator modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation. Figure 3-4 shows the pin connections.

The oscillator design requires the use of a crystal rated for parallel resonant operation.

Note: Use of a crystal rated for series resonant operation may give a frequency out of the crystal manufacturer's specifications.

#### **CAPACITOR SELECTION FOR TABLE 3-2:** CERAMIC RESONATORS

| Typical | Capacitor | Values | Used: |  |

|---------|-----------|--------|-------|--|

|         |           |        |       |  |

| Mode | Freq.    | OSC1  | OSC2  |

|------|----------|-------|-------|

| HS   | 8.0 MHz  | 27 pF | 27 pF |

|      | 16.0 MHz | 22 pF | 22 pF |

Capacitor values are for design guidance only.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application. Refer to the following application notes for oscillator-specific information:

- AN588, "PIC<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices"

- AN849, "Basic PIC<sup>®</sup> Oscillator Design"

- AN943, "Practical PIC® Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

See the notes following Table 3-3 for additional information.

#### **TABLE 3-3:** CAPACITOR SELECTION FOR **CRYSTAL OSCILLATOR**

| Osc Type | Crystal<br>Freq. | Typical Capa<br>Tes |       |

|----------|------------------|---------------------|-------|

|          | Fieq.            | C1                  | C2    |

| HS       | 4 MHz            | 27 pF               | 27 pF |

|          | 8 MHz            | 22 pF               | 22 pF |

|          | 20 MHz           | 15 pF               | 15 pF |

#### Capacitor values are for design guidance only.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

Refer to the Microchip application notes cited in Table 3-2 for oscillator specific information. Also see the notes following this table for additional information.

- Note 1: Higher capacitance increases the stability of oscillator but also increases the start-up time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 3: Rs may be required to avoid overdriving crystals with low drive level specification.

- 4: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

### **RESONATOR OPERATION** (HS OR HSPLL CONFIGURATION)

# 4.6 Exiting Idle and Sleep Modes

An exit from Sleep mode or any of the Idle modes is triggered by an interrupt, a Reset or a WDT time-out. This section discusses the triggers that cause exits from power-managed modes. The clocking subsystem actions are discussed in each of the power-managed modes (see Section 4.2 "Run Modes", Section 4.3 "Sleep Mode" and Section 4.4 "Idle Modes").

### 4.6.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit from an Idle mode or Sleep mode to a Run mode. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCONx or PIEx registers. The exit sequence is initiated when the corresponding interrupt flag bit is set.

On all exits from Idle or Sleep modes by interrupt, code execution branches to the interrupt vector if the GIE/ GIEH bit (INTCON<7>) is set. Otherwise, code execution continues or resumes without branching (see **Section 10.0 "Interrupts"**).

## 4.6.2 EXIT BY WDT TIME-OUT

A WDT time-out will cause different actions depending on which power-managed mode the device is in when the time-out occurs.

If the device is not executing code (all Idle modes and Sleep mode), the time-out will result in an exit from the power-managed mode (see Section 4.2 "Run Modes" and Section 4.3 "Sleep Mode"). If the device is executing code (all Run modes), the time-out will result in a WDT Reset (see Section 28.2 "Watchdog Timer (WDT)").

Executing a SLEEP or CLRWDT instruction clears the WDT timer and postscaler, loses the currently selected clock source (if the Fail-Safe Clock Monitor is enabled) and modifies the IRCFx bits in the OSCCON register (if the internal oscillator block is the device clock source).

### 4.6.3 EXIT BY RESET

Normally, the device is held in Reset by the Oscillator Start-up Timer (OST) until the primary clock becomes ready. At that time, the OSTS bit is set and the device begins executing code. If the internal oscillator block is the new clock source, the HFIOFS/MFIOFS bits are set instead.

The exit delay time from Reset to the start of code execution depends on both the clock sources before and after the wake-up, and the type of oscillator, if the new clock source is the primary clock. Exit delays are summarized in Table 4-4.

Code execution can begin before the primary clock becomes ready. If either the Two-Speed Start-up (see Section 28.4 "Two-Speed Start-up") or Fail-Safe Clock Monitor (see Section 28.5 "Fail-Safe Clock Monitor") is enabled, the device may begin execution as soon as the Reset source has cleared. Execution is clocked by the INTOSC multiplexer driven by the internal oscillator block. Execution is clocked by the internal oscillator block until either the primary clock becomes ready or a power-managed mode is entered before the primary clock becomes ready; the primary clock is then shut down.

#### 4.6.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. The two cases are:

- When in PRI\_IDLE mode, where the primary clock source is not stopped

- When the primary clock source is not any of the LP, XT, HS or HSPLL modes

In these instances, the primary clock source either does not require an oscillator start-up delay, since it is already running (PRI\_IDLE), or normally, does not require an oscillator start-up delay (RC, EC and INTIO Oscillator modes). However, a fixed delay of interval, TCSD, following the wake event is still required when leaving Sleep and Idle modes to allow the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

## 7.4 Erasing Flash Program Memory

The erase blocks are 32 words or 64 bytes.

Word erase in the Flash array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 64 bytes of program memory is erased. The Most Significant 16 bits of the TBLPTR<21:6> point to the block being erased. The TBLPTR<5:0> bits are ignored.

The EECON1 register commands the erase operation. The EEPGD bit must be set to point to the Flash program memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

For protection, the write initiate sequence for EECON2 must be used.

A long write is necessary for erasing the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

#### 7.4.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- 1. Load the Table Pointer register with the address of row to be erased.

- 2. Set the EECON1 register for the erase operation:

- · Set the EEPGD bit to point to program memory

- Clear the CFGS bit to access program memory

- · Set the WREN bit to enable writes

- · Set the FREE bit to enable the erase

- 3. Disable the interrupts.

- 4. Write 55h to EECON2.

- 5. Write 0AAh to EECON2.

- Set the WR bit. This begins the row erase cycle. The CPU will stall for the duration of the erase for TIW. (See Parameter D133A.)

- 7. Re-enable interrupts.

|           | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL | ; load TBLPTR with the base<br>; address of the memory block |

|-----------|----------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------|

| ERASE_ROW |                                                    |                                                                                     |                                                              |

|           | BSF                                                | EECON1, EEPGD                                                                       | ; point to Flash program memory                              |

|           | BCF                                                | EECON1, CFGS                                                                        | ; access Flash program memory                                |

|           | BSF                                                | EECON1, WREN                                                                        | ; enable write to memory                                     |

|           | BSF                                                | EECON1, FREE                                                                        | ; enable Row Erase operation                                 |

|           | BCF                                                | INTCON, GIE                                                                         | ; disable interrupts                                         |

| Required  | MOVLW                                              | 55h                                                                                 |                                                              |

| Sequence  | MOVWF                                              | EECON2                                                                              | ; write 55h                                                  |

|           | MOVLW                                              | 0AAh                                                                                |                                                              |

|           | MOVWF                                              | EECON2                                                                              | ; write OAAh                                                 |

|           | BSF                                                | EECON1, WR                                                                          | ; start erase (CPU stall)                                    |

|           | BSF                                                | INTCON, GIE                                                                         | ; re-enable interrupts                                       |

#### EXAMPLE 7-2: ERASING A FLASH PROGRAM MEMORY ROW

| R/W-0         | R/W-0                               | R/W-0                                | R/W-0             | R/W-0            | R/W-0            | R/W-0           | R/W-0              |

|---------------|-------------------------------------|--------------------------------------|-------------------|------------------|------------------|-----------------|--------------------|

| IRXIF         | WAKIF                               | ERRIF                                | TXB2IF            | TXB1IF           | TXB0IF           | RXB1IF          | RXB0IF/<br>FIFOFIF |

| bit 7         | •                                   |                                      |                   |                  |                  |                 | bit                |

|               |                                     |                                      |                   |                  |                  |                 |                    |

| Legend:       | 1.1                                 |                                      | 1.11              |                  |                  | 1               |                    |

| R = Readable  |                                     | W = Writable                         |                   | -                | nented bit, read |                 |                    |

| -n = Value at | PUR                                 | '1' = Bit is set                     | [                 | '0' = Bit is cle | ared             | x = Bit is unk  | nown               |

| bit 7         | IRXIF: Invalid                      | d Message Rec                        | eived Interrup    | t Flag bits      |                  |                 |                    |

|               |                                     | d message occ                        | •                 | •                |                  |                 |                    |

|               |                                     | id message occ                       |                   |                  |                  |                 |                    |

| bit 6         | WAKIF: Bus                          | Wake-up Activi                       | ity Interrupt Fla | ag bit           |                  |                 |                    |

|               |                                     | on the CAN bus<br>ity on the CAN     |                   |                  |                  |                 |                    |

| bit 5         | ERRIF: Erro                         | r Interrupt Flag                     | bit (Multiple s   | ources in CON    | ISTAT register)  |                 |                    |

|               |                                     | has occurred in                      |                   | • •              | ources)          |                 |                    |

|               |                                     | module errors                        |                   |                  |                  |                 |                    |

| bit 4         |                                     | nsmit Buffer 2 l                     |                   |                  |                  |                 |                    |

|               |                                     | t Buffer 2 has c<br>t Buffer 2 has n |                   |                  | •                | lay be reloaded |                    |

| bit 3         |                                     | nsmit Buffer 1 li                    | •                 |                  | a message        |                 |                    |

|               |                                     | t Buffer 1 has c                     |                   |                  | nessage and m    | ay be reloaded  | l                  |

|               | 0 = Transmi                         | t Buffer 1 has n                     | ot completed      | transmission of  | a message        |                 |                    |

| bit 2         |                                     | nsmit Buffer 0 I                     |                   |                  |                  |                 |                    |

|               |                                     | t Buffer 0 has c<br>t Buffer 0 has n |                   |                  |                  | ay be reloaded  | l                  |

| bit 1         | RXB1IF: Red                         | ceive Buffer 1 Ir                    | nterrupt Flag b   | bit              |                  |                 |                    |

|               | $\frac{\text{Mode 0:}}{1 - CAN De}$ | aaiua Duffar 1 k                     |                   |                  |                  |                 |                    |

|               |                                     | ceive Buffer 1 h<br>ceive Buffer 1 h |                   | 0                |                  |                 |                    |

|               | Modes 1 and                         |                                      |                   |                  |                  |                 |                    |

|               |                                     | Receive Buffer/I                     |                   |                  | •                |                 |                    |

|               |                                     | Receive Buffer/I                     |                   |                  | message          |                 |                    |

| bit 0         | =                                   | is dependent o                       | on the selected   | I mode:          |                  |                 |                    |

|               | Mode 0:<br><b>PYBOIE:</b> Rec       | ceive Buffer 0 Ir                    | nterrunt Elaa h   | .i+              |                  |                 |                    |

|               |                                     | ceive Buffer 0 h                     |                   |                  |                  |                 |                    |

|               |                                     | ceive Buffer 0 h                     |                   | •                |                  |                 |                    |

|               | <u>Mode 1:</u><br>Unimplemer        | nted: Read as '                      | 0'                |                  |                  |                 |                    |

|               | Mode 2:                             |                                      |                   |                  |                  |                 |                    |

|               | FIFOFIF: FIF                        | O Full Interrup                      | t Flag bit        |                  |                  |                 |                    |

|               |                                     | s reached full s                     |                   |                  | UE bit           |                 |                    |

# REGISTER 10-8: PIR5: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 5

# REGISTER 10-13: PIE5: PERIPHERAL INTERRUPT ENABLE REGISTER 5

| R/W-0         | R/W-0                                | R/W-0             | R/W-0            | R/W-0            | R/W-0           | R/W-0           | R/W-0              |

|---------------|--------------------------------------|-------------------|------------------|------------------|-----------------|-----------------|--------------------|

| IRXIE         | WAKIE                                | ERRIE             | TXB2IE           | TXB1IE           | TXB0IE          | RXB1IE          | RXB0IE/<br>FIFOFIE |

| bit 7         |                                      | -                 |                  |                  |                 |                 | bit C              |

| Legend:       |                                      |                   |                  |                  |                 |                 |                    |

| R = Readable  | e bit                                | W = Writable      | bit              | U = Unimpler     | mented bit, rea | ad as '0'       |                    |

| -n = Value at | POR                                  | '1' = Bit is set  |                  | '0' = Bit is cle | ared            | x = Bit is unki | nown               |

| bit 7         | IRXIE: Invali<br>1 = Interrupt       | d Message Rec     | eived Interrup   | ot Flag bit      |                 |                 |                    |

|               | 0 = Interrupt                        |                   |                  |                  |                 |                 |                    |

| bit 6         | •                                    | Wake-up Activ     | itv Interrupt FI | aq bit           |                 |                 |                    |

|               | 1 = Interrupt<br>0 = Interrupt       | t is enabled      |                  |                  |                 |                 |                    |

| bit 5         | ERRIE: Erro                          | or Interrupt Flag | bit (multiple s  | ources in the (  | COMSTAT regi    | ister)          |                    |

|               | 1 = Interrupt<br>0 = Interrupt       | t is enabled      |                  |                  | -               | ·               |                    |

| bit 4         | TXB2IE: Tra                          | nsmit Buffer 2 I  | nterrupt Flag I  | bit              |                 |                 |                    |

|               | 1 = Interrupt<br>0 = Interrupt       |                   |                  |                  |                 |                 |                    |

| bit 3         | TXB1IE: Tra                          | nsmit Buffer 1 I  | nterrupt Flag I  | bit              |                 |                 |                    |

|               | 1 = Interrupt<br>0 = Interrupt       |                   |                  |                  |                 |                 |                    |

| bit 2         | TXB0IE: Tra                          | nsmit Buffer 0 I  | nterrupt Flag I  | bit              |                 |                 |                    |

|               | 1 = Interrupt<br>0 = Interrupt       |                   |                  |                  |                 |                 |                    |

| bit 1         | RXB1IE: Re                           | ceive Buffer 1 li | nterrupt Flag b  | bit              |                 |                 |                    |

|               | 1 = Interrupt<br>0 = Interrupt       |                   |                  |                  |                 |                 |                    |

| bit 0         | Bit operation<br>Mode 0:             | is dependent c    | n the selected   | d mode:          |                 |                 |                    |

|               | <b>RXB0IE</b> : Red<br>1 = Interrupt |                   | nterrupt Flag b  | bit              |                 |                 |                    |

|               | 0 = Interrupt                        | t is disabled     |                  |                  |                 |                 |                    |

|               | Mode 1:<br>Unimplemer                | nted: Read as '   | 0'               |                  |                 |                 |                    |

|               | Mode 2:                              |                   |                  |                  |                 |                 |                    |

|               |                                      | O Full Interrup   | t Flag bit       |                  |                 |                 |                    |

|               | 1 = Interrupt                        |                   |                  |                  |                 |                 |                    |

|               | 0 = Interrupt                        |                   |                  |                  |                 |                 |                    |

### 10.6 INTx Pin Interrupts

External interrupts on the RB0/INT0, RB1/INT1, RB2/INT2 and RB3/INT3 pins are edge-triggered. If the corresponding INTEDGx bit in the INTCON2 register is set (= 1), the interrupt is triggered by a rising edge. If that bit is clear, the trigger is on the falling edge.

When a valid edge appears on the RBx/INTx pin, the corresponding flag bit, INTxIF, is set. This interrupt can be disabled by clearing the corresponding enable bit, INTxIE. Before re-enabling the interrupt, the flag bit (INTxIF) must be cleared in software in the Interrupt Service Routine.

All external interrupts (INT0, INT1, INT2 and INT3) can wake up the processor from the power-managed modes, if bit, INTxIE, was set prior to going into the power-managed modes. If the Global Interrupt Enable bit (GIE) is set, the processor will branch to the interrupt vector following wake-up.

The interrupt priority for INT1, INT2 and INT3 is determined by the value contained in the Interrupt Priority bits, INT1IP (INTCON3<6>), INT2IP (INTCON3<7>) and INT3IP (INTCON2<1>).

There is no priority bit associated with INT0; it is always a high-priority interrupt source.

#### 10.7 TMR0 Interrupt

In 8-bit mode (the default), an overflow in the TMR0 register (FFh  $\rightarrow$  00h) will set flag bit, TMR0IF. In 16-bit mode, an overflow in the TMR0H:TMR0L register pair (FFFFh  $\rightarrow$  0000h) will set TMR0IF.

The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit, TMR0IP (INTCON2<2>). For further details on the Timer0 module, see **Section 13.0 "Timer0 Module"**.

## 10.8 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>), and each individual pin can be enabled/disabled by its corresponding bit in the IOCB register.

Interrupt priority for PORTB interrupt-on-change is determined by the value contained in the interrupt priority bit, RBIP (INTCON2<0>).

| REGISTER 10-20: | IOCB: INTERRUPT-ON-CHANGE PORTB CONTROL REGISTER |  |

|-----------------|--------------------------------------------------|--|

|                 |                                                  |  |

| R/W-0                | R/W-0                | R/W-0                | R/W-0                | U-0 | U-0 | U-0 | U-0   |

|----------------------|----------------------|----------------------|----------------------|-----|-----|-----|-------|

| IOCB7 <sup>(1)</sup> | IOCB6 <sup>(1)</sup> | IOCB5 <sup>(1)</sup> | IOCB4 <sup>(1)</sup> | —   | —   | —   | —     |

| bit 7                |                      |                      |                      |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| ontrol bits <sup>(1)</sup> |

|----------------------------|

| ontrol bits <sup>(1)</sup> |

1 = Interrupt-on-change is enabled

0 = Interrupt-on-change is disabled

bit 3-0 Unimplemented: Read as '0'

Note 1: Interrupt-on-change also requires that the RBIE bit of the INTCON register be set.

In addition to the expanded range of modes available through the CCP1CON and ECCP1AS registers, the ECCP module has two additional registers associated with Enhanced PWM operation and auto-shutdown features. They are:

- ECCP1DEL Enhanced PWM Control

- PSTR1CON Pulse Steering Control

# 20.1 ECCP Outputs and Configuration

The Enhanced CCP module may have up to four PWM outputs, depending on the selected operating mode. The CCP1CON register is modified to allow control over four PWM outputs: ECCP1/P1A, P1B, P1C and P1D. Applications can use one, two or four of these outputs.

The outputs that are active depend on the ECCP operating mode selected. The pin assignments are summarized in Table 20-2.

To configure the I/O pins as PWM outputs, the proper PWM mode must be selected by setting the P1M<1:0> and CCP1M<3:0> bits. The appropriate TRIS direction bits for the port pins must also be set as outputs.

#### 20.1.1 ECCP MODULE AND TIMER RESOURCES

The ECCP modules use Timers, 1, 2, 3 and 4, depending on the mode selected. These timers are available to CCP modules in Capture, Compare or PWM modes, as shown in Table 20-1.

#### TABLE 20-1: ECCP MODE – TIMER RESOURCE

| ECCP Mode | Timer Resource   |

|-----------|------------------|

| Capture   | Timer1 or Timer3 |

| Compare   | Timer1 or Timer3 |

| PWM       | Timer2 or Timer4 |

The assignment of a particular timer to a module is determined by the Timer to ECCP enable bits in the CCPTMRS register (Register 20-2). The interactions between the two modules are depicted in Figure 20-1. Capture operations are designed to be used when the timer is configured for Synchronous Counter mode. Capture operations may not work as expected if the associated timer is configured for Asynchronous Counter mode.

## 20.2 Capture Mode

In Capture mode, the CCPR1H:CCPR1L register pair captures the 16-bit value of the TMR1 or TMR3 registers when an event occurs on the corresponding ECCP1 pin. An event is defined as one of the following:

- · Every falling edge

- · Every rising edge

- Every fourth rising edge

- Every 16<sup>th</sup> rising edge

The event is selected by the mode select bits, CCP1M<3:0> (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit, CCP1IF, is set (PIR3<1>). The flag must be cleared by software. If another capture occurs before the value in the CCPR1H/L register is read, the old captured value is overwritten by the new captured value.

## 20.2.1 ECCP PIN CONFIGURATION

In Capture mode, the appropriate ECCP1 pin should be configured as an input by setting the corresponding TRIS direction bit.

**Note:** If the ECCP1 pin is configured as an output, a write to the port can cause a capture condition.

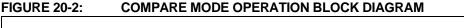

## 20.3 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the Timer register pair value selected in the CCPTMR1 register. When a match occurs, the ECCP1 pin can be:

- Driven high

- Driven low

- Toggled (high-to-low or low-to-high)

- Unchanged (that is, reflecting the state of the I/O latch)

The action on the pin is based on the value of the mode select bits (CCP1M<3:0>). At the same time, the interrupt flag bit, CCP1IF, is set.

#### 20.3.1 ECCP PIN CONFIGURATION

Users must configure the ECCP1 pin as an output by clearing the appropriate TRIS bit.

| Note: | Clearing the C  | CP1CON re      | egister wil | I force |

|-------|-----------------|----------------|-------------|---------|

|       | the ECCP1       | compare        | output      | latch   |

|       | (depending on   | device conf    | iguration)  | to the  |

|       | default low lev | /el. This is r | not the pe  | ort I/O |

|       | data latch.     |                |             |         |

#### 20.3.2 TIMER1/2/3/4 MODE SELECTION

Timer1, 2, 3 or 4 must be running in Timer mode or Synchronized Counter mode if the ECCP module is using the compare feature. In Asynchronous Counter mode, the compare operation will not work reliably.

#### 20.3.3 SOFTWARE INTERRUPT MODE

When the Generate Software Interrupt mode is chosen (CCP1M<3:0> = 1010), the ECCP1 pin is not affected; only the CCP1IF interrupt flag is affected.

#### 20.3.4 SPECIAL EVENT TRIGGER

The ECCP module is equipped with a Special Event Trigger. This is an internal hardware signal generated in Compare mode to trigger actions by other modules. The Special Event Trigger is enabled by selecting the Compare Special Event Trigger mode (CCP1M<3:0> = 1011).

The Special Event Trigger resets the Timer register pair for whichever timer resource is currently assigned as the module's time base. This allows the CCPR1 registers to serve as a programmable Period register for either timer.

The Special Event Trigger can also start an A/D conversion. In order to do this, the A/D Converter must already be enabled.

# REGISTER 20-5: PSTR1CON: PULSE STEERING CONTROL<sup>(1)</sup>

| bit 7 bit 0 |       |     |         |       |       |       |       |

|-------------|-------|-----|---------|-------|-------|-------|-------|

| CMPL1       | CMPL0 | —   | STRSYNC | STRD  | STRC  | STRB  | STRA  |

| R/W-0       | R/W-0 | U-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-1 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-6 | CMPL<1:0>: Complementary Mode Output Assignment Steering Sync bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 00 = See STR < D:A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | 01 = PA and PB are selected as the complementary output pair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | 10 = PA and PC are selected as the complementary output pair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6:4 C   | 11 = PA and PD are selected as the complementary output pair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 4   | STRSYNC: Steering Sync bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | 1 = Output steering update occurs on the next PWM period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | 0 = Output steering update occurs at the beginning of the instruction cycle boundary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| bit 3   | STRD: Steering Enable bit D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | 1 = P1D pin has the PWM waveform with polarity control from CCP1M<1:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | 0 = P1D pin is assigned to port pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| bit 2   | STRC: Steering Enable bit C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | 1 = P1C pin has the PWM waveform with polarity control from CCP1M<1:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | 0 = P1C pin is assigned to port pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| bit 1   | STRB: Steering Enable bit B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | 1 = P1B pin has the PWM waveform with polarity control from CCP1M<1:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |