#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | ECANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.6K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x12b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26k80-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                                                     | Pin<br>Num | Pin<br>Type | Buffer<br>Type   | Description                                                      |  |  |  |

|------------------------------------------------------------------------------|------------|-------------|------------------|------------------------------------------------------------------|--|--|--|

|                                                                              |            |             |                  | PORTC is a bidirectional I/O port.                               |  |  |  |

| RC0/SOSCO/SCLKI                                                              | 48         |             |                  |                                                                  |  |  |  |

| RC0                                                                          |            | I/O         | ST/<br>CMOS      | Digital I/O.                                                     |  |  |  |

| SOSCO                                                                        |            | Ι           | ST               | Timer1 oscillator output.                                        |  |  |  |

| SCLKI                                                                        |            | I           | ST               | Digital SOSC input.                                              |  |  |  |

| RC1/SOSCI                                                                    | 49         |             |                  |                                                                  |  |  |  |

| RC1                                                                          |            | I/O         | ST/<br>CMOS      | Digital I/O.                                                     |  |  |  |

| SOSCI                                                                        |            | Ι           | CMOS             | SOSC oscillator input.                                           |  |  |  |

| RC2/T1G/CCP2                                                                 | 50         |             |                  |                                                                  |  |  |  |

| RC2                                                                          |            | I/O         | ST/<br>CMOS      | Digital I/O.                                                     |  |  |  |

| T1G                                                                          |            | Ι           | ST               | Timer1 external clock gate input.                                |  |  |  |

| CCP2                                                                         |            | I/O         | ST               | Capture 2 input/Compare 2 output/PWM2 output.                    |  |  |  |

| RC3/REFO/SCL/SCK                                                             | 51         |             |                  |                                                                  |  |  |  |

| RC3                                                                          |            | I/O         | ST/<br>CMOS      | Digital I/O.                                                     |  |  |  |

| REFO                                                                         |            | 0           | CMOS             | Reference clock out.                                             |  |  |  |

| SCL                                                                          |            | I/O         | l <sup>2</sup> C | Synchronous serial clock input/output for I <sup>2</sup> C mode. |  |  |  |

| SCK                                                                          |            | I/O         | ST               | Synchronous serial clock input/output for SPI mode.              |  |  |  |

| RC4/SDA/SDI                                                                  | 62         |             |                  |                                                                  |  |  |  |

| RC4                                                                          |            | I/O         | ST/<br>CMOS      | Digital I/O.                                                     |  |  |  |

| SDA                                                                          |            | I/O         | l <sup>2</sup> C | I <sup>2</sup> C data input/output.                              |  |  |  |

| SDI                                                                          |            | Ι           | ST               | SPI data in.                                                     |  |  |  |

| RC5/SDO                                                                      | 63         |             |                  |                                                                  |  |  |  |

| RC5                                                                          |            | I/O         | ST/<br>CMOS      | Digital I/O.                                                     |  |  |  |

| SDO                                                                          |            | 0           | CMOS             | SPI data out.                                                    |  |  |  |

| RC6/CCP3                                                                     | 64         |             |                  |                                                                  |  |  |  |

| RC6                                                                          |            | I/O         | ST/<br>CMOS      | Digital I/O.                                                     |  |  |  |

| CCP3                                                                         |            | I/O         | ST/<br>CMOS      | Capture 3 input/Compare 3 output/PWM3 output.                    |  |  |  |

| RC7/CCP4                                                                     | 1          |             |                  |                                                                  |  |  |  |

| RC7                                                                          |            | I/O         | ST/<br>CMOS      | Digital I/O.                                                     |  |  |  |

| CCP4                                                                         |            | I/O         | ST/<br>CMOS      | Capture 4 input/Compare 4 output/PWM4 output.                    |  |  |  |

| <b>Legend:</b> $I^2C^{TM} = I^2C/S$<br>ST = Schmit<br>I = Input<br>P = Power |            |             | er               | CMOS = CMOS compatible input or output                           |  |  |  |

#### TABLE 1-6: PIC18F6XK80 PINOUT I/O DESCRIPTIONS (CONTINUED)

### 2.4 Voltage Regulator Pins (ENVREG and VCAP/VDDCORE)

The on-chip voltage regulator enable pin, ENVREG, must always be connected directly to either a supply voltage or to ground. Tying ENVREG to VDD enables the regulator, while tying it to ground disables the regulator. Refer to **Section 28.3 "On-Chip Voltage Regulator"** for details on connecting and using the on-chip regulator.

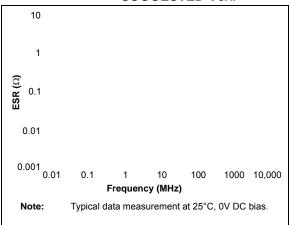

When the regulator is enabled, a low-ESR (< 5 $\Omega$ ) capacitor is required on the VCAP/VDDCORE pin to stabilize the voltage regulator output voltage. The VCAP/VDDCORE pin must not be connected to VDD and must use a capacitor of 10  $\mu$ F connected to ground. The type can be ceramic or tantalum. Suitable examples of capacitors are shown in Table 2-1. Capacitors with equivalent specifications can be used.

Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices.

It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to **Section 31.0** "**Electrical Characteristics**" for additional information.

When the regulator is disabled, the VCAP/VDDCORE pin must be tied to a voltage supply at the VDDCORE level. Refer to **Section 31.0** "**Electrical Characteristics**" for information on VDD and VDDCORE. Some PIC18FXXKXX families, or some devices within a family, do not provide the option of enabling or disabling the on-chip voltage regulator:

- Some devices (with the name, PIC18LFXXKXX) permanently disable the voltage regulator. These devices do not have the ENVREG pin and require a 0.1  $\mu$ F capacitor on the VCAP/VDDCORE pin. The VDD level of these devices must comply with the "voltage regulator disabled" specification for Parameter D001, in Section 31.0 "Electrical Characteristics".

- Some devices permanently enable the voltage regulator. These devices also do not have the ENVREG pin. The 10  $\mu$ F capacitor is still required on the

FIGURE 2-3:

VCAP/VDDCORE pin.

FREQUENCY vs. ESR PERFORMANCE FOR SUGGESTED VCAP

### TABLE 2-1: SUITABLE CAPACITOR EQUIVALENTS

| Make      | Part #             | Nominal<br>Capacitance | Base Tolerance | Rated Voltage | Temp. Range  |

|-----------|--------------------|------------------------|----------------|---------------|--------------|

| TDK       | C3216X7R1C106K     | 10 µF                  | ±10%           | 16V           | -55 to 125°C |

| TDK       | C3216X5R1C106K     | 10 µF                  | ±10%           | 16V           | -55 to 85°C  |

| Panasonic | ECJ-3YX1C106K      | 10 µF                  | ±10%           | 16V           | -55 to 125°C |

| Panasonic | ECJ-4YB1C106K      | 10 µF                  | ±10%           | 16V           | -55 to 85°C  |

| Murata    | GRM32DR71C106KA01L | 10 µF                  | ±10%           | 16V           | -55 to 125°C |

| Murata    | GRM31CR61C106KC31L | 10 µF                  | ±10%           | 16V           | -55 to 85°C  |

#### 5.4 Brown-out Reset (BOR)

The PIC18F66K80 family has four BOR Power modes:

- High-Power BOR

- Medium Power BOR

- Low-Power BOR

- Zero-Power BOR

Each power mode is selected by the BORPWR<1:0> setting (CONFIG2L<6:5>). For low, medium and high-power BOR, the module monitors the VDD depending on the BORV<1:0> setting (CONFIG1L<3:2>). The typical current draw ( $\Delta$ IBOR) for zero, low and medium power BOR is 200 nA, 750 nA and 3  $\mu$ A, respectively. A BOR event re-arms the Power-on Reset. It also causes a Reset, depending on which of the trip levels has been set: 1.8V, 2V, 2.7V or 3V.

BOR is enabled by BOREN<1:0> (CONFIG2L<2:1>) and the SBOREN bit (RCON<6>). The four BOR configurations are summarized in Table 5-1.

In Zero-Power BOR (ZPBORMV), the module monitors the VDD voltage and re-arms the POR at about 2V. ZPBORMV does not cause a Reset, but re-arms the POR.

The BOR accuracy varies with its power level. The lower the power setting, the less accurate the BOR trip levels are. Therefore, the high-power BOR has the highest accuracy and the low-power BOR has the lowest accuracy. The trip levels (BVDD, Parameter D005), current consumption (Section 31.2 "DC Characteristics: Power-Down and Supply Current PIC18F66K80 Family (Industrial/Extended)") and time required below BVDD (TBOR, Parameter 35) can all be found in Section 31.0 "Electrical Characteristics".

#### 5.4.1 SOFTWARE ENABLED BOR

When BOREN<1:0> = 01, the BOR can be enabled or disabled by the user in software. This is done with the control bit, SBOREN (RCON<6>). Setting SBOREN enables the BOR to function as previously described. Clearing SBOREN disables the BOR entirely. The SBOREN bit operates only in this mode; otherwise it is read as '0'. Placing the BOR under software control gives the user the additional flexibility of tailoring the application to its environment without having to reprogram the device to change BOR configuration. It also allows the user to tailor device power consumption in software by eliminating the incremental current that the BOR consumes. While the BOR current is typically very small, it may have some impact in low-power applications.

| Note: | Even when BOR is under software con-<br>trol, the Brown-out Reset voltage level is |

|-------|------------------------------------------------------------------------------------|

|       | still set by the BORV<1:0> Configuration bits; it cannot be changed in software.   |

#### 5.4.2 DETECTING BOR

When Brown-out Reset is enabled, the BOR bit always resets to '0' on any Brown-out Reset or Power-on Reset event. This makes it difficult to determine if a Brown-out Reset event has occurred just by reading the state of BOR alone. A more reliable method is to simultaneously check the state of both POR and BOR. This assumes that the POR bit is reset to '1' in software immediately after any Power-on Reset event. IF BOR is '0' while POR is '1', it can be reliably assumed that a Brown-out Reset event has occurred.

#### 5.4.3 DISABLING BOR IN SLEEP MODE

When BOREN<1:0> = 10, the BOR remains under hardware control and operates as previously described. Whenever the device enters Sleep mode, however, the BOR is automatically disabled. When the device returns to any other operating mode, BOR is automatically re-enabled.

This mode allows for applications to recover from brown-out situations, while actively executing code, when the device requires BOR protection the most. At the same time, it saves additional power in Sleep mode by eliminating the small incremental BOR current.

| BOR Con | BOR Configuration |                     |                                                                                       |

|---------|-------------------|---------------------|---------------------------------------------------------------------------------------|

| BOREN1  | BOREN0            | SBOREN<br>(RCON<6>) | BOR Operation                                                                         |

| 0       | 0                 | Unavailable         | BOR is disabled; must be enabled by reprogramming the Configuration bits.             |

| 0       | 1                 | Available           | BOR is enabled in software; operation is controlled by SBOREN.                        |

| 1       | 0                 | Unavailable         | BOR is enabled in hardware, in Run and Idle modes; disabled during Sleep mode.        |

| 1       | 1                 | Unavailable         | BOR is enabled in hardware; must be disabled by reprogramming the Configuration bits. |

TABLE 5-1:BOR CONFIGURATIONS

| R/W-0         | R/W-0                          | R/W-0            | R/W-0            | U-0              | R/W-0            | R/W-0           | R/W-0  |

|---------------|--------------------------------|------------------|------------------|------------------|------------------|-----------------|--------|

| TMR4IE        | EEIE                           | CMP2IE           | CMP1IE           | —                | CCP5IE           | CCP4IE          | CCP3IE |

| bit 7         |                                |                  |                  |                  |                  | •<br>•          | bit 0  |

|               |                                |                  |                  |                  |                  |                 |        |

| Legend:       |                                |                  |                  |                  |                  |                 |        |

| R = Readable  | e bit                          | W = Writable     | bit              | U = Unimple      | mented bit, read | d as '0'        |        |

| -n = Value at | POR                            | '1' = Bit is set |                  | '0' = Bit is cle | eared            | x = Bit is unkr | nown   |

| L:1 7         |                                |                  | to my unt Elon b | :4               |                  |                 |        |

| bit 7         | 1 = Interrupt                  | R4 Overflow In   | terrupt Flag b   | iit.             |                  |                 |        |

|               | 0 = Interrupt                  |                  |                  |                  |                  |                 |        |

| bit 6         | •                              | EDATA/Flash      | Nrite Operatio   | on Interrupt Fla | a bit            |                 |        |

|               | 1 = Interrupt                  |                  |                  |                  | 5                |                 |        |

|               | 0 = Interrupt                  | is disabled      |                  |                  |                  |                 |        |

| bit 5         | CMP2IE: CM                     | P2 Interrupt Fl  | ag bit           |                  |                  |                 |        |

|               | 1 = Interrupt                  |                  |                  |                  |                  |                 |        |

|               | 0 = Interrupt                  |                  |                  |                  |                  |                 |        |

| bit 4         |                                | P1 Interrupt Fl  | ag bit           |                  |                  |                 |        |

|               | 1 = Interrupt<br>0 = Interrupt |                  |                  |                  |                  |                 |        |

| bit 3         | •                              | ted: Read as '   | 0'               |                  |                  |                 |        |

| bit 2         | -                              | P5 Interrupt Fla |                  |                  |                  |                 |        |

|               | 1 = Interrupt                  | •                | 3                |                  |                  |                 |        |

|               | 0 = Interrupt                  |                  |                  |                  |                  |                 |        |

| bit 1         | CCP4IE: CCI                    | P4 Interrupt Fla | ag bit           |                  |                  |                 |        |

|               | 1 = Interrupt                  |                  |                  |                  |                  |                 |        |

|               | 0 = Interrupt                  |                  |                  |                  |                  |                 |        |

| bit 0         |                                | P3 Interrupt Fla | ag bits          |                  |                  |                 |        |

|               | 1 = Interrupt                  |                  |                  |                  |                  |                 |        |

|               | 0 = Interrupt                  |                  |                  |                  |                  |                 |        |

#### REGISTER 10-12: PIE4: PERIPHERAL INTERRUPT ENABLE REGISTER 4

#### 10.6 INTx Pin Interrupts

External interrupts on the RB0/INT0, RB1/INT1, RB2/INT2 and RB3/INT3 pins are edge-triggered. If the corresponding INTEDGx bit in the INTCON2 register is set (= 1), the interrupt is triggered by a rising edge. If that bit is clear, the trigger is on the falling edge.

When a valid edge appears on the RBx/INTx pin, the corresponding flag bit, INTxIF, is set. This interrupt can be disabled by clearing the corresponding enable bit, INTxIE. Before re-enabling the interrupt, the flag bit (INTxIF) must be cleared in software in the Interrupt Service Routine.

All external interrupts (INT0, INT1, INT2 and INT3) can wake up the processor from the power-managed modes, if bit, INTxIE, was set prior to going into the power-managed modes. If the Global Interrupt Enable bit (GIE) is set, the processor will branch to the interrupt vector following wake-up.

The interrupt priority for INT1, INT2 and INT3 is determined by the value contained in the Interrupt Priority bits, INT1IP (INTCON3<6>), INT2IP (INTCON3<7>) and INT3IP (INTCON2<1>).

There is no priority bit associated with INT0; it is always a high-priority interrupt source.

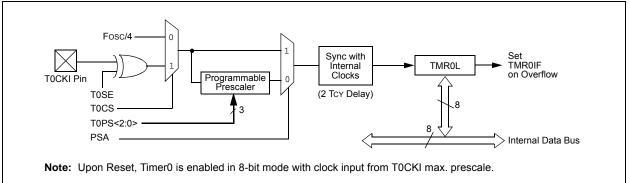

#### 10.7 TMR0 Interrupt

In 8-bit mode (the default), an overflow in the TMR0 register (FFh  $\rightarrow$  00h) will set flag bit, TMR0IF. In 16-bit mode, an overflow in the TMR0H:TMR0L register pair (FFFFh  $\rightarrow$  0000h) will set TMR0IF.

The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit, TMR0IP (INTCON2<2>). For further details on the Timer0 module, see **Section 13.0 "Timer0 Module"**.

#### 10.8 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>), and each individual pin can be enabled/disabled by its corresponding bit in the IOCB register.

Interrupt priority for PORTB interrupt-on-change is determined by the value contained in the interrupt priority bit, RBIP (INTCON2<0>).

| REGISTER 10-20: | IOCB: INTERRUPT-ON-CHANGE PORTB CONTROL REGISTER |  |

|-----------------|--------------------------------------------------|--|

|                 |                                                  |  |

| R/W-0                | R/W-0                | R/W-0                | R/W-0                | U-0 | U-0 | U-0 | U-0 |  |

|----------------------|----------------------|----------------------|----------------------|-----|-----|-----|-----|--|

| IOCB7 <sup>(1)</sup> | IOCB6 <sup>(1)</sup> | IOCB5 <sup>(1)</sup> | IOCB4 <sup>(1)</sup> | —   | —   | —   | —   |  |

| bit 7 bit 0          |                      |                      |                      |     |     |     |     |  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| ontrol bits <sup>(1)</sup> |

|----------------------------|

| ontrol bits <sup>(1)</sup> |

1 = Interrupt-on-change is enabled

0 = Interrupt-on-change is disabled

bit 3-0 Unimplemented: Read as '0'

Note 1: Interrupt-on-change also requires that the RBIE bit of the INTCON register be set.

### 13.1 Timer0 Operation

Timer0 can operate as either a timer or a counter. The mode is selected with the TOCS bit (TOCON<5>). In Timer mode (TOCS = 0), the module increments on every clock by default unless a different prescaler value is selected (see **Section 13.3 "Prescaler"**). If the TMR0 register is written to, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

The Counter mode is selected by setting the T0CS bit (= 1). In this mode, Timer0 increments either on every rising edge or falling edge of the T0CKI pin. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (T0CON<4>); clearing this bit selects the rising edge. Restrictions on the external clock input are discussed below.

An external clock source can be used to drive Timer0; however, it must meet certain requirements to ensure that the external clock can be synchronized with the internal phase clock (Tosc). There is a delay between synchronization and the onset of incrementing the timer/counter.

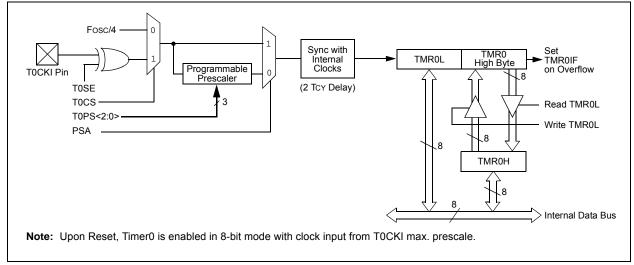

#### 13.2 Timer0 Reads and Writes in 16-Bit Mode

TMR0H is not the actual high byte of Timer0 in 16-bit mode. It is actually a buffered version of the real high byte of Timer0, which is not directly readable nor writable. (See Figure 13-2.) TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte were valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

#### FIGURE 13-1: TIMER0 BLOCK DIAGRAM (8-BIT MODE)

#### FIGURE 13-2: TIMER0 BLOCK DIAGRAM (16-BIT MODE)

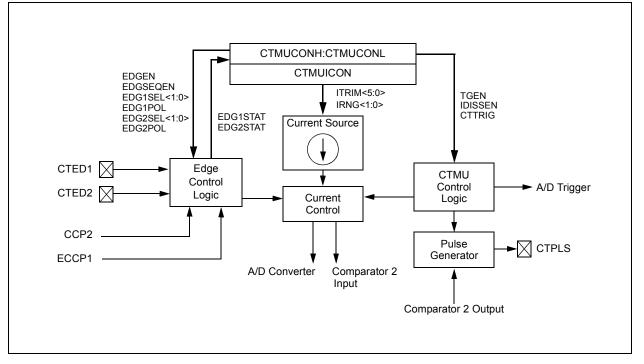

### 18.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

The Charge Time Measurement Unit (CTMU) is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. By working with other on-chip analog modules, the CTMU can precisely measure time, capacitance and relative changes in capacitance or generate output pulses with a specific time delay. The CTMU is ideal for interfacing with capacitive-based sensors.

The module includes these key features:

- Up to 11 channels available for capacitive or time measurement input

- Low-cost temperature measurement using on-chip diode channel

- On-chip precision current source

- Four-edge input trigger sources

- · Polarity control for each edge source

- · Control of edge sequence

- · Control of response to edges

- · Time measurement resolution of 1 nanosecond

- High-precision time measurement

- Time delay of external or internal signal asynchronous to system clock

- Accurate current source suitable for capacitive measurement

The CTMU works in conjunction with the A/D Converter to provide up to 11 channels for time or charge measurement, depending on the specific device and the number of A/D channels available. When configured for time delay, the CTMU is connected to one of the analog comparators. The level-sensitive input edge sources can be selected from four sources: two external inputs or the ECCP1/CCP2 Special Event Triggers.

The CTMU special event can trigger the Analog-to-Digital Converter module.

Figure 18-1 provides a block diagram of the CTMU.

#### FIGURE 18-1: CTMU BLOCK DIAGRAM

### 20.4 PWM (Enhanced Mode)

The Enhanced PWM mode can generate a PWM signal on up to four different output pins with up to 10 bits of resolution. It can do this through four different PWM Output modes:

- Single PWM

- Half-Bridge PWM

- Full-Bridge PWM, Forward mode

- Full-Bridge PWM, Reverse mode

To select an Enhanced PWM mode, the P1M bits of the CCP1CON register must be set appropriately.

The PWM outputs are multiplexed with I/O pins and are designated: P1A, P1B, P1C and P1D. The polarity of the PWM pins is configurable and is selected by setting the CCP1M bits in the CCP1CON register appropriately.

Table 20-1 provides the pin assignments for each Enhanced PWM mode.

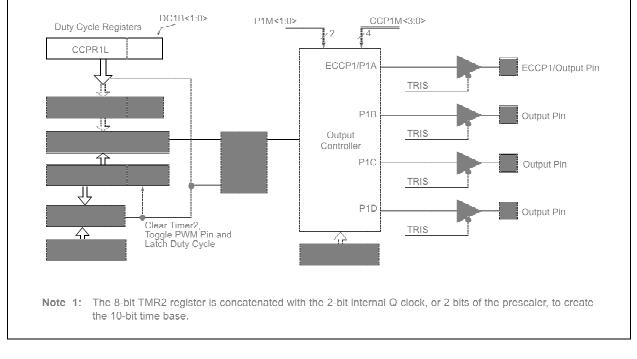

Figure 20-3 provides an example of a simplified block diagram of the Enhanced PWM module.

**Note:** To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

#### FIGURE 20-3: EXAMPLE SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODE

Note 1: The TRIS register value for each PWM output must be configured appropriately.2: Any pin not used by an Enhanced PWM mode is available for alternate pin functions.

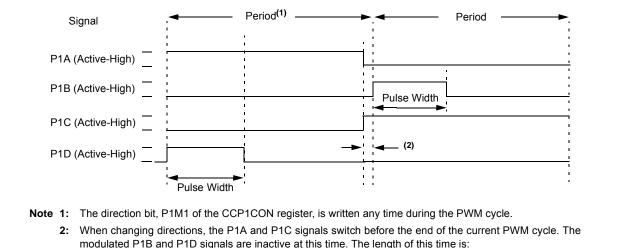

### 20.4.2.1 Direction Change in Full-Bridge Mode

In the Full-Bridge mode, the P1M1 bit in the CCP1CON register allows users to control the forward/reverse direction. When the application firmware changes this direction control bit, the module will change to the new direction on the next PWM cycle.

A direction change is initiated in software by changing the P1M1 bit of the CCP1CON register. The following sequence occurs prior to the end of the current PWM period:

- The modulated outputs (P1B and P1D) are placed in their inactive state.

- The associated unmodulated outputs (P1A and P1C) are switched to drive in the opposite direction.

- PWM modulation resumes at the beginning of the next period.

For an illustration of this sequence, see Figure 20-10.

The Full-Bridge mode does not provide a dead-band delay. As one output is modulated at a time, a dead-band delay is generally not required. There is a situation where a dead-band delay is required. This situation occurs when both of the following conditions are true:

- The direction of the PWM output changes when the duty cycle of the output is at or near 100%.

- The turn-off time of the power switch, including the power device and driver circuit, is greater than the turn-on time.

Figure 20-11 shows an example of the PWM direction changing from forward to reverse, at a near 100% duty cycle. In this example, at time, t1, the P1A and P1D outputs become inactive, while the P1C output becomes active. Since the turn-off time of the power devices is longer than the turn-on time, a shoot-through current will flow through power devices, QC and QD (see Figure 20-8), for the duration of 't'. The same phenomenon will occur to power devices, QA and QB, for PWM direction change from reverse to forward.

If changing PWM direction at high duty cycle is required for an application, two possible solutions for eliminating the shoot-through current are:

- Reduce PWM duty cycle for one PWM period before changing directions.

- Use switch drivers that can drive the switches off faster than they can drive them on.

Other options to prevent shoot-through current may exist.

#### FIGURE 20-10: EXAMPLE OF PWM DIRECTION CHANGE

(1/FOSC) • TMR2 Prescale Value.

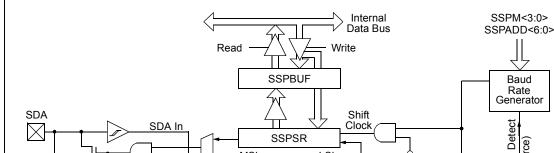

#### 21.4.6 MASTER MODE

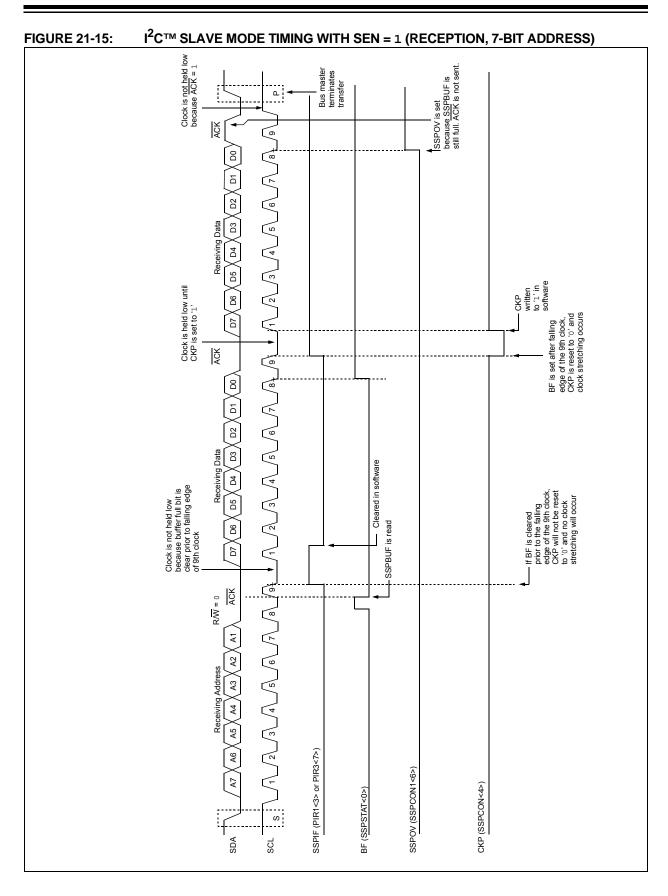

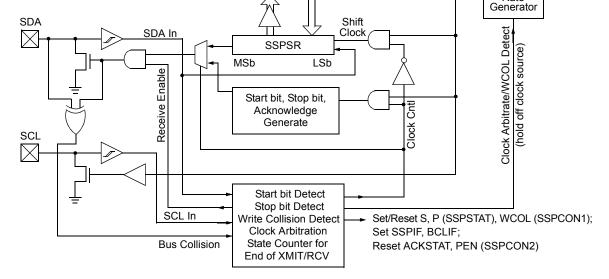

Master mode is enabled by setting and clearing the appropriate SSPMx bits in SSPCON1 and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware if the TRIS bits are set.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  $I^2C$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a Start condition on SDA and SCL.

- 2. Assert a Repeated Start condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Configure the  $I^2C$  port to receive data.

**FIGURE 21-18:**

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

Note: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause the MSSP Interrupt Flag bit, SSPIF, to be set (and MSSP interrupt, if enabled):

- Start condition

- Stop condition

- · Data transfer byte transmitted/received

- Acknowledge transmitted

- Repeated Start

MSSP BLOCK DIAGRAM (I<sup>2</sup>C<sup>™</sup> MASTER MODE)

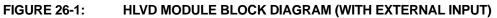

The module is enabled by setting the HLVDEN bit (HLVDCON<4>). Each time the HLVD module is enabled, the circuitry requires some time to stabilize. The IRVST bit (HLVDCON<5>) is a read-only bit used to indicate when the circuit is stable. The module can only generate an interrupt after the circuit is stable and IRVST is set.

The VDIRMAG bit (HLVDCON<7>) determines the overall operation of the module. When VDIRMAG is cleared, the module monitors for drops in VDD below a predetermined set point. When the bit is set, the module monitors for rises in VDD above the set point.

#### 26.1 Operation

When the HLVD module is enabled, a comparator uses an internally generated reference voltage as the set point. The set point is compared with the trip point, where each node in the resistor divider represents a trip point voltage. The "trip point" voltage is the voltage level at which the device detects a high or low-voltage event, depending on the configuration of the module.

When the supply voltage is equal to the trip point, the voltage tapped off of the resistor array is equal to the internal reference voltage generated by the voltage reference module. The comparator then generates an interrupt signal by setting the HLVDIF bit.

The trip point voltage is software programmable to any one of 16 values. The trip point is selected by programming the HLVDL<3:0> bits (HLVDCON<3:0>).

The HLVD module has an additional feature that allows the user to supply the trip voltage to the module from an external source. This mode is enabled when bits, HLVDL<3:0>, are set to '1111'. In this state, the comparator input is multiplexed from the external input pin, HLVDIN. This gives users the flexibility of configuring the High/Low-Voltage Detect interrupt to occur at any voltage in the valid operating range.

| R/W-0                                                                | R/W-0                                                                                                 | U-0                                                                                                                                                   | U-0                                                                                            | U-0                       | R/W-0                  | R/W-0                  | R/W-0                  |  |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------|------------------------|------------------------|------------------------|--|

| WAKDIS                                                               | WAKFIL                                                                                                | —                                                                                                                                                     | _                                                                                              | _                         | SEG2PH2 <sup>(1)</sup> | SEG2PH1 <sup>(1)</sup> | SEG2PH0 <sup>(1)</sup> |  |

| bit 7                                                                |                                                                                                       | ·                                                                                                                                                     |                                                                                                | -                         | ·                      |                        | bit 0                  |  |

| Legend:                                                              |                                                                                                       |                                                                                                                                                       |                                                                                                |                           |                        |                        |                        |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                                                       |                                                                                                                                                       |                                                                                                |                           |                        |                        |                        |  |

| -n = Value at I                                                      | POR                                                                                                   | '1' = Bit is set                                                                                                                                      |                                                                                                | '0' = Bit is cle          | ared                   | x = Bit is unkr        | nown                   |  |

| bit 7                                                                | 1 = Disable C                                                                                         | ke-up Disable I<br>AN bus activity<br>AN bus activity                                                                                                 | wake-up feat                                                                                   |                           |                        |                        |                        |  |

| bit 6                                                                | 1 = Use CAN                                                                                           | ects CAN bus L<br>bus line filter fo<br>line filter is not                                                                                            | or wake-up                                                                                     |                           |                        |                        |                        |  |

| bit 5-3                                                              | Unimplemen                                                                                            | ted: Read as '                                                                                                                                        | כי                                                                                             |                           |                        |                        |                        |  |

| bit 2-0                                                              | 111 = Phase<br>110 = Phase<br>101 = Phase<br>100 = Phase<br>011 = Phase<br>010 = Phase<br>001 = Phase | >: Phase Segn<br>Segment 2 tim<br>Segment 2 tim | e = 8 x TQ<br>e = 7 x TQ<br>e = 6 x TQ<br>e = 5 x TQ<br>e = 4 x TQ<br>e = 3 x TQ<br>e = 2 x TQ | elect bits <sup>(1)</sup> |                        |                        |                        |  |

#### REGISTER 27-54: BRGCON3: BAUD RATE CONTROL REGISTER 3

Note 1: These bits are ignored if SEG2PHTS bit (BRGCON2<7>) is '0'.

### 28.3.3 OPERATION OF REGULATOR IN SLEEP

The difference in the two regulators' operation arises with Sleep mode. The ultra low-power regulator gives the device the lowest current in the Regulator Enabled mode.

The on-chip regulator can go into a lower power mode when the device goes to Sleep by setting the REGSLP bit (WDTCON<7>). This puts the regulator in a standby mode so that the device consumes much less current.

The on-chip regulator can also go into the Ultra Low-Power mode, which consumes the lowest current possible with the <u>regulator</u> enabled. This mode is controlled by the <u>RETEN</u> bit (CONFIG1L<0>) and SRETEN bit (WDTCON<4>). The various modes of regulator operation are shown in Table 28-3.

When the ultra low-power regulator is in Sleep mode, the internal reference voltages in the chip will be shut off and any interrupts referring to the internal reference will not wake up the device. If the BOR or LVD is enabled, the regulator will keep the internal references on and the lowest possible current will not be achieved.

When using the ultra low-power regulator in Sleep mode, the device will take about 250  $\mu s$  to start executing code after it wakes up.

| Device       | Power Mode                                   | REGSLP<br>WDTCON<7> | SRETEN<br>WDTCON<4> | RETEN<br>CONFIG1L<0> |  |  |  |  |  |

|--------------|----------------------------------------------|---------------------|---------------------|----------------------|--|--|--|--|--|

| PIC18FXXK80  | Normal Operation (Sleep)                     | 0                   | х                   | 1                    |  |  |  |  |  |

| PIC18FXXK80  | Low-Power mode (Sleep)                       | 1                   | х                   | 1                    |  |  |  |  |  |

| PIC18FXXK80  | Normal Operation (Sleep)                     | 0                   | 0                   | 0                    |  |  |  |  |  |

| PIC18FXXK80  | Low-Power mode (Sleep)                       | 1                   | 0                   | 0                    |  |  |  |  |  |

| PIC18FXXK80  | Ultra Low-Power mode (Sleep)                 | x                   | 1                   | 0                    |  |  |  |  |  |

| PIC18LFXXK80 | Reserved <sup>(2)</sup>                      | х                   | Don't Care          | 0                    |  |  |  |  |  |

| PIC18LFXXK80 | Regulator Bypass mode (Sleep) <sup>(2)</sup> | x                   | х                   | 1                    |  |  |  |  |  |

#### TABLE 28-3: SLEEP MODE REGULATOR SETTINGS<sup>(1)</sup>

**Note 1:** x — Indicates that VIT status is invalid.

2: The ultra low-power regulator should be disabled (RETEN = 1, ULP disabled) on PIC18LFXXK80 devices to obtain the lowest possible Sleep current.

### 29.0 INSTRUCTION SET SUMMARY

The PIC18F66K80 family of devices incorporates the standard set of 75 PIC18 core instructions, as well as an extended set of 8 new instructions for the optimization of code that is recursive or that utilizes a software stack. The extended set is discussed later in this section.

#### 29.1 Standard Instruction Set

The standard PIC18 MCU instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from these PIC MCU instruction sets. Most instructions are a single program memory word (16 bits), but there are four instructions that require two program memory locations.

Each single-word instruction is a 16-bit word divided into an opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into four basic categories:

- Byte-oriented operations

- Bit-oriented operations

- · Literal operations

- Control operations

The PIC18 instruction set summary in Table 29-2 lists **byte-oriented**, **bit-oriented**, **literal** and **control** operations. Table 29-1 shows the opcode field descriptions.

Most byte-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The destination of the result (specified by 'd')

- 3. The accessed memory (specified by 'a')

The file register designator, 'f', specifies which file register is to be used by the instruction. The destination designator, 'd', specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the WREG register. If 'd' is one, the result is placed in the file register specified in the instruction.

All **bit-oriented** instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The bit in the file register (specified by 'b')

- 3. The accessed memory (specified by 'a')

The bit field designator, 'b', selects the number of the bit affected by the operation, while the file register designator, 'f', represents the number of the file in which the bit is located. The **literal** instructions may use some of the following operands:

- A literal value to be loaded into a file register (specified by 'k')

- The desired FSR register to load the literal value into (specified by 'f')

- No operand required (specified by '—')

The **control** instructions may use some of the following operands:

- A program memory address (specified by 'n')

- The mode of the CALL or RETURN instructions (specified by 's')

- The mode of the table read and table write instructions (specified by 'm')

- No operand required (specified by '—')

All instructions are a single word, except for four double-word instructions. These instructions were made double-word to contain the required information in 32 bits. In the second word, the 4 MSbs are '1's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

All single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the Program Counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP.

The double-word instructions execute in two instruction cycles.

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the Program Counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Two-word branch instructions (if true) would take 3  $\mu$ s.

Figure 29-1 shows the general formats that the instructions can have. All examples use the convention 'nnh' to represent a hexadecimal number.

The Instruction Set Summary, shown in Table 29-2, lists the standard instructions recognized by the Microchip MPASM<sup>™</sup> Assembler.

**Section 29.1.1 "Standard Instruction Set"** provides a description of each instruction.

| RET          | RETFIE Return from Interrupt                |                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                             |  |  |  |

|--------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|--|--|

| Synta        | ax:                                         | RETFIE {s}                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                             |  |  |  |

| Operands:    |                                             | $s \in [0,1]$                                                                                                         | s ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                        |                                             |  |  |  |

| Operation:   |                                             | $1 \rightarrow GIE/GI$<br>if s = 1,<br>(WS) $\rightarrow$ W,<br>(STATUSS)<br>(BSRS) $\rightarrow$ I                   | ,                                                                                                                                                                                                                                                                                                                                                                                                                |                                             |  |  |  |

| Statu        | s Affected:                                 | GIE/GIEH,                                                                                                             | PEIE/GIEL.                                                                                                                                                                                                                                                                                                                                                                                                       |                                             |  |  |  |

| Enco         | ding:                                       | 0000                                                                                                                  | 0000 000                                                                                                                                                                                                                                                                                                                                                                                                         | 01 000s                                     |  |  |  |

| Description: |                                             | and Top-of-<br>the PC. Inte<br>setting eithe<br>Global Inter<br>contents of<br>STATUSS a<br>their corres<br>STATUS an | Return from interrupt. Stack is popped<br>and Top-of-Stack (TOS) is loaded into<br>the PC. Interrupts are enabled by<br>setting either the high or low-priority<br>Global Interrupt Enable bit. If 's' = 1, the<br>contents of the shadow registers WS,<br>STATUSS and BSRS are loaded into<br>their corresponding registers W,<br>STATUS and BSR. If 's' = 0, no update<br>of these registers occurs (default). |                                             |  |  |  |

| Words:       |                                             | 1                                                                                                                     | ,                                                                                                                                                                                                                                                                                                                                                                                                                | ()                                          |  |  |  |

| Cycles:      |                                             | 2                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                             |  |  |  |

|              | ycle Activity:                              |                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                             |  |  |  |

| ~ ·          | Q1                                          | Q2                                                                                                                    | Q3                                                                                                                                                                                                                                                                                                                                                                                                               | Q4                                          |  |  |  |

|              | Decode                                      | No<br>operation                                                                                                       | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                  | POP PC<br>from stack<br>Set GIEH or<br>GIEL |  |  |  |

|              | No                                          | No                                                                                                                    | No                                                                                                                                                                                                                                                                                                                                                                                                               | No                                          |  |  |  |

|              | operation                                   | operation                                                                                                             | operation                                                                                                                                                                                                                                                                                                                                                                                                        | operation                                   |  |  |  |

| Exan         | After Interrupt<br>PC<br>W<br>BSR<br>STATUS | RETFIE 1                                                                                                              | = TOS<br>= WS<br>= BSRS<br>= STATL<br>= 1                                                                                                                                                                                                                                                                                                                                                                        | JSS                                         |  |  |  |

|              | LW                                                    | Return Lite                                        | eral to W                                                                                                                                                                                |                                     |  |  |  |  |

|--------------|-------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|--|--|--|

| Synt         | ax:                                                   | RETLW k                                            | RETLW k                                                                                                                                                                                  |                                     |  |  |  |  |

| Operands:    |                                                       | $0 \le k \le 255$                                  |                                                                                                                                                                                          |                                     |  |  |  |  |

| Oper         | ation:                                                | · · ·                                              | $k \rightarrow W$ ,<br>(TOS) $\rightarrow$ PC,<br>PCLATU, PCLATH are unchanged                                                                                                           |                                     |  |  |  |  |

| Statu        | s Affected:                                           | None                                               |                                                                                                                                                                                          |                                     |  |  |  |  |

| Enco         | ding:                                                 | 0000                                               | 1100 kł                                                                                                                                                                                  | kk kkkk                             |  |  |  |  |

| Description: |                                                       | The Progra<br>the top of th<br>The high ac         | W is loaded with the eight-bit literal 'k'.<br>The Program Counter is loaded from<br>the top of the stack (the return address).<br>The high address latch (PCLATH)<br>remains unchanged. |                                     |  |  |  |  |

| Word         | ls:                                                   | 1                                                  |                                                                                                                                                                                          |                                     |  |  |  |  |

| Cycle        | es:                                                   | 2                                                  |                                                                                                                                                                                          |                                     |  |  |  |  |

| 0 C          | ycle Activity:                                        |                                                    |                                                                                                                                                                                          |                                     |  |  |  |  |

|              | Q1                                                    | Q2                                                 | Q3                                                                                                                                                                                       | Q4                                  |  |  |  |  |

|              | Decode                                                | Read<br>literal 'k'                                | Process<br>Data                                                                                                                                                                          | POP PC<br>from stack,<br>write to W |  |  |  |  |

|              | No                                                    | No                                                 | No                                                                                                                                                                                       | No                                  |  |  |  |  |

|              | operation                                             | operation                                          | operation                                                                                                                                                                                |                                     |  |  |  |  |

|              | <u> </u>                                              |                                                    |                                                                                                                                                                                          | operation                           |  |  |  |  |

| <u>Exar</u>  | nple:                                                 |                                                    |                                                                                                                                                                                          | operation                           |  |  |  |  |

| Exar         | n <u>ple:</u><br>Call Table                           | ; W contai<br>; offset<br>; W now ha<br>; table va | ns table<br>value<br>as                                                                                                                                                                  |                                     |  |  |  |  |

| Exar         | CALL TABLE                                            | ; W contai<br>; offset v<br>; W now ha             | ns table<br>value<br>as                                                                                                                                                                  |                                     |  |  |  |  |

| :            | CALL TABLE<br>LE<br>ADDWF PCL<br>RETLW k0<br>RETLW k1 | ; W contai<br>; offset v<br>; W now ha             | ns table<br>value<br>as<br>alue<br>set                                                                                                                                                   |                                     |  |  |  |  |

| CALL TABLE          | ;   | W contains table |  |  |  |  |  |

|---------------------|-----|------------------|--|--|--|--|--|

|                     | ;   | offset value     |  |  |  |  |  |

|                     | ;   | W now has        |  |  |  |  |  |

|                     | ;   | table value      |  |  |  |  |  |

| :                   |     |                  |  |  |  |  |  |

| ABLE                |     |                  |  |  |  |  |  |

| ADDWF PCL           | ;   | W = offset       |  |  |  |  |  |

| RETLW k0            | ;   | Begin table      |  |  |  |  |  |

| RETLW k1            | ;   |                  |  |  |  |  |  |

| :                   |     |                  |  |  |  |  |  |

| :                   |     |                  |  |  |  |  |  |

| RETLW kn            | ;   | End of table     |  |  |  |  |  |

|                     |     |                  |  |  |  |  |  |

| Defense la standier |     |                  |  |  |  |  |  |

| Before Instruct     | IOI | 1                |  |  |  |  |  |

```

07h

W

=

After Instruction

```

```

W

value of kn

```

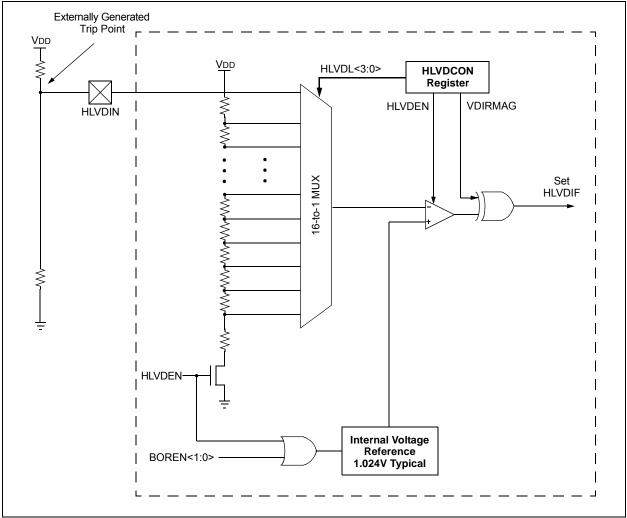

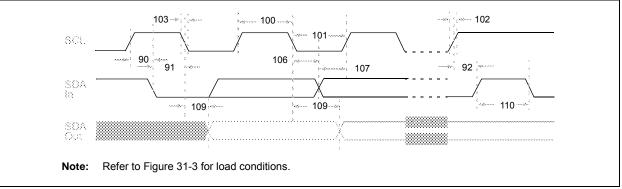

| Param.<br>No. | Symbol  | Characte        | ristic                    | Min              | Max | Units | Conditions               |

|---------------|---------|-----------------|---------------------------|------------------|-----|-------|--------------------------|

| 90            | TSU:STA | Start Condition | 100 kHz mode              | 2(Tosc)(BRG + 1) |     | ns    | Only relevant for        |

|               |         | Setup Time      | 400 kHz mode              | 2(Tosc)(BRG + 1) | _   |       | Repeated Start condition |

|               |         |                 | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _   |       |                          |

| 91            | THD:STA | Start Condition | 100 kHz mode              | 2(Tosc)(BRG + 1) | _   | ns    | After this period, the   |

|               |         | Hold Time       | 400 kHz mode              | 2(Tosc)(BRG + 1) | _   |       | first clock pulse is     |

|               |         |                 | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _   |       | generated                |

| 92            | Tsu:sto | Stop Condition  | 100 kHz mode              | 2(Tosc)(BRG + 1) | _   | ns    |                          |

|               |         | Setup Time      | 400 kHz mode              | 2(Tosc)(BRG + 1) | _   |       |                          |

|               |         |                 | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _   |       |                          |

| 93            | THD:STO | Stop Condition  | 100 kHz mode              | 2(Tosc)(BRG + 1) | _   | ns    |                          |

|               |         | Hold Time       | 400 kHz mode              | 2(Tosc)(BRG + 1) | _   | 1     |                          |

|               |         |                 | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _   | 1     |                          |

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C^{TM}$  pins.

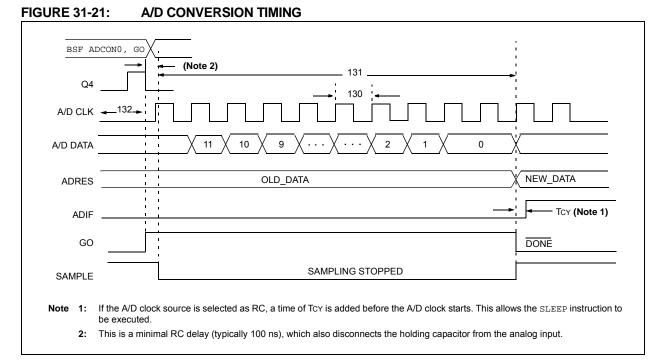

| TABLE 31-26: | A/D CONVERSION REQUIREMENTS |

|--------------|-----------------------------|

|--------------|-----------------------------|

| Param<br>No. | Symbol | Characteristic                                                     | Min | Мах                 | Units | Conditions                                 |

|--------------|--------|--------------------------------------------------------------------|-----|---------------------|-------|--------------------------------------------|

| 130          | Tad    | A/D Clock Period                                                   | 0.8 | 12.5 <sup>(1)</sup> | μS    | Tosc based, VREF $\geq$ 3.0V               |

|              |        |                                                                    | 1.4 | 25 <sup>(1)</sup>   | μS    | VDD = 3.0V; Tosc based,<br>VREF full range |

|              |        |                                                                    |     | 1                   | μS    | A/D RC mode                                |

|              |        |                                                                    | _   | 3                   | μS    | VDD = 3.0V; A/D RC mode                    |

| 131          | TCNV   | Conversion Time<br>(not including acquisition time) <sup>(2)</sup> | 14  | 15                  | Tad   |                                            |

| 132          | TACQ   | Acquisition Time <sup>(3)</sup>                                    | 1.4 |                     | μS    | -40°C to +125°C                            |

| 135          | Tswc   | Switching Time from Convert $\rightarrow$ Sample                   | _   | (Note 4)            |       |                                            |

| TBD          | TDIS   | Discharge Time                                                     | 0.2 | —                   | μS    | -40°C to +125°C                            |

Note 1: The time of the A/D clock period is dependent on the device frequency and the TAD clock divider.

2: ADRES registers may be read on the following TCY cycle.

**3:** The time for the holding capacitor to acquire the "New" input voltage when the voltage changes full scale after the conversion (VDD to Vss or Vss to VDD). The source impedance (*Rs*) on the input channels is 50Ω.

4: On the following cycle of the device clock.

### TABLE B-2: NOTABLE DIFFERENCES BETWEEN 64-PIN DEVICES – PIC18F66K80 AND PIC18F8680 FAMILIES

| Characteristic                 | PIC18F66K80 Family                                                   | PIC18F8680 Family                                             |

|--------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------|

| Max Operating Frequency        | 64 MHz                                                               | 40 MHz                                                        |

| Max Program Memory             | 64K                                                                  | 64K                                                           |

| Data Memory (bytes)            | 3,648                                                                | 3,328                                                         |

| СТМИ                           | Yes                                                                  | No                                                            |

| SOSC Oscillator Options        | Low-power oscillator option for SOSC                                 | No options                                                    |

| T1CKI Clock                    | T1CKI can be used as a clock without<br>enabling the SOSC oscillator | No                                                            |

| INTOSC                         | Up to 16 MHz                                                         | No Internal Oscillator                                        |

| SPI/I <sup>2</sup> C™          | 1 Module                                                             | 1 Module                                                      |

| Timers                         | Two 8-bit, Three 16-bit                                              | Two 8-bit, Three 16-bit                                       |

| ECCP                           | 1                                                                    | 1                                                             |

| ССР                            | 4                                                                    | 1                                                             |

| Data EEPROM (bytes)            | 1,024                                                                | 1,024                                                         |

| WDT Prescale Options           | 22                                                                   | 16                                                            |

| 5V Operation                   | 18FXXK80 parts – 5V operation<br>18LFXXK80 parts – 3.3V operation    | Yes                                                           |

| nanoWatt XLP                   | Yes                                                                  | No                                                            |

| On-Chip 3.3V Regulator         | 18FXXK80 parts – Yes<br>18LFXXK80 parts – No                         | No                                                            |

| Low-Power BOR                  | Yes                                                                  | No                                                            |

| A/D Converter                  | 12-bit signed differential                                           | 10-bit                                                        |

| A/D Channels                   | 15 Channels                                                          | 12 Channels                                                   |

| Internal Temp Sensor           | Yes                                                                  | No                                                            |

| EUSART                         | Two                                                                  | One                                                           |

| Comparators                    | Two                                                                  | Two                                                           |

| Oscillator Options             | 14                                                                   | Seven                                                         |

| Ultra Low-Power Wake-up (ULPW) | Yes                                                                  | No                                                            |

| Adjustable Slew Rate for I/O   | Yes                                                                  | No                                                            |

| PLL                            | Available for all oscillator options                                 | Available for only high-speed crystal and external oscillator |

| Data Signal Modulator          | Yes                                                                  | No                                                            |

| Error States452                                         |

|---------------------------------------------------------|

| Form                                                    |

| Stuff Bit                                               |

| Error Modes State (diagram)453                          |

| Error Recognition Mode439                               |

| Filter-Mask Truth (table)444                            |

| Functional Modes439                                     |

| Mode 0 (Legacy Mode)439                                 |

| Mode 1 (Enhanced Legacy Mode)439                        |

| Mode 2 (Enhanced FIFO Mode)                             |