Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | ECANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 64KB (32K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 3.6K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 8x12b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 28-QFN-S (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26k80t-i-mm |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

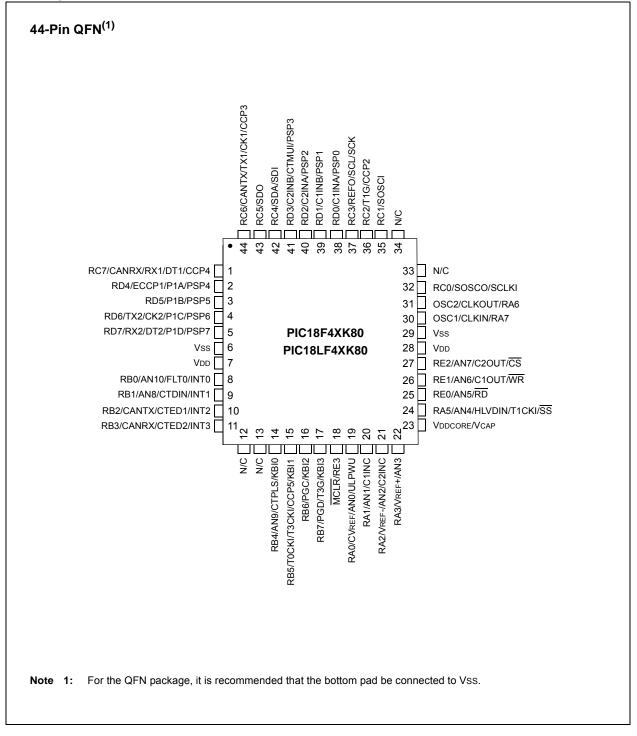

### **Pin Diagrams (Continued)**

### 4.4.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator block using the INTOSC multiplexer. This mode provides controllable power conservation during Idle periods.

From RC\_RUN, this mode is entered by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, first set IDLEN, then set the SCS1 bit and execute SLEEP. To maintain software compatibility with future devices, it is recommended that SCS0 also be cleared, though its value is ignored. The INTOSC multiplexer may be used to select a higher clock frequency by modifying the IRCFx bits before executing the SLEEP instruction. When the clock source is switched to the INTOSC multiplexer, the primary oscillator is shut down and the OSTS bit is cleared.

If the IRCFx bits are set to any non-zero value, or the INTSRC/MFIOSEL bit is set, the INTOSC output is enabled. The HFIOFS/MFIOFS bits become set, after the INTOSC output becomes stable, after an interval of TIOBST (Parameter 38, Table 31-11). For information on the HFIOFS/MFIOFS bits, see Table 4-3.

Clocks to the peripherals continue while the INTOSC source stabilizes. The HFIOFS/MFIOFS bits will remain set if the IRCFx bits were previously at a non-zero value or if INTSRC was set before the SLEEP instruction was executed and the INTOSC source was already stable. If the IRCFx bits and INTSRC are all clear, the INTOSC output will not be enabled, the HFIOFS/MFIOFS bits will remain clear and there will be no indication of the current clock source.

When a wake event occurs, the peripherals continue to be clocked from the INTOSC multiplexer. After a delay of TCSD (Parameter 38, Table 31-11) following the wake event, the CPU begins executing code clocked by the INTOSC multiplexer. The IDLEN and SCSx bits are not affected by the wake-up. The INTOSC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

### 4.5 Selective Peripheral Module Control

Idle mode allows users to substantially reduce power consumption by stopping the CPU clock. Even so, peripheral modules still remain clocked, and thus, consume power. There may be cases where the application needs what this mode does not provide: the allocation of power resources to the CPU processing with minimal power consumption from the peripherals.

PIC18F66K80 family devices address this requirement by allowing peripheral modules to be selectively disabled, reducing or eliminating their power consumption. This can be done with two control bits:

- Peripheral Enable bit, generically named XXXEN Located in the respective module's main control register

- Peripheral Module Disable (PMD) bit, generically named, XXXMD – Located in one of the PMDx Control registers (PMD0, PMD1 or PMD2)

Disabling a module by clearing its XXXEN bit disables the module's functionality, but leaves its registers available to be read and written to. This reduces power consumption, but not by as much as the second approach.

Most peripheral modules have an enable bit.

In contrast, setting the PMD bit for a module disables all clock sources to that module, reducing its power consumption to an absolute minimum. In this state, the control and status registers associated with the peripheral are also disabled, so writes to those registers have no effect and read values are invalid. Many peripheral modules have a corresponding PMD bit.

There are three PMD registers in PIC18F66K80 family devices: PMD0, PMD1 and PMD2. These registers have bits associated with each module for disabling or enabling a particular peripheral.

# TABLE 4-4:EXIT DELAY ON WAKE-UP BY RESET FROM SLEEP MODE OR ANY IDLE MODE<br/>(BY CLOCK SOURCES)

| Power-Managed<br>Mode | Clock Source <sup>(5)</sup> | Exit Delay                 | Clock Ready<br>Status Bits |

|-----------------------|-----------------------------|----------------------------|----------------------------|

|                       | LP, XT, HS                  |                            |                            |

|                       | HSPLL                       |                            | OSTS                       |

|                       | EC, RC                      | TCSD <sup>(1)</sup>        |                            |

| PRI_IDLE mode         | HF-INTOSC <sup>(2)</sup>    | ICSD**                     | HFIOFS                     |

|                       | MF-INTOSC <sup>(2)</sup>    |                            | MFIOFS                     |

|                       | LF-INTOSC                   |                            | None                       |

| SEC_IDLE mode         | SOSC                        | TCSD <sup>(1)</sup>        | SOSCRUN                    |

|                       | HF-INTOSC <sup>(2)</sup>    |                            | HFIOFS                     |

| RC_IDLE mode          | MF-INTOSC <sup>(2)</sup>    | Tcsd <sup>(1)</sup>        | MFIOFS                     |

|                       | LF-INTOSC                   |                            | None                       |

|                       | LP, XT, HS                  | Tost <sup>(3)</sup>        |                            |

|                       | HSPLL                       | Tost + t <sub>rc</sub> (3) | OSTS                       |

| Sloop mode            | EC, RC                      | TCSD <sup>(1)</sup>        |                            |

| Sleep mode            | HF-INTOSC <sup>(2)</sup>    |                            | HFIOFS                     |

|                       | MF-INTOSC <sup>(2)</sup>    | TIOBST <sup>(4)</sup>      | MFIOFS                     |

|                       | LF-INTOSC                   |                            | None                       |

**Note 1:** TCSD (Parameter 38, Table 31-11) is a required delay when waking from Sleep and all Idle modes, and runs concurrently with any other required delays (see **Section 4.4 "Idle Modes"**).

2: Includes postscaler derived frequencies. On Reset, INTOSC defaults to HF-INTOSC at 8 MHz.

**3:** TOST is the Oscillator Start-up Timer (Parameter 32, Table 31-11). TRC is the PLL Lock-out Timer (Parameter F12, Table 31-7); it is also designated as TPLL.

4: Execution continues during TIOBST (Parameter 39, Table 31-11), the INTOSC stabilization period.

**5:** The clock source is dependent upon the settings of the SCSx (OSCCON<1:0>), IRCFx (OSCCON<6:4>) and FOSCx (CONFIG1H<3:0>) bits.

| Register    | A           | Applicable Devices |             | Power-on<br>Reset,<br>Brown-out<br>Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via<br>WDT<br>or Interrupt |

|-------------|-------------|--------------------|-------------|------------------------------------------|------------------------------------------------------------------|------------------------------------|

| TXB1SIDH    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| TXB1CON     | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | 0000 0-00                                | 0000 0-00                                                        | uuuu u-uu                          |

| CANCON_RO3  | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | 1000 0000                                | 1000 0000                                                        | uuuu uuuu                          |

| CANSTAT_RO3 | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | 1000 0000                                | 1000 0000                                                        | uuuu uuuu                          |

| TXB2D7      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| TXB2D6      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| TXB2D5      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| TXB2D4      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| TXB2D3      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| TXB2D2      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| TXB2D1      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| TXB2D0      | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| TXB2DLC     | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| TXB2EIDL    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| TXB2EIDH    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| TXB2SIDL    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxx- x-xx                                | uuu- u-uu                                                        | uuu- u-uu                          |

| TXB2SIDH    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| TXB2CON     | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | 0000 0-00                                | 0000 0-00                                                        | uuuu u-uu                          |

| RXM1EIDL    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXM1EIDH    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXM1SIDL    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxx- 0-xx                                | uuu- u-uu                                                        | uuu- u-uu                          |

| RXM1SIDH    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXM0EIDL    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXM0EIDH    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXM0SIDL    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxx- 0-xx                                | uuu- u-uu                                                        | uuu- u-uu                          |

| RXM0SIDH    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF5EIDL    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF5EIDH    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF5SIDL    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxx- x-xx                                | uuu- u-uu                                                        | uuu- u-uu                          |

| RXF5SIDH    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF4EIDL    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF4EIDH    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF4SIDL    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxx- x-xx                                | uuu- u-uu                                                        | uuu- u-uu                          |

| RXF4SIDH    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF3EIDL    | PIC18F2XK80 | PIC18F4XK80        | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

### TABLE 5-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged; x = unknown; - = unimplemented bit, read as '0'; q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 5-3 for Reset value for specific conditions.

5: Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read as '0'.

### TABLE 6-2: PIC18F66K80 FAMILY REGISTER FILE SUMMARY (CONTINUED)

| Addr. | File Name   | Bit 7                                                               | Bit 6           | Bit 5    | Bit 4         | Bit 3           | Bit 2         | Bit 1                  | Bit 0                   | Value on<br>POR, BOR<br>on page |

|-------|-------------|---------------------------------------------------------------------|-----------------|----------|---------------|-----------------|---------------|------------------------|-------------------------|---------------------------------|

| EA3h  | B2EIDH      | EID15                                                               | EID14           | EID13    | EID12         | EID11           | EID10         | EID9                   | EID8                    | 97                              |

| EA2h  | B2SIDL      | SID2                                                                | SID1            | SID0     | SRR           | EXID            | _             | EID17                  | EID16                   | 97                              |

| EA1h  | B2SIDH      | SID10                                                               | SID9            | SID8     | SID7          | SID6            | SID5          | SID4                   | SID3                    | 97                              |

| EA0h  | B2CON       | TXBIF                                                               | TXABT           | TXLARB   | TXERR         | TXREQ           | _             | TXPRI1                 | TXPRI0                  | 97                              |

| E9Fh  | CANCON RO8  | CANCON R                                                            | 08              | 1        |               |                 |               |                        |                         | 97                              |

| E9Eh  | CANSTAT_RO8 | <br>CANSTAT_R                                                       | 08              |          |               |                 |               |                        |                         | 97                              |

| E9Dh  | B1D7        | B1D77                                                               | B1D76           | B1D75    | B1D71         | B1D73           | B1D72         | B1D71                  | B1D70                   | 97                              |

| E9Ch  | B1D6        | B1D67                                                               | B1D66           | B1D65    | B1D61         | B1D63           | B1D62         | B1D61                  | B1D60                   | 97                              |

| E9Bh  | B1D5        | B1D57                                                               | B1D56           | B1D55    | B1D51         | B1D53           | B1D52         | B1D51                  | B1D50                   | 97                              |

| E9Ah  | B1D4        | B1D47                                                               | B1D46           | B1D45    | B1D41         | B1D43           | B1D42         | B1D41                  | B1D40                   | 97                              |

| E99h  | B1D3        | B1D37                                                               | B1D36           | B1D35    | B1D31         | B1D33           | B1D32         | B1D31                  | B1D30                   | 97                              |

| E98h  | B1D2        | B1D27                                                               | B1D26           | B1D25    | B1D21         | B1D23           | B1D22         | B1D21                  | B1D20                   | 97                              |

| E97h  | B1D1        | B1D17                                                               | B1D16           | B1D15    | B1D11         | B1D13           | B1D12         | B1D11                  | B1D10                   | 97                              |

| E96h  | B1D0        | B1D07                                                               | B1D06           | B1D05    | B1D01         | B1D03           | B1D02         | B1D01                  | B1D00                   | 97                              |

| E95h  | B1DLC       | _                                                                   | TXRTR           |          | _             | DLC3            | DLC2          | DLC1                   | DLC0                    | 97                              |

| E94h  | B1EIDL      | EID7                                                                | EID6            | EID5     | EID4          | EID3            | EID2          | EID1                   | EID0                    | 97                              |

| E93h  | B1EIDH      | EID15                                                               | EID14           | EID3     | EID4<br>EID12 | EID3            | EID2<br>EID10 | EID1<br>EID9           | EID8                    | 97                              |

| E92h  | BISIDL      | SID2                                                                | SID14           | SID0     | SRR           | EXID            | LIDIO         | EID9<br>EID17          | EID16                   | 97                              |

|       |             |                                                                     |                 |          | SID7          |                 |               |                        |                         | 97                              |

| E91h  | B1SIDH      | SID10                                                               | SID9            | SID8     |               | SID6            | SID5          | SID4<br>TXPRI1         | SID3                    | -                               |

| E90h  | B1CON       | TXBIF                                                               | TXABT           | TXLARB   | TXERR         | TXREQ           | RTREN         |                        | TXPRI0                  | 97                              |

| E90h  | B1CON       | RXFUL                                                               | RXM1            | RXRTRRO  | FILHIT4       | FILHIT3         | FILHIT2       | FILHIT1                | FILHIT0                 | 97                              |

| E8Fh  | CANCON_RO9  | CANCON_R                                                            |                 |          |               |                 |               |                        |                         | 97                              |

| E8Eh  | CANSTAT_RO9 | CANSTAT_R                                                           | I               | 00075    | 20220         | 00070           | 20270         | <b>D</b> 0 <b>DT</b> ( | <b>D</b> 0 <b>D T</b> 0 | 97                              |

| E8Dh  | B0D7        | B0D77                                                               | B0D76           | B0D75    | B0D70         | B0D73           | B0D72         | B0D71                  | B0D70                   | 97                              |

| E8Ch  | B0D6        | B0D67                                                               | B0D66           | B0D65    | B0D60         | B0D63           | B0D62         | B0D61                  | B0D60                   | 97                              |

| E8Bh  | B0D5        | B0D57                                                               | B0D56           | B0D55    | B0D50         | B0D53           | B0D52         | B0D51                  | B0D50                   | 97                              |

| E8Ah  | B0D4        | B0D47                                                               | B0D46           | B0D45    | B0D40         | B0D43           | B0D42         | B0D41                  | B0D40                   | 97                              |

| E89h  | B0D3        | B0D37                                                               | B0D36           | B0D35    | B0D30         | B0D33           | B0D32         | B0D31                  | B0D30                   | 97                              |

| E88h  | B0D2        | B0D27                                                               | B0D26           | B0D25    | B0D20         | B0D23           | B0D22         | B0D21                  | B0D20                   | 98                              |

| E87h  | B0D1        | B0D17                                                               | B0D16           | B0D15    | B0D10         | B0D13           | B0D12         | B0D11                  | B0D10                   | 98                              |

| E86h  | B0D0        | B0D07                                                               | B0D06           | B0D05    | B0D00         | B0D03           | B0D02         | B0D01                  | B0D00                   | 98                              |

| E85h  | BODLC       | _                                                                   | RXRTR           | RB1      | RB0           | DLC3            | DLC2          | DLC1                   | DLC0                    | 98                              |

| E84h  | B0EIDL      | EID7                                                                | EID6            | EID5     | EID4          | EID3            | EID2          | EID1                   | EID0                    | 98                              |

| E83h  | B0EIDH      | EID15                                                               | EID14           | EID13    | EID12         | EID11           | EID10         | EID9                   | EID8                    | 98                              |

| E82h  | B0SIDL      | SID2                                                                | SID1            | SID0     | SRR           | EXID            | _             | EID17                  | EID16                   | 98                              |

| E81h  | B0SIDH      | SID10                                                               | SID9            | SID8     | SID7          | SID6            | SID5          | SID4                   | SID3                    | 98                              |

| E80h  | B0CON       | TXBIF                                                               | TXABT           | TXLARB   | TXERR         | TXREQ           | RTREN         | TXPRI1                 | TXPRI0                  | 98                              |

| E80h  | B0CON       | RTXFUL                                                              | RXM1            | RXRTRRO  | FILHIT4       | FILHIT3         | FILHIT2       | FILHIT1                | FILHIT0                 | 98                              |

| E7Fh  | TXBIE       | —                                                                   | —               | —        | CAN TX Buff   | er Interrupt En | nable         | —                      | —                       | 98                              |

| E7Eh  | BIE0        | CAN Buffer In                                                       | nterrupt Enabl  | e        |               |                 |               |                        |                         | 98                              |

| E7Dh  | BSEL0       | Mode Select                                                         | Register 0      |          |               |                 |               | _                      | _                       | 98                              |

| E7Ch  | MSEL3       | CAN Mask S                                                          | elect Register  | 3        |               |                 |               |                        |                         | 98                              |

| E7Bh  | MSEL2       | CAN Mask S                                                          | elect Register  | 2        |               |                 |               |                        |                         | 98                              |

| E7Ah  | MSEL1       | CAN Mask S                                                          | elect Register  | 1        |               |                 |               |                        |                         | 98                              |

| E79h  | MSEL0       | CAN Mask S                                                          | elect Register  | 0        |               |                 |               |                        |                         | 98                              |

| E78h  | RXFBCON7    | CAN Buffer 1                                                        | 5/14 Pointer F  | Register |               |                 |               |                        |                         | 98                              |

| E77h  | RXFBCON6    | CAN Buffer 15/14 Pointer Register CAN Buffer 13/12 Pointer Register |                 |          |               |                 |               |                        | 98                      |                                 |

| E76h  | RXFBCON5    | CAN Buller 13/12 Pointer Register                                   |                 |          |               |                 |               |                        | 98                      |                                 |

| E75h  | RXFBCON4    |                                                                     | /8 Pointer Reg  | -        |               |                 |               |                        |                         | 98                              |

|       | RXFBCON3    |                                                                     | 7/6 Pointer Reg | -        |               |                 |               |                        |                         | 98                              |

| E74h  |             |                                                                     |                 | , ·      |               |                 |               |                        |                         |                                 |

#### 6.4.3.2 FSR Registers and POSTINC, POSTDEC, PREINC and PLUSW

In addition to the INDF operand, each FSR register pair also has four additional indirect operands. Like INDF, these are "virtual" registers that cannot be indirectly read or written to. Accessing these registers actually accesses the associated FSR register pair, but also performs a specific action on its stored value.

These operands are:

- POSTDEC Accesses the FSR value, then automatically decrements it by '1' afterwards

- POSTINC Accesses the FSR value, then automatically increments it by '1' afterwards

- PREINC Increments the FSR value by '1', then uses it in the operation

- PLUSW Adds the signed value of the W register (range of -127 to 128) to that of the FSR and uses the new value in the operation

In this context, accessing an INDF register uses the value in the FSR registers without changing them. Similarly, accessing a PLUSW register gives the FSR value, offset by the value in the W register, with neither value actually changed in the operation. Accessing the other virtual registers changes the value of the FSR registers.

Operations on the FSRs with POSTDEC, POSTINC and PREINC affect the entire register pair. Rollovers of the FSRnL register, from FFh to 00h, carry over to the FSRnH register. On the other hand, results of these operations do not change the value of any flags in the STATUS register (for example, Z, N and OV bits).

The PLUSW register can be used to implement a form of Indexed Addressing in the data memory space. By manipulating the value in the W register, users can reach addresses that are fixed offsets from pointer addresses. In some applications, this can be used to implement some powerful program control structure, such as software stacks, inside of data memory.

### 6.4.3.3 Operations by FSRs on FSRs

Indirect Addressing operations that target other FSRs or virtual registers represent special cases. For example, using an FSR to point to one of the virtual registers will not result in successful operations.

As a specific case, assume that the FSR0H:FSR0L registers contain FE7h, the address of INDF1. Attempts to read the value of the INDF1, using INDF0 as an operand, will return 00h. Attempts to write to INDF1, using INDF0 as the operand, will result in a NOP.

On the other hand, using the virtual registers to write to an FSR pair may not occur as planned. In these cases, the value will be written to the FSR pair, but without any incrementing or decrementing. Thus, writing to INDF2 or POSTDEC2 will write the same value to the FSR2H:FSR2L.

Since the FSRs are physical registers mapped in the SFR space, they can be manipulated through all direct operations. Users should proceed cautiously when working on these registers, however, particularly if their code uses Indirect Addressing.

Similarly, operations by Indirect Addressing are generally permitted on all other SFRs. Users should exercise the appropriate caution, so that they do not inadvertently change settings that might affect the operation of the device.

### 6.5 Program Memory and the Extended Instruction Set

The operation of program memory is unaffected by the use of the extended instruction set.

Enabling the extended instruction set adds five additional two-word commands to the existing PIC18 instruction set: ADDFSR, CALLW, MOVSF, MOVSS and SUBFSR. These instructions are executed as described in Section 6.2.4 "Two-Word Instructions".

### 7.4 Erasing Flash Program Memory

The erase blocks are 32 words or 64 bytes.

Word erase in the Flash array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 64 bytes of program memory is erased. The Most Significant 16 bits of the TBLPTR<21:6> point to the block being erased. The TBLPTR<5:0> bits are ignored.

The EECON1 register commands the erase operation. The EEPGD bit must be set to point to the Flash program memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

For protection, the write initiate sequence for EECON2 must be used.

A long write is necessary for erasing the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

#### 7.4.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- 1. Load the Table Pointer register with the address of row to be erased.

- 2. Set the EECON1 register for the erase operation:

- · Set the EEPGD bit to point to program memory

- Clear the CFGS bit to access program memory

- · Set the WREN bit to enable writes

- · Set the FREE bit to enable the erase

- 3. Disable the interrupts.

- 4. Write 55h to EECON2.

- 5. Write 0AAh to EECON2.

- Set the WR bit. This begins the row erase cycle. The CPU will stall for the duration of the erase for TIW. (See Parameter D133A.)

- 7. Re-enable interrupts.

|           | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL | ; load TBLPTR with the base<br>; address of the memory block |

|-----------|----------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------|

| ERASE_ROW |                                                    |                                                                                     |                                                              |

|           | BSF                                                | EECON1, EEPGD                                                                       | ; point to Flash program memory                              |

|           | BCF                                                | EECON1, CFGS                                                                        | ; access Flash program memory                                |

|           | BSF                                                | EECON1, WREN                                                                        | ; enable write to memory                                     |

|           | BSF                                                | EECON1, FREE                                                                        | ; enable Row Erase operation                                 |

|           | BCF                                                | INTCON, GIE                                                                         | ; disable interrupts                                         |

| Required  | MOVLW                                              | 55h                                                                                 |                                                              |

| Sequence  | MOVWF                                              | EECON2                                                                              | ; write 55h                                                  |

|           | MOVLW                                              | 0AAh                                                                                |                                                              |

|           | MOVWF                                              | EECON2                                                                              | ; write OAAh                                                 |

|           | BSF                                                | EECON1, WR                                                                          | ; start erase (CPU stall)                                    |

|           | BSF                                                | INTCON, GIE                                                                         | ; re-enable interrupts                                       |

#### EXAMPLE 7-2: ERASING A FLASH PROGRAM MEMORY ROW

| R/W-0         | R/W-0                               | R/W-0                                | R/W-0             | R/W-0            | R/W-0            | R/W-0           | R/W-0              |

|---------------|-------------------------------------|--------------------------------------|-------------------|------------------|------------------|-----------------|--------------------|

| IRXIF         | WAKIF                               | ERRIF                                | TXB2IF            | TXB1IF           | TXB0IF           | RXB1IF          | RXB0IF/<br>FIFOFIF |

| bit 7         | •                                   |                                      |                   |                  |                  |                 | bit                |

|               |                                     |                                      |                   |                  |                  |                 |                    |

| Legend:       | 1.1                                 |                                      | 1.11              |                  |                  | 1               |                    |

| R = Readable  |                                     | W = Writable                         |                   | -                | nented bit, read |                 |                    |

| -n = Value at | PUR                                 | '1' = Bit is set                     | [                 | '0' = Bit is cle | ared             | x = Bit is unk  | nown               |

| bit 7         | IRXIF: Invalid                      | d Message Rec                        | eived Interrup    | t Flag bits      |                  |                 |                    |

|               |                                     | d message occ                        | •                 | •                |                  |                 |                    |

|               |                                     | id message occ                       |                   |                  |                  |                 |                    |

| bit 6         | WAKIF: Bus                          | Wake-up Activi                       | ity Interrupt Fla | ag bit           |                  |                 |                    |

|               |                                     | on the CAN bus<br>ity on the CAN     |                   |                  |                  |                 |                    |

| bit 5         | ERRIF: Erro                         | r Interrupt Flag                     | bit (Multiple s   | ources in CON    | ISTAT register)  |                 |                    |

|               |                                     | has occurred in                      |                   | • •              | ources)          |                 |                    |

|               |                                     | module errors                        |                   |                  |                  |                 |                    |

| bit 4         |                                     | nsmit Buffer 2 l                     |                   |                  |                  |                 |                    |

|               |                                     | t Buffer 2 has c<br>t Buffer 2 has n |                   |                  | •                | lay be reloaded |                    |

| bit 3         |                                     | nsmit Buffer 1 li                    | •                 |                  | a message        |                 |                    |

|               |                                     | t Buffer 1 has c                     |                   |                  | nessage and m    | ay be reloaded  | l                  |

|               | 0 = Transmi                         | t Buffer 1 has n                     | ot completed      | transmission of  | a message        |                 |                    |

| bit 2         |                                     | nsmit Buffer 0 I                     |                   |                  |                  |                 |                    |

|               |                                     | t Buffer 0 has c<br>t Buffer 0 has n |                   |                  |                  | ay be reloaded  | l                  |

| bit 1         | RXB1IF: Red                         | ceive Buffer 1 Ir                    | nterrupt Flag b   | bit              |                  |                 |                    |

|               | $\frac{\text{Mode 0:}}{1 - CAN De}$ | aaiva Duffar 1 k                     |                   |                  |                  |                 |                    |

|               |                                     | ceive Buffer 1 h<br>ceive Buffer 1 h |                   | 0                |                  |                 |                    |

|               | Modes 1 and                         |                                      |                   |                  |                  |                 |                    |

|               |                                     | Receive Buffer/I                     |                   |                  | •                |                 |                    |

|               |                                     | Receive Buffer/I                     |                   |                  | message          |                 |                    |

| bit 0         | =                                   | is dependent o                       | on the selected   | I mode:          |                  |                 |                    |

|               | Mode 0:<br><b>PYBOIE:</b> Rec       | ceive Buffer 0 Ir                    | nterrunt Elaa h   | .i+              |                  |                 |                    |

|               |                                     | ceive Buffer 0 h                     |                   |                  |                  |                 |                    |

|               |                                     | ceive Buffer 0 h                     |                   | •                |                  |                 |                    |

|               | <u>Mode 1:</u><br>Unimplemer        | nted: Read as '                      | 0'                |                  |                  |                 |                    |

|               | Mode 2:                             |                                      |                   |                  |                  |                 |                    |

|               | FIFOFIF: FIF                        | O Full Interrup                      | t Flag bit        |                  |                  |                 |                    |

|               |                                     | s reached full s                     |                   |                  | UE bit           |                 |                    |

# REGISTER 10-8: PIR5: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 5

### 10.4 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are six Peripheral Interrupt Priority registers (IPR1 through IPR6). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit (RCON<7>) be set.

#### REGISTER 10-14: IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1

| R/W-1                  | R/W-1                          | R/W-1            | R/W-1            | R/W-1              | R/W-1            | R/W-1           | R/W-1  |

|------------------------|--------------------------------|------------------|------------------|--------------------|------------------|-----------------|--------|

| PSPIP                  | ADIP                           | RC1IP            | TX1IP            | SSPIP              | TMR1GIP          | TMR2IP          | TMR1IP |

| bit 7                  |                                |                  |                  |                    |                  |                 | bit 0  |

|                        |                                |                  |                  |                    |                  |                 |        |

| Legend:<br>R = Readabl | lo bit                         | W = Writable     | hit              | II – Unimplon      | nented bit, read | 1 00 '0'        |        |

| -n = Value at          |                                | '1' = Bit is set |                  | '0' = Bit is clea  |                  | x = Bit is unkr |        |

|                        | IFOR                           | I - DILIS SEL    |                  |                    | areu             |                 | 101011 |

| bit 7                  | PSPIP: Parall                  | el Slave Port F  | Read/Write Inte  | errupt Priority bi | t                |                 |        |

|                        | 1 = High prio<br>0 = Low prior |                  |                  |                    |                  |                 |        |

| bit 6                  |                                | onverter Interru | pt Priority bit  |                    |                  |                 |        |

|                        | 1 = High prio<br>0 = Low prior | •                |                  |                    |                  |                 |        |

| bit 5                  | •                              | RTx Receive I    | nterrunt Priorit | v hit              |                  |                 |        |

| bit o                  | 1 = High prio                  |                  |                  | y on               |                  |                 |        |

|                        | 0 = Low prior                  |                  |                  |                    |                  |                 |        |

| bit 4                  | TX1IP: EUSA                    | RTx Transmit     | nterrupt Priorit | ty bit             |                  |                 |        |

|                        | 1 = High prio<br>0 = Low prior | •                |                  |                    |                  |                 |        |

| bit 3                  | •                              | •                | Serial Port In   | terrupt Priority   | hit              |                 |        |

| Sit C                  | 1 = High prio                  | •                |                  | ton up trinonty i  |                  |                 |        |

|                        | 0 = Low prior                  | ity              |                  |                    |                  |                 |        |

| bit 2                  | TMR1GIP: Tir                   | mer1 Gate Inte   | rrupt Priority b | it                 |                  |                 |        |

|                        | 1 = High prio<br>0 = Low prior | ,                |                  |                    |                  |                 |        |

| bit 1                  | •                              | R2 to PR2 Mate   | h Interrunt Pri  | ority hit          |                  |                 |        |

|                        | 1 = High prio                  |                  | in monuper n     | only bit           |                  |                 |        |

|                        | 0 = Low prior                  | •                |                  |                    |                  |                 |        |

| bit 0                  | TMR1IP: TMF                    | R1 Overflow Inf  | errupt Priority  | bit                |                  |                 |        |

|                        | 1 = High prio                  |                  |                  |                    |                  |                 |        |

|                        | 0 = Low prior                  | цу               |                  |                    |                  |                 |        |

| Pin Name    | Function               | TRIS<br>Setting | I/O | I/O Type | Description                                                                            |

|-------------|------------------------|-----------------|-----|----------|----------------------------------------------------------------------------------------|

| RE5/CANTX   | RE5 <sup>(1)</sup>     | 0               | 0   | DIG      | LATE<5> data output.                                                                   |

|             |                        | 1               | Ι   | ST       | PORTE<5> data input.                                                                   |

|             | CANTX <sup>(1,2)</sup> | 0               | 0   | DIG      | CAN bus TX.                                                                            |

| RE6/RX2/DT2 | RE6 <sup>(1)</sup>     | 0               | 0   | DIG      | LATE<6> data output.                                                                   |

|             |                        | 1               | Ι   | ST       | PORTE<6> data input.                                                                   |

|             | RX2 <sup>(1)</sup>     | 1               | Ι   | ST       | Asynchronous serial receive data input (EUSARTx module).                               |

|             | DT2 <sup>(1)</sup>     | 1               | 0   | DIG      | Synchronous serial data output (EUSARTx module); takes priority over port data.        |

|             |                        | 1               | I   | ST       | Synchronous serial data input (EUSARTx module); user must configure as an input.       |

| RE7/TX2/CK2 | RE7 <sup>(1)</sup>     | 0               | 0   | DIG      | LATE<7> data output.                                                                   |

|             |                        | 1               | Ι   | ST       | PORTE<7> data input.                                                                   |

|             | TX2 <sup>(1)</sup>     | 0               | 0   | DIG      | Asynchronous serial data output (EUSARTx module); takes priority over port data.       |

|             | CK2 <sup>(1)</sup>     | 0               | 0   | DIG      | Synchronous serial clock output (EUSARTx module); user must configure as an input.     |

|             |                        | 1               | Ι   | ST       | Synchronous serial clock input (EUSARTx module); user must config-<br>ure as an input. |

### TABLE 11-9: PORTE FUNCTIONS (CONTINUED)

Legend: O = Output, I = Input, ANA = Analog Signal, DIG = CMOS Output, ST = Schmitt Trigger Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option)

Note 1: These bits are unavailable for 40 and 44-pin devices (PIC18F4XK0).

2: This is the alternate pin assignment for CANRX and CANTX on 64-pin devices (PIC18F6XK80) when the CANMX Configuration bit is cleared.

| Name    | Bit 7              | Bit 6              | Bit 5               | Bit 4               | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|---------|--------------------|--------------------|---------------------|---------------------|--------|--------|--------|--------|

| PORTE   | RE7 <sup>(1)</sup> | RE6 <sup>(1)</sup> | RE5 <sup>(1)</sup>  | RE4 <sup>(1)</sup>  | RE3    | RE2    | RE1    | RE0    |

| LATE    | LATE7              | LATE6              | LATE5               | LATE4               | —      | LATE2  | LATE1  | LATE0  |

| TRISE   | TRISE7             | TRISE6             | TRISE5              | TRISE4              | —      | TRISE2 | TRISE1 | TRISE0 |

| PADCFG1 | RDPU               | REPU               | RFPU <sup>(1)</sup> | RGPU <sup>(1)</sup> | _      |        | _      | CTMUDS |

| ANCON0  | ANSEL7             | ANSEL6             | ANSEL5              | ANSEL4              | ANSEL3 | ANSEL2 | ANSEL1 | ANSEL0 |

Legend: Shaded cells are not used by PORTE.

Note 1: These bits are unimplemented on 44-pin devices, read as '0'.

#### **REGISTER 11-5: PSPCON: PARALLEL SLAVE PORT CONTROL REGISTER**

| R-0   | R-0 | R/W-0 | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-------|---------|-----|-----|-----|-------|

| IBF   | OBF | IBOV  | PSPMODE | _   | —   | —   |       |

| bit 7 |     |       |         |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | <b>IBF:</b> Input Buffer Full Status bit<br>1 = A word has been received and is waiting to be read by the CPU<br>0 = No word has been received          |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | <b>OBF:</b> Output Buffer Full Status bit                                                                                                               |

|         | <ul> <li>1 = The output buffer still holds a previously written word</li> <li>0 = The output buffer has been read</li> </ul>                            |

| bit 5   | IBOV: Input Buffer Overflow Detect bit                                                                                                                  |

|         | <ul> <li>1 = A write occurred when a previously input word had not been read (must be cleared in software)</li> <li>0 = No overflow occurred</li> </ul> |

| bit 4   | PSPMODE: Parallel Slave Port Mode Select bit                                                                                                            |

|         | 1 = Parallel Slave Port mode<br>0 = General Purpose I/O mode                                                                                            |

| bit 3-0 | Unimplemented: Read as '0'                                                                                                                              |

#### FIGURE 11-4: PARALLEL SLAVE PORT WRITE WAVEFORMS

|              | Q1   Q2   Q3   Q4 Q1   Q2   Q3   Q4 Q1   Q2   Q3   Q4 |

|--------------|-------------------------------------------------------|

| CS           |                                                       |

| WR           |                                                       |

| RD -         |                                                       |

| PORTD<7:0> — |                                                       |

| IBF          |                                                       |

| OBF —        |                                                       |

| PSPIF        |                                                       |

For more details on selecting the optimum C1 and C2 for a given crystal, see the crystal manufacture's applications information. The optimum value depends in part on the amount of parasitic capacitance in the circuit, which is often unknown. For that reason, it is highly recommended that thorough testing and validation of the oscillator be performed after values have been selected.

#### 14.5.1 USING SOSC AS A CLOCK SOURCE

The SOSC oscillator is also available as a clock source in power-managed modes. By setting the clock select bits, SCS<1:0> (OSCCON<1:0>), to '01', the device switches to SEC\_RUN mode and both the CPU and peripherals are clocked from the SOSC oscillator. If the IDLEN bit (OSCCON<7>) is cleared and a SLEEP instruction is executed, the device enters SEC\_IDLE mode. Additional details are available in **Section 4.0 "Power-Managed Modes"**.

Whenever the SOSC oscillator is providing the clock source, the SOSC System Clock Status flag, SOSCRUN (OSCCON2<6>), is set. This can be used to determine the controller's current clocking mode. It can also indicate the clock source currently being used by the Fail-Safe Clock Monitor.

If the Clock Monitor is enabled and the SOSC oscillator fails while providing the clock, polling the SOCSRUN bit will indicate whether the clock is being provided by the SOSC oscillator or another source.

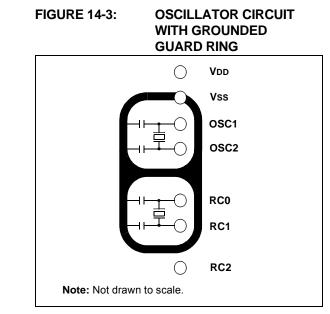

# 14.5.2 SOSC OSCILLATOR LAYOUT CONSIDERATIONS

The SOSC oscillator circuit draws very little power during operation. Due to the low-power nature of the oscillator, it may also be sensitive to rapidly changing signals in close proximity. This is especially true when the oscillator is configured for extremely Low-Power mode, SOSCSEL<1:0> (CONFIG1L<4:3>) = 01.

The oscillator circuit, displayed in Figure 14-2, should be located as close as possible to the microcontroller. There should be no circuits passing within the oscillator circuit boundaries other than Vss or VDD.

If a high-speed circuit must be located near the oscillator, it may help to have a grounded guard ring around the oscillator circuit. The guard, as displayed in Figure 14-3, could be used on a single-sided PCB or in addition to a ground plane. (Examples of a high-speed circuit include the ECCP1 pin, in Output Compare or PWM mode, or the primary oscillator, using the OSC2 pin.)

In the Low Drive Level mode, SOSCSEL<1:0> = 01, it is critical that RC2 I/O pin signals be kept away from the oscillator circuit. Configuring RC2 as a digital output, and toggling it, can potentially disturb the oscillator circuit, even with a relatively good PCB layout. If possible, either leave RC2 unused or use it as an input pin with a slew rate limited signal source. If RC2 must be used as a digital output, it may be necessary to use the Higher Drive Level Oscillator mode (SOSCSEL<1:0> = 11) with many PCB layouts.

Even in the Higher Drive Level mode, careful layout procedures should still be followed when designing the oscillator circuit.

In addition to dV/dt induced noise considerations, it is important to ensure that the circuit board is clean. Even a very small amount of conductive, soldering flux residue can cause PCB leakage currents that can overwhelm the oscillator circuit.

## 14.6 Timer1 Interrupt

The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The Timer1 interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled or disabled by setting or clearing the Timer1 Interrupt Enable bit, TMR1IE (PIE1<0>).

| <b>IGURE 21-5:</b>             | SPI N             | IODE W      | AVEFO                                              | RM (SLA       | VE MO                     | DE WITH | CKE =            | 0)                                    |                   |                                              |                 |

|--------------------------------|-------------------|-------------|----------------------------------------------------|---------------|---------------------------|---------|------------------|---------------------------------------|-------------------|----------------------------------------------|-----------------|

| <br>SS<br>Opilonsi             | ( .               |             |                                                    |               |                           |         |                  |                                       |                   |                                              |                 |

| 80%<br>{CKP = 0<br>CXE = 0}    | :<br>:<br>:<br>:X |             | ,<br>                                              | ·             | ·                         |         |                  |                                       |                   | ·<br>·                                       | :<br>:<br>:<br> |

| - VAR 20)<br>- ROR             | ·<br>·            | :<br>:<br>: | (<br>(<br>() () () () () () () () () () () () () ( | ,<br>,<br>, , | ;<br>;<br>; , ,           |         | (<br>(<br>(      | ;<br>;<br>; ;                         | 2<br>2<br>3       | ,<br>,<br>,                                  |                 |

| 2508<br>(CRE = 1<br>(CRE = 5)  | 2<br>3<br>3       |             |                                                    |               |                           |         |                  | · · · · · · · · · · · · · · · · · · · |                   |                                              |                 |

| Verlie en<br>Sisteration       |                   |             | 5<br>2<br>7<br>7                                   | :<br>d        | *<br>\$******<br>\$<br>\$ |         | 5<br>2<br>7<br>7 | :<br>::<br>:<br>:                     | *<br>.5<br>1<br>1 | :<br>:                                       | ,<br>           |

| \$6 <b>x</b> 3                 |                   | Kana a      |                                                    | N 88.8        |                           | X68.3   | X 88.0           |                                       |                   |                                              |                 |

| SD:<br>(S3:82 = 33)            |                   |             |                                                    |               |                           |         |                  |                                       |                   | Mygeeneerine<br>E C                          | :<br>:<br>:     |

| ingasi<br>Serrecia             | ·<br>·<br>·       |             |                                                    | . 4.          |                           | <i></i> |                  | :<br>. <i>B</i> e                     | :<br>:<br>:       | 49.                                          |                 |

| (3367 = 6)                     |                   |             |                                                    | *<br>*        | ,<br>,<br>,               |         | 5<br>2<br>5      |                                       | * :<br>* :        | :<br>:<br>:///////////////////////////////// |                 |

| - S-SPHF<br>Britanupî<br>Filag | ;<br>;<br>;<br>;  |             | s<br>2<br>2                                        | :<br>:<br>:   | <<br>;<br>;<br>;          |         | 5<br>2<br>2<br>2 | :<br>:<br>::                          |                   | ilia<br>A stent Co                           | . Produce       |

| 355 <b>0</b> 355 65            | 2<br>1            | *<br>:      |                                                    | ;<br>,        | :                         |         | i<br>i           | ;<br>,                                |                   | ) († Next Ox<br>Fritter Ox                   |                 |

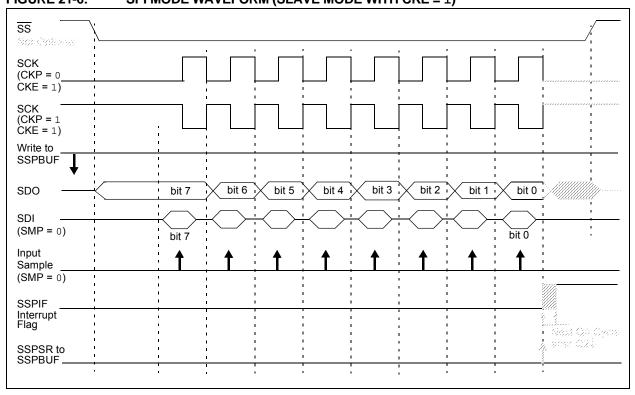

# FIGURE 21-6: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

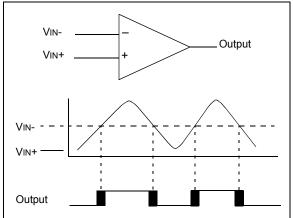

### 24.2 Comparator Operation

A single comparator is shown in Figure 24-2, along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input, VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input, VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 24-2 represent the uncertainty due to input offsets and response time.

FIGURE 24-2: SINGLE COMPARATOR

### 24.3 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response to a comparator input change. Otherwise, the maximum delay of the comparators should be used (see **Section 31.0 "Electrical Characteristics"**).

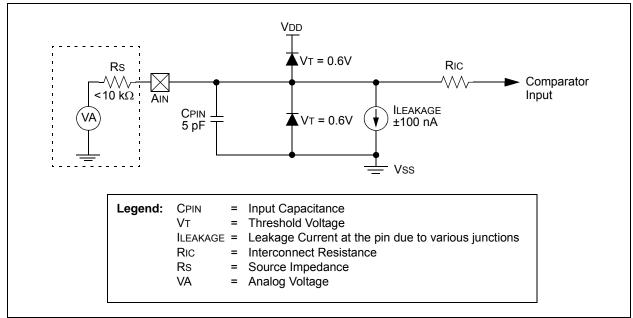

### 24.4 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 24-3. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and VSs. The analog input, therefore, must be between VSs and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up condition may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

#### FIGURE 24-3: COMPARATOR ANALOG INPUT MODEL

# 28.3.3 OPERATION OF REGULATOR IN SLEEP

The difference in the two regulators' operation arises with Sleep mode. The ultra low-power regulator gives the device the lowest current in the Regulator Enabled mode.

The on-chip regulator can go into a lower power mode when the device goes to Sleep by setting the REGSLP bit (WDTCON<7>). This puts the regulator in a standby mode so that the device consumes much less current.

The on-chip regulator can also go into the Ultra Low-Power mode, which consumes the lowest current possible with the <u>regulator</u> enabled. This mode is controlled by the <u>RETEN</u> bit (CONFIG1L<0>) and SRETEN bit (WDTCON<4>). The various modes of regulator operation are shown in Table 28-3.

When the ultra low-power regulator is in Sleep mode, the internal reference voltages in the chip will be shut off and any interrupts referring to the internal reference will not wake up the device. If the BOR or LVD is enabled, the regulator will keep the internal references on and the lowest possible current will not be achieved.

When using the ultra low-power regulator in Sleep mode, the device will take about 250  $\mu s$  to start executing code after it wakes up.

| TABLE 20-5. 51 |                                              |                     | -                   | -                    |

|----------------|----------------------------------------------|---------------------|---------------------|----------------------|

| Device         | Power Mode                                   | REGSLP<br>WDTCON<7> | SRETEN<br>WDTCON<4> | RETEN<br>CONFIG1L<0> |

| PIC18FXXK80    | Normal Operation (Sleep)                     | 0                   | х                   | 1                    |

| PIC18FXXK80    | Low-Power mode (Sleep)                       | 1                   | х                   | 1                    |

| PIC18FXXK80    | Normal Operation (Sleep)                     | 0                   | 0                   | 0                    |

| PIC18FXXK80    | Low-Power mode (Sleep)                       | 1                   | 0                   | 0                    |

| PIC18FXXK80    | Ultra Low-Power mode (Sleep)                 | x                   | 1                   | 0                    |

| PIC18LFXXK80   | Reserved <sup>(2)</sup>                      | х                   | Don't Care          | 0                    |

| PIC18LFXXK80   | Regulator Bypass mode (Sleep) <sup>(2)</sup> | x                   | х                   | 1                    |

### TABLE 28-3: SLEEP MODE REGULATOR SETTINGS<sup>(1)</sup>

**Note 1:** x — Indicates that VIT status is invalid.

2: The ultra low-power regulator should be disabled (RETEN = 1, ULP disabled) on PIC18LFXXK80 devices to obtain the lowest possible Sleep current.

| DAW                        | Decimal A                                 | djust W Regis                                         | ter                            | DECF                                       | Decrement                                                    | f                                                                             |                         |

|----------------------------|-------------------------------------------|-------------------------------------------------------|--------------------------------|--------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------|

| Syntax:                    | DAW                                       |                                                       |                                | Syntax:                                    | DECF f{,c                                                    | l {,a}}                                                                       |                         |

| Operands:                  | None                                      |                                                       |                                | Operands:                                  | $0 \leq f \leq 255$                                          |                                                                               |                         |

| Operation:                 | •                                         | > 9] or [DC = 1<br>6 → W<3:0>;                        | ], then                        |                                            | $\begin{array}{l} d \in [0,1] \\ a \in [0,1] \end{array}$    |                                                                               |                         |

|                            | else                                      |                                                       |                                | Operation:                                 | $(f) - 1 \rightarrow de$                                     | est                                                                           |                         |

|                            | (W<3:0>) –                                | → W<3:0>                                              |                                | Status Affected:                           | C, DC, N, C                                                  | DV, Z                                                                         |                         |

|                            | lf [W<7:4>                                | > 9] or [C = 1],                                      | then                           | Encoding:                                  | 0000                                                         | 01da ff                                                                       | ff ffff                 |

|                            | (W<7:4>) +<br>C = 1<br>else<br>(W<7:4>) - | 6 → W<7:4>;<br>→ W<7:4>                               |                                | Description:                               | result is sto                                                | register 'f'. If<br>red in W. If 'd<br>red back in re                         | ' is '1', the           |

| Status Affected:           | С                                         |                                                       |                                |                                            | . ,                                                          | he Access Ba                                                                  | nk is selected.         |

| Encoding:<br>Description:  | 0000                                      | 0000 000<br>s the eight-bit                           |                                |                                            | lf 'a' is '1', t<br>GPR bank.                                | he BSR is use                                                                 | ed to select the        |

| Words:                     | resulting fro<br>variables (e             | om the earlier a<br>each in packed<br>es a correct pa | addition of two<br>BCD format) |                                            | set is enabl<br>in Indexed<br>mode wher<br><b>Section 29</b> | ed, this instru<br>Literal Offset<br>lever f ≤ 95 (5<br><b>.2.3 "Byte-O</b> l | Fh). See                |

| Cycles:                    | 1                                         |                                                       |                                |                                            |                                                              | set Mode" for                                                                 |                         |

| Q Cycle Activity:          |                                           |                                                       |                                | Words:                                     | 1                                                            |                                                                               |                         |

| Q1                         | Q2                                        | Q3                                                    | Q4                             | Cycles:                                    | 1                                                            |                                                                               |                         |