Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | ECANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 35                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.6K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x12b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf45k80-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-5: | PIC18F4XK80 PINOUT I/O DESCRIPTIONS (CONTINUED) |

|------------|-------------------------------------------------|

|------------|-------------------------------------------------|

|                                                                                           | Pin N | umber        |             | Duffer         |                                               |  |

|-------------------------------------------------------------------------------------------|-------|--------------|-------------|----------------|-----------------------------------------------|--|

| Pin Name                                                                                  | PDIP  | QFN/<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                                   |  |

|                                                                                           |       |              |             |                | PORTD is a bidirectional I/O port.            |  |

| RD0/C1INA/PSP0                                                                            | 19    | 38           |             |                |                                               |  |

| RD0                                                                                       |       |              | I/O         | ST/<br>CMOS    | Digital I/O.                                  |  |

| C1INA                                                                                     |       |              | I           | Analog         | Comparator 1 Input A.                         |  |

| PSP0                                                                                      |       |              | I/O         | ST/<br>CMOS    | Parallel Slave Port data.                     |  |

| RD1/C1INB/PSP1                                                                            | 20    | 39           |             |                |                                               |  |

| RD1                                                                                       |       |              | I/O         | ST/<br>CMOS    | Digital I/O.                                  |  |

| C1INB                                                                                     |       |              | I           | Analog         | Comparator 1 Input B.                         |  |

| PSP1                                                                                      |       |              | I/O         | ST/<br>CMOS    | Parallel Slave Port data.                     |  |

| RD2/C2INA/PSP2                                                                            | 21    | 40           |             |                |                                               |  |

| RD2                                                                                       |       |              | I/O         | ST/<br>CMOS    | Digital I/O.                                  |  |

| C2INA                                                                                     |       |              | I.          | Analog         | Comparator 2 Input A.                         |  |

| PSP2                                                                                      |       |              | I/O         | ST/<br>CMOS    | Parallel Slave Port data.                     |  |

| RD3/C2INB/CTMUI/<br>PSP3                                                                  | 22    | 41           |             |                |                                               |  |

| RD3                                                                                       |       |              | I/O         | ST/<br>CMOS    | Digital I/O.                                  |  |

| C2INB                                                                                     |       |              | I           | Analog         | Comparator 2 Input B.                         |  |

| CTMUI                                                                                     |       |              |             |                | CTMU pulse generator charger for the C2INB.   |  |

| PSP3                                                                                      |       |              | I/O         | ST/<br>CMOS    | Parallel Slave Port data.                     |  |

| RD4/ECCP1/P1A/PSP4                                                                        | 27    | 2            |             |                |                                               |  |

| RD4                                                                                       |       |              | I/O         | ST/<br>CMOS    | Digital I/O.                                  |  |

| ECCP1                                                                                     |       |              | I/O         | ST             | Capture 1 input/Compare 1 output/PWM1 output. |  |

| P1A                                                                                       |       |              | 0           | CMOS           | Enhanced PWM1 Output A.                       |  |

| PSP4                                                                                      |       |              | I/O         | ST/<br>CMOS    | Parallel Slave Port data.                     |  |

| RD5/P1B/PSP5                                                                              | 28    | 3            |             |                |                                               |  |

| RD5                                                                                       |       |              | I/O         | ST/<br>CMOS    | Digital I/O.                                  |  |

| P1B                                                                                       |       |              | 0           | CMOS           | Enhanced PWM1 Output B.                       |  |

| PSP5                                                                                      |       |              | I/O         | ST/<br>CMOS    | Parallel Slave Port data.                     |  |

| <b>Legend:</b> $I^2C^{TM} = I^2C/SN$                                                      |       |              |             |                | CMOS = CMOS compatible input or output        |  |

| ST = Schmitt Trigger input with CMOS levels Analog = Analog input<br>I = Input O = Output |       |              |             |                |                                               |  |

l P = Input = Power

| Pin Name                                                                                  | Pin<br>Num | Pin<br>Type | Buffer<br>Type | Description                                   |  |  |

|-------------------------------------------------------------------------------------------|------------|-------------|----------------|-----------------------------------------------|--|--|

|                                                                                           |            |             |                | PORTB is a bidirectional I/O port.            |  |  |

| RB0/AN10/FLT0/INT0                                                                        | 13         |             |                |                                               |  |  |

| RB0                                                                                       |            | I/O         | ST/<br>CMOS    | Digital I/O.                                  |  |  |

| AN10                                                                                      |            | Ι           | Analog         | Analog Input 10.                              |  |  |

| FLT0                                                                                      |            | Ι           | ST             | Enhanced PWM Fault input for ECCP1.           |  |  |

| INT0                                                                                      |            | Ι           | ST             | External Interrupt 0.                         |  |  |

| RB1/AN8/CTDIN/INT1                                                                        | 14         |             |                |                                               |  |  |

| RB1                                                                                       |            | I/O         | ST/<br>CMOS    | Digital I/O.                                  |  |  |

| AN8                                                                                       |            | Ι           | Analog         | Analog Input 8.                               |  |  |

| CTDIN                                                                                     |            | Ι           | ST             | CTMU pulse delay input.                       |  |  |

| INT1                                                                                      |            | Ι           | ST             | External Interrupt 1.                         |  |  |

| RB2/CANTX/CTED1/<br>INT2                                                                  | 15         |             |                |                                               |  |  |

| RB2                                                                                       |            | I/O         | ST/<br>CMOS    | Digital I/O.                                  |  |  |

| CANTX                                                                                     |            | 0           | CMOS           | CAN bus TX.                                   |  |  |

| CTED1                                                                                     |            | Ι           | ST             | CTMU Edge 1 input.                            |  |  |

| INT2                                                                                      |            | Ι           | ST             | External Interrupt 2.                         |  |  |

| RB3/CANRX/CTED2/<br>INT3                                                                  | 16         |             |                |                                               |  |  |

| RB3                                                                                       |            | I/O         | ST/<br>CMOS    | Digital I/O.                                  |  |  |

| CANRX                                                                                     |            | Ι           | ST             | CAN bus RX.                                   |  |  |

| CTED2                                                                                     |            | Ι           | ST             | CTMU Edge 2 input.                            |  |  |

| INT3                                                                                      |            | Ι           | ST             | External Interrupt 3.                         |  |  |

| RB4/AN9/CTPLS/KBI0                                                                        | 20         |             |                |                                               |  |  |

| RB4                                                                                       |            | I/O         | ST/<br>CMOS    | Digital I/O.                                  |  |  |

| AN9                                                                                       |            | Ι           | Analog         | Analog Input 9.                               |  |  |

| CTPLS                                                                                     |            | 0           | ST             | CTMU pulse generator output.                  |  |  |

| KBI0                                                                                      |            | Ι           | ST             | Interrupt-on-change pin.                      |  |  |

| RB5/T0CKI/T3CKI/CCP5/<br>KBI1                                                             | 21         |             |                |                                               |  |  |

| RB5                                                                                       |            | I/O         | ST/<br>CMOS    | Digital I/O.                                  |  |  |

| TOCKI                                                                                     |            | I           | ST             | Timer0 external clock input.                  |  |  |

| ТЗСКІ                                                                                     |            | I           | ST             | Timer3 external clock input.                  |  |  |

| CCP5                                                                                      |            | I/O         | ST/<br>CMOS    | Capture 5 input/Compare 5 output/PWM5 output. |  |  |

| KBI1                                                                                      |            | I           | ST             | Interrupt-on-change pin.                      |  |  |

| Legend: I <sup>2</sup> C™ = I <sup>2</sup> C/SI<br>ST = Schmitt<br>I = Input<br>P = Power |            |             | er             | CMOS = CMOS compatible input or output        |  |  |

| TABLE 1-6: | PIC18F6XK80 PINOUT I/O DESCRIPTIONS (CONTINUED) |

|------------|-------------------------------------------------|

|------------|-------------------------------------------------|

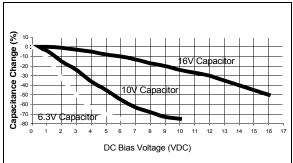

# 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R), or -20%/+80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex:  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%$ . Due to the extreme temperature tolerance, a 10  $\mu$ F nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal regulator if the application must operate over a wide temperature range.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

A typical DC bias voltage vs. capacitance graph for X7R type and Y5V type capacitors is shown in Figure 2-4.

#### FIGURE 2-4: DC BIAS VOLTAGE vs. CAPACITANCE CHARACTERISTICS

When selecting a ceramic capacitor to be used with the internal voltage regulator, it is suggested to select a high-voltage rating, so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at 16V for the 2.5V core voltage. Suggested capacitors are shown in Table 2-1.

# 2.5 ICSP Pins

The PGC and PGD pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100 $\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGC and PGD pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGCx/PGDx pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 30.0 "Development Support"**.

The use of the flag and control bits in the OSCCON register is discussed in more detail in **Section 4.0** "Power-Managed Modes".

- Note 1: The Timer1/3/5/7 oscillator must be enabled to select the secondary clock source. The Timerx oscillator is enabled by setting the SOSCEN bit in the Timerx Control register (TxCON<3>). If the Timerx oscillator is not enabled, then any attempt to select a secondary clock source when executing a SLEEP instruction will be ignored.

- 2: It is recommended that the Timerx oscillator be operating and stable before executing the SLEEP instruction or a very long delay may occur while the Timerx oscillator starts.

#### 3.3.2.1 System Clock Selection and Device Resets

Since the SCSx bits are cleared on all forms of Reset, this means the primary oscillator defined by the FOSC<3:0> Configuration bits is used as the primary clock source on device Resets. This could either be the internal oscillator block by itself, or one of the other primary clock sources (HS, EC, XT, LP, External RC and PLL-enabled modes).

In those cases when the internal oscillator block, without PLL, is the default clock on Reset, the Fast RC Oscillator (INTOSC) will be used as the device clock source. It will initially start at 8 MHz; the postscaler selection that corresponds to the Reset value of the IRCF<2:0> bits ('110').

Regardless of which primary oscillator is selected, INTOSC will always be enabled on device power-up. It serves as the clock source until the device has loaded its configuration values from memory. It is at this point that the FOSCx Configuration bits are read and the oscillator selection of the operational mode is made.

Note that either the primary clock source or the internal oscillator will have two bit setting options for the possible values of the SCS<1:0> bits, at any given time.

# 3.3.3 OSCILLATOR TRANSITIONS

PIC18F66K80 family devices contain circuitry to prevent clock "glitches" when switching between clock sources. A short pause in the device clock occurs during the clock switch. The length of this pause is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Clock transitions are discussed in greater detail in Section 4.1.2 "Entering Power-Managed Modes".

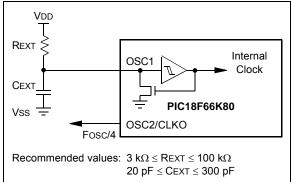

# 3.4 RC Oscillator

For timing-insensitive applications, the RC and RCIO Oscillator modes offer additional cost savings. The actual oscillator frequency is a function of several factors:

- · Supply voltage

- Values of the external resistor (REXT) and capacitor (CEXT)

- · Operating temperature

Given the same device, operating voltage and temperature, and component values, there will also be unit to unit frequency variations. These are due to factors such as:

- · Normal manufacturing variation

- Difference in lead frame capacitance between package types (especially for low CEXT values)

- Variations within the tolerance of the limits of  $\ensuremath{\mathsf{Rext}}$  and  $\ensuremath{\mathsf{Cext}}$

In the RC Oscillator mode, the oscillator frequency, divided by 4, is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 3-2 shows how the R/C combination is connected.

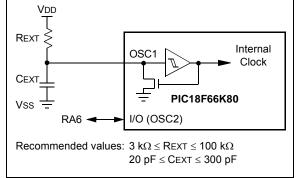

The RCIO Oscillator mode (Figure 3-3) functions like the RC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6).

#### FIGURE 3-3: RCIO OSO

#### EXAMPLE 8-1: DATA EEPROM READ

| MOVLW | DATA_EE_ADDRH | ;                                           |

|-------|---------------|---------------------------------------------|

| MOVWF | EEADRH        | ; Upper bits of Data Memory Address to read |

| MOVLW | DATA_EE_ADDR  | ;                                           |

| MOVWF | EEADR         | ; Lower bits of Data Memory Address to read |

| BCF   | EECON1, EEPGD | ; Point to DATA memory                      |

| BCF   | EECON1, CFGS  | ; Access EEPROM                             |

| BSF   | EECON1, RD    | ; EEPROM Read                               |

| NOP   |               |                                             |

| MOVF  | EEDATA, W     | ; $W = EEDATA$                              |

#### EXAMPLE 8-2: DATA EEPROM WRITE

|          | MOVLW | DATA_EE_ADDRH | ;                                             |

|----------|-------|---------------|-----------------------------------------------|

|          | MOVWF | EEADRH        | ; Upper bits of Data Memory Address to write  |

|          | MOVLW | DATA_EE_ADDR  | ;                                             |

|          | MOVWF | EEADR         | ; Lower bits of Data Memory Address to write  |

|          | MOVLW | DATA_EE_DATA  | i                                             |

|          | MOVWF | EEDATA        | ; Data Memory Value to write                  |

|          | BCF   | EECON1, EEPGD | ; Point to DATA memory                        |

|          | BCF   | EECON1, CFGS  | ; Access EEPROM                               |

|          | BSF   | EECON1, WREN  | ; Enable writes                               |

|          |       |               |                                               |

|          | BCF   | INTCON, GIE   | ; Disable Interrupts                          |

|          | MOVLW | 55h           | i                                             |

| Required | MOVWF | EECON2        | ; Write 55h                                   |

| Sequence | MOVLW | 0AAh          | ;                                             |

|          | MOVWF | EECON2        | ; Write OAAh                                  |

|          | BSF   | EECON1, WR    | ; Set WR bit to begin write                   |

|          | BTFSC | EECON1, WR    | ; Wait for write to complete GOTO \$-2        |

|          | BSF   | INTCON, GIE   | ; Enable Interrupts                           |

|          |       |               |                                               |

|          |       |               | ; User code execution                         |

|          | BCF   | EECON1, WREN  | ; Disable writes on write complete (EEIF set) |

### **10.9 Context Saving During Interrupts**

During interrupts, the return PC address is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the Fast Return Stack. If a fast return from interrupt is not used (see **Section 6.3 "Data Memory Organization"**), the user may need to save the WREG, STATUS and BSR registers on entry to the Interrupt Service Routine (ISR). Depending on the user's application, other registers also may need to be saved.

Example 10-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

#### EXAMPLE 10-1: SAVING STATUS, WREG AND BSR REGISTERS IN RAM

| MOVWF<br>MOVFF<br>;<br>; USER<br>; | W_TEMP<br>STATUS, STATUS_TEMP<br>BSR, BSR_TEMP<br>ISR CODE | ; W_TEMP is in virtual bank<br>; STATUS_TEMP located anywhere<br>; BSR_TMEP located anywhere |

|------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| MOVFF                              | BSR_TEMP, BSR                                              | ; Restore BSR                                                                                |

| MOVF                               | W_TEMP, W                                                  | ; Restore WREG                                                                               |

| MOVFF                              | STATUS_TEMP, STATUS                                        | ; Restore STATUS                                                                             |

#### TABLE 10-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name    | Bit 7    | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0   |

|---------|----------|-----------|---------|---------|---------|---------|--------|---------|

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF  | INT0IF | RBIF    |

| INTCON2 | RBPU     | INTEDG0   | INTEDG1 | INTEDG2 | INTEDG3 | TMR0IP  | INT3IP | RBIP    |

| INTCON3 | INT2IP   | INT1IP    | INT3IE  | INT2IE  | INT1IE  | INT3IF  | INT2IF | INT1IF  |

| PIR1    | PSPIP    | ADIF      | RC1IF   | TX1IF   | SSPIF   | TMR1GIF | TMR2IF | TMR1IF  |

| PIR2    | OSCFIF   | —         | _       | _       | BCLIF   | HLVDIF  | TMR3IF | TMR3GIF |

| PIR3    | —        | —         | RC2IF   | TX2IF   | CTMUIF  | CCP2IF  | CCP1IF | —       |

| PIR4    | TMR4IF   | EEIF      | CMP2IF  | CMP1IF  | —       | CCP5IF  | CCP4IF | CCP3IF  |

| PIR5    | IRXIF    | WAKIF     | ERRIF   | TXB2IF  | TXB1IF  | TXB0IF  | RXB1IF | RXB0IF  |

| PIE1    | PSPIE    | ADIE      | RC1IE   | TX1IE   | SSPIE   | TMR1GIE | TMR2IE | TMR1IE  |

| PIE2    | OSCFIE   | —         | _       | _       | BCLIE   | HLVDIE  | TMR3IE | TMR3GIE |

| PIE3    | —        | —         | RC2IE   | TX2IE   | CTMUIE  | CCP2IE  | CCP1IE |         |

| PIE4    | TMR4IE   | EEIE      | CCP2IE  | CMP1IE  | —       | CCP5IE  | CCP4IE | CCP3IE  |

| PIE5    | IRXIE    | WAKIE     | ERRIE   | TXB2IE  | TXB1IE  | TXB0IE  | RXB1IE | RXB0IE  |

| IPR1    | PSPIP    | ADIP      | RC1IP   | TX1IP   | SSPIP   | TMR1GIP | TMR2IP | TMR1IP  |

| IPR2    | OSCFIP   | _         | _       | _       | BCLIP   | HLVDIP  | TMR3IP | TMR3GIP |

| IPR3    | _        | _         | RC2IP   | TX2IP   | CTMUIP  | CCP2IP  | CCP1IP |         |

| IPR4    | TMR4IP   | EEIP      | CMP2IP  | CMP1IP  | —       | CCP5IP  | CCP4IP | CCP3IP  |

| IPR5    | IRXIP    | WAKIP     | ERRIP   | TXB2IP  | TXB1IP  | TXB0IP  | RXB1IP | RXB0IP  |

| RCON    | IPEN     | SBOREN    | CM      | RI      | TO      | PD      | POR    | BOR     |

Legend: Shaded cells are not used by the interrupts.

# 12.5 Carrier Source Polarity Select

The signal provided from any selected input source for the carrier high and carrier low signals can be inverted. Inverting the signal for the carrier high source is enabled by setting the MDCHPOL bit of the MDCARH register. Inverting the signal for the carrier low source is enabled by setting the MDCLPOL bit of the MDCARL register.

# 12.6 Carrier Source Pin Disable

Some peripherals assert control over their corresponding output pin when they are enabled. For example, when the CCP1 module is enabled, the output of CCP1 is connected to the CCP1 pin.

This default connection to a pin can be disabled by setting the MDCHODIS bit in the MDCARH register for the carrier high source and the MDCLODIS bit in the MDCARL register for the carrier low source.

#### 12.7 Programmable Modulator Data

The MDBIT of the MDCON register can be selected as the source for the modulator signal. This gives the user the ability to program the value used for modulation.

### 12.8 Modulator Source Pin Disable

The modulator source default connection to a pin can be disabled by setting the MDSODIS bit in the MDSRC register.

### 12.9 Modulated Output Polarity

The modulated output signal provided on the MDOUT pin can also be inverted. Inverting the modulated output signal is enabled by setting the MDOPOL bit of the MDCON register.

#### 12.10 Slew Rate Control

When modulated data streams of 20 MHz or greater are required, the slew rate limitation on the output port pin can be disabled. The slew rate limitation can be removed by clearing the MDSLR bit in the MDCON register.

### 12.11 Operation In Sleep Mode

The DSM module is not affected by Sleep mode. The DSM can still operate during Sleep if the Carrier and Modulator input sources are also still operable during Sleep.

#### 12.12 Effects of a Reset

Upon any device Reset, the Data Signal Modulator module is disabled. The user's firmware is responsible for initializing the module before enabling the output. The registers are reset to their default values.

# 19.3 Compare Mode

In Compare mode, the 16-bit CCPRx register value is constantly compared against the Timer register pair value selected in the CCPTMR register. When a match occurs, the CCPx pin can be:

- Driven high

- Driven low

- Toggled (high-to-low or low-to-high)

- Unchanged (that is, reflecting the state of the I/O latch)

The action on the pin is based on the value of the mode select bits (CCPxM<3:0>). At the same time, the interrupt flag bit, CCPxIF, is set.

Figure 19-2 gives the Compare mode block diagram

#### 19.3.1 CCP PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the appropriate TRIS bit.

| Note: | Clearing the CCPxCON register will force  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|

|       | the corresponding CCPx compare output     |  |  |  |  |  |  |  |

|       | latch (depending on device configuration) |  |  |  |  |  |  |  |

|       | to the default low level. This is not the |  |  |  |  |  |  |  |

|       | PORTx data latch.                         |  |  |  |  |  |  |  |

#### 19.3.2 TIMER1/3 MODE SELECTION

If the CCPx module is using the compare feature in conjunction with any of the Timer1/3 timers, the timers must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the compare operation may not work.

Note: Details of the timer assignments for the CCPx modules are given in Table 19-2.

#### 19.3.3 SOFTWARE INTERRUPT MODE

When the Generate Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPx pin is not affected. Only a CCP interrupt is generated, if enabled, and the CCPxIE bit is set.

#### 19.3.4 SPECIAL EVENT TRIGGER

All CCP modules are equipped with a Special Event Trigger. This is an internal hardware signal generated in Compare mode to trigger actions by other modules. The Special Event Trigger is enabled by selecting the Compare Special Event Trigger mode bits (CCPxM<3:0> = 1011).

For either CCPx module, the Special Event Trigger resets the Timer register pair for whichever timer resource is currently assigned as the module's time base. This allows the CCPRx registers to serve as a programmable Period register for either timer.

#### 21.4.14 SLEEP OPERATION

While in Sleep mode, the  $I^2C$  module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 21.4.15 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 21.4.16 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit (SSPSTAT<4>) is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the MSSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- A Start Condition

- · A Repeated Start Condition

- An Acknowledge Condition

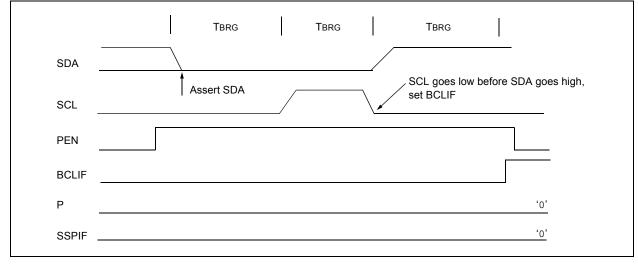

#### 21.4.17 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

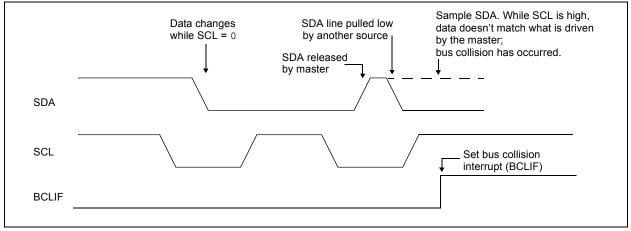

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high, and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = 0, then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF, and reset the  $I^2C$  port to its Idle state (Figure 21-27).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine, and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is Idle and the S and P bits are cleared.

#### FIGURE 21-27: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

# 21.4.17.2 Bus Collision During a Repeated Start Condition

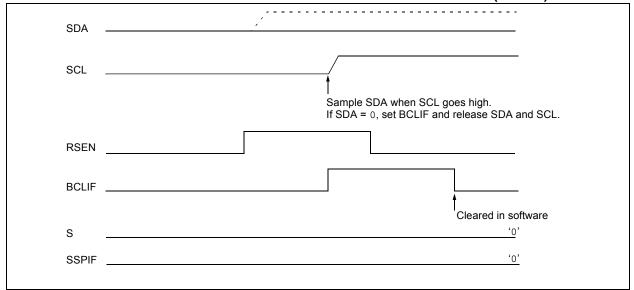

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from a low level to a high level.

- SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 21-31). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

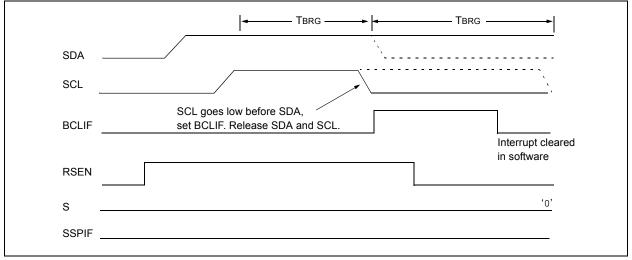

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition (see Figure 21-32).

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

FIGURE 21-31: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

#### 21.4.17.3 Bus Collision During a Stop Condition

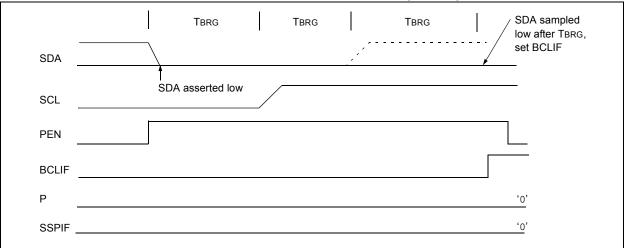

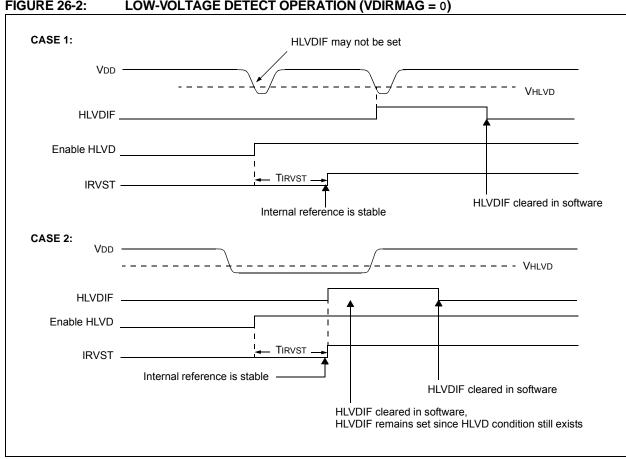

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high.

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPADD<6:0> and counts down to 0. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 21-33). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 21-34).

#### FIGURE 21-33: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 21-34: BUS COLLISION DURING A STOP CONDITION (CASE 2)

#### **REGISTER 23-4:** ADRESH: A/D RESULT HIGH BYTE REGISTER, LEFT JUSTIFIED (ADFM = 0)

| R/W-x   | R/W-x   | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|---------|---------|--------|--------|--------|--------|--------|--------|

| ADRES11 | ADRES10 | ADRES9 | ADRES8 | ADRES7 | ADRES6 | ADRES5 | ADRES4 |

| bit 7   |         |        |        |        |        |        |        |

|         |         |        |        |        |        |        |        |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 ADRES<11:4>: A/D Result High Byte bits

#### **REGISTER 23-5:** ADRESL: A/D RESULT LOW BYTE REGISTER, LEFT JUSTIFIED (ADFM = 0)

| R/W-x  | R/W-x  | R/W-x  | R/W-x  | U-x    | U-x    | U-x    | U-x    |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADRES3 | ADRES2 | ADRES1 | ADRES0 | ADSGN3 | ADSGN2 | ADSGN1 | ADSGN0 |

| bit 7  |        |        |        |        |        |        |        |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

ADSGN<3:0>: A/D Result Sign bits

1 = A/D result is negative

0 = A/D result is positive

#### REGISTER 23-6: ADRESH: A/D RESULT HIGH BYTE REGISTER, RIGHT JUSTIFIED (ADFM = 1)

| U-x    | U-x    | U-x    | U-x    | R/W-x   | R/W-x   | R/W-x  | R/W-x  |

|--------|--------|--------|--------|---------|---------|--------|--------|

| ADSGN7 | ADSGN6 | ADSGN5 | ADSGN4 | ADRES11 | ADRES10 | ADRES9 | ADRES8 |

| bit 7  |        |        |        |         |         |        |        |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-4 ADSGN<7:4>: A/D Result Sign bits 1 = A/D result is negative 0 = A/D result is positive

bit 3-0 ADRES<11:8>: A/D Result High Byte bits

bit 3-0

# REGISTER 28-12: CONFIG7H: CONFIGURATION REGISTER 7 HIGH (BYTE ADDRESS 30000Dh)

| U-0                                | R/C-1 | U-0           | U-0                                | U-0  | U-0             | U-0  | U-0   |

|------------------------------------|-------|---------------|------------------------------------|------|-----------------|------|-------|

| —                                  | EBTRB | —             | _                                  | —    | —               | —    | —     |

| bit 7                              |       |               |                                    |      |                 |      | bit 0 |

|                                    |       |               |                                    |      |                 |      |       |

| Legend:                            |       | C = Clearable | bit                                |      |                 |      |       |

| R = Readable bit W = Writable bit  |       | bit           | U = Unimplemented bit, read as '0' |      |                 |      |       |

| -n = Value at POR '1' = Bit is set |       |               | '0' = Bit is cle                   | ared | x = Bit is unkr | nown |       |

bit 7 Unimplemented: Read as '0'

|       | •                                                                                    |

|-------|--------------------------------------------------------------------------------------|

| bit 6 | EBTRB: Boot Block Table Read Protection bit                                          |

|       | 1 = Boot block is not protected from table reads executed in other $blocks^{(1)}$    |

|       | 0 = Boot block is protected from table reads executed in other blocks <sup>(1)</sup> |

|       |                                                                                      |

bit 5-0 Unimplemented: Read as '0'

**Note 1:** For the memory size of the blocks, see Figure 28-6.

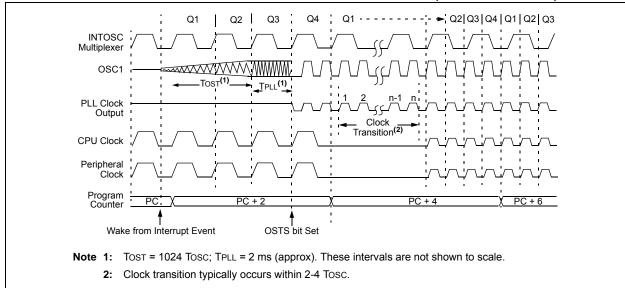

### 28.4 Two-Speed Start-up

The Two-Speed Start-up feature helps to minimize the latency period from oscillator start-up to code execution by allowing the microcontroller to use the INTOSC (LF-INTOSC, MF-INTOSC, HF-INTOSC) oscillator as a clock source until the primary clock source is available. It is enabled by setting the IESO Configuration bit.

Two-Speed Start-up should be enabled only if the primary oscillator mode is LP, XT or HS (Crystal-Based modes). Other sources do not require an OST start-up delay; for these, Two-Speed Start-up should be disabled.

When enabled, Resets and wake-ups from Sleep mode cause the device to configure itself to run from the internal oscillator block as the clock source, following the time-out of the Power-up Timer after a Power-on Reset is enabled. This allows almost immediate code execution while the primary oscillator starts and the OST is running. Once the OST times out, the device automatically switches to PRI\_RUN mode.

To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IRCF<2:0>, immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting the IRCF2:0> bits prior to entering Sleep mode.

In all other power-managed modes, Two-Speed Startup is not used. The device will be clocked by the currently selected clock source until the primary clock source becomes available. The setting of the IESO bit is ignored.

#### 28.4.1 SPECIAL CONSIDERATIONS FOR USING TWO-SPEED START-UP

While using the INTOSC oscillator in Two-Speed Startup, the device still obeys the normal command sequences for entering power-managed modes, including multiple SLEEP instructions (refer to **Section 4.1.4 "Multiple Sleep Commands**"). In practice, this means that user code can change the SCS<1:0> bit settings or issue SLEEP instructions before the OST times out. This would allow an application to briefly wake-up, perform routine "housekeeping" tasks and return to Sleep before the device starts to operate from the primary oscillator.

User code can also check if the primary clock source is currently providing the device clocking by checking the status of the OSTS bit (OSCCON<3>). If the bit is set, the primary oscillator is providing the clock. Otherwise, the internal oscillator block is providing the clock during wake-up from Reset or Sleep mode.

#### FIGURE 28-3: TIMING TRANSITION FOR TWO-SPEED START-UP (INTOSC TO HSPLL)

#### 28.6.2 DATA EEPROM CODE PROTECTION

The entire data EEPROM is protected from external reads and writes by two bits: CPD and WRTD. CPD inhibits external reads and writes of data EEPROM. WRTD inhibits internal and external writes to data EEPROM. The CPU can always read data EEPROM under normal operation, regardless of the protection bit settings.

#### 28.6.3 CONFIGURATION REGISTER PROTECTION

The Configuration registers can be write-protected. The WRTC bit controls protection of the Configuration registers. In normal execution mode, the WRTC bit is readable only. WRTC can only be written via ICSP or an external programmer.

#### 28.7 ID Locations

Eight memory locations (20000h-200007h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are both readable and writable during normal execution through the TBLRD and TBLWT instructions or during program/verify. The ID locations can be read when the device is code-protected.

# 28.8 In-Circuit Serial Programming

The PIC18F66K80 family of devices can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

For the various programming modes, see the programming specification

### 28.9 In-Circuit Debugger

When the  $\overline{\text{DEBUG}}$  Configuration bit is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some resources are not available for general use. Table 28-5 shows which resources are required by the background debugger.

| TABLE 28-5: | DEBUGGER | RESOURCES |

|-------------|----------|-----------|

|-------------|----------|-----------|

| I/O Pins:       | RB6, RB7   |

|-----------------|------------|

| Stack:          | Two levels |

| Program Memory: | 512 bytes  |

| Data Memory:    | 10 bytes   |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/RE3, VDD, VSS, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip or one of the third-party development tool companies.

| SUB          | WFB                                | Subtract V                                                                                          | N from f                                                                                                                                                                                                    | with Borr                                                        | ow                                             |  |  |

|--------------|------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------|--|--|

| Syntax:      |                                    | SUBWFB f {,d {,a}}                                                                                  |                                                                                                                                                                                                             |                                                                  |                                                |  |  |

| Oper         | ands:                              | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \end{array}$                                   |                                                                                                                                                                                                             |                                                                  |                                                |  |  |

|              |                                    | a ∈ [0,1]                                                                                           | _                                                                                                                                                                                                           |                                                                  |                                                |  |  |

| Oper         | ation:                             | (f) – (W) –                                                                                         | $(C) \rightarrow de$                                                                                                                                                                                        | st                                                               |                                                |  |  |

| Statu        | is Affected:                       | N, OV, C, I                                                                                         | DC, Z                                                                                                                                                                                                       |                                                                  | <u> </u>                                       |  |  |

| Enco         | oding:                             | 0101                                                                                                | 10da                                                                                                                                                                                                        | ffff                                                             | ffff                                           |  |  |

| Description: |                                    | from regist<br>method). If<br>in W. If 'd' i                                                        | Subtract W and the Carry flag (borrow)<br>from register 'f' (2's complement<br>method). If 'd' is '0', the result is stored<br>in W. If 'd' is '1', the result is stored back<br>in register 'f' (default). |                                                                  |                                                |  |  |

|              |                                    | lf 'a' is '0',<br>lf 'a' is '1',<br>GPR bank                                                        | the BSR i                                                                                                                                                                                                   |                                                                  |                                                |  |  |

|              |                                    | If 'a' is '0' a<br>set is enab<br>in Indexed<br>mode whe<br>Section 29<br>Bit-Orient<br>Literal Off | bled, this in<br>Literal Of<br>never f ≤ 9<br>9.2.3 "Byt<br>ed Instru                                                                                                                                       | nstruction<br>fset Addro<br>95 (5Fh).<br>te-Oriento<br>ctions in | operates<br>essing<br>See<br>ed and<br>Indexed |  |  |

| Word         | ls:                                | 1                                                                                                   |                                                                                                                                                                                                             |                                                                  |                                                |  |  |

| Cycle        | es:                                | 1                                                                                                   |                                                                                                                                                                                                             |                                                                  |                                                |  |  |

| QC           | ycle Activity:                     |                                                                                                     |                                                                                                                                                                                                             |                                                                  |                                                |  |  |

|              | Q1                                 | Q2                                                                                                  | Q                                                                                                                                                                                                           | 3                                                                | Q4                                             |  |  |

|              | Decode                             | Read                                                                                                | Proce                                                                                                                                                                                                       |                                                                  | Write to                                       |  |  |

| <b>E</b> ver |                                    | register 'f'                                                                                        | Dat                                                                                                                                                                                                         |                                                                  | estination                                     |  |  |

| Exar         | n <u>ple 1:</u><br>Before Instruct | SUBWFB                                                                                              | REG, 1                                                                                                                                                                                                      | L, U                                                             |                                                |  |  |

|              | REG                                | = 19h                                                                                               | (000                                                                                                                                                                                                        | 1 1001)                                                          |                                                |  |  |

|              | W                                  | = 0Dh<br>= 1                                                                                        |                                                                                                                                                                                                             | 0 1101)                                                          |                                                |  |  |

|              | C<br>After Instructio              | -                                                                                                   |                                                                                                                                                                                                             |                                                                  |                                                |  |  |

|              | REG                                | = 0Ch                                                                                               | (000                                                                                                                                                                                                        |                                                                  |                                                |  |  |

|              | W<br>C                             | = 0Dh<br>= 1                                                                                        | (000                                                                                                                                                                                                        | 0 1101)                                                          |                                                |  |  |

|              | Ž<br>N                             | = 0                                                                                                 |                                                                                                                                                                                                             |                                                                  |                                                |  |  |

| Evon         |                                    | = 0                                                                                                 |                                                                                                                                                                                                             | It is positi                                                     | ve                                             |  |  |

|              | nple 2:<br>Before Instruct         | SUBWFB                                                                                              | REG, O                                                                                                                                                                                                      | , 0                                                              |                                                |  |  |

|              | REG                                | = 1Bh                                                                                               | (000                                                                                                                                                                                                        | 1 1011)                                                          |                                                |  |  |

|              | W<br>C                             | = 1Ah<br>= 0                                                                                        | (000)                                                                                                                                                                                                       | 1 1010)                                                          |                                                |  |  |

|              | After Instructio<br>REG<br>W       | n<br>= 1Bh<br>= 00h                                                                                 | (000                                                                                                                                                                                                        | 1 1011)                                                          |                                                |  |  |

|              | C<br>Z<br>N                        | = 1<br>= 1<br>= 0                                                                                   | ; resu                                                                                                                                                                                                      | lt is zero                                                       |                                                |  |  |

| <u>Ex</u> an | nple 3:                            | SUBWFB                                                                                              | REG, 1                                                                                                                                                                                                      | L, O                                                             |                                                |  |  |

|              | Before Instruct                    |                                                                                                     |                                                                                                                                                                                                             |                                                                  |                                                |  |  |

|              | REG<br>W<br>C                      | = 03h<br>= 0Eh<br>= 1                                                                               |                                                                                                                                                                                                             | 0 0011)<br>0 1101)                                               |                                                |  |  |

|              | After Instructio                   |                                                                                                     |                                                                                                                                                                                                             |                                                                  |                                                |  |  |

|              | REG                                | = F5h                                                                                               |                                                                                                                                                                                                             | 1 0100)                                                          |                                                |  |  |

|              | W                                  | = 0Eh                                                                                               |                                                                                                                                                                                                             | comp]<br>0 1101)                                                 |                                                |  |  |

|              | C<br>Z<br>N                        | = 0<br>= 0<br>= 1                                                                                   |                                                                                                                                                                                                             | It is negat                                                      | ive                                            |  |  |

|              |                                    |                                                                                                     |                                                                                                                                                                                                             |                                                                  |                                                |  |  |

| SWAPF                                                                                                   | Swap f                                                                                 |                                                                                 |                                    |  |  |  |

|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------|--|--|--|

| Syntax:                                                                                                 | SWAPF f                                                                                | [,d {,a}}                                                                       |                                    |  |  |  |

| Operands:                                                                                               | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$     | d ∈ [0,1]                                                                       |                                    |  |  |  |

| Operation:                                                                                              | (f<3:0>) → dest<7:4>,<br>(f<7:4>) → dest<3:0>                                          |                                                                                 |                                    |  |  |  |

| Status Affected:                                                                                        | None                                                                                   |                                                                                 |                                    |  |  |  |

| Encoding:                                                                                               | 0011                                                                                   | 10da ff                                                                         | ff ffff                            |  |  |  |

| Description:                                                                                            | 'f' are excha<br>is placed in                                                          | and lower nibl<br>anged. If 'd' is<br>W. If 'd' is '1'<br>gister 'f' (defa      |                                    |  |  |  |

|                                                                                                         | ,                                                                                      |                                                                                 | nk is selected<br>ed to select the |  |  |  |

|                                                                                                         | set is enabl<br>in Indexed I<br>mode when<br>Section 29                                | ed, this instru<br>∟iteral Offset a<br>ever f ≤ 95 (5<br>. <b>2.3 "Byte-O</b> r | Fh). See                           |  |  |  |

|                                                                                                         |                                                                                        | d Instruction<br>set Mode" for                                                  | ns in Indexed                      |  |  |  |

| Words:                                                                                                  |                                                                                        |                                                                                 | ns in Indexed                      |  |  |  |

| Words:<br>Cycles:                                                                                       | Literal Offs                                                                           |                                                                                 | ns in Indexed                      |  |  |  |

|                                                                                                         | Literal Offs                                                                           |                                                                                 | ns in Indexed                      |  |  |  |

| Cycles:                                                                                                 | Literal Offs                                                                           |                                                                                 | ns in Indexed                      |  |  |  |

| Cycles:<br>Q Cycle Activity:                                                                            | Literal Offs<br>1<br>1<br>Q2<br>Read                                                   | Q3<br>Process                                                                   | Q4<br>Write to                     |  |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1                                                                      | Literal Offs<br>1<br>1<br>Q2                                                           | Q3                                                                              | as in Indexed<br>details.<br>Q4    |  |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1                                                                      | Literal Offs<br>1<br>1<br>Q2<br>Read<br>register 'f'                                   | Q3<br>Process                                                                   | Q4<br>Write to                     |  |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode                                                            | Literal Offs<br>1<br>1<br>Q2<br>Read<br>register 'f'                                   | Q3<br>Process<br>Data                                                           | Q4<br>Write to                     |  |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:<br>Before Instruc<br>REG                       | Literal Offs<br>1<br>1<br>Q2<br>Read<br>register 'f'<br>SWAPF R<br>tion<br>= 53h       | Q3<br>Process<br>Data                                                           | Q4<br>Write to                     |  |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:<br>Before Instruc                              | Literal Offs<br>1<br>1<br>Q2<br>Read<br>register 'f'<br>SWAPF R<br>tion<br>= 53h       | Q3<br>Process<br>Data                                                           | Q4<br>Write to                     |  |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:<br>Before Instruct<br>REG<br>After Instruction | Literal Offs<br>1<br>1<br>Q2<br>Read<br>register 'f'<br>SWAPF R<br>tion<br>= 53h<br>on | Q3<br>Process<br>Data                                                           | Q4<br>Write to                     |  |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:<br>Before Instruct<br>REG<br>After Instruction | Literal Offs<br>1<br>1<br>Q2<br>Read<br>register 'f'<br>SWAPF R<br>tion<br>= 53h<br>on | Q3<br>Process<br>Data                                                           | Q4<br>Write to                     |  |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:<br>Before Instruct<br>REG<br>After Instruction | Literal Offs<br>1<br>1<br>Q2<br>Read<br>register 'f'<br>SWAPF R<br>tion<br>= 53h<br>on | Q3<br>Process<br>Data                                                           | Q4<br>Write to                     |  |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br>Example:<br>Before Instruct<br>REG<br>After Instruction | Literal Offs<br>1<br>1<br>Q2<br>Read<br>register 'f'<br>SWAPF R<br>tion<br>= 53h<br>on | Q3<br>Process<br>Data                                                           | Q4<br>Write to                     |  |  |  |

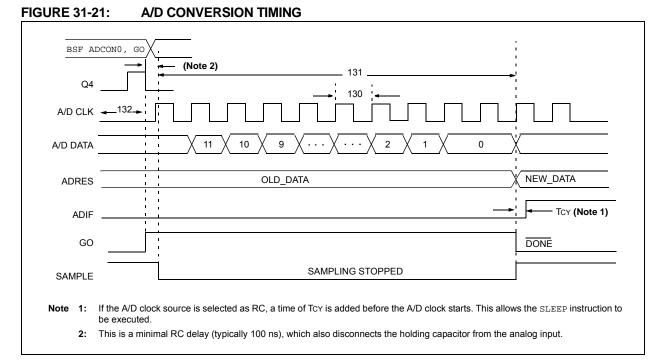

| TABLE 31-26: | A/D CONVERSION REQUIREMENTS |

|--------------|-----------------------------|

|--------------|-----------------------------|

| Param<br>No. | Symbol | Characteristic                                                     | Min | Мах                 | Units | Conditions                                 |

|--------------|--------|--------------------------------------------------------------------|-----|---------------------|-------|--------------------------------------------|

| 130          | Tad    | A/D Clock Period                                                   | 0.8 | 12.5 <sup>(1)</sup> | μS    | Tosc based, VREF $\geq$ 3.0V               |

|              |        |                                                                    | 1.4 | 25 <sup>(1)</sup>   | μS    | VDD = 3.0V; TOSC based,<br>VREF full range |