Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | ECANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 35                                                                           |

| Program Memory Size        | 32KB (16K × 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 3.6K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 11x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 44-QFN (8x8)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf45k80t-i-ml |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

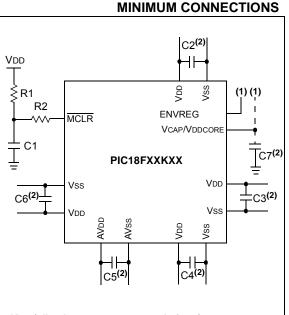

# 2.0 GUIDELINES FOR GETTING STARTED WITH PIC18FXXKXX MICROCONTROLLERS

# 2.1 Basic Connection Requirements

Getting started with the PIC18F66K80 family family of 8-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- ENVREG (if implemented) and VCAP/VDDCORE pins (see Section 2.4 "Voltage Regulator Pins (ENVREG and VCAP/VDDCORE)")

These pins must also be connected if they are being used in the end application:

- PGC/PGD pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

Note: The AVDD and AVss pins must always be connected, regardless of whether any of the analog modules are being used.

The minimum mandatory connections are shown in Figure 2-1.

# FIGURE 2-1: RECOMMENDED

#### Key (all values are recommendations):

C1 through C6: 0.1  $\mu\text{F},$  20V ceramic R1: 10 k $\Omega$

R2: 100Ω to 470Ω

- Note 1: See Section 2.4 "Voltage Regulator Pins (ENVREG and VCAP/VDDCORE)" for explanation of ENVREG pin connections.

- 2: The example shown is for a PIC18F device with five VDD/VSS and AVDD/AVSS pairs. Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

| TABLE 5-4: | INITALIZAT  | REGISTERS (     | JUNTINUED)  |                                          |                                                                  |                                    |

|------------|-------------|-----------------|-------------|------------------------------------------|------------------------------------------------------------------|------------------------------------|

| Register   | A           | pplicable Devic | es          | Power-on<br>Reset,<br>Brown-out<br>Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via<br>WDT<br>or Interrupt |

| RXF12SIDH  | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF11EIDL  | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF11EIDH  | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF11SIDL  | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxx- x-xx                                | uuu- u-uu                                                        | uuu- u-uu                          |

| RXF11SIDH  | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF10EIDL  | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF10EIDH  | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF10SIDL  | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxx- x-xx                                | uuu- u-uu                                                        | uuu- u-uu                          |

| RXF10SIDH  | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF9EIDL   | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF9EIDH   | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF9SIDL   | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxx- x-xx                                | uuu- u-uu                                                        | uuu- u-uu                          |

| RXF9SIDH   | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF8EIDL   | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF8EIDH   | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF8SIDL   | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxx- x-xx                                | uuu- u-uu                                                        | uuu- u-uu                          |

| RXF8SIDH   | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF7EIDL   | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF7EIDH   | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF7SIDL   | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxx- x-xx                                | uuu- u-uu                                                        | uuu- u-uu                          |

| RXF7SIDH   | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF6EIDL   | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF6EIDH   | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXF6SIDL   | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxx- x-xx                                | uuu- u-uu                                                        | uuu- u-uu                          |

| RXF6SIDH   | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | xxxx xxxx                                | uuuu uuuu                                                        | uuuu uuuu                          |

| RXFCON0    | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | 0000 0000                                | 0000 0000                                                        | uuuu uuuu                          |

| RXFCON1    | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | 0000 0000                                | 0000 0000                                                        | uuuu uuuu                          |

| BRGCON3    | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | 00000                                    | 00000                                                            | uuuuu                              |

| BRGCON2    | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | 0000 0000                                | 0000 0000                                                        | uuuu uuuu                          |

| BRGCON1    | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | 0000 0000                                | 0000 0000                                                        | uuuu uuuu                          |

| TXERRCNT   | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | 0000 0000                                | 0000 0000                                                        | uuuu uuuu                          |

| RXERRCNT   | PIC18F2XK80 | PIC18F4XK80     | PIC18F6XK80 | 0000 0000                                | 0000 0000                                                        | uuuu uuuu                          |

### TABLE 5-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged; x = unknown; - = unimplemented bit, read as '0'; q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 5-3 for Reset value for specific conditions.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read as '0'.

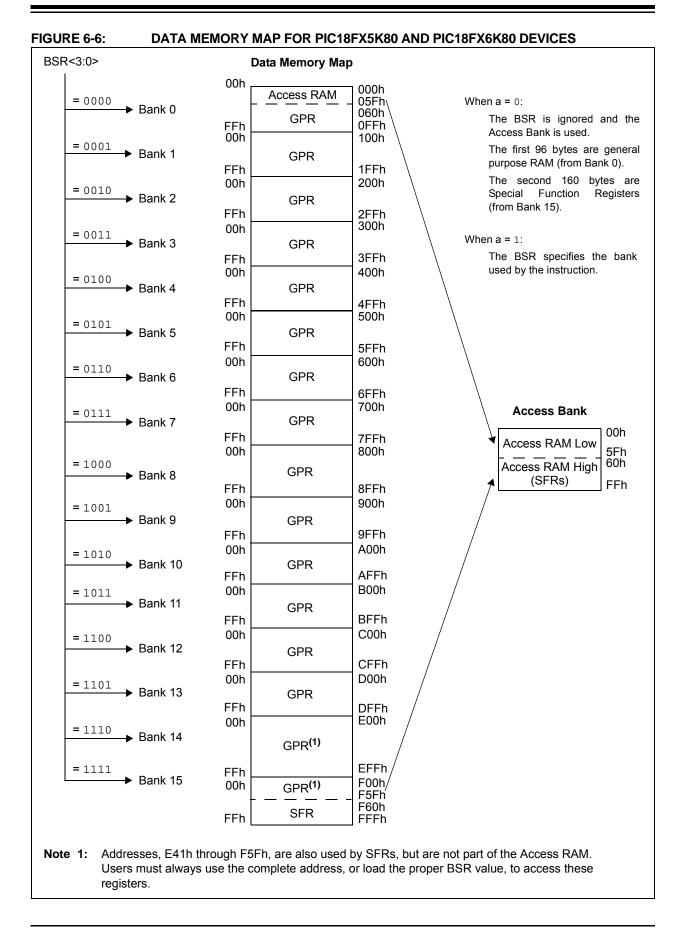

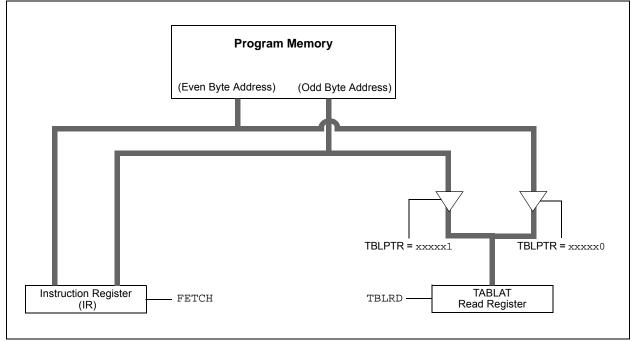

### 7.3 Reading the Flash Program Memory

The TBLRD instruction is used to retrieve data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation.

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 7-4 shows the interface between the internal program memory and the TABLAT.

### FIGURE 7-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 7-1: READING A FLASH PROGRAM MEMORY WORD

| READ WORD | MOVLW<br>MOVWF<br>MOVLW<br>MOVLW<br>MOVLW<br>MOVWF | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL | ; Load TBLPTR with the base<br>; address of the word |

|-----------|----------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------|

|           | TBLRD*                                             | +                                                                                   | ; read into TABLAT and increment                     |

|           | MOVF                                               | TABLAT, W                                                                           | ; get data                                           |

|           | MOVWF                                              | WORD_EVEN                                                                           |                                                      |

|           | TBLRD*                                             | +                                                                                   | ; read into TABLAT and increment                     |

|           | MOVF                                               | TABLAT, W                                                                           | ; get data                                           |

|           | MOVF                                               | WORD_ODD                                                                            |                                                      |

|           |                                                    |                                                                                     |                                                      |

| FIGURE 12-4:                 | CARRIER LOW SYNCHRONIZATION (MDCHSYNC = 0, MDCLSYNC = 1) |

|------------------------------|----------------------------------------------------------|

| Carrier High (CARH)          |                                                          |

| Carrier Low (CARL)           |                                                          |

| Modulator (MOD)              |                                                          |

| MDCHSYNC = 0<br>MDCLSYNC = 1 |                                                          |

| Active Carrier<br>State-     |                                                          |

|                              |                                                          |

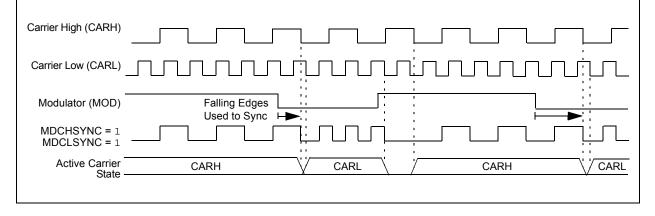

#### FIGURE 12-5: FULL SYNCHRONIZATION (MDCHSYNC = 1, MDCLSYNC = 1)

## 14.7 Resetting Timer1 Using the ECCP Special Event Trigger

If ECCP modules are configured to use Timer1 and to generate a Special Event Trigger in Compare mode (CCP1M<3:0> = 1011), this signal will reset Timer1. The trigger from ECCP will also start an A/D conversion if the A/D module is enabled. (For more information, see **Section 20.3.4 "Special Event Trigger"**.)

To take advantage of this feature, the module must be configured as either a timer or a synchronous counter. When used this way, the CCPR1H:CCPR1L register pair effectively becomes a Period register for Timer1.

If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a Special Event Trigger, the write operation will take precedence.

| Note: | The Special Event Trigger from the ECCP    |

|-------|--------------------------------------------|

|       | module will only clear the TMR1 register's |

|       | content, but not set the TMR1IF interrupt  |

|       | flag bit (PIR1<0>).                        |

# 14.8 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using the Timer1 gate circuitry. This is also referred to as Timer1 gate count enable.

Timer1 gate can also be driven by multiple selectable sources.

#### 14.8.1 TIMER1 GATE COUNT ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit (T1GCON<6>).

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 14-4 for timing details.

| TABLE 14-3: | TIMER1 GATE ENABLE |

|-------------|--------------------|

|             | SELECTIONS         |

| T1CLK <sup>(†)</sup> | T1GPOL<br>(T1GCON<6>) | T1G Pin | Timer1<br>Operation |

|----------------------|-----------------------|---------|---------------------|

| $\uparrow$           | 0                     | 0       | Counts              |

| $\uparrow$           | 0                     | 1       | Holds Count         |

| $\uparrow$           | 1                     | 0       | Holds Count         |

| $\uparrow$           | 1                     | 1       | Counts              |

† The clock on which TMR1 is running. For more information, see Figure 14-1.

| Note: | The CCP and ECCP modules use Timers,     |  |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|--|

|       | 1 through 4, for some modes. The assign- |  |  |  |  |  |  |  |  |

|       | ment of a particular timer to a CCP/ECCP |  |  |  |  |  |  |  |  |

|       | module is determined by the Timer to CCP |  |  |  |  |  |  |  |  |

|       | enable bits in the CCPTMRS register. For |  |  |  |  |  |  |  |  |

|       | more details, see Register 20-2 and      |  |  |  |  |  |  |  |  |

|       | Register 19-2.                           |  |  |  |  |  |  |  |  |

|       |                                          |  |  |  |  |  |  |  |  |

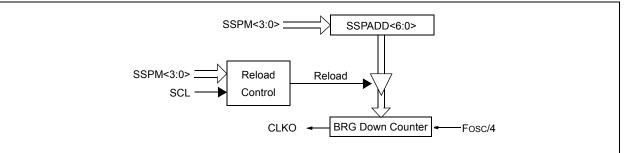

### 21.4.7 BAUD RATE

In I<sup>2</sup>C Master mode, the Baud Rate Generator (BRG) reload value is placed in the 8 bits of the SSPADD register (Figure 21-19). When a write occurs to SSPBUF, the Baud Rate Generator will automatically begin counting. The BRG counts down to 0 and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (Tcr) on the Q2 and Q4 clocks. In I<sup>2</sup>C Master mode, the BRG is reloaded automatically.

Once the given operation is complete (i.e., transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCL pin will remain in its last state.

Table 21-3 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPADD. The SSPADD BRG value of 00h is not supported.

#### FIGURE 21-19: BAUD RATE GENERATOR BLOCK DIAGRAM

### TABLE 21-3: I<sup>2</sup>C<sup>™</sup> CLOCK RATE w/BRG

| Fosc                  | Fcy    | Fcy * 2 | BRG Value | Fsc∟<br>(2 Rollovers of BRG) |

|-----------------------|--------|---------|-----------|------------------------------|

| 40 MHz                | 10 MHz | 20 MHz  | 18h       | 400 kHz <sup>(1)</sup>       |

| 40 MHz                | 10 MHz | 20 MHz  | 1Fh       | 312.5 kHz                    |

| 40 MHz                | 10 MHz | 20 MHz  | 63h       | 100 kHz                      |

| 16 MHz                | 4 MHz  | 8 MHz   | 09h       | 400 kHz <sup>(1)</sup>       |

| 16 MHz                | 4 MHz  | 8 MHz   | 0Ch       | 308 kHz                      |

| 16 MHz                | 4 MHz  | 8 MHz   | 27h       | 100 kHz                      |

| 4 MHz                 | 1 MHz  | 2 MHz   | 02h       | 333 kHz <sup>(1)</sup>       |

| 4 MHz                 | 1 MHz  | 2 MHz   | 09h       | 100 kHz                      |

| 16 MHz <sup>(2)</sup> | 4 MHz  | 8 MHz   | 03h       | 1 MHz <sup>(1)</sup>         |

**Note 1:** The I<sup>2</sup>C interface does not conform to the 400 kHz I<sup>2</sup>C specification (which applies to rates greater than 100 kHz) in all details, but may be used with care where higher rates are required by the application.

2: A minimum 16-MHz Fosc is required for 1 MHz I<sup>2</sup>C.

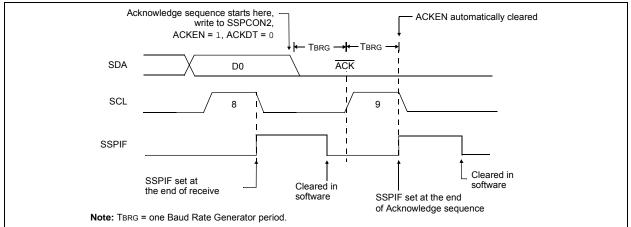

#### 21.4.12 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit. ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG; the SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into an inactive state (Figure 21-25).

#### 21.4.12.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

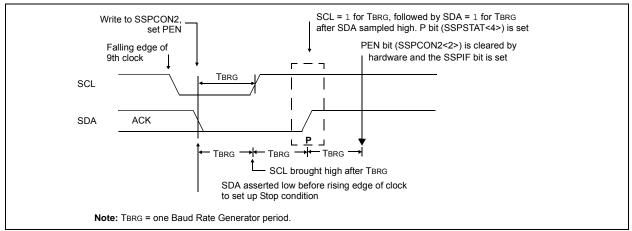

#### 21.4.13 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN (SSPCON2<2>). At the end of a receive/transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to 0. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 21-26).

#### 21.4.13.1 WCOL Status Flag

If the user writes the SSPBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 21-25: ACKNOWLEDGE SEQUENCE WAVEFORM

#### FIGURE 21-26: STOP CONDITION RECEIVE OR TRANSMIT MODE

© 2010-2012 Microchip Technology Inc.

### 22.5 EUSARTx Synchronous Slave Mode

Synchronous Slave mode is entered by clearing bit, CSRC (TXSTAx<7>). This mode differs from the Synchronous Master mode in that the shift clock is supplied externally at the CKx pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in any low-power mode.

#### 22.5.1 EUSARTx SYNCHRONOUS SLAVE TRANSMISSION

The operation of the Synchronous Master and Slave modes is identical, except in the case of Sleep mode.

If two words are written to the TXREGx and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in the TXREGx register.

- c) Flag bit, TXxIF, will not be set.

- d) When the first word has been shifted out of TSR, the TXREGx register will transfer the second word to the TSR and flag bit, TXxIF, will now be set.

e) If enable bit, TXxIE, is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. Clear bits, CREN and SREN.

- 3. If interrupts are desired, set enable bit, TXxIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting enable bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREGx register.

- 8. If using interrupts, ensure that the GIE and PEIE bits (INTCON<7:6>) are set.

| Name     | Bit 7     | Bit 6                     | Bit 5        | Bit 4         | Bit 3  | Bit 2   | Bit 1   | Bit 0  |  |  |

|----------|-----------|---------------------------|--------------|---------------|--------|---------|---------|--------|--|--|

| INTCON   | GIE/GIEH  | PEIE/GIEL                 | TMR0IE       | INT0IE        | RBIE   | TMR0IF  | INT0IF  | RBIF   |  |  |

| PIR1     | PSPIF     | ADIF                      | RC1IF        | TX1IF         | SSPIF  | TMR1GIF | TMR2IF  | TMR1IF |  |  |

| PIE1     | PSPIE     | ADIE                      | RC1IE        | TX1IE         | SSPIE  | TMR1GIE | TMR2IE  | TMR1IE |  |  |

| IPR1     | PSPIP     | ADIP                      | RC1IP        | TX1IP         | SSPIP  | TMR1GIP | TMR2IP  | TMR1IP |  |  |

| PIR3     | _         | _                         | RC2IF        | TX2IF         | CTMUIF | CCP2IF  | CCP1IF  | _      |  |  |

| PIE3     | —         | _                         | RC2IE        | TX2IE         | CTMUIE | CCP2IE  | CCP1IE  | _      |  |  |

| IPR3     | —         | _                         | RC2IP        | TX2IP         | CTMUIP | CCP2IP  | CCP1IP  |        |  |  |

| RCSTA1   | SPEN      | RX9                       | SREN         | CREN          | ADDEN  | FERR    | OERR    | RX9D   |  |  |

| TXREG1   | EUSART1 T | EUSART1 Transmit Register |              |               |        |         |         |        |  |  |

| TXSTA1   | CSRC      | TX9                       | TXEN         | SYNC          | SENDB  | BRGH    | TRMT    | TX9D   |  |  |

| BAUDCON1 | ABDOVF    | RCIDL                     | RXDTP        | TXCKP         | BRG16  | _       | WUE     | ABDEN  |  |  |

| SPBRGH1  | EUSART1 B | aud Rate Ge               | nerator Regi | ster High Byt | e      |         |         |        |  |  |

| SPBRG1   | EUSART1 B | aud Rate Ge               | nerator Regi | ster Low Byte | e      |         |         |        |  |  |

| RCSTA2   | SPEN      | RX9                       | SREN         | CREN          | ADDEN  | FERR    | OERR    | RX9D   |  |  |

| TXREG2   | EUSART2 T | ransmit Regis             | ster         |               |        |         |         |        |  |  |

| TXSTA2   | CSRC      | TX9                       | TXEN         | SYNC          | SENDB  | BRGH    | TRMT    | TX9D   |  |  |

| BAUDCON2 | ABDOVF    | RCIDL                     | RXDTP        | TXCKP         | BRG16  | _       | WUE     | ABDEN  |  |  |

| SPBRGH2  | EUSART2 B | aud Rate Ge               | nerator Regi | ster High Byt | e      |         |         |        |  |  |

| SPBRG2   | EUSART2 B | aud Rate Ge               | nerator Regi | ster Low Byte | Э      |         |         |        |  |  |

| PMD0     | CCP5MD    | CCP4MD                    | CCP3MD       | CCP2MD        | CCP1MD | UART2MD | UART1MD | SSPMD  |  |  |

| ODCON    | SSPOD     | CCP5OD                    | CCP4OD       | CCP3OD        | CCP2OD | CCP10D  | U2OD    | U10D   |  |  |

### TABLE 22-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

# 23.2 A/D Registers

23.2.1 A/D CONTROL REGISTERS

### REGISTER 23-1: ADCON0: A/D CONTROL REGISTER 0

| U-0                                                         | R/W-0                               | R/W-0                            | R/W-0           | R/W-0                                                                  | R/W-0                   | R/W-0             | R/W-0          |  |  |

|-------------------------------------------------------------|-------------------------------------|----------------------------------|-----------------|------------------------------------------------------------------------|-------------------------|-------------------|----------------|--|--|

|                                                             | CHS4                                | CHS3                             | CHS2            | CHS1                                                                   | CHS0                    | GO/DONE           | ADON           |  |  |

| bit 7                                                       |                                     |                                  |                 |                                                                        |                         |                   | bit 0          |  |  |

| Legend:                                                     |                                     |                                  |                 |                                                                        |                         |                   |                |  |  |

| R = Read                                                    | lable bit                           | W = Writable                     | bit             | U = Unimplen                                                           | nented bit, rea         | id as '0'         |                |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = |                                     |                                  |                 |                                                                        | x = Bit is unkno        | own               |                |  |  |

| bit 7                                                       | Unimpleme                           | nted: Read as '                  | ר,              |                                                                        |                         |                   |                |  |  |

| bit 6-2                                                     | -                                   | Analog Channel                   |                 |                                                                        |                         |                   |                |  |  |

| 511 0 2                                                     |                                     | annel 00 (AN0)                   |                 | 10000 <b>= (Re</b>                                                     | served)(2)              |                   |                |  |  |

|                                                             |                                     | annel 01 (AN1)                   |                 | 10000 = (Re)                                                           | eserved) <sup>(2)</sup> |                   |                |  |  |

|                                                             |                                     | annel 02 (AN2)                   |                 | 10010 = (Re                                                            |                         |                   |                |  |  |

|                                                             |                                     | annel 03 (AN3)                   |                 | 10011 <b>= (R</b> e                                                    |                         |                   |                |  |  |

|                                                             |                                     | annel 04 (AN4)                   |                 | 10100 <b>= (R</b> e                                                    |                         |                   |                |  |  |

|                                                             |                                     | annel 05 (AN5)                   |                 | 10101 <b>= (Re</b>                                                     |                         |                   |                |  |  |

|                                                             |                                     | annel 06 (AN6) <sup>(</sup>      |                 | $10110 = (Reserved)^{(2)}$                                             |                         |                   |                |  |  |

|                                                             |                                     | annel 07 (AN7) <sup>(</sup>      | 1,2)            | 10111 = (Reserved) <sup>(2)</sup><br>11000 = (Reserved) <sup>(2)</sup> |                         |                   |                |  |  |

|                                                             |                                     | annel 08 (AN8)                   |                 | 11000 = (Re)<br>11001 = (Re)                                           |                         |                   |                |  |  |

|                                                             |                                     | annel 09 (AN9)<br>annel 10 (AN10 | <b>`</b>        | 11001 = (Re)<br>11010 = (Re)                                           |                         |                   |                |  |  |

|                                                             | 01010 = Characteristics 01011 = (Re |                                  | )               | 11010 = (Re                                                            |                         |                   |                |  |  |

|                                                             | 01100 = (Re                         |                                  |                 |                                                                        | UX disconnec            | t)(3)             |                |  |  |

|                                                             | 01101 <b>= (Re</b>                  |                                  |                 |                                                                        |                         | perature diode)   |                |  |  |

|                                                             | 01110 <b>= (R</b> e                 |                                  |                 |                                                                        | annel 30 (VDD           |                   |                |  |  |

|                                                             | 01111 <b>= (R</b> e                 | eserved)(2)                      |                 | 11111 <b>= Ch</b>                                                      | annel 31 (1.02          | 24V band gap)     |                |  |  |

| bit 1                                                       | GO/DONE: A                          | VD Conversion                    | Status bit      |                                                                        |                         |                   |                |  |  |

|                                                             | 1 = A/D cyc                         | le is in progres                 | ss. Setting th  | is bit starts an                                                       | A/D convers             | ion cycle. The    | bit is cleared |  |  |

|                                                             |                                     | ically by hardwa                 |                 |                                                                        | s completed.            | -                 |                |  |  |

|                                                             | 0 = A/D con                         | version has con                  | npleted or is n | ot in progress                                                         |                         |                   |                |  |  |

| bit 0                                                       | ADON: A/D                           | On bit                           |                 |                                                                        |                         |                   |                |  |  |

|                                                             | 1 = A/D Con                         | verter is operati                | ng              |                                                                        |                         |                   |                |  |  |

|                                                             | 0 = A/D conv                        | version module i                 | s shut off and  | consuming no o                                                         | operating curr          | ent               |                |  |  |

| Note 1:                                                     | These channels                      | are not impleme                  | ented on 28-pi  | n devices.                                                             |                         |                   |                |  |  |

| 2:                                                          | Performing a cor                    | nversion on unin                 | nplemented ch   | nannels will retu                                                      | rn random va            | lues.             |                |  |  |

| 3:                                                          | Channel 28 turns                    |                                  |                 | allow for minimu                                                       | um capacitive           | loading of the A/ | D input, for   |  |  |

|                                                             | finer resolution C                  | CIMU time mea                    | surements.      |                                                                        |                         |                   |                |  |  |

| R/W-0        | U-0                                                                                                      | R/W-0                     | R/W-0         | R/W-0                    | R/W-0            | R/W-0           | R/W-0 |

|--------------|----------------------------------------------------------------------------------------------------------|---------------------------|---------------|--------------------------|------------------|-----------------|-------|

| ADFM         | _                                                                                                        | ACQT2                     | ACQT1         | ACQT0                    | ADCS2            | ADCS1           | ADCS0 |

| bit 7        |                                                                                                          |                           |               | ·                        |                  |                 | bit 0 |

|              |                                                                                                          |                           |               |                          |                  |                 |       |

| Legend:      |                                                                                                          |                           |               |                          |                  |                 |       |

| R = Readat   |                                                                                                          | W = Writable              | bit           | •                        | nented bit, read |                 |       |

| -n = Value a | at POR                                                                                                   | '1' = Bit is set          |               | '0' = Bit is clea        | ared             | x = Bit is unkr | lown  |

| bit 7        | ADFM: A/D R                                                                                              | esult Format S            | elect bit     |                          |                  |                 |       |

|              | 1 = Right justi<br>0 = Left justifie                                                                     |                           |               |                          |                  |                 |       |

| bit 6        | Unimplement                                                                                              | ted: Read as '            | )'            |                          |                  |                 |       |

| bit 5-3      | ACQT<2:0>:                                                                                               | A/D Acquisitior           | n Time Select | bits                     |                  |                 |       |

|              | 111 = 20 TAD<br>110 = 16 TAD<br>101 = 12 TAD<br>100 = 8 TAD<br>011 = 6 TAD<br>010 = 4 TAD<br>001 = 2 TAD |                           |               |                          |                  |                 |       |

|              | 000 = 0 TAD <sup>(1</sup>                                                                                |                           |               |                          |                  |                 |       |

| bit 2-0      | 111 = FRC (cl<br>110 = Fosc/6<br>101 = Fosc/1<br>100 = Fosc/4                                            | 6<br>ock derived fro<br>2 | m A/D RC osc  | sillator) <sup>(1)</sup> |                  |                 |       |

#### REGISTER 23-3: ADCON2: A/D CONTROL REGISTER 2

**Note 1:** If the A/D FRC clock source is selected, a delay of one TCY (instruction cycle) is added before the A/D clock starts. This allows the SLEEP instruction to be executed before starting a conversion.

| Mode 0     | R/C-0                                                                                                                           | R/W-0                                                                                                                                                                          | R/W-0                               | U-0           | R-0              | R/W-0           | R-0             | R-0     |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------|------------------|-----------------|-----------------|---------|--|--|

| Mode 0     | RXFUL <sup>(1)</sup>                                                                                                            | RXM1                                                                                                                                                                           | RXM0                                |               | RXRTRRO          | FILHIT2         | FILHIT1         | FILHIT0 |  |  |

|            |                                                                                                                                 |                                                                                                                                                                                |                                     |               |                  |                 |                 |         |  |  |

| Mode 1,2   | R/C-0                                                                                                                           | R/W-0                                                                                                                                                                          | R-0                                 | R-0           | R-0              | R-0             | R-0             | R-0     |  |  |

|            | RXFUL <sup>(1)</sup>                                                                                                            | RXM1                                                                                                                                                                           | RTRRO                               | FILHIT4       | FILHIT3          | FILHIT2         | FILHIT1         | FILHIT0 |  |  |

|            | bit 7                                                                                                                           |                                                                                                                                                                                |                                     |               |                  |                 |                 | bit (   |  |  |

| Legend:    |                                                                                                                                 |                                                                                                                                                                                | C = Clearabl                        | e bit         |                  |                 |                 |         |  |  |

| R = Reada  | able bit                                                                                                                        |                                                                                                                                                                                | W = Writable                        | e bit         | U = Unimple      | mented bit, r   | ead as '0'      |         |  |  |

| -n = Value | at POR                                                                                                                          |                                                                                                                                                                                | '1' = Bit is se                     | t             | '0' = Bit is cle | eared           | x = Bit is un   | known   |  |  |

| L:1 7      | RXFUL: Rece                                                                                                                     |                                                                                                                                                                                |                                     |               |                  |                 |                 |         |  |  |

| bit 7      |                                                                                                                                 |                                                                                                                                                                                |                                     |               |                  |                 |                 |         |  |  |

|            |                                                                                                                                 |                                                                                                                                                                                | is a received n<br>i to receive a r |               | е                |                 |                 |         |  |  |

| bit 6-5, 6 | Mode 0:                                                                                                                         |                                                                                                                                                                                |                                     |               |                  |                 |                 |         |  |  |

|            |                                                                                                                                 |                                                                                                                                                                                | er Mode bit 1 (                     |               |                  |                 |                 | t 5)    |  |  |

|            |                                                                                                                                 | 1 = Receive all messages (including those with errors); filter criteria is ignored<br>0 = Receive only valid messages with extended identifier; EXIDEN in RXFnSIDL must be '1' |                                     |               |                  |                 |                 |         |  |  |

|            |                                                                                                                                 |                                                                                                                                                                                | essages with                        |               |                  |                 |                 |         |  |  |

|            |                                                                                                                                 |                                                                                                                                                                                | sages as per                        |               |                  |                 |                 |         |  |  |

|            | <u>Mode 1, 2:</u>                                                                                                               |                                                                                                                                                                                |                                     |               |                  |                 |                 |         |  |  |

|            | <b>RXM1:</b> Receive Buffer Mode bit<br>1 = Receive all messages (including those with errors); acceptance filters are ignored  |                                                                                                                                                                                |                                     |               |                  |                 |                 |         |  |  |

|            |                                                                                                                                 |                                                                                                                                                                                | ages as per a                       |               |                  | e filters are l | gnorea          |         |  |  |

| bit 5      | Mode 0:                                                                                                                         |                                                                                                                                                                                |                                     |               |                  |                 |                 |         |  |  |

|            |                                                                                                                                 | Receive Buffe                                                                                                                                                                  | er Mode bit 0 (o                    | combines wi   | th RXM1 to fo    | orm RXM<1:0     | )> bits, see bi | t 6)    |  |  |

|            | Mode 1, 2:<br>PTPPO: Remote Transmission Request bit for Received Message (read only)                                           |                                                                                                                                                                                |                                     |               |                  |                 |                 |         |  |  |

|            | <b>RTRRO:</b> Remote Transmission Request bit for Received Message (read-only)<br>1 = A remote transmission request is received |                                                                                                                                                                                |                                     |               |                  |                 |                 |         |  |  |

|            | 1 = A remote transmission request is received<br>0 = A remote transmission request is not received                              |                                                                                                                                                                                |                                     |               |                  |                 |                 |         |  |  |

| bit 4      | Mode 0:                                                                                                                         |                                                                                                                                                                                |                                     |               |                  |                 |                 |         |  |  |

|            | FILHIT24: Fil                                                                                                                   | ter Hit bit 4                                                                                                                                                                  |                                     |               |                  |                 |                 |         |  |  |

|            | Mode 1, 2:<br>FILHIT<4:0>: Filter Hit bit 4                                                                                     |                                                                                                                                                                                |                                     |               |                  |                 |                 |         |  |  |

|            | This bit combines with other bits to form the filter acceptance bits<4:0>.                                                      |                                                                                                                                                                                |                                     |               |                  |                 |                 |         |  |  |

| bit 3      | Mode 0:                                                                                                                         |                                                                                                                                                                                |                                     |               |                  |                 |                 |         |  |  |

|            | RXRTRRO: Remote Transmission Request bit for Received Message (read-only)                                                       |                                                                                                                                                                                |                                     |               |                  |                 |                 |         |  |  |

|            |                                                                                                                                 |                                                                                                                                                                                | n request is rec<br>n request is no |               |                  |                 |                 |         |  |  |

|            | Mode 1, 2:                                                                                                                      |                                                                                                                                                                                |                                     |               |                  |                 |                 |         |  |  |

|            | FILHIT<4:0>:                                                                                                                    |                                                                                                                                                                                | -                                   |               |                  |                 |                 |         |  |  |

|            | This bit comb                                                                                                                   | ines with oth                                                                                                                                                                  | er bits to form                     | the filter ac | ceptance bits<   | :4:0>.          |                 |         |  |  |

| Note 1:    | This bit is set b<br>is read. As long                                                                                           |                                                                                                                                                                                |                                     |               |                  |                 |                 |         |  |  |

### REGISTER 27-14: RXB1CON: RECEIVE BUFFER 1 CONTROL REGISTER

#### REGISTER 27-28: BnEIDH: TX/RX BUFFER 'n' EXTENDED IDENTIFIER REGISTERS, HIGH BYTE IN RECEIVE MODE $[0 \le n \le 5, TXnEN (BSEL0<n>) = 0]^{(1)}$

| EID15         EID14         EID13         EID12         EID11         EID10         EID9         EID8           bit 7         bit 0 | R-x   | R-x   | R-x   | R-x   | R-x   | R-x   | R-x  | R-x   |

|-------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|------|-------|

| bit 7 bit 0                                                                                                                         | EID15 | EID14 | EID13 | EID12 | EID11 | EID10 | EID9 | EID8  |

|                                                                                                                                     | bit 7 |       |       |       |       |       |      | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 EID<15:8>: Extended Identifier bits

Note 1: These registers are available in Mode 1 and 2 only.

####

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID15 | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 EID<15:8>: Extended Identifier bits

**Note 1:** These registers are available in Mode 1 and 2 only.

###

| R-x   | R-x  | R-x  | R-x  | R-x  | R-x  | R-x  | R-x   |

|-------|------|------|------|------|------|------|-------|

| EID7  | EID6 | EID5 | EID4 | EID3 | EID2 | EID1 | EID0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

|       |      |      |      |      |      |      |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 EID<7:0>: Extended Identifier bits

Note 1: These registers are available in Mode 1 and 2 only.

| R/W-0                 | R/W-1                        | R/W-0                                            | R/W-1        | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |

|-----------------------|------------------------------|--------------------------------------------------|--------------|------------------|------------------|-----------------|--------|--|--|

| FIL3_1                | FIL3_0                       | FIL2_1                                           | FIL2_0       | FIL1_1           | FIL1_0           | FIL0_1          | FIL0_0 |  |  |

| bit 7                 |                              |                                                  |              |                  |                  |                 | bit (  |  |  |

|                       |                              |                                                  |              |                  |                  |                 |        |  |  |

| Legend:<br>R = Readab | la hit                       | W = Writable                                     | hit          |                  | monted bit read  |                 |        |  |  |

|                       |                              |                                                  |              | •                | mented bit, read |                 |        |  |  |

| -n = Value a          | IPUR                         | '1' = Bit is se                                  | l            | '0' = Bit is cle | areo             | x = Bit is unkr | IOWN   |  |  |

| bit 7-6               | FIL3 <1:0>:                  | Filter 3 Select                                  | bits 1 and 0 |                  |                  |                 |        |  |  |

|                       | 11 <b>= No mas</b>           |                                                  |              |                  |                  |                 |        |  |  |

|                       | 10 = Filter 1                | -                                                |              |                  |                  |                 |        |  |  |

|                       |                              | 01 = Acceptance Mask 1<br>00 = Acceptance Mask 0 |              |                  |                  |                 |        |  |  |

| bit 5 1               | •                            | Filter 2 Select                                  | hite 1 and 0 |                  |                  |                 |        |  |  |

| bit 5-4               | 11 = No mas                  |                                                  | Dits I and 0 |                  |                  |                 |        |  |  |

|                       | 10 = Filter 18               |                                                  |              |                  |                  |                 |        |  |  |

|                       | 01 = Accepta                 | ance Mask 1                                      |              |                  |                  |                 |        |  |  |

|                       | 00 = Accepta                 | ance Mask 0                                      |              |                  |                  |                 |        |  |  |

| bit 3-2               | FIL1_<1:0>:                  | Filter 1 Select                                  | bits 1 and 0 |                  |                  |                 |        |  |  |

|                       | 11 <b>= No mas</b>           |                                                  |              |                  |                  |                 |        |  |  |

|                       | 10 = Filter 1                |                                                  |              |                  |                  |                 |        |  |  |

|                       | 01 = Accepta<br>00 = Accepta |                                                  |              |                  |                  |                 |        |  |  |

| bit 1-0               | •                            | Filter 0 Select                                  | hite 1 and 0 |                  |                  |                 |        |  |  |

| DIL 1-0               | 11 = No mas                  |                                                  |              |                  |                  |                 |        |  |  |

|                       | 10 = Filter 1                |                                                  |              |                  |                  |                 |        |  |  |

|                       | 01 = Accepta                 | -                                                |              |                  |                  |                 |        |  |  |

|                       | 00 = Accepta                 |                                                  |              |                  |                  |                 |        |  |  |

# REGISTER 27-48: MSEL0: MASK SELECT REGISTER 0<sup>(1)</sup>

Note 1: This register is available in Mode 1 and 2 only.

|              |                                            | Branch if Z                                                                               | lero                                             |                                                 |                                   |  |  |  |

|--------------|--------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------|-----------------------------------|--|--|--|

| Synt         | ax:                                        | BZ n                                                                                      |                                                  |                                                 |                                   |  |  |  |

| Ope          | rands:                                     | -128 ≤ n ≤ 1                                                                              | $-128 \le n \le 127$                             |                                                 |                                   |  |  |  |

| Ope          | ration:                                    | if Zero bit is<br>(PC) + 2 + 2                                                            | ,                                                | ;                                               |                                   |  |  |  |

| Statu        | us Affected:                               | None                                                                                      |                                                  |                                                 |                                   |  |  |  |

| Enco         | oding:                                     | 1110                                                                                      | 0000                                             | nnnn                                            | nnnn                              |  |  |  |

| Description: |                                            | If the Zero I<br>will branch.                                                             | oit is '1',                                      | then the                                        | program                           |  |  |  |

|              |                                            | The 2's con<br>added to the<br>incrementer<br>instruction,<br>PC + 2 + 2r<br>two-cycle in | e PC. Sin<br>d to fetch<br>the new<br>n. This in | nce the P<br>n the nex<br>address<br>istruction | C will have<br>t<br>will be       |  |  |  |

| Word         | ds:                                        | 1                                                                                         |                                                  |                                                 |                                   |  |  |  |

| Cycl         | es:                                        | 1(2)                                                                                      |                                                  |                                                 |                                   |  |  |  |

|              | Sycle Activity:                            |                                                                                           |                                                  |                                                 |                                   |  |  |  |

|              | Q1                                         | Q2                                                                                        | Q3                                               | 3                                               | Q4                                |  |  |  |

|              | Decode                                     | Read literal                                                                              | Process<br>Data                                  |                                                 |                                   |  |  |  |

|              | Decode                                     | 'n'                                                                                       |                                                  |                                                 | Write to<br>PC                    |  |  |  |

|              | No                                         |                                                                                           |                                                  | a                                               |                                   |  |  |  |

|              | No                                         | 'n'                                                                                       | Data                                             | a                                               | PC                                |  |  |  |

| lf N         | No<br>operation<br>o Jump:                 | 'n'<br>No<br>operation                                                                    | Data<br>No<br>operat                             | a<br>ion c                                      | PC<br>No<br>operation             |  |  |  |

| If N         | No<br>operation<br>o Jump:<br>Q1           | 'n'<br>No<br>operation<br>Q2                                                              | Data<br>No<br>operat                             | ion c                                           | PC<br>No<br>operation<br>Q4       |  |  |  |

| lf Ne        | No<br>operation<br>o Jump:                 | 'n'<br>No<br>operation<br>Q2<br>Read literal                                              | Data<br>No<br>operat<br>Q3<br>Proce              | a<br>ion c<br>3<br>ess                          | PC<br>No<br>operation<br>Q4<br>No |  |  |  |

| lf No        | No<br>operation<br>o Jump:<br>Q1           | 'n'<br>No<br>operation<br>Q2                                                              | Data<br>No<br>operat                             | a<br>ion c<br>3<br>ess                          | PC<br>No<br>operation<br>Q4       |  |  |  |

|              | No<br>operation<br>o Jump:<br>Q1           | 'n'<br>No<br>operation<br>Q2<br>Read literal                                              | Data<br>No<br>operat<br>Q3<br>Proce<br>Data      | a<br>ion c<br>3<br>ess                          | PC<br>No<br>operation<br>Q4<br>No |  |  |  |

|              | No<br>operation<br>o Jump:<br>Q1<br>Decode | 'n'<br>No<br>operation<br>Q2<br>Read literal<br>'n'<br>HERE<br>tion<br>= adu              | Data<br>No<br>operat<br>Q3<br>Proce<br>Data      | a c                                             | PC<br>No<br>operation<br>Q4<br>No |  |  |  |

| Syntax:                                             | CALL k {,s}                                                                                                                                                  |                                                                           |                                                                       |                                                                   |  |  |  |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|

| Operands:                                           | $0 \le k \le 1048575$<br>s $\in$ [0,1]                                                                                                                       |                                                                           |                                                                       |                                                                   |  |  |  |

| Operation:                                          | $\begin{array}{l} (PC) + 4 \rightarrow \\ k \rightarrow PC < 20 \\ \text{if } s = 1 \\ (W) \rightarrow WS, \\ (STATUS) - \\ (BSR) \rightarrow B \end{array}$ | ):1>;<br>→ STATL                                                          | JSS,                                                                  |                                                                   |  |  |  |

| Status Affected:                                    | None                                                                                                                                                         |                                                                           |                                                                       |                                                                   |  |  |  |

| Encoding:<br>1st word (k<7:0>)<br>2nd word(k<19:8>) | 1110<br>1111                                                                                                                                                 | 110s<br>k <sub>19</sub> kkk                                               | k <sub>7</sub> kki<br>kkkk                                            | 0                                                                 |  |  |  |