Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | ECANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 35                                                                           |

| Program Memory Size        | 64KB (32K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 3.6K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 11x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-TQFP                                                                      |

| Supplier Device Package    | 44-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf46k80t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

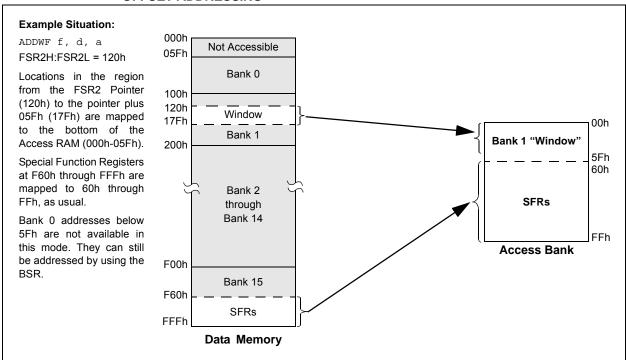

### 6.6.3 MAPPING THE ACCESS BANK IN INDEXED LITERAL OFFSET MODE

The use of Indexed Literal Offset Addressing mode effectively changes how the lower part of Access RAM (00h to 5Fh) is mapped. Rather than containing just the contents of the bottom part of Bank 0, this mode maps the contents from Bank 0 and a user-defined "window" that can be located anywhere in the data memory space.

The value of FSR2 establishes the lower boundary of the addresses mapped into the window, while the upper boundary is defined by FSR2 plus 95 (5Fh). Addresses in the Access RAM above 5Fh are mapped as previously described. (See **Section 6.3.2 "Access Bank"**.) An example of Access Bank remapping in this addressing mode is shown in Figure 6-10.

Remapping the Access Bank applies *only* to operations using the Indexed Literal Offset mode. Operations that use the BSR (Access RAM bit = 1) will continue to use Direct Addressing as before. Any Indirect or Indexed Addressing operation that explicitly uses any of the indirect file operands (including FSR2) will continue to operate as standard Indirect Addressing. Any instruction that uses the Access Bank, but includes a register address of greater than 05Fh, will use Direct Addressing and the normal Access Bank map.

## 6.6.4 BSR IN INDEXED LITERAL OFFSET MODE

Although the Access Bank is remapped when the extended instruction set is enabled, the operation of the BSR remains unchanged. Direct Addressing, using the BSR to select the data memory bank, operates in the same manner as previously described.

FIGURE 6-10: REMAPPING THE ACCESS BANK WITH INDEXED LITERAL OFFSET ADDRESSING

NOTES:

TABLE 8-1: REGISTERS ASSOCIATED WITH DATA EEPROM MEMORY

| Name   | Bit 7    | Bit 6           | Bit 5          | Bit 4          | Bit 3 | Bit 2  | Bit 1  | Bit 0  |

|--------|----------|-----------------|----------------|----------------|-------|--------|--------|--------|

| INTCON | GIE/GIEH | PEIE/GIEL       | TMR0IE         | INT0IE         | RBIE  | TMR0IF | INT0IF | RBIF   |

| EEADRH | EEPROM A | ddress Registe  | er High Byte   |                |       |        |        |        |

| EEADR  | EEPROM A | ddress Regist   | ter Low Byte   |                |       |        |        |        |

| EEDATA | EEPROM D | ata Register    |                |                |       |        |        |        |

| EECON2 | EEPROM C | Control Registe | er 2 (not a ph | nysical regist | ter)  |        |        |        |

| EECON1 | EEPGD    | CFGS            | _              | FREE           | WRERR | WREN   | WR     | RD     |

| IPR4   | TMR4IP   | EEIP            | CMP2IP         | CMP1IP         | _     | CCP5IP | CCP4IP | CCP3IP |

| PIR4   | TMR4IF   | EEIF            | CMP2IF         | CMP1IF         | _     | CCP5IF | CCP4IF | CCP3IF |

| PIE4   | TMR4IE   | EEIE            | CMP2IE         | CMP1IE         | _     | CCP5IE | CCP4IE | CCP3IE |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

#### 12.0 DATA SIGNAL MODULATOR

**Note:** The Data Signal Modulator is only available on 64-pin devices (PIC18F6XK80).

The Data Signal Modulator (DSM) is a peripheral which allows the user to mix a data stream, also known as a modulator signal, with a carrier signal to produce a modulated output.

Both the carrier and the modulator signals are supplied to the DSM module, either internally from the output of a peripheral, or externally through an input pin.

The modulated output signal is generated by performing a logical "AND" operation of both the carrier and modulator signals and then it is provided to the MDOUT pin.

The carrier signal is comprised of two distinct and separate signals: a carrier high (CARH) signal and a carrier low (CARL) signal. During the time in which the modulator (MOD) signal is in a logic high state, the DSM mixes the carrier high signal with the modulator signal. When the modulator signal is in a logic low state, the DSM mixes the carrier low signal with the modulator signal.

Using this method, the DSM can generate the following types of key modulation schemes:

- Frequency-Shift Keying (FSK)

- · Phase-Shift Keying (PSK)

- On-Off Keying (OOK)

Additionally, the following features are provided within the DSM module:

- Carrier Synchronization

- · Carrier Source Polarity Select

- · Carrier Source Pin Disable

- Programmable Modulator Data

- · Modulator Source Pin Disable

- · Modulated Output Polarity Select

- · Slew Rate Control

Figure 12-1 shows a simplified block diagram of the Data Signal Modulator peripheral.

#### REGISTER 12-3: MDCARH: MODULATION HIGH CARRIER CONTROL REGISTER

| R/W-0       | R/W-x   | R/W-x    | U-0 | R/W-x                | R/W-x                | R/W-x                | R/W-x                |

|-------------|---------|----------|-----|----------------------|----------------------|----------------------|----------------------|

| MDCHODIS    | MDCHPOL | MDCHSYNC | _   | MDCH3 <sup>(1)</sup> | MDCH2 <sup>(1)</sup> | MDCH1 <sup>(1)</sup> | MDCH0 <sup>(1)</sup> |

| bit 7 bit 0 |         |          |     |                      |                      |                      |                      |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 7 MDCHODIS: Modulator High Carrier Output Disable bit 1 = Output signal driving the peripheral output pin (selected by MDCH<3:0>) is disabled 0 = Output signal driving the peripheral output pin (selected by MDCH<3:0>) is enabled MDCHPOL: Modulator High Carrier Polarity Select bit bit 6 1 = Selected high carrier signal is inverted 0 = Selected high carrier signal is not inverted MDCHSYNC: Modulator High Carrier Synchronization Enable bit bit 5 1 = Modulator waits for a falling edge on the high time carrier signal before allowing a switch to the low time carrier 0 = Modulator output is not synchronized to the high time carrier signal<sup>(1)</sup> bit 4 Unimplemented: Read as '0' MDCH<3:0> Modulator Data High Carrier Selection bits(1) bit 3-0 1111-1001 = Reserved 1000 = CCP5 output (PWM Output mode only) 0111 = CCP4 output (PWM Output mode only) 0110 = CCP3 output (PWM Output mode only) 0101 = CCP2 output (PWM Output mode only) 0100 = ECCP1 output (PWM Output mode only) 0011 = Reference clock module signal 0010 = MDCIN2 port pin 0001 = MDCIN1 port pin

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

0000 = Vss

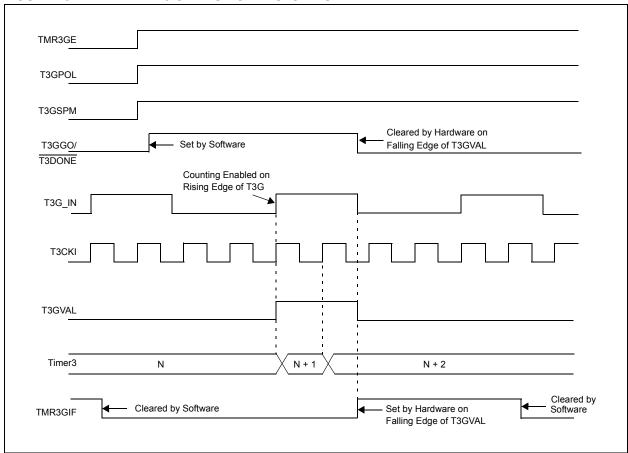

## 16.5.4 TIMER3 GATE SINGLE PULSE MODE

When Timer3 Gate Single Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer3 Gate Single Pulse mode is first enabled by setting the T3GSPM bit (T3GCON<4>). Next, the T3GGO/T3DONE bit (T3GCON<3>) must be set.

The Timer3 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T3GGO/T3DONE bit will automatically be cleared. No

other gate events <u>will be allowed to increment Timer3</u> until the  $T3GGO/\overline{T3DONE}$  bit is once again set in software.

Clearing the T3GSPM bit will also clear the T3GGO/T3DONE bit. (For timing details, see Figure 16-4.)

Simultaneously enabling the Toggle mode and the Single Pulse mode will permit both sections to work together. This allows the cycle times on the Timer3 gate source to be measured. (For timing details, see Figure 16-5.)

FIGURE 16-4: TIMER3 GATE SINGLE PULSE MODE

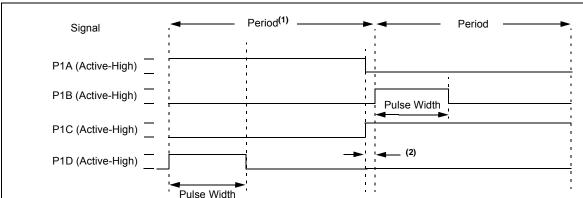

## 20.4.2.1 Direction Change in Full-Bridge Mode

In the Full-Bridge mode, the P1M1 bit in the CCP1CON register allows users to control the forward/reverse direction. When the application firmware changes this direction control bit, the module will change to the new direction on the next PWM cycle.

A direction change is initiated in software by changing the P1M1 bit of the CCP1CON register. The following sequence occurs prior to the end of the current PWM period:

- The modulated outputs (P1B and P1D) are placed in their inactive state.

- The associated unmodulated outputs (P1A and P1C) are switched to drive in the opposite direction.

- PWM modulation resumes at the beginning of the next period.

For an illustration of this sequence, see Figure 20-10.

The Full-Bridge mode does not provide a dead-band delay. As one output is modulated at a time, a dead-band delay is generally not required. There is a situation where a dead-band delay is required. This situation occurs when both of the following conditions are true:

- The direction of the PWM output changes when the duty cycle of the output is at or near 100%.

- The turn-off time of the power switch, including the power device and driver circuit, is greater than the turn-on time.

Figure 20-11 shows an example of the PWM direction changing from forward to reverse, at a near 100% duty cycle. In this example, at time, t1, the P1A and P1D outputs become inactive, while the P1C output becomes active. Since the turn-off time of the power devices is longer than the turn-on time, a shoot-through current will flow through power devices, QC and QD (see Figure 20-8), for the duration of 't'. The same phenomenon will occur to power devices, QA and QB, for PWM direction change from reverse to forward.

If changing PWM direction at high duty cycle is required for an application, two possible solutions for eliminating the shoot-through current are:

- Reduce PWM duty cycle for one PWM period before changing directions.

- Use switch drivers that can drive the switches off faster than they can drive them on.

Other options to prevent shoot-through current may exist.

- Note 1: The direction bit, P1M1 of the CCP1CON register, is written any time during the PWM cycle.

- 2: When changing directions, the P1A and P1C signals switch before the end of the current PWM cycle. The modulated P1B and P1D signals are inactive at this time. The length of this time is: (1/Fosc) TMR2 Prescale Value.

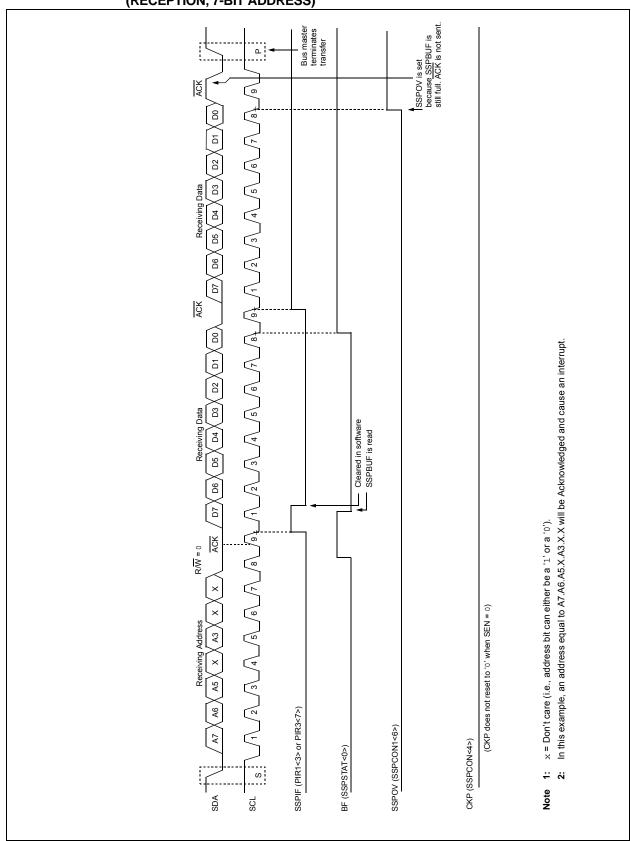

FIGURE 21-9:  $I^2C^{TM}$  SLAVE MODE TIMING WITH SEN = 0 AND ADMSK<5:1> = 01011 (RECEPTION, 7-BIT ADDRESS)

#### REGISTER 23-3: ADCON2: A/D CONTROL REGISTER 2

| R/W-0       | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------------|-----|-------|-------|-------|-------|-------|-------|--|

| ADFM        | _   | ACQT2 | ACQT1 | ACQT0 | ADCS2 | ADCS1 | ADCS0 |  |

| bit 7 bit 0 |     |       |       |       |       |       |       |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified

0 = Left justified

bit 6 **Unimplemented:** Read as '0'

bit 5-3 ACQT<2:0>: A/D Acquisition Time Select bits

111 **= 20 T**AD

110 **= 16 T**AD

101 = **12** TAD

100 = 8 TAD

011 = 6 TAD

010 = 4 TAD

001 = 2 TAD

$000 = 0 \text{ TAD}^{(1)}$

bit 2-0 ADCS<2:0>: A/D Conversion Clock Select bits

111 = FRC (clock derived from A/D RC oscillator)<sup>(1)</sup>

110 = Fosc/64

101 = Fosc/16

100 = Fosc/4

011 = FRC (clock derived from A/D RC oscillator)<sup>(1)</sup>

010 = Fosc/32

001 = Fosc/8

000 = Fosc/2

**Note 1:** If the A/D FRC clock source is selected, a delay of one Tcy (instruction cycle) is added before the A/D clock starts. This allows the SLEEP instruction to be executed before starting a conversion.

# 26.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

The PIC18F66K80 family of devices has a High/Low-Voltage Detect module (HLVD). This is a programmable circuit that sets both a device voltage trip point and the direction of change from that point. If the device experiences an excursion past the trip point in that direction, an interrupt flag is set. If the interrupt is enabled, the program execution branches to the interrupt vector address and the software responds to the interrupt.

Legend:

R = Readable bit

The High/Low-Voltage Detect Control register (Register 26-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

The module's block diagram is shown in Figure 26-1.

#### REGISTER 26-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

W = Writable bit

| R/W-0       | R-0   | R-0   | R/W-0  | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |  |

|-------------|-------|-------|--------|-----------------------|-----------------------|-----------------------|-----------------------|--|

| VDIRMAG     | BGVST | IRVST | HLVDEN | HLVDL3 <sup>(1)</sup> | HLVDL2 <sup>(1)</sup> | HLVDL1 <sup>(1)</sup> | HLVDL0 <sup>(1)</sup> |  |

| bit 7 bit 0 |       |       |        |                       |                       |                       |                       |  |

U = Unimplemented bit, read as '0'

| -n = Value a | at POR          | '1' = Bit is set                                           | '0' = Bit is cleared                                                  | x = Bit is unknown                                                       |

|--------------|-----------------|------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------|

|              |                 |                                                            |                                                                       |                                                                          |

| bit 7        | VDIRMA          | G: Voltage Direction Magni                                 | tude Select bit                                                       |                                                                          |

|              |                 | •                                                          | als or exceeds trip point (HLVD<br>als or falls below trip point (HLV | •                                                                        |

| bit 6        | BGVST:          | Band Gap Reference Volta                                   | ges Stable Status Flag bit                                            |                                                                          |

|              |                 | nal band gap voltage refere<br>nal band gap voltage refere |                                                                       |                                                                          |

| bit 5        | IRVST: I        | nternal Reference Voltage S                                | Stable Flag bit                                                       |                                                                          |

|              | 0 = India       | •                                                          | ct logic will not generate the inte                                   | flag at the specified voltage range errupt flag at the specified voltage |

| bit 4        | HLVDEN          | I: High/Low-Voltage Detect                                 | Power Enable bit                                                      |                                                                          |

|              | 1 = HLV         | D enabled                                                  |                                                                       |                                                                          |

|              | 0 = HLV         | D disabled                                                 |                                                                       |                                                                          |

| bit 3-0      | HLVDL<          | 3:0>: Voltage Detection Lin                                | nit bits <sup>(1)</sup>                                               |                                                                          |

|              | 1111 <b>= E</b> | External analog input is use                               | d (input comes from the HLVDI                                         | N pin)                                                                   |

|              | 1110 <b>= N</b> | Maximum setting                                            |                                                                       |                                                                          |

|              | •               |                                                            |                                                                       |                                                                          |

|              | •               |                                                            |                                                                       |                                                                          |

|              | 0000 = <b>N</b> | Minimum setting                                            |                                                                       |                                                                          |

| Note 1. F    | or the electri  | ical appoifications, and Dars                              | motor D420 in Section 24.0 "I                                         | Electrical Characteristics"                                              |

Note 1: For the electrical specifications, see Parameter D420 in Section 31.0 "Electrical Characteristics".

#### REGISTER 27-48: MSEL0: MASK SELECT REGISTER 0<sup>(1)</sup>

| R/W-0  | R/W-1  | R/W-0  | R/W-1  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FIL3_1 | FIL3_0 | FIL2_1 | FIL2_0 | FIL1_1 | FIL1_0 | FIL0_1 | FIL0_0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-6 FIL3\_<1:0>: Filter 3 Select bits 1 and 0

11 **= No mask**

10 = Filter 15

01 = Acceptance Mask 1

00 = Acceptance Mask 0

bit 5-4 FIL2\_<1:0>: Filter 2 Select bits 1 and 0

11 = No mask

10 = Filter 15

01 = Acceptance Mask 1

00 = Acceptance Mask 0

bit 3-2 FIL1\_<1:0>: Filter 1 Select bits 1 and 0

11 = No mask

10 = Filter 15

01 = Acceptance Mask 1

00 = Acceptance Mask 0

bit 1-0 FIL0\_<1:0>: Filter 0 Select bits 1 and 0

11 **= No mask**

10 = Filter 15

01 = Acceptance Mask 1

00 = Acceptance Mask 0

Note 1: This register is available in Mode 1 and 2 only.

TABLE 29-2: PIC18F66K80 FAMILY INSTRUCTION SET (CONTINUED)

| Mnemo    | onic,   | Decerinties                   | Cycles     | 16-E    | Bit Instr | uction \ | Vord  | Status                 | Notes |

|----------|---------|-------------------------------|------------|---------|-----------|----------|-------|------------------------|-------|

| Opera    | nds     | Description                   | Cycles     | MSb LSb |           | Affected | Notes |                        |       |

| BIT-ORIE | NTED O  | PERATIONS                     |            |         |           |          |       |                        |       |

| BCF      | f, b, a | Bit Clear f                   | 1          | 1001    | bbba      | ffff     | ffff  | None                   | 1, 2  |

| BSF      | f, b, a | Bit Set f                     | 1          | 1000    | bbba      | ffff     | ffff  | None                   | 1, 2  |

| BTFSC    | f, b, a | Bit Test f, Skip if Clear     | 1 (2 or 3) | 1011    | bbba      | ffff     | ffff  | None                   | 3, 4  |

| BTFSS    | f, b, a | Bit Test f, Skip if Set       | 1 (2 or 3) | 1010    | bbba      | ffff     |       | None                   | 3, 4  |

| BTG      | f, b, a | Bit Toggle f                  | 1          | 0111    | bbba      | ffff     | ffff  | None                   | 1, 2  |

| CONTROL  | OPER    | ATIONS                        |            | •       |           |          |       |                        |       |

| ВС       | n       | Branch if Carry               | 1 (2)      | 1110    | 0010      | nnnn     | nnnn  | None                   |       |

| BN       | n       | Branch if Negative            | 1 (2)      | 1110    | 0110      | nnnn     | nnnn  | None                   |       |

| BNC      | n       | Branch if Not Carry           | 1 (2)      | 1110    | 0011      | nnnn     | nnnn  | None                   |       |

| BNN      | n       | Branch if Not Negative        | 1 (2)      | 1110    | 0111      | nnnn     | nnnn  | None                   |       |

| BNOV     | n       | Branch if Not Overflow        | 1 (2)      | 1110    | 0101      | nnnn     | nnnn  | None                   |       |

| BNZ      | n       | Branch if Not Zero            | 1 (2)      | 1110    | 0001      | nnnn     | nnnn  | None                   |       |

| BOV      | n       | Branch if Overflow            | 1 (2)      | 1110    | 0100      | nnnn     | nnnn  | None                   |       |

| BRA      | n       | Branch Unconditionally        | 2          | 1101    | 0nnn      | nnnn     | nnnn  |                        |       |

| BZ       | n       | Branch if Zero                | 1 (2)      | 1110    | 0000      | nnnn     | nnnn  | None                   |       |

| CALL     | n, s    | Call Subroutine 1st word      | 2          | 1110    | 110s      | kkkk     | kkkk  | None                   |       |

|          |         | 2nd word                      |            | 1111    | kkkk      | kkkk     | kkkk  |                        |       |

| CLRWDT   | _       | Clear Watchdog Timer          | 1          | 0000    | 0000      | 0000     | 0100  | TO, PD                 |       |

| DAW      | _       | Decimal Adjust WREG           | 1          | 0000    | 0000      | 0000     | 0111  | С                      |       |

| GOTO     | n       | Go to Address 1st word        | 2          | 1110    | 1111      | kkkk     | kkkk  | None                   |       |

|          |         | 2nd word                      |            | 1111    | kkkk      | kkkk     | kkkk  |                        |       |

| NOP      | _       | No Operation                  | 1          | 0000    | 0000      | 0000     |       | None                   |       |

| NOP      | _       | No Operation                  | 1          |         | XXXX      | XXXX     |       | None                   | 4     |

| POP      | _       | Pop Top of Return Stack (TOS) | 1          | 0000    | 0000      | 0000     |       | None                   |       |

| PUSH     | _       |                               | 1          | 0000    | 0000      | 0000     | 0101  | None                   |       |

| RCALL    | n       | Relative Call                 | 2          | 1101    | 1nnn      | nnnn     |       | None                   |       |

| RESET    |         | Software Device Reset         | 1          | 0000    | 0000      | 1111     | 1111  | All                    |       |

| RETFIE   | S       | Return from Interrupt Enable  | 2          | 0000    | 0000      | 0001     | 000s  | GIE/GIEH,<br>PEIE/GIEL |       |

| RETLW    | k       | Return with Literal in WREG   | 2          | 0000    | 1100      | kkkk     | kkkk  | None                   |       |

| RETURN   | S       | Return from Subroutine        | 2          | 0000    | 0000      | 0001     | 001s  | None                   |       |

| SLEEP    | _       | Go into Standby mode          | 1          | 0000    | 0000      | 0000     | 0011  | TO, PD                 |       |

- Note 1: When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as an input and is driven low by an external device, the data will be written back with a '0'.

- 2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

- **3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

- **4:** Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

**BNC Branch if Not Carry** Syntax: BNC n Operands:  $\text{-}128 \leq n \leq 127$ if Carry bit is '0', Operation:  $(PC) + 2 + 2n \rightarrow PC$ Status Affected: None Encoding: 1110 0011 nnnn nnnn Description: If the Carry bit is '0', then the program will branch.

> The 2's complement number, '2n', is added to the PC. Since the PC will have

incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then a

two-cycle instruction.

Words: Cycles: 1(2)

Q Cycle Activity: If Jump:

| Q1        | Q2           | Q3        | Q4        |

|-----------|--------------|-----------|-----------|

| Decode    | Read literal | Process   | Write to  |

|           | ʻn'          | Data      | PC        |

| No        | No           | No        | No        |

| operation | operation    | operation | operation |

If No Jump:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read literal | Process | No        |

|        | ʻn'          | Data    | operation |

Example: HERE BNC Jump

Before Instruction

PC address (HERE)

After Instruction

If Carry PC

address (Jump)

If Carry PC

address (HERE + 2)

**BNN Branch if Not Negative**

Syntax: BNN n Operands:  $\text{-}128 \leq n \leq 127$ if Negative bit is '0', Operation:

$(PC) + 2 + 2n \rightarrow PC$

Status Affected: None

Encoding: 1110 0111 nnnn nnnn

Description: If the Negative bit is '0', then the

program will branch.

The 2's complement number, '2n', is added to the PC. Since the PC will have incremented to fetch the next

instruction, the new address will be PC + 2 + 2n. This instruction is then a

two-cycle instruction.

Words:

Cycles: 1(2)

Q Cycle Activity:

If Jump:

| Q1        | Q2           | Q3        | Q4        |

|-----------|--------------|-----------|-----------|

| Decode    | Read literal | Process   | Write to  |

|           | 'n'          | Data      | PC        |

| No        | No           | No        | No        |

| operation | operation    | operation | operation |

If No Jump:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read literal | Process | No        |

|        | ʻn'          | Data    | operation |

Example: HERE BNN Jump

Before Instruction

PC address (HERE)

After Instruction

If Negative PC

address (Jump)

If Negative PC

address (HERE + 2)

## 31.2 DC Characteristics: Power-Down and Supply Current PIC18F66K80 Family (Industrial/Extended) (Continued)

| PIC18F66K80 Family<br>(Industrial/Extended) |                      |                        | Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |       |        |                                                          |                                                 |  |  |

|---------------------------------------------|----------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|----------------------------------------------------------|-------------------------------------------------|--|--|

| Param<br>No.                                | Device               | Тур                    | Max                                                                                                                                                                                                                                 | Units |        | Conditions                                               |                                                 |  |  |

|                                             | Supply Current (IDD) | Cont. <sup>(2,3)</sup> | •                                                                                                                                                                                                                                   |       |        |                                                          |                                                 |  |  |

|                                             | PIC18LFXXK80         | 330                    | 480                                                                                                                                                                                                                                 | μА    | -40°C  |                                                          |                                                 |  |  |

|                                             |                      | 330                    | 480                                                                                                                                                                                                                                 | μА    | +25°C  |                                                          |                                                 |  |  |

|                                             |                      | 330                    | 480                                                                                                                                                                                                                                 | μА    | +60°C  | V <sub>DD</sub> = 1.8V <sup>(4)</sup> Regulator Disabled |                                                 |  |  |

|                                             |                      | 340                    | 500                                                                                                                                                                                                                                 | μА    | +85°C  |                                                          |                                                 |  |  |

|                                             |                      | 350                    | 540                                                                                                                                                                                                                                 | μА    | +125°C |                                                          |                                                 |  |  |

|                                             | PIC18LFXXK80         | 522                    | 720                                                                                                                                                                                                                                 | μА    | -40°C  |                                                          |                                                 |  |  |

|                                             |                      | 522                    | 720                                                                                                                                                                                                                                 | μА    | +25°C  |                                                          |                                                 |  |  |

|                                             |                      | 522                    | 720                                                                                                                                                                                                                                 | μА    | +60°C  | V <sub>DD</sub> = 3.3V <sup>(4)</sup> Regulator Disabled | Fosc = 4 MHz (RC_IDLE mode, Internal HF-INTOSC) |  |  |

|                                             |                      | 540                    | 740                                                                                                                                                                                                                                 | μА    | +85°C  | Tregulator Bloablea                                      |                                                 |  |  |

|                                             |                      | 550                    | 780                                                                                                                                                                                                                                 | μА    | +125°C |                                                          |                                                 |  |  |

|                                             | PIC18FXXK80          | 540                    | 760                                                                                                                                                                                                                                 | μА    | -40°C  |                                                          |                                                 |  |  |

|                                             |                      | 540                    | 760                                                                                                                                                                                                                                 | μА    | +25°C  |                                                          | ,                                               |  |  |

|                                             |                      | 540                    | 760                                                                                                                                                                                                                                 | μА    | +60°C  | V <sub>DD</sub> = 3.3V <sup>(5)</sup> Regulator Enabled  |                                                 |  |  |

|                                             |                      | 560                    | 780                                                                                                                                                                                                                                 | μА    | +85°C  | rtogalator Enabled                                       |                                                 |  |  |

|                                             |                      | 580                    | 810                                                                                                                                                                                                                                 | μА    | +125°C |                                                          |                                                 |  |  |

|                                             | PIC18FXXK80          | 600                    | 1250                                                                                                                                                                                                                                | μА    | -40°C  |                                                          |                                                 |  |  |

|                                             |                      | 600                    | 1250                                                                                                                                                                                                                                | μА    | +25°C  | (5)                                                      |                                                 |  |  |

|                                             |                      | 600                    | 1250                                                                                                                                                                                                                                | μА    | +60°C  | V <sub>DD</sub> = 5V <sup>(5)</sup> Regulator Enabled    |                                                 |  |  |

|                                             |                      | 610                    | 1300                                                                                                                                                                                                                                | μА    | +85°C  | - regulator Enabled                                      |                                                 |  |  |

|                                             |                      | 620                    | 1340                                                                                                                                                                                                                                | μА    | +125°C |                                                          |                                                 |  |  |

**Legend:** Shading of rows is to assist in readability of the table.

Note 1: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in a high-impedance state and tied to VDD or Vss, and all features that add delta current are disabled (such as WDT, SOSC oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT enabled/disabled as specified.

- 3: Standard, low-cost 32 kHz crystals have an operating temperature range of -10°C to +70°C. Extended temperature crystals are available at a much higher cost.

- 4: For LF devices,  $\overline{RETEN}$  (CONFIG1L<0>) = 1.

- 5: For F devices, SRETEN (WDTCON<4>) = 1 and  $\overline{\text{RETEN}}$  (CONFIG1L<0>) = 0.

# 31.2 DC Characteristics: Power-Down and Supply Current PIC18F66K80 Family (Industrial/Extended) (Continued)

| PIC18F66K80 Family<br>(Industrial/Extended) |                                                            |     | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |       |                 |                                              |                        |  |  |  |

|---------------------------------------------|------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------|----------------------------------------------|------------------------|--|--|--|

| Param<br>No.                                | Device                                                     | Тур | Max                                                                                                                                                                                         | Units |                 | Conditions                                   |                        |  |  |  |

|                                             | Module Differential Currents (ΔΙWDT, ΔΙΒΟR, ΔΙΗLVD, ΔΙΑDC) |     |                                                                                                                                                                                             |       |                 |                                              |                        |  |  |  |

| D022                                        | Watchdog Timer                                             |     |                                                                                                                                                                                             |       |                 |                                              |                        |  |  |  |

| (∆lwdt)                                     | PIC18LFXXK80                                               | 0.4 | 2                                                                                                                                                                                           | μА    | -40°C to +125°C | V <sub>DD</sub> = 1.8V<br>Regulator Disabled |                        |  |  |  |

|                                             | PIC18LFXXK80                                               | 0.6 | 3                                                                                                                                                                                           | μА    | -40°C to +125°C | V <sub>DD</sub> = 3.3V<br>Regulator Disabled |                        |  |  |  |

|                                             | PIC18FXXK80                                                | 0.6 | 3                                                                                                                                                                                           | μА    | -40°C to +125°C | V <sub>DD</sub> = 3.3V<br>Regulator Enabled  |                        |  |  |  |

|                                             | PIC18FXXK80                                                | 0.8 | 4                                                                                                                                                                                           | μА    | -40°C to +125°C | V <sub>DD</sub> = 5.5V<br>Regulator Enabled  |                        |  |  |  |

| D022A                                       | Brown-out Reset                                            |     |                                                                                                                                                                                             |       |                 |                                              |                        |  |  |  |

| (ΔIBOR)                                     | PIC18LFXXK80                                               | 4.6 | 20                                                                                                                                                                                          | μА    | -40°C to +125°C | V <sub>DD</sub> = 1.8V<br>Regulator Disabled |                        |  |  |  |

|                                             | PIC18FXXK80                                                | 4.6 | 20                                                                                                                                                                                          | μА    | -40°C to +125°C | V <sub>DD</sub> = 3.3V<br>Regulator Enabled  | High-Power BOR         |  |  |  |

|                                             | PIC18FXXK80                                                | 4.6 | 20                                                                                                                                                                                          | μА    | -40°C to +125°C | V <sub>DD</sub> = 5.5V<br>Regulator Enabled  |                        |  |  |  |

| D022B                                       | High/Low-Voltage Detect                                    |     |                                                                                                                                                                                             |       |                 |                                              |                        |  |  |  |

| ∆IHLVD                                      | PIC18LFXXK80                                               | 3.8 | 10                                                                                                                                                                                          | μА    | -40°C to +125°C | V <sub>DD</sub> = 1.8V<br>Regulator Disabled |                        |  |  |  |

|                                             | PIC18LFXXK80                                               | 4.5 | 12                                                                                                                                                                                          | μА    | -40°C to +125°C | V <sub>DD</sub> = 3.3V<br>Regulator Disabled |                        |  |  |  |

|                                             | PIC18FXXK80                                                | 3.8 | 12                                                                                                                                                                                          | μА    | -40°C to +125°C | V <sub>DD</sub> = 3.3V<br>Regulator Enabled  |                        |  |  |  |

|                                             | PIC18FXXK80                                                | 4.9 | 13                                                                                                                                                                                          | μА    | -40°C to +125°C | V <sub>DD</sub> = 5.5V<br>Regulator Enabled  |                        |  |  |  |

| D026<br>∆IADC                               | A/D Converter                                              |     |                                                                                                                                                                                             |       |                 |                                              |                        |  |  |  |

|                                             | PIC18LFXXK80                                               | 0.4 | 1.5                                                                                                                                                                                         |       | -40°C to +125°C | V <sub>DD</sub> = 1.8V<br>Regulator Disabled |                        |  |  |  |

|                                             | PIC18LFXXK80                                               | 0.5 | 2                                                                                                                                                                                           | μА    | -40°C to +125°C | V <sub>DD</sub> = 3.3V<br>Regulator Disabled | A/D on not accuration  |  |  |  |

|                                             | PIC18FXXK80                                                | 0.5 | 3                                                                                                                                                                                           | μА    | -40°C to +125°C | V <sub>DD</sub> = 3.3V<br>Regulator Enabled  | A/D on, not converting |  |  |  |

|                                             | PIC18FXXK80                                                | 1   | 3                                                                                                                                                                                           | μА    | -40°C to +125°C | V <sub>DD</sub> = 5.5V<br>Regulator Enabled  |                        |  |  |  |

**Legend:** Shading of rows is to assist in readability of the table.

Note 1: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in a high-impedance state and tied to VDD or Vss, and all features that add delta current are disabled (such as WDT, SOSC oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

- 3: Standard, low-cost 32 kHz crystals have an operating temperature range of -10°C to +70°C. Extended temperature crystals are available at a much higher cost.

- 4: For LF devices,  $\overline{RETEN}$  (CONFIG1L<0>) = 1.

- 5: For F devices, SRETEN (WDTCON<4>) = 1 and  $\overline{\text{RETEN}}$  (CONFIG1L<0>) = 0.

#### 28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    |      | MILLIMETERS |       |  |  |

|--------------------------|----------|------|-------------|-------|--|--|

| Dimension                | n Limits | MIN  | NOM         | MAX   |  |  |

| Number of Pins           | N        |      | 28          |       |  |  |

| Pitch                    | е        |      | 0.65 BSC    |       |  |  |

| Overall Height           | Α        | _    | _           | 2.00  |  |  |

| Molded Package Thickness | A2       | 1.65 | 1.75        | 1.85  |  |  |

| Standoff                 | A1       | 0.05 | _           | _     |  |  |

| Overall Width            | Е        | 7.40 | 7.80        | 8.20  |  |  |

| Molded Package Width     | E1       | 5.00 | 5.30        | 5.60  |  |  |

| Overall Length           | D        | 9.90 | 10.20       | 10.50 |  |  |

| Foot Length              | L        | 0.55 | 0.75        | 0.95  |  |  |

| Footprint                | L1       |      | 1.25 REF    |       |  |  |

| Lead Thickness           | С        | 0.09 | -           | 0.25  |  |  |

| Foot Angle               | ф        | 0°   | 4°          | 8°    |  |  |

| Lead Width               | b        | 0.22 | _           | 0.38  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- ${\tt BSC: Basic \ Dimension. \ Theoretically \ exact \ value \ shown \ without \ tolerances.}$

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

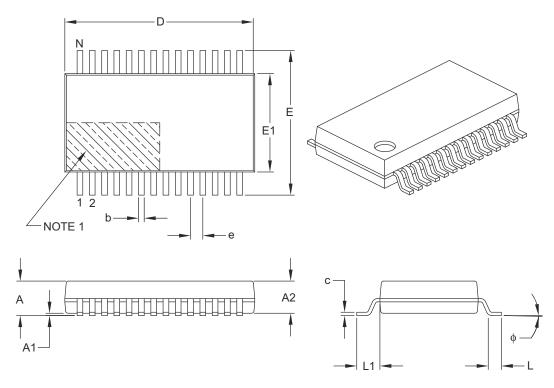

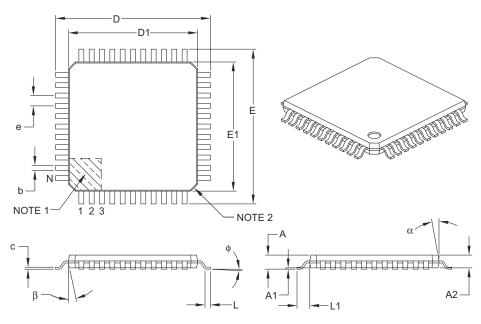

#### 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |           | MILLIMETERS | 3    |

|--------------------------|------------------|-----------|-------------|------|

|                          | Dimension Limits | MIN       | NOM         | MAX  |

| Number of Leads          | N                | 44        |             |      |

| Lead Pitch               | е                | 0.80 BSC  |             |      |

| Overall Height           | Α                | -         | _           | 1.20 |

| Molded Package Thickness | A2               | 0.95      | 1.00        | 1.05 |

| Standoff                 | A1               | 0.05      | _           | 0.15 |

| Foot Length              | L                | 0.45      | 0.60        | 0.75 |

| Footprint                | L1               |           | 1.00 REF    |      |

| Foot Angle               | ф                | 0°        | 3.5°        | 7°   |

| Overall Width            | E                | 12.00 BSC |             |      |

| Overall Length           | D                |           | 12.00 BSC   |      |

| Molded Package Width     | E1               |           | 10.00 BSC   |      |

| Molded Package Length    | D1               |           | 10.00 BSC   |      |

| Lead Thickness           | С                | 0.09      | _           | 0.20 |

| Lead Width               | b                | 0.30      | 0.37        | 0.45 |

| Mold Draft Angle Top     | α                | 11°       | 12°         | 13°  |

| Mold Draft Angle Bottom  | β                | 11°       | 12°         | 13°  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

| SLRCON (Slew Rate Control)                                                                   |     | Software Simulator (MPLAB SIM)                   | . 535 |

|----------------------------------------------------------------------------------------------|-----|--------------------------------------------------|-------|

| SSPCON1 (MSSP Control 1, I <sup>2</sup> C Mode)                                              | 298 | Special Event Trigger. See Compare (CCP Module). |       |

| SSPCON1 (MSSP Control 1, SPI Mode)                                                           | 289 | Special Event Trigger. See Compare (ECCP Mode).  |       |

| SSPCON2 (MSSP Control 2, I <sup>2</sup> C Master Mode)                                       |     | SPI Mode (MSSP)                                  | . 287 |

| SSPCON2 (MSSP Control 2, I <sup>2</sup> C Slave Mode)                                        | 300 | Associated Registers                             | . 295 |

| SSPMSK (I <sup>2</sup> C Slave Address Mask)                                                 | 300 | Bus Mode Compatibility                           | . 295 |

| SSPSTAT (MSSP Status, I <sup>2</sup> C Mode)                                                 | 297 | Effects of a Reset                               | . 295 |

| SSPSTAT (MSSP Status, SPI Mode)                                                              | 288 | Enabling SPI I/O                                 | . 291 |

| STATUS                                                                                       |     | Master Mode                                      | . 292 |

| STKPTR (Stack Pointer)                                                                       | 104 | Master/Slave Connection                          |       |

| T0CON (Timer0 Control)                                                                       |     | Operation                                        | . 290 |

| T1CON (Timer1 Control)                                                                       |     | Operation in Power-Managed Modes                 |       |

| T1GCON (Timer1 Gate Control)                                                                 |     | Serial Clock                                     |       |

| T2CON (Timer2 Control)                                                                       |     | Serial Data In                                   |       |

| T3CON (Timer3 Control)                                                                       |     | Serial Data Out                                  |       |

| T3GCON (Timer3 Gate Control)                                                                 |     | Slave Mode                                       |       |

| T4CON (Timer4 Control)                                                                       |     | Slave Select                                     |       |

| TXBIE (Transmit Buffers Interrupt Enable)                                                    |     | Slave Select Synchronization                     |       |

| TXBnCON (Transmit Buffer n Control)                                                          |     | SPI Clock                                        |       |

| TXBnDLC (Transmit Buffer n Data Length Code)                                                 |     | SSPBUF Register                                  |       |

| ,                                                                                            |     | SSPSR Register                                   |       |

| TXBnDm (Transmit Buffer n Data Field Byte m) TXBnEIDH (Transmit Buffer n Extended Identifier |     |                                                  |       |

| · ·                                                                                          | -   | Typical Connection                               |       |

| Byte)                                                                                        |     | SS                                               |       |

| TXBnEIDL (Transmit Buffer n Extended Identifier                                              |     | SSPOV                                            |       |

| Byte)                                                                                        |     | SSPOV Status Flag                                | . 322 |

| TXBnSIDH (Transmit Buffer n Standard Identifier                                              |     | SSPSTAT Register                                 |       |

| Byte)                                                                                        |     | R/W Bit                                          |       |

| TXBnSIDL (Transmit Buffer n Standard Identifier                                              |     | Stack Full/Underflow Resets                      |       |

| Byte)                                                                                        |     | SUBFSR                                           |       |

| TXERRCNT (Transmit Error Count)                                                              |     | SUBFWB                                           |       |

| TXSTAx (Transmit Status and Control)                                                         |     | SUBLW                                            |       |

| WDTCON (Watchdog Timer Control)                                                              |     | SUBULNK                                          | . 529 |

| WPUB (Weak Pull-up PORTB Enable)                                                             |     | SUBWF                                            |       |

| RESET                                                                                        | 513 | SUBWFB                                           | . 520 |

| Resets7                                                                                      |     | SWAPF                                            | . 520 |

| Brown-out Reset (BOR)                                                                        | 457 | т                                                |       |

| Oscillator Start-up Timer (OST)                                                              |     | -                                                |       |

| Power-on Reset (POR)                                                                         | 457 | Table Pointer Operations (table)                 |       |

| Power-up Timer (PWRT)                                                                        | 457 | Table Reads/Table Writes                         | . 105 |

| RETFIE                                                                                       | 514 | TBLRD                                            | . 521 |

| RETLW                                                                                        | 514 | TBLWT                                            |       |

| RETURN                                                                                       | 515 | Time-out in Various Situations (table)           | 84    |

| Return Address Stack                                                                         | 103 | Timer0                                           | . 205 |

| Return Stack Pointer (STKPTR)                                                                | 104 | Associated Registers                             | . 207 |

| Revision History                                                                             |     | Operation                                        | . 206 |

| RLCF                                                                                         |     | Overflow Interrupt                               | . 207 |

| RLNCF                                                                                        | 516 | Prescaler                                        | . 207 |

| RRCF                                                                                         |     | Switching Assignment                             | . 207 |

| RRNCF                                                                                        |     | Prescaler Assignment (PSA Bit)                   |       |

|                                                                                              |     | Prescaler Select (T0PS2:T0PS0 Bits)              |       |

| S                                                                                            |     | Reads and Writes in 16-Bit Mode                  |       |

| SCK                                                                                          | 287 | Source Edge Select (T0SE Bit)                    |       |

| SDI                                                                                          |     | Source Select (TOCS Bit)                         |       |

| SDO                                                                                          |     | Timer1                                           |       |

| SEC IDLE Mode                                                                                |     | 16-Bit Read/Write Mode                           |       |

| SEC RUN Mode                                                                                 |     | Associated Registers                             |       |

| <b>–</b>                                                                                     |     | Clock Source Selection                           | 240   |

| Selective Peripheral Module Control                                                          |     | Gate                                             |       |

| Serial Clock, SCK                                                                            |     |                                                  |       |

| Serial Data In (SDI)                                                                         |     | Interrupt                                        |       |

| Serial Data Out (SDO)                                                                        | ∠ఠ/ | Operation                                        |       |

| Serial Peripheral Interface. See SPI Mode.                                                   | -1- | Oscillator                                       |       |

| SETF                                                                                         |     | Oscillator, as Secondary Clock                   |       |

| Shoot-Through Current                                                                        |     | Resetting, Using the ECCP Special Event Trigger  |       |

| Slave Select (SS)                                                                            |     | SOSC Oscillator                                  |       |

| SLEEP                                                                                        |     | Layout Considerations                            |       |

| Sleep Mode                                                                                   | 70  | Use as a Clock Source                            | . 215 |