Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | ECANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 54                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.6K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x12b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

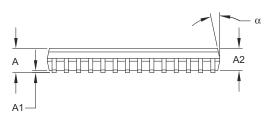

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 64-VQFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf66k80-i-mr |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

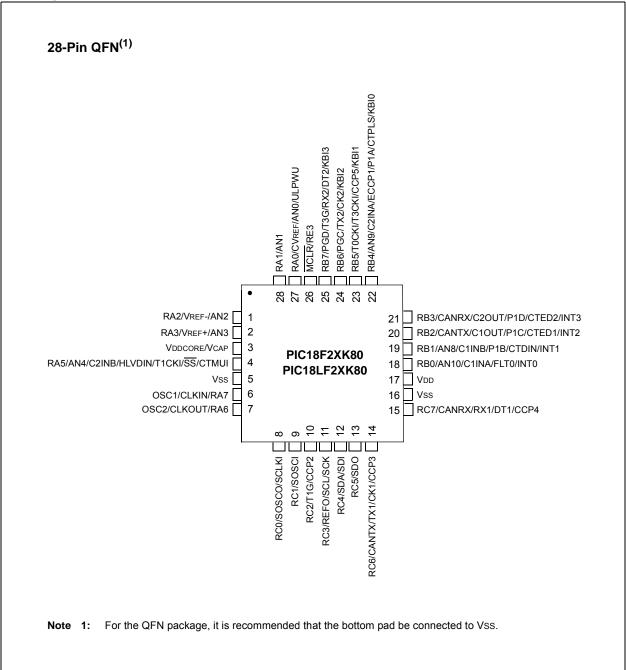

#### **Pin Diagrams**

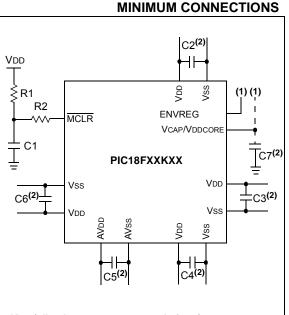

# 2.0 GUIDELINES FOR GETTING STARTED WITH PIC18FXXKXX MICROCONTROLLERS

### 2.1 Basic Connection Requirements

Getting started with the PIC18F66K80 family family of 8-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- ENVREG (if implemented) and VCAP/VDDCORE pins (see Section 2.4 "Voltage Regulator Pins (ENVREG and VCAP/VDDCORE)")

These pins must also be connected if they are being used in the end application:

- PGC/PGD pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

Note: The AVDD and AVss pins must always be connected, regardless of whether any of the analog modules are being used.

The minimum mandatory connections are shown in Figure 2-1.

# FIGURE 2-1: RECOMMENDED

#### Key (all values are recommendations):

C1 through C6: 0.1  $\mu\text{F},$  20V ceramic R1: 10 k $\Omega$

R2: 100Ω to 470Ω

- Note 1: See Section 2.4 "Voltage Regulator Pins (ENVREG and VCAP/VDDCORE)" for explanation of ENVREG pin connections.

- 2: The example shown is for a PIC18F device with five VDD/VSS and AVDD/AVSS pairs. Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

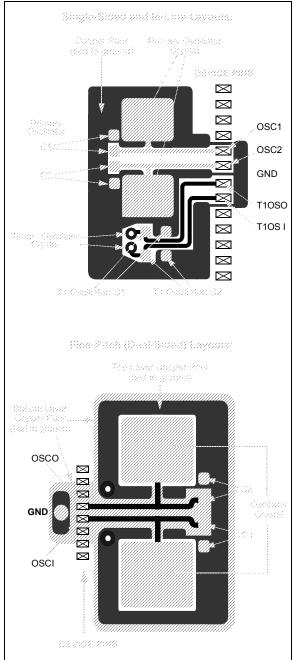

### 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 3.0 "Oscillator Configurations"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

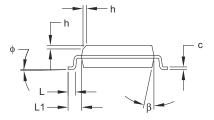

Layout suggestions are shown in Figure 2-4. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

### 2.7 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

#### FIGURE 2-5:

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

### 4.4.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator block using the INTOSC multiplexer. This mode provides controllable power conservation during Idle periods.

From RC\_RUN, this mode is entered by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, first set IDLEN, then set the SCS1 bit and execute SLEEP. To maintain software compatibility with future devices, it is recommended that SCS0 also be cleared, though its value is ignored. The INTOSC multiplexer may be used to select a higher clock frequency by modifying the IRCFx bits before executing the SLEEP instruction. When the clock source is switched to the INTOSC multiplexer, the primary oscillator is shut down and the OSTS bit is cleared.

If the IRCFx bits are set to any non-zero value, or the INTSRC/MFIOSEL bit is set, the INTOSC output is enabled. The HFIOFS/MFIOFS bits become set, after the INTOSC output becomes stable, after an interval of TIOBST (Parameter 38, Table 31-11). For information on the HFIOFS/MFIOFS bits, see Table 4-3.

Clocks to the peripherals continue while the INTOSC source stabilizes. The HFIOFS/MFIOFS bits will remain set if the IRCFx bits were previously at a non-zero value or if INTSRC was set before the SLEEP instruction was executed and the INTOSC source was already stable. If the IRCFx bits and INTSRC are all clear, the INTOSC output will not be enabled, the HFIOFS/MFIOFS bits will remain clear and there will be no indication of the current clock source.

When a wake event occurs, the peripherals continue to be clocked from the INTOSC multiplexer. After a delay of TCSD (Parameter 38, Table 31-11) following the wake event, the CPU begins executing code clocked by the INTOSC multiplexer. The IDLEN and SCSx bits are not affected by the wake-up. The INTOSC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

### 4.5 Selective Peripheral Module Control

Idle mode allows users to substantially reduce power consumption by stopping the CPU clock. Even so, peripheral modules still remain clocked, and thus, consume power. There may be cases where the application needs what this mode does not provide: the allocation of power resources to the CPU processing with minimal power consumption from the peripherals.

PIC18F66K80 family devices address this requirement by allowing peripheral modules to be selectively disabled, reducing or eliminating their power consumption. This can be done with two control bits:

- Peripheral Enable bit, generically named XXXEN Located in the respective module's main control register

- Peripheral Module Disable (PMD) bit, generically named, XXXMD – Located in one of the PMDx Control registers (PMD0, PMD1 or PMD2)

Disabling a module by clearing its XXXEN bit disables the module's functionality, but leaves its registers available to be read and written to. This reduces power consumption, but not by as much as the second approach.

Most peripheral modules have an enable bit.

In contrast, setting the PMD bit for a module disables all clock sources to that module, reducing its power consumption to an absolute minimum. In this state, the control and status registers associated with the peripheral are also disabled, so writes to those registers have no effect and read values are invalid. Many peripheral modules have a corresponding PMD bit.

There are three PMD registers in PIC18F66K80 family devices: PMD0, PMD1 and PMD2. These registers have bits associated with each module for disabling or enabling a particular peripheral.

# **10.0 INTERRUPTS**

Members of the PIC18F66K80 family of devices have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a high-priority level or a low-priority level. The high-priority interrupt vector is at 0008h and the low-priority interrupt vector is at 0018h. High-priority interrupt events will interrupt any low-priority interrupts that may be in progress.

The registers for controlling interrupt operation are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2, PIR3, PIR4 and PIR5

- PIE1, PIE2, PIE3, PIE4 and PIE5

- IPR1, IPR2, IPR3, IPR4 and IPR5

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit Indicating that an interrupt event occurred

- Enable bit Enabling program execution to branch to the interrupt vector address when the flag bit is set

- **Priority bit** Specifying high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits that enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate Global Interrupt Enable bit are set, the interrupt will vector immediately to address 0008h or 0018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit that enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit that enables/disables all interrupt sources. All interrupts branch to address 0008h in Compatibility mode.

When an interrupt is responded to, the Global Interrupt Enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a low-priority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine (ISR), the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used) that re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding enable bit or the GIE bit.

**Note:** Do not use the MOVFF instruction to modify any of the Interrupt Control registers while **any** interrupt is enabled. Doing so may cause erratic microcontroller behavior.

| Pin Name         | Function             | TRIS<br>Setting | I/O | I/О Туре | Description                                                                                                                                     |

|------------------|----------------------|-----------------|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| RB4/AN9/C2INA/   | RB4                  | 0               | 0   | DIG      | LATB<4> data output.                                                                                                                            |

| ECCP1/P1A/CTPLS/ |                      | 1               | I   | ST       | PORTB<4> data input; weak pull-up when RBPU bit is cleared.                                                                                     |

| KBI0             | AN9                  | 1               | Ι   | ANA      | A/D Input Channel 9 and Comparator C2+ input. Default input configuration on POR; not affected by analog output.                                |

|                  | C2INA <sup>(1)</sup> | 2               | Ι   | ANA      | Comparator 2 Input A.                                                                                                                           |

|                  | ECCP1 <sup>(1)</sup> | 0               | 0   | DIG      | ECCP1 compare output and ECCP1 PWM output. Takes priority over port data.                                                                       |

|                  |                      | 1               | Ι   | ST       | ECCP1 capture input.                                                                                                                            |

|                  | P1A <sup>(1)</sup>   | 0               | 0   | DIG      | ECCP1 Enhanced PWM output, Channel A. May be configured for<br>tri-state during Enhanced PWM shutdown events. Takes priority<br>over port data. |

|                  | CTPLS                | х               | 0   | DIG      | CTMU pulse generator output.                                                                                                                    |

|                  | KBI0                 | 1               | Ι   | ST       | Interrupt-on-pin change.                                                                                                                        |

| RB5/T0CKI/T3CKI/ | RB5                  | 0               | 0   | DIG      | LATB<5> data output.                                                                                                                            |

| CCP5/KBI1        |                      | 1               | Ι   | ST       | PORTB<5> data input; weak pull-up when RBPU bit is cleared.                                                                                     |

|                  | T0CKI <sup>(3)</sup> | x               | Ι   | ST       | Timer0 clock input.                                                                                                                             |

|                  | T3CKI <sup>(4)</sup> | x               | Ι   | ST       | Timer3 clock input.                                                                                                                             |

|                  | CCP5                 | 0               | 0   | DIG      | CCP5 compare/PWM output. Takes priority over port data.                                                                                         |

| -                |                      | 1               | Ι   | ST       | CCP5 capture input.                                                                                                                             |

|                  | KBI1                 | 1               | I   | ST       | Interrupt-on-pin change.                                                                                                                        |

| RB6/PGC/TX2/CK2/ | RB6                  | 0               | 0   | DIG      | LATB<6> data output.                                                                                                                            |

| KBI2             |                      | 1               | Ι   | ST       | PORTB<6> data input; weak pull-up when RBPU bit is cleared.                                                                                     |

|                  | PGC                  | x               | Ι   | ST       | Serial execution (ICSP™) clock input for ICSP and ICD operation.                                                                                |

|                  | TX2 <sup>(1)</sup>   | 0               | 0   | DIG      | Asynchronous serial data output (EUSARTx module); takes priority over port data.                                                                |

|                  | CK2 <sup>(1)</sup>   | 0               | 0   | DIG      | Synchronous serial clock output (EUSARTx module); user must configure as an input.                                                              |

|                  |                      | 1               | -   | ST       | Synchronous serial clock input (EUSARTx module); user must<br>configure as an input.                                                            |

|                  | KBI2                 | 1               | Ι   | ST       | Interrupt-on-pin change.                                                                                                                        |

| RB7/PGD/T3G/RX2/ | RB7                  | 0               | 0   | DIG      | LATB<7> data output.                                                                                                                            |

| DT2/KBI3         |                      | 1               | -   | ST       | PORTB<7> data input; weak pull-up when RBPU bit is cleared.                                                                                     |

|                  | PGD                  | х               | 0   | DIG      | Serial execution data output for ICSP and ICD operation.                                                                                        |

|                  |                      | x               | Ι   | ST       | Serial execution data input for ICSP and ICD operation.                                                                                         |

|                  | T3G                  | x               | -   | ST       | Timer3 external clock gate input.                                                                                                               |

|                  | RX2 <sup>(1)</sup>   | 1               | I   | ST       | Asynchronous serial receive data input (EUSARTx module).                                                                                        |

|                  | DT2 <sup>(1)</sup>   | 1               | 0   | DIG      | Synchronous serial data output (AUSART module); takes priority over port data.                                                                  |

|                  |                      | 1               | Ι   | ST       | Synchronous serial data input (AUSART module); user must<br>configure as an input.                                                              |

|                  | KBI3                 | 1               | Ι   | ST       | Interrupt-on-pin change.                                                                                                                        |

| TABLE 11-3: | PORTB FUNCTIONS | (CONTINUED) |

|-------------|-----------------|-------------|

|             |                 |             |

Legend: O = Output; I = Input; ANA = Analog Signal; DIG = CMOS Output; ST = Schmitt Trigger Buffer Input;

x = Don't care (TRIS bit does not affect port direction or is overridden for this option)

Note 1: This pin assignment is only available for 28-pin devices (PIC18F2XK80).

2: This is the default pin assignment for CANRX and CANTX when the CANMX Configuration bit is set.

3: This is the default pin assignment for TOCKI when the TOCKMX Configuration bit is set.

4: This is the default pin assignment for T3CKI for 28, 40 and 44-pin devices. This is the alternate pin assignment for T3CKI for 64-pin devices when T3CKMX is cleared.

# 14.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates these features:

- · Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- · Selectable clock source (internal or external) with device clock or SOSC oscillator internal options

- Interrupt-on-overflow

- Reset on ECCP Special Event Trigger

- · Timer with gated control

Figure 14-1 displays a simplified block diagram of the Timer1 module.

The module derives its clocking source from either the secondary oscillator or from an external digital source. If using the secondary oscillator, there are the additional options for low-power, high-power and external digital clock source.

Timer1 is controlled through the T1CON Control register (Register 14-1). It also contains the Timer1 Oscillator Enable bit (SOSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

The Fosc clock source should not be used with the ECCP capture/compare features. If the timer will be used with the capture or compare features, always select one of the other timer clocking options.

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0 | R/W-0  |

|---------|---------|---------|---------|--------|--------|-------|--------|

| TMR1CS1 | TMR1CS0 | T1CKPS1 | T1CKPS0 | SOSCEN | T1SYNC | RD16  | TMR10N |

| bit 7   |         |         |         |        |        |       | bit 0  |

REGISTER 14-1: T1CON: TIMER1 CONTROL REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-6 | TMR1CS<1:0>: Timer1 Clock Source Select bits                                                                                                                                                                                                                                                                              |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 10 = Timer1 clock source is either from pin or oscillator, depending on the SOSCEN bit:                                                                                                                                                                                                                                   |

|         | SOSCEN = 0:                                                                                                                                                                                                                                                                                                               |

|         | External clock is from the T1CKI pin (on the rising edge).                                                                                                                                                                                                                                                                |

|         | <u>SOSCEN = 1:</u><br>Depending on the SOSCSELx Configuration bit, the clock source is either a crystal oscillator on<br>SOSCI/SOSCO or an internal digital clock from the SCLKI pin.<br>01 = Timer1 clock source is the system clock (Fosc) <sup>(1)</sup><br>00 = Timer1 clock source is the instruction clock (Fosc/4) |

| bit 5-4 | T1CKPS<1:0>: Timer1 Input Clock Prescale Select bits                                                                                                                                                                                                                                                                      |

|         | 11 = 1:8 Prescale value<br>10 = 1:4 Prescale value<br>01 = 1:2 Prescale value<br>00 = 1:1 Prescale value                                                                                                                                                                                                                  |

| bit 3   | SOSCEN: SOSC Oscillator Enable bit                                                                                                                                                                                                                                                                                        |

|         | 1 = SOSC is enabled and available for Timer1                                                                                                                                                                                                                                                                              |

|         | 0 = SOSC is disabled for Timer1<br>The oscillator inverter and feedback resistor are turned off to eliminate power drain.                                                                                                                                                                                                 |

| bit 2   | <b>T1SYNC</b> : Timer1 External Clock Input Synchronization Select bit                                                                                                                                                                                                                                                    |

|         | <u>TMR1CS&lt;1:0&gt; = 10:</u>                                                                                                                                                                                                                                                                                            |

|         | 1 = Do not synchronize external clock input                                                                                                                                                                                                                                                                               |

|         | 0 = Synchronizes external clock input                                                                                                                                                                                                                                                                                     |

|         | $\frac{\text{TMR1CS} < 1:0> = 0x:}{\text{TMR1CS} < 1:0> = 1}$                                                                                                                                                                                                                                                             |

|         | This bit is ignored. Timer1 uses the internal clock when TMR1CS<1:0> = $1x$ .                                                                                                                                                                                                                                             |

| Note 1  | The Fosc clock source should not be selected if the timer will be used with the FCCP canture/compare                                                                                                                                                                                                                      |

ck source should not be selected if the timer will be used with the ECCP capture/compare features.

| R/W-0         | R/W-0                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                   | R/W-0                                                                                                                                                                                                   | R/W-0                                                                                                                                      | R/W-0                                                                                                                  | R/W-0                                                                              | R/W-0             |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------|

| P1M1          | P1M0                                                                                                                                                                                     | DC1B1                                                                                                                                                                                                                                   | DC1B0                                                                                                                                                                                                   | CCP1M3                                                                                                                                     | CCP1M2                                                                                                                 | CCP1M1                                                                             | CCP1M0            |

| bit 7         |                                                                                                                                                                                          |                                                                                                                                                                                                                                         |                                                                                                                                                                                                         | •                                                                                                                                          |                                                                                                                        | ·                                                                                  | bit               |

| Legend:       |                                                                                                                                                                                          |                                                                                                                                                                                                                                         |                                                                                                                                                                                                         |                                                                                                                                            |                                                                                                                        |                                                                                    |                   |

| R = Readabl   | le bit                                                                                                                                                                                   | W = Writable                                                                                                                                                                                                                            | bit                                                                                                                                                                                                     | U = Unimpler                                                                                                                               | mented bit, read                                                                                                       | d as '0'                                                                           |                   |

| -n = Value at | POR                                                                                                                                                                                      | '1' = Bit is set                                                                                                                                                                                                                        | :                                                                                                                                                                                                       | '0' = Bit is cle                                                                                                                           | ared                                                                                                                   | x = Bit is unki                                                                    | nown              |

| bit 7-6       | <u>If CCP1M&lt;3</u><br>xx = P1A a<br><u>If CCP1M&lt;3</u><br>00 = Single<br><b>Steeri</b><br>01 = Full-br                                                                               | output: P1A, P<br>ng Mode")<br>idge output forv                                                                                                                                                                                         | <u>o:</u><br>ture/compare i<br>1B, P1C and<br>vard: P1D is m                                                                                                                                            | nput/output; P1<br>P1D are contro<br>nodulated; P1A                                                                                        | olled by steering                                                                                                      | g (see <b>Section</b><br>P1C is inactive                                           | 20.4.7 "Puls      |

|               | assign                                                                                                                                                                                   | ridge output: F<br>led as port pins<br>idge output reve                                                                                                                                                                                 |                                                                                                                                                                                                         |                                                                                                                                            |                                                                                                                        |                                                                                    |                   |

| bit 5-4       | Capture moc<br>Unused.<br>Compare mc<br>Unused.<br>PWM mode:                                                                                                                             | ode:                                                                                                                                                                                                                                    |                                                                                                                                                                                                         |                                                                                                                                            | . The eight MS                                                                                                         | bs of the duty c                                                                   | ycle are foun     |

| bit 3-0       |                                                                                                                                                                                          | >: ECCP1 Mod                                                                                                                                                                                                                            | e Select bits                                                                                                                                                                                           |                                                                                                                                            |                                                                                                                        |                                                                                    |                   |

|               | 0001 = Res<br>0010 = Cor<br>0011 = Cap<br>0100 = Cap<br>0101 = Cap<br>0110 = Cap<br>0111 = Cap<br>1000 = Cor<br>1001 = Cor<br>1010 = Cor<br>1011 = Cor<br>sets<br>1100 = PW<br>1101 = PW | npare mode: To<br>oture mode<br>oture mode: Eve<br>oture mode: Eve<br>oture mode: Eve<br>oture mode: Eve<br>npare mode: Ini<br>npare mode: Ini<br>npare mode: Ini<br>npare mode: Tri<br>s CCP1IF bit)<br>M mode: P1A a<br>M mode: P1A a | eggle output or<br>ery falling edge<br>ery rising edge<br>ery fourth rising<br>itialize ECCP1<br>itialize ECCP1<br>enerate softwa<br>igger special e<br>and P1C are a<br>und P1C are a<br>und P1C are a | n match<br>g edge<br>edge<br>pin low, set ou<br>pin high, clear<br>the interrupt on<br>vent (ECCP1 r<br>ctive-high; P1B<br>ctive-high; P1B | utput on compa<br>output on com<br>ly, ECCP1 pin r<br>esets TMR1 or<br>and P1D are a<br>and P1D are a<br>and P1D are a | pare match (se<br>reverts to I/O st<br>TMR3, starts A<br>active-high<br>active-low | et CCP1IF)<br>ate |

#### REGISTER 20-1: CCP1CON: ENHANCED CAPTURE/COMPARE/PWM1 CONTROL

| <b>IGURE 21-5:</b>             | SPI N             | IODE W      | AVEFO                                              | RM (SLA       | VE MO                     | DE WITH | CKE =            | 0)                                    |                   |                                              |                 |

|--------------------------------|-------------------|-------------|----------------------------------------------------|---------------|---------------------------|---------|------------------|---------------------------------------|-------------------|----------------------------------------------|-----------------|

| <br>SS<br>Opiicasi             | ( .               |             |                                                    |               |                           |         |                  |                                       |                   |                                              |                 |

| 80%<br>{CKP = 0<br>CXE = 0}    | :<br>:<br>:<br>:X |             | ,<br>                                              | ·             | ·                         |         |                  |                                       |                   | ·<br>·                                       | :<br>:<br>:<br> |

| - VAR 20)<br>- ROR             | ·<br>·            | :<br>:<br>: | (<br>(<br>() () () () () () () () () () () () () ( | ,<br>,<br>, , | ;<br>;<br>; , ,           |         | (<br>(<br>(      | ;<br>;<br>;                           | 2<br>2<br>3       | ,<br>,<br>,                                  |                 |

| 2508<br>(CRE = 5<br>(CRE = 5)  | 2<br>5<br>5       |             |                                                    |               |                           |         |                  | · · · · · · · · · · · · · · · · · · · |                   |                                              |                 |

| Verlie en<br>Sisteration       |                   |             | 5<br>2<br>7<br>7                                   | :<br>d        | *<br>\$******<br>\$<br>\$ |         | 5<br>2<br>7<br>7 | :<br>::<br>:<br>:                     | *<br>.5<br>1<br>1 | :<br>:                                       | ,<br>           |

| \$6 <b>x</b> 3                 |                   | Kana a      |                                                    | N 88.8        |                           | X68.3   | X 88.0           |                                       |                   | . 88-8                                       |                 |

| SD:<br>(S3:82 = 33)            |                   |             |                                                    |               |                           |         |                  |                                       |                   | Mygeeneerine<br>E C                          | :<br>:<br>:     |

| ingasi<br>Serrecia             | ·<br>·<br>·       |             |                                                    | . 4.          |                           | <i></i> |                  | :<br>. <i>B</i> e                     | :<br>:<br>:       | 49.                                          |                 |

| (3367 = 6)                     |                   |             |                                                    | *<br>*        | ,<br>,<br>,               |         | 5<br>2<br>5      |                                       | * :<br>* :        | :<br>:<br>:///////////////////////////////// |                 |

| - S-SPHF<br>Britanupî<br>Filag | ;<br>;<br>;<br>;  |             | s<br>2<br>2                                        | :<br>:<br>:   | <<br>;<br>;<br>;          |         | 5<br>2<br>2<br>2 | :<br>:<br>::                          |                   | ilia<br>A stent Ca                           | . Produce       |

| 355 <b>0</b> 355 65            | 2<br>1            | *<br>:      |                                                    | ;<br>,        | :                         |         | i<br>i           | ;<br>,                                |                   | 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 -      |                 |

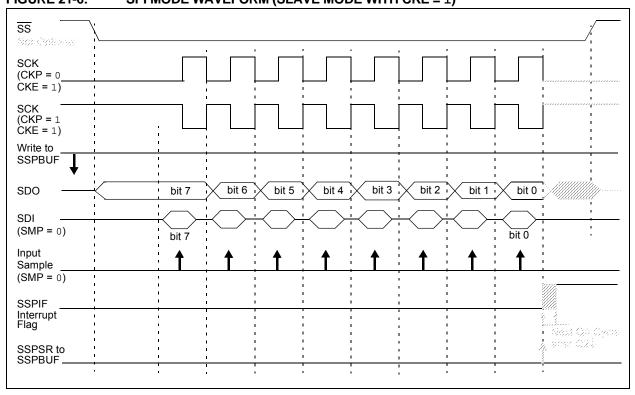

# FIGURE 21-6: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

## 25.0 COMPARATOR VOLTAGE REFERENCE MODULE

The comparator voltage reference is a 32-tap resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it may also be used independently of them.

A block diagram of the module is shown in Figure 25-1. The resistor ladder is segmented to provide a range of CVREF values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/VSS or an external voltage reference.

#### 25.1 Configuring the Comparator Voltage Reference

The comparator voltage reference module is controlled through the CVRCON register (Register 25-1). The comparator voltage reference provides a range of output voltage with 32 levels.

The CVR<4:0> selection bits (CVRCON<4:0>) offer a range of output voltages. Equation 25-1 shows the how the comparator voltage reference is computed.

### EQUATION 25-1:

$$\frac{\text{If CVRSS} = 1:}{\text{CVREF}} = \left(\text{VREF} + \frac{\text{CVR} < 4:0>}{32}\right) \cdot (\text{VREF} + - \text{VREF})$$

$$\frac{\text{If CVRSS} = 0:}{\text{CVREF}} = \left(\text{AVSS} + \frac{\text{CVR} < 4:0>}{32}\right) \cdot (\text{AVDD} - \text{AVSS})$$

The comparator reference supply voltage can come from either VDD and Vss, or the external VREF+ and VREF- that are multiplexed with RA3 and RA2. The voltage source is selected by the CVRSS bit (CVRCON<5>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output (see Table 31-2 in **Section 31.0 "Electrical Characteristics"**).

# REGISTER 25-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0         | R/W-0        | R/W-0              | R/W-0           | R/W-0                  | R/W-0           | R/W-0           | R/W-0 |

|---------------|--------------|--------------------|-----------------|------------------------|-----------------|-----------------|-------|

| CVREN         | CVROE        | CVRSS              | CVR4            | CVR3                   | CVR2            | CVR1            | CVR0  |

| bit 7         | -            |                    |                 |                        |                 |                 | bit ( |

|               |              |                    |                 |                        |                 |                 |       |

| Legend:       |              |                    |                 |                        |                 |                 |       |

| R = Readable  | e bit        | W = Writable b     | bit             | U = Unimplem           | nented bit, rea | d as '0'        |       |

| -n = Value at | POR          | '1' = Bit is set   |                 | '0' = Bit is clea      | ared            | x = Bit is unkr | nown  |

|               |              |                    |                 |                        |                 |                 |       |

| bit 7         |              | nparator Voltage   |                 | nable bit              |                 |                 |       |

|               |              | ircuit powered o   |                 |                        |                 |                 |       |

|               | 0 = CVREF C  | ircuit powered d   | own             |                        |                 |                 |       |

| bit 6         | CVROE: Cor   | mparator VREF C    | output Enable   | bit                    |                 |                 |       |

|               |              | oltage level is or |                 |                        |                 |                 |       |

|               | 0 = CVREF V  | oltage level is di | sconnected fr   | om CVREF pin           |                 |                 |       |

| bit 5         | CVRSS: Con   | nparator VREF S    | ource Selection | on bit                 |                 |                 |       |

|               | 1 = Compara  | ator reference so  | ource, CVRSR    | C = VREF+ - VRI        | EF-             |                 |       |

|               | 0 = Compara  | ator reference so  | ource, CVRSR    | c = AVDD – AVs         | S               |                 |       |

| bit 4-0       | CVR<4:0>: (  | Comparator VRE     | Value Selec     | tion $0 \le CVR < 4$ : | 0> ≤ 31 bits    |                 |       |

|               | When CVRS    |                    |                 |                        |                 |                 |       |

|               | CVREF = (VRI | EF-) + (CVR<4:0    | >/32) • (VREF   | + – VREF-)             |                 |                 |       |

|               | When CVRS    |                    | (00) (1) (      |                        |                 |                 |       |

|               | CVREF = (AV  | ss) + (CVR<4:0     | >/32) • (AVDD   | – AVSS)                |                 |                 |       |

|               |              |                    |                 |                        |                 |                 |       |

#### 27.2.3.2 Message Acceptance Filters and Masks

This section describes the message acceptance filters and masks for the CAN receive buffers.

# REGISTER 27-37: RXFnSIDH: RECEIVE ACCEPTANCE FILTER 'n' STANDARD IDENTIFIER FILTER REGISTERS, HIGH BYTE [0 $\leq$ n $\leq$ 15]<sup>(1)</sup>

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID10 | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-0 SID<10:3>: Standard Identifier Filter bits (if EXIDEN = 0) Extended Identifier Filter bits, EID<28:21> (if EXIDEN = 1).

Note 1: Registers, RXF6SIDH:RXF15SIDH, are available in Mode 1 and 2 only.

# REGISTER 27-38: RXFnSIDL: RECEIVE ACCEPTANCE FILTER 'n' STANDARD IDENTIFIER FILTER REGISTERS, LOW BYTE [0 $\le$ n $\le$ 15]<sup>(1)</sup>

| R/W-x | R/W-x | R/W-x | U-0 | R/W-x                 | U-0 | R/W-x | R/W-x |

|-------|-------|-------|-----|-----------------------|-----|-------|-------|

| SID2  | SID1  | SID0  | —   | EXIDEN <sup>(2)</sup> |     | EID17 | EID16 |

| bit 7 |       |       |     |                       |     |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-5 | SID<2:0>: Standard Identifier Filter bits (if EXIDEN = 0)    |

|---------|--------------------------------------------------------------|

|         | Extended Identifier Filter bits, EID<20:18> (if EXIDEN = 1). |

| bit 4   | Unimplemented: Read as '0'                                   |

| bit 3   | EXIDEN: Extended Identifier Filter Enable bit <sup>(2)</sup> |

|         | 1 = Filter will only accept extended ID messages             |

|         | 0 = Filter will only accept standard ID messages             |

| bit 2   | Unimplemented: Read as '0'                                   |

| hit 1_0 | EID-17:16>: Extended Identifier Filter hits                  |

- bit 1-0 EID<17:16>: Extended Identifier Filter bits

- **Note 1:** Registers, RXF6SIDL:RXF15SIDL, are available in Mode 1 and 2 only.

- 2: In Mode 0, this bit must be set/cleared as required, irrespective of corresponding mask register value.

Table 27-2 shows the relation between the clock generated by the PLL and the frequency error from jitter (measured jitter-induced error of 2%, Gaussian distribution, within 3 standard deviations), as a percentage of the nominal clock frequency.

This is clearly smaller than the expected drift of a crystal oscillator, typically specified at 100 ppm or 0.01%. If we add jitter to oscillator drift, we have a total frequency drift of 0.0132%. The total oscillator frequency errors for common clock frequencies and bit rates, including both drift and jitter, are shown in Table 27-3.

| <b>TABLE 27-2</b> : | FREQUENCY ERROR FROM JITTER AT VARIOUS PLL GENERATED CLOCK SPEEDS |

|---------------------|-------------------------------------------------------------------|

|                     |                                                                   |

| PLL<br>Output |                     |                     | Frequenc           | y Error at Various N | Iominal Bit Times  | s (Bit Rates)    |

|---------------|---------------------|---------------------|--------------------|----------------------|--------------------|------------------|

|               | P <sub>jitter</sub> | T <sub>jitter</sub> | 8 μs<br>(125 Kb/s) | 4 μs<br>(250 Kb/s)   | 2 μs<br>(500 Kb/s) | 1 μs<br>(1 Mb/s) |

| 40 MHz        | 0.5 ns              | 1 ns                | 0.00125%           | 0.00250%             | 0.005%             | 0.01%            |

| 24 MHz        | 0.83 ns             | 1.67 ns             | 0.00209%           | 0.00418%             | 0.008%             | 0.017%           |

| 16 MHz        | 1.25 ns             | 2.5 ns              | 0.00313%           | 0.00625%             | 0.013%             | 0.025%           |

# TABLE 27-3:TOTAL FREQUENCY ERROR AT VARIOUS PLL GENERATED CLOCK SPEEDS<br/>(100 PPM OSCILLATOR DRIFT, INCLUDING ERROR FROM JITTER)

|                    | Frequency Error at Various Nominal Bit Times (Bit Rates) |                    |                    |                  |  |  |  |  |

|--------------------|----------------------------------------------------------|--------------------|--------------------|------------------|--|--|--|--|

| Nominal PLL Output | 8 μs<br>(125 Kb/s)                                       | 4 μs<br>(250 Kb/s) | 2 μs<br>(500 Kb/s) | 1 μs<br>(1 Mb/s) |  |  |  |  |

| 40 MHz             | 0.01125%                                                 | 0.01250%           | 0.015%             | 0.02%            |  |  |  |  |

| 24 MHz             | 0.01209%                                                 | 0.01418%           | 0.018%             | 0.027%           |  |  |  |  |

| 16 MHz             | 0.01313%                                                 | 0.01625%           | 0.023%             | 0.035%           |  |  |  |  |

ADD W to f

$\mathsf{ADDWF} \quad \ \ f\left\{,d\left\{,a\right\}\right\}$

### 29.1.1 STANDARD INSTRUCTION SET

| ADDLW                                                       | ADD Litera                        | al to W        |           |               | ADDWF                                           |

|-------------------------------------------------------------|-----------------------------------|----------------|-----------|---------------|-------------------------------------------------|

| Syntax:                                                     | ADDLW                             | k              |           |               | Syntax:                                         |

| Operands:                                                   | $0 \le k \le 255$                 | 5              | Operands: |               |                                                 |

| Operation:                                                  | (W) + k $\rightarrow$             | W              |           |               |                                                 |

| Status Affected:                                            | N, OV, C, [                       | DC, Z          |           |               | Operation:                                      |

| Encoding:                                                   | 0000                              | 1111           | kkkk      | kkkk          | Operation:<br>Status Affected:                  |

| Description:                                                | The conter<br>8-bit literal<br>W. |                | Encoding  |               |                                                 |

| Words:                                                      | 1                                 |                |           |               |                                                 |

| Cycles:                                                     | 1                                 |                |           |               |                                                 |

| Q Cycle Activity:                                           |                                   |                |           |               |                                                 |

| Q1                                                          | Q2                                | Q3             |           | Q4            | 1                                               |

| Decode                                                      | Read<br>literal 'k'               | Proces<br>Data | is N      | Write to<br>W |                                                 |

| Example:<br>Before Instruc<br>W =<br>After Instructi<br>W = | ction<br>10h                      | 15h            |           |               |                                                 |

|                                                             |                                   |                |           |               | Words:                                          |

|                                                             |                                   |                |           |               | Cycles:                                         |

|                                                             |                                   |                |           |               | Q Cycle Activity:<br>Q1                         |

|                                                             |                                   |                |           |               | Decode                                          |

|                                                             |                                   |                |           |               | Example:                                        |

|                                                             |                                   |                |           |               | Before Instruct<br>W<br>REG<br>After Instructio |

| ,                                              |                                                                                                        |                                                                                                                                      | •                                                              |                                                    |  |  |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------|--|--|--|

| Operands:                                      | 0 ≤ f ≤ 255<br>d ∈ [0,1]                                                                               |                                                                                                                                      |                                                                |                                                    |  |  |  |

|                                                | a ∈ [0,1]<br>a ∈ [0,1]                                                                                 |                                                                                                                                      |                                                                |                                                    |  |  |  |

| Operation:                                     | (W) + (f) $\rightarrow$                                                                                | dest                                                                                                                                 |                                                                |                                                    |  |  |  |

| Status Affected:                               | N, OV, C, E                                                                                            | DC, Z                                                                                                                                |                                                                |                                                    |  |  |  |

| Encoding:                                      | 0010                                                                                                   | 01da                                                                                                                                 | ffff                                                           | ffff                                               |  |  |  |

| Description:                                   | result is sto                                                                                          | Add W to register 'f'. If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored back in register 'f' (default). |                                                                |                                                    |  |  |  |

|                                                | If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank.                                                      | he BSR i                                                                                                                             |                                                                |                                                    |  |  |  |

|                                                | If 'a' is '0' a<br>set is enab<br>in Indexed<br>mode wher<br>Section 29<br>Bit-Oriente<br>Literal Offs | led, this in<br>Literal Of<br>never f ≤ 9<br>0.2.3 "Byt<br>ed Instrue                                                                | nstruction<br>fset Addr<br>95 (5Fh).<br>ce-Orient<br>ctions in | n operates<br>ressing<br>See<br>red and<br>Indexed |  |  |  |

| Words:                                         | 1                                                                                                      |                                                                                                                                      |                                                                |                                                    |  |  |  |

| Cycles:                                        | 1                                                                                                      |                                                                                                                                      |                                                                |                                                    |  |  |  |

| Q Cycle Activity:                              |                                                                                                        |                                                                                                                                      |                                                                |                                                    |  |  |  |

| Q1                                             | Q2                                                                                                     | Q3                                                                                                                                   |                                                                | Q4                                                 |  |  |  |

| Decode                                         | Read<br>register 'f'                                                                                   | Proce:<br>Data                                                                                                                       |                                                                | Write to<br>estination                             |  |  |  |

|                                                |                                                                                                        |                                                                                                                                      |                                                                |                                                    |  |  |  |

| Example:                                       | ADDWF                                                                                                  | REG, (                                                                                                                               | Ο, Ο                                                           |                                                    |  |  |  |

| Before Instruc<br>W<br>REG<br>After Instructio | = 17h<br>= 0C2h                                                                                        |                                                                                                                                      |                                                                |                                                    |  |  |  |

| W<br>REG                                       | = 0D9h<br>= 0C2h                                                                                       |                                                                                                                                      |                                                                |                                                    |  |  |  |

**Note:** All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in symbolic addressing. If a label is used, the instruction format then becomes: {label} instruction argument(s).

| IORLW               | Inclusive OR Literal with W           |                            |      |               |  |  |  |  |

|---------------------|---------------------------------------|----------------------------|------|---------------|--|--|--|--|

| Syntax:             | IORLW k                               |                            |      |               |  |  |  |  |

| Operands:           | $0 \le k \le 255$                     | 5                          |      |               |  |  |  |  |

| Operation:          | (W) .OR. k                            | (W) .OR. $k \rightarrow W$ |      |               |  |  |  |  |

| Status Affected:    | N, Z                                  |                            |      |               |  |  |  |  |

| Encoding:           | 0000                                  | 1001                       | kkkk | kkkk          |  |  |  |  |

| Description:        | The conter<br>eight-bit lite<br>in W. |                            |      |               |  |  |  |  |

| Words:              | 1                                     |                            |      |               |  |  |  |  |

| Cycles:             | 1                                     |                            |      |               |  |  |  |  |

| Q Cycle Activity:   |                                       |                            |      |               |  |  |  |  |

| Q1                  | Q2                                    | Q3                         |      | Q4            |  |  |  |  |

| Decode              | Read<br>literal 'k'                   | Proce<br>Data              |      | Write to<br>W |  |  |  |  |

| Example:            | IORLW                                 | 35h                        |      |               |  |  |  |  |

| Before Instruc<br>W | tion<br>= 9Ah                         |                            |      |               |  |  |  |  |

BFh

=

After Instruction W

| IORWF                                                                        | Inclusive C                                                                                                                                                                                                                                                                          | R W wit                                                                                                                                                  | h f  |                       |  |  |  |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|--|--|--|

| Syntax:                                                                      | IORWF f                                                                                                                                                                                                                                                                              | {,d {,a}}                                                                                                                                                |      |                       |  |  |  |

| Operands:                                                                    | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                                                                   |                                                                                                                                                          |      |                       |  |  |  |

| Operation:                                                                   | (W) .OR. (f)                                                                                                                                                                                                                                                                         | $\rightarrow$ dest                                                                                                                                       |      |                       |  |  |  |

| Status Affected:                                                             | N, Z                                                                                                                                                                                                                                                                                 |                                                                                                                                                          |      |                       |  |  |  |

| Encoding:                                                                    | 0001                                                                                                                                                                                                                                                                                 | 00da                                                                                                                                                     | ffff | ffff                  |  |  |  |

| Description:                                                                 | '0', the resu                                                                                                                                                                                                                                                                        | Inclusive OR W with register 'f'. If 'd' is<br>'0', the result is placed in W. If 'd' is '1',<br>the result is placed back in register 'f'<br>(default). |      |                       |  |  |  |

|                                                                              | ,                                                                                                                                                                                                                                                                                    | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.                                                 |      |                       |  |  |  |

|                                                                              | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 29.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                                                                                                                                                          |      |                       |  |  |  |