Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| D-4-9-                     |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Details                    |                                                                              |

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | ECANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 54                                                                           |

| Program Memory Size        | 64KB (32K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 3.6K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 11x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-TQFP                                                                      |

| Supplier Device Package    | 64-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf66k80t-i-pt |

**NOTES:**

#### 6.2 PIC18 Instruction Cycle

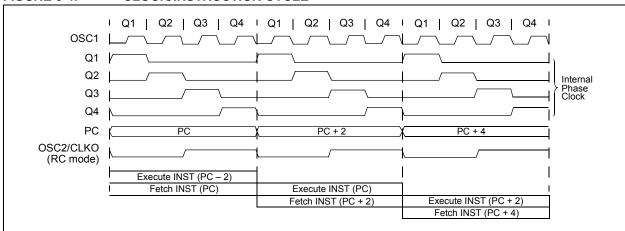

#### 6.2.1 CLOCKING SCHEME

The microcontroller clock input, whether from an internal or external source, is internally divided by four to generate four non-overlapping quadrature clocks (Q1, Q2, Q3 and Q4). Internally, the Program Counter is incremented on every Q1, with the instruction fetched from the program memory and latched into the Instruction Register (IR) during Q4.

The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 6-4.

#### 6.2.2 INSTRUCTION FLOW/PIPELINING

An "Instruction Cycle" consists of four Q cycles, Q1 through Q4. The instruction fetch and execute are pipelined in such a manner that a fetch takes one instruction cycle, while the decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction (such as GOTO) causes the Program Counter to change, two cycles are required to complete the instruction. (See Example 6-3.)

A fetch cycle begins with the Program Counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle, Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

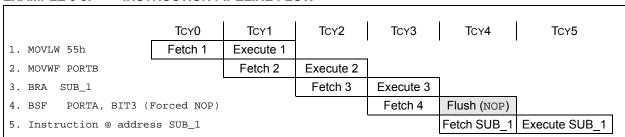

#### **EXAMPLE 6-3: INSTRUCTION PIPELINE FLOW**

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

TABLE 6-2: PIC18F66K80 FAMILY REGISTER FILE SUMMARY (CONTINUED)

|        | L 0-2. F  | 10101001      |                | I ILEGIO        |                |          | · · (00.11. | <u>.                                 </u> | 1       |                                 |

|--------|-----------|---------------|----------------|-----------------|----------------|----------|-------------|-------------------------------------------|---------|---------------------------------|

| Addr.  | File Name | Bit 7         | Bit 6          | Bit 5           | Bit 4          | Bit 3    | Bit 2       | Bit 1                                     | Bit 0   | Value on<br>POR, BOR<br>on page |

| F9Fh   | IPR1      | PSPIP         | ADIP           | RC1IP           | TX1IP          | SSPIP    | TMR1GIP     | TMR2IP                                    | TMR1IP  | 90                              |

| F9Eh   | PIR1      | PSPIF         | ADIF           | RC1IF           | TX1IF          | SSPIF    | TMR1GIF     | TMR2IF                                    | TMR1IF  | 89                              |

| F9Dh   | PIE1      | PSPIE         | ADIE           | RC1IE           | TX1IE          | SSPIE    | TMR1GIE     | TMR2IE                                    | TMR1IE  | 89                              |

| F9Ch   | PSTR1CON  | CMPL1         | CMPL0          | _               | STRSYNC        | STRD     | STRC        | STRB                                      | STRA    | 89                              |

| F9Bh   | OSCTUNE   | INTSRC        | PLLEN          | TUN5            | TUN4           | TUN3     | TUN2        | TUN1                                      | TUN0    | 90                              |

| F9Ah   | REFOCON   | ROON          | _              | ROSSLP          | ROSEL          | RODIV3   | RODIV2      | RODIV1                                    | RODIV0  | 90                              |

| F99h   | CCPTMRS   | _             | _              | _               | C5TSEL         | C4TSEL   | C3TSEL      | C2TSEL                                    | C1TSEL  | 90                              |

| F98h   | TRISG     | _             | _              | _               | TRISG4         | TRISG3   | TRISG2      | TRISG1                                    | TRISG0  | 90                              |

| F97h   | TRISF     | TRISF7        | TRISF6         | TRISF5          | TRISF4         | TRISF3   | TRISF2      | TRISF1                                    | TRISF0  | 90                              |

| F96h   | TRISE     | TRISE7        | TRISE6         | TRISE5          | TRISE4         | _        | TRISE2      | TRISE1                                    | TRISE0  | 90                              |

| F95h   | TRISD     | TRISD7        | TRISD6         | TRISD5          | TRISD4         | TRISD3   | TRISD2      | TRISD1                                    | TRISD0  | 90                              |

| F94h   | TRISC     | TRISC7        | TRISC6         | TRISC5          | TRISC4         | TRISC3   | TRISC2      | TRISC1                                    | TRISC0  | 90                              |

| F93h   | TRISB     | TRISB7        | TRISB6         | TRISB5          | TRISB4         | TRISB3   | TRISB2      | TRISB1                                    | TRISB0  | 90                              |

| F92h   | TRISA     | TRISA7        | TRISA6         | TRISA5          | _              | TRISA3   | TRISA2      | TRISA1                                    | TRISA0  | 90                              |

| F91h   | ODCON     | SSPOD         | CCP5OD         | CCP4OD          | CCP3OD         | CCP2OD   | CCP10D      | U2OD                                      | U10D    | 90                              |

| F90h   | SLRCON    | -             | SLRG           | SLRF            | SLRE           | SLRD     | SLRC        | SLRB                                      | SLRA    | 90                              |

| F8Fh   | LATG      | _             | SLNG           | JLINI           | LATG4          | LATG3    | LATG2       | LATG1                                     | LATG0   | 90                              |

|        |           | LATE7         | LATEC          | LATE            | LATG4          | LAIGS    |             |                                           |         |                                 |

| F8Eh   | LATE      | LATE7         | LATF6          | LATF5           |                | _        | LATF2       | LATF1                                     | LATF0   | 90                              |

| F8Dh   | LATE      | LATE7         | LATE6          | LATE5           | LATE4          |          | LATE2       | LATE1                                     | LATE0   | 90                              |

| F8Ch   | LATO      | LATD7         | LATD6          | LATD5           | LATD4          | LATD3    | LATD2       | LATD1                                     | LATD0   | 90                              |

| F8Bh   | LATC      | LATC7         | LATC6          | LATC5           | LATC4          | LATC3    | LATC2       | LATC1                                     | LATC0   | 90                              |

| F8Ah   | LATB      | LATB7         | LATB6          | LATB5           | LATB4          | LATB3    | LATB2       | LATB1                                     | LATB0   | 90                              |

| F89h   | LATA      | LATA7         | LATA6          | LATA5           | _              | LATA3    | LATA2       | LATA1                                     | LATA0   | 90                              |

| F88h   | T4CON     | _             | T4OUTPS3       | T4OUTPS2        | T4OUTPS1       | T4OUTPS0 | TMR4ON      | T4CKPS1                                   | T4CKPS0 | 90                              |

| F87h   | TMR4      | Timer4 Regis  | ter            |                 | 1              | Т        | Т           | 1                                         | 1       | 90                              |

| F86h   | PORTG     | _             | _              | _               | RG4            | RG3      | RG2         | RG1                                       | RG0     | 90                              |

| F85h   | PORTF     | RF7           | RF6            | RF5             | RF4            | RF3      | RF2         | RF1                                       | RF0     | 90                              |

| F84h   | PORTE     | RE7           | RE6            | RE5             | RE4            | RE3      | RE2         | RE1                                       | RE0     | 90                              |

| F83h   | PORTD     | RD7           | RD6            | RD5             | RD4            | RD3      | RD2         | RD1                                       | RD0     | 90                              |

| F82h   | PORTC     | RC7           | RC6            | RC5             | RC4            | RC3      | RC2         | RC1                                       | RC0     | 90                              |

| F81h   | PORTB     | RB7           | RB6            | RB5             | RB4            | RB3      | RB2         | RB1                                       | RB0     | 90                              |

| F80h   | PORTA     | RA7           | RA6            | RA5             | _              | RA3      | RA2         | RA1                                       | RA0     | 90                              |

| F7Fh   | EECON1    | EEPGD         | CFGS           | _               | FREE           | WRERR    | WREN        | WR                                        | RD      | 90                              |

| F7Eh   | EECON2    | Flash Self-Pr | ogram Control  | Register (not   | a physical reg | ister)   |             |                                           |         | 90                              |

| F7Dh   | SPBRGH1   | EUSART1 Ba    | aud Rate Gene  | erator Register | High Byte      |          |             |                                           |         | 90                              |

| F7Ch   | SPBRGH2   | EUSART2 Ba    | aud Rate Gene  | erator Register | High Byte      |          |             |                                           |         | 90                              |

| F7Bh   | SPBRG2    | EUSART2 Ba    | aud Rate Gene  | erator Register | Low Byte       |          |             |                                           |         | 90                              |

| F7Ah   | RCREG2    | EUSART2 Re    | eceive Registe | r               |                |          |             |                                           |         | 90                              |

| F79h   | TXREG2    | EUSART2 Tr    | ansmit Registe | er              |                |          |             |                                           |         | 91                              |

| F78h   | IPR5      | IRXIP         | WAKIP          | ERRIP           | TX2BIP         | TXB1IP   | TXB0IP      | RXB1IP                                    | RXB0IP  | 91                              |

| F77h   | PIR5      | IRXIF         | WAKIF          | ERRIF           | TXB2IF         | TXB1IF   | TXB0IF      | RXB1IF                                    | RXB0IF  | 91                              |

| F76H   | PIE5      | IRXIE         | WAKIE          | ERRIE           | TX2BIE         | TXB1IE   | TXB0IE      | RXB1IE                                    | RXB0IE  | 91                              |

| F75h   | EEADRH    |               | ress Register  |                 | 1              | 1        | 1           | 1                                         | 1       | 91                              |

| F74h   | EEADR     |               | ress Register  | • •             |                |          |             |                                           |         | 91                              |

| F73h   | EEDATA    | Data EE Data  |                |                 |                |          |             |                                           |         | 91                              |

| F72h   | ECANCON   | MDSEL1        | MDSEL0         | FIFOWM          | EWIN4          | EWIN3    | EWIN2       | EWIN1                                     | EWIN0   | 91                              |

| F71h   | COMSTAT   | RXB00VFL      | RXB10VFL       | TXBO            | TXBP           | RXBP     | TXWARN      | RXWARN                                    | EWARN   | 91                              |

| F70h   | CIOCON    | TX2SRC        | TX2EN          | ENDRHI          | CANCAP         | 10.01    |             |                                           | CLKSEL  | 91                              |

| F6Fh   | CANCON    | REQOP2        | REQOP1         | REQOP0          | ABAT           | WIN2/FP3 | WIN1/FP2    | WIN0/FP1                                  | FP0     | 91                              |

| F6Eh   | CANSTAT   | OPMODE2       | OPMODE1        | OPMODE0         | _/<br>ADA1     | ICODE2/  | ICODE1/     | ICODE0/                                   | —/      | 91                              |

| , OLII | OANO IAI  | OI WIODL2     | OI WODE!       | OI WIODEU       | EICOD4         | EICODE3  | EICODE2     | EICODE1                                   | EICODE0 | 91                              |

#### 8.0 DATA EEPROM MEMORY

The data EEPROM is a nonvolatile memory array, separate from the data RAM and program memory, that is used for long-term storage of program data. It is not directly mapped in either the register file or program memory space, but is indirectly addressed through the Special Function Registers (SFRs). The EEPROM is readable and writable during normal operation over the entire VDD range.

Five SFRs are used to read and write to the data EEPROM, as well as the program memory. They are:

- EECON1

- EECON2

- EEDATA

- EEADR

- EEADRH

The data EEPROM allows byte read and write. When interfacing to the data memory block, EEDATA holds the 8-bit data for read/write and the EEADRH:EEADR register pair holds the address of the EEPROM location being accessed.

The EEPROM data memory is rated for high erase/write cycle endurance. A byte write automatically erases the location and writes the new data (erase-before-write). The write time is controlled by an on-chip timer; it will vary with voltage and temperature, as well as from chip-to-chip. Please refer to Parameter D122 (Table 31-1 in Section 31.0 "Electrical Characteristics") for exact limits.

#### 8.1 EEADR and EEADRH Registers

The EEADRH:EEADR register pair is used to address the data EEPROM for read and write operations. EEADRH holds the two MSbs of the address; the upper 6 bits are ignored. The 10-bit range of the pair can address a memory range of 1024 bytes (00h to 3FFh).

#### 8.2 EECON1 and EECON2 Registers

Access to the data EEPROM is controlled by two registers: EECON1 and EECON2. These are the same registers which control access to the program memory and are used in a similar manner for the data EEPROM.

The EECON1 register (Register 8-1) is the control register for data and program memory access. Control bit, EEPGD, determines if the access will be to program memory or data EEPROM memory. When clear, operations will access the data EEPROM memory. When set, program memory is accessed.

Control bit, CFGS, determines if the access will be to the Configuration registers or to program memory/data EEPROM memory. When set, subsequent operations access Configuration registers. When CFGS is clear, the EEPGD bit selects either program Flash or data EEPROM memory.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WREN bit is set and cleared, when the internal programming timer expires and the write operation is complete.

Note: During normal operation, the WRERR is read as '1'. This can indicate that a write operation was prematurely terminated by a Reset, or a write operation was attempted improperly.

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software; it is cleared in hardware at the completion of the write operation.

**Note:** The EEIF interrupt flag bit (PIR4<6>) is set when the write is complete. It must be cleared in software.

Control bits, RD and WR, start read and erase/write operations, respectively. These bits are set by firmware and cleared by hardware at the completion of the operation.

The RD bit cannot be set when accessing program memory (EEPGD = 1). Program memory is read using table read instructions. See **Section 7.1** "**Table Reads and Table Writes**" regarding table reads.

The EECON2 register is not a physical register. It is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

#### 8.6 Operation During Code-Protect

Data EEPROM memory has its own code-protect bits in Configuration Words. External read and write operations are disabled if code protection is enabled.

The microcontroller itself can both read and write to the internal data EEPROM regardless of the state of the code-protect Configuration bit. Refer to Section 28.0 "Special Features of the CPU" for additional information.

#### 8.7 Protection Against Spurious Write

There are conditions when the device may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been implemented. On power-up, the WREN bit is cleared. In addition, writes to the EEPROM are blocked during the Power-up Timer period (TPWRT, Parameter 33).

The write initiate sequence, and the WREN bit together, help prevent an accidental write during brown-out, power glitch or software malfunction.

#### 8.8 Using the Data EEPROM

The data EEPROM is a high-endurance, byte-addressable array that has been optimized for the storage of frequently changing information (e.g., program variables or other data that are updated often). Frequently changing values will typically be updated more often than Parameter D124. If this is not the case, an array refresh must be performed. For this reason, variables that change infrequently (such as constants, IDs, calibration, etc.) should be stored in Flash program memory.

A simple data EEPROM refresh routine is shown in Example 8-3.

**Note:** If data EEPROM is only used to store constants and/or data that changes often, an array refresh is likely not required. See Parameter D124.

#### **EXAMPLE 8-3:** DATA EEPROM REFRESH ROUTINE

```

; Start at address 0

CLRF

EEADR

CLRF

EEADRH

EECON1, CFGS

BCF

; Set for memory

EECON1, EEPGD

; Set for Data EEPROM

BCF

BCF

INTCON, GIE

; Disable interrupts

EECON1, WREN

; Enable writes

LOOP

; Loop to refresh array

EECON1, RD

RSF

; Read current address

MOVLW

55h

; Write 55h

MOVWF

EECON2

MOVLW

0AAh

EECON2

; Write OAAh

MOVWF

EECON1, WR

BSF

; Set WR bit to begin write

BTFSC

EECON1, WR

; Wait for write to complete

BRA

$-2

INCFSZ EEADR, F

; Increment address

BRA

LOOP

; Not zero, do it again

INCFSZ EEADRH, F

; Increment the high address

TIOOP

; Not zero, do it again

BRA

BCF

EECON1, WREN

; Disable writes

; Enable interrupts

BSF

INTCON, GIE

```

#### REGISTER 10-6: PIR3: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 3

| U-0   | U-0 | R-0   | R-0   | R/W-0  | R/W-0  | R/W-0  | U-0   |

|-------|-----|-------|-------|--------|--------|--------|-------|

| _     | _   | RC2IF | TX2IF | CTMUIF | CCP2IF | CCP1IF | _     |

| bit 7 |     |       |       |        |        |        | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-6 **Unimplemented:** Read as '0'

bit 5 RC2IF: EUSARTx Receive Interrupt Flag bit

1 = The EUSARTx receive buffer, RCREG2, is full (cleared when RCREG2 is read)

0 = The EUSARTx receive buffer is empty

bit 4 **TX2IF:** EUSARTx Transmit Interrupt Flag bit

1 = The EUSARTx transmit buffer, TXREG2, is empty (cleared when TXREG2 is written)

0 = The EUSARTx transmit buffer is full

bit 3 CTMUIF: CTMU Interrupt Flag bit

1 = CTMU interrupt occurred (must be cleared in software)

0 = No CTMU interrupt occurred

bit 2 CCP2IF: CCP2 Interrupt Flag bit

Capture mode:

1 = A TMR1/TMR3 register capture occurred (must be cleared in software)

0 = No TMR1/TMR3 register capture occurred

Compare mode:

1 = A TMR1/TMR3 register compare match occurred (must be cleared in software)

0 = No TMR1/TMR3 register compare match occurred

PWM mode:

Unused in this mode.

bit 1 CCP1IF: ECCP1 Interrupt Flag bit

Capture mode

1 = A TMR1/TMR3 register capture occurred (must be cleared in software)

0 = No TMR1/TMR3 register capture occurred

Compare mode:

1 = A TMR1/TMR3 register compare match occurred (must be cleared in software)

0 = No TMR1/TMR3 register compare match occurred

PWM mode:

Unused in this mode.

bit 0 **Unimplemented:** Read as '0'

#### REGISTER 12-1: MDCON: MODULATION CONTROL REGISTER

| R/W-0 | R/W-0 | R/W-1 | R/W-0  | R/W-0 | U-0 | U-0 | R/W-0 |

|-------|-------|-------|--------|-------|-----|-----|-------|

| MDEN  | MDOE  | MDSLR | MDOPOL | MDO   | _   | _   | MDBIT |

| bit 7 |       |       |        |       |     |     | bit 0 |

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

-n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

bit 7 MDEN: Modulator Module Enable bit 1 = Modulator module is enabled and mixing input signals 0 = Modulator module is disabled and has no output bit 6 MDOE: Modulator Module Pin Output Enable bit 1 = Modulator pin output is enabled 0 = Modulator pin output is disabled MDSLR: MDOUT Pin Slew Rate Limiting bit bit 5 1 = MDOUT pin slew rate limiting is enabled 0 = MDOUT pin slew rate limiting is disabled bit 4 MDOPOL: Modulator Output Polarity Select bit 1 = Modulator output signal is inverted 0 = Modulator output signal is not inverted bit 3 MDO: Modulator Output bit Displays the current output value of the modulator module. (2) bit 2-1 Unimplemented: Read as '0' bit 0 MDBIT: Modulator Source Input bit Allows software to manually set modulation source input to module. (1)

**Note 1:** The MDBIT must be selected as the modulation source in the MDSRC register for this operation.

**2:** The modulated output frequency can be greater and asynchronous from the clock that updates this register bit. The bit value may not be valid for higher speed modulator or carrier signals.

#### 14.4 Timer1 16-Bit Read/Write Mode

Timer1 can be configured for 16-bit reads and writes. When the RD16 control bit (T1CON<1>) is set, the address for TMR1H is mapped to a buffer register for the high byte of Timer1. A read from TMR1L loads the contents of the high byte of Timer1 into the Timer1 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer1 must also take place through the TMR1H Buffer register. The Timer1 high byte is updated with the contents of TMR1H when a write occurs to TMR1L. This allows a user to write all 16 bits at once to both the high and low bytes of Timer1.

The high byte of Timer1 is not directly readable or writable in this mode. All reads and writes must take place through the Timer1 High Byte Buffer register. Writes to TMR1H do not clear the Timer1 prescaler. The prescaler is only cleared on writes to TMR1L.

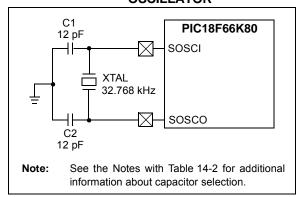

#### 14.5 SOSC Oscillator

An on-chip crystal oscillator circuit is incorporated between pins, SOSCI (input) and SOSCO (amplifier output). It can be enabled one of these ways:

- Setting the SOSCEN bit in either the T1CON or T3CON register (TxCON<3>)

- Setting the SOSCGO bit in the OSCCON2 register (OSCCON2<3>)

- Setting the SCSx bits to secondary clock source in the OSCCON register (OSCCON<1:0> = 01)

The SOSCGO bit is used to warm up the SOSC so that it is ready before any peripheral requests it.

The oscillator is a low-power circuit rated for 32 kHz crystals. It will continue to run during all power-managed modes. The circuit for a typical low-power oscillator is depicted in Figure 14-2. Table 14-2 provides the capacitor selection for the SOSC oscillator.

The user must provide a software time delay to ensure proper start-up of the SOSC oscillator.

# FIGURE 14-2: EXTERNAL COMPONENTS FOR THE SOSC OSCILLATOR

TABLE 14-2: CAPACITOR SELECTION FOR THE TIMER OSCILLATOR<sup>(2,3,4,5)</sup>

| Oscillator<br>Type | Freq.  | C1                   | C2                   |

|--------------------|--------|----------------------|----------------------|

| LP                 | 32 kHz | 12 pF <sup>(1)</sup> | 12 pF <sup>(1)</sup> |

- Note 1: Microchip suggests these values as a starting point in validating the oscillator circuit.

- 2: Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

- **3:** Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Capacitor values are for design guidance only. Values listed would be typical of a CL = 10 pF rated crystal, when SOSCSEL<1:0> = 11.

- 5: Incorrect capacitance value may result in a frequency not meeting the crystal manufacturer's tolerance specification.

The SOSC crystal oscillator drive level is determined based on the SOSCSELx (CONFIG1L<4:3>) Configuration bits. The Higher Drive Level mode, SOSCSEL<1:0> = 11, is intended to drive a wide variety of 32.768 kHz crystals with a variety of Load Capacitance (CL) ratings.

The Lower Drive Level mode is highly optimized for extremely low-power consumption. It is not intended to drive all types of 32.768 kHz crystals. In the Low Drive Level mode, the crystal oscillator circuit may not work correctly if excessively large discrete capacitors are placed on the SOSCO and SOSCI pins. This mode is designed to work only with discrete capacitances of approximately 3 pF-10 pF on each pin.

Crystal manufacturers usually specify a CL (Load Capacitance) rating for their crystals. This value is related to, but not necessarily the same as, the values that should be used for C1 and C2 in Figure 14-2.

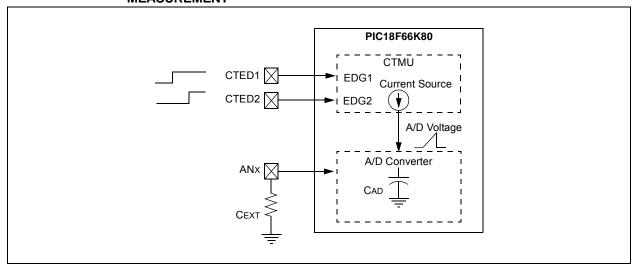

# 18.6 Measuring Time with the CTMU Module

Time can be precisely measured after the ratio (C/I) is measured from the current and capacitance calibration step. To do that:

- 1. Initialize the A/D Converter and the CTMU.

- 2. Set EDG1STAT.

- 3. Set EDG2STAT.

- Perform an A/D conversion.

- Calculate the time between edges as T = (C/I) \* V, where:

- I is calculated in the current calibration step (Section 18.4.1 "Current Source Calibration")

- C is calculated in the capacitance calibration step (Section 18.4.2 "Capacitance Calibration")

- · V is measured by performing the A/D conversion

It is assumed that the time measured is small enough that the capacitance,  ${\rm CAD} + {\rm CEXT}$ , provides a valid voltage to the A/D Converter. For the smallest time measurement, always set the A/D Channel Select bits CHS<4:0> (ADCON0<6:2>) to an unused A/D channel, the corresponding pin for which is not connected to any circuit board trace. This minimizes added stray capacitance, keeping the total circuit capacitance close to that of the A/D Converter itself (25 pF).

To measure longer time intervals, an external capacitor may be connected to an A/D channel and that channel selected whenever making a time measurement.

FIGURE 18-3: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR TIME MEASUREMENT

# 20.4.8 OPERATION IN POWER-MANAGED MODES

In Sleep mode, all clock sources are disabled. Timer2/4 will not increment and the state of the module will not change. If the ECCP1 pin is driving a value, it will continue to drive that value. When the device wakes up, it will continue from this state. If Two-Speed Start-ups are enabled, the initial start-up frequency from HF-INTOSC and the postscaler may not be stable immediately.

In PRI\_IDLE mode, the primary clock will continue to clock the ECCP1 module without change.

# 20.4.8.1 Operation with Fail-Safe Clock Monitor (FSCM)

If the Fail-Safe Clock Monitor (FSCM) is enabled, a clock failure will force the device into the power-managed RC\_RUN mode and the OSCFIF bit of the PIR2 register will be set. The ECCP1 will then be clocked from the internal oscillator clock source, which may have a different clock frequency than the primary clock.

#### 20.4.9 EFFECTS OF A RESET

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the ECCP registers to their Reset states.

This forces the ECCP module to reset to a state compatible with previous, non-enhanced CCP modules used on other PIC18 and PIC16 devices.

#### 21.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

#### 21.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be devices such as serial EEPROMs, shift registers, display drivers and A/D Converters. The MSSP module can operate in either of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C™)

- Full Master mode

- Slave mode (with general address call)

The I<sup>2</sup>C interface supports the following modes in hardware:

- · Master mode

- · Multi-Master mode

- Slave mode with 5-bit and 7-bit address masking (with address masking for both 10-bit and 7-bit addressing)

#### 21.2 Control Registers

The MSSP module has three associated control registers. These include a status register (SSPSTAT) and two control registers (SSPCON1 and SSPCON2). The use of these registers and their individual configuration bits differ significantly depending on whether the MSSP module is operated in SPI or  $I^2C$  mode.

Additional details are provided under the individual sections.

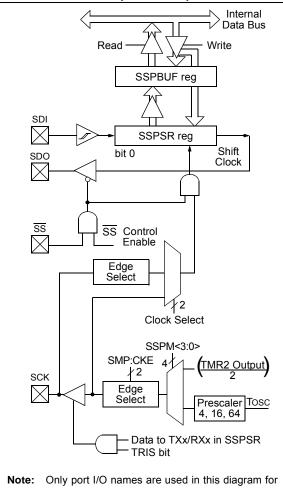

#### 21.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- · Serial Data In (SDI) RC4/SDA/SDI

- Serial Clock (SCK) RC3/REF0/SCL/SCK

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS) – RA5/AN4/C2INB/ HLVDIN/T1CKI/SS/CTMU1

Figure 21-1 shows the block diagram of the MSSP module when operating in SPI mode.

FIGURE 21-1: MSSP BLOCK DIAGRAM (SPI MODE)

**Note:** Only port I/O names are used in this diagram for the sake of brevity. Refer to the text for a full list of multiplexed functions.

#### 21.4.3.2 Address Masking Modes

Masking an address bit causes that bit to become a "don't care". When one address bit is masked, two addresses will be Acknowledged and cause an interrupt. It is possible to mask more than one address bit at a time, which greatly expands the number of addresses Acknowledged.

The  $I^2C$  slave behaves the same way, whether address masking is used or not. However, when address masking is used, the  $I^2C$  slave can Acknowledge multiple addresses and cause interrupts. When this occurs, it is necessary to determine which address caused the interrupt by checking the SSPBUF.

The PIC18F66K80 family of devices is capable of using two different Address Masking modes in I<sup>2</sup>C slave operation: 5-Bit Address Masking and 7-Bit Address Masking. The Masking mode is selected at device configuration using the MSSPMSK Configuration bit. The default device configuration is 7-Bit Address Masking.

Both Masking modes, in turn, support address masking of 7-bit and 10-bit addresses. The combination of Masking modes and addresses provide different ranges of Acknowledgable addresses for each combination.

While both Masking modes function in roughly the same manner, the way they use address masks are different.

#### 21.4.3.3 5-Bit Address Masking Mode

As the name implies, 5-Bit Address Masking mode uses an address mask of up to 5 bits to create a range of addresses to be Acknowledged, using bits, 5 through 1,

of the incoming address. This allows the module to Acknowledge up to 31 addresses when using 7-bit addressing, or 63 addresses with 10-bit addressing (see Example 21-2). This Masking mode is selected when the MSSPMSK Configuration bit is programmed ('0').

The address mask in this mode is stored in the SSPCON2 register, which stops functioning as a control register in I<sup>2</sup>C Slave mode (Register 21-6). In 7-Bit Addressing mode, address mask bits, ADMSK<5:1> (SSPCON2<5:1>), mask the corresponding address bits in the SSPADD register. For any ADMSKx bits that are set (ADMSK<n> = 1), the corresponding address bit is ignored (SSPADD<n> = x). For the module to issue an address Acknowledge, it is sufficient to match only on addresses that do not have an active address mask.

In 10-Bit Addressing mode, bits, ADMSK<5:2>, mask the corresponding address bits in the SSPADD register. In addition, ADMSK1 simultaneously masks the two LSbs of the address (SSPADD<1:0>). For any ADMSKx bits that are active (ADMSK<n> = 1), the corresponding address bit is ignored (SPxADD<n> = x). Also note that although in 10-Bit Addressing mode, the upper address bits reuse part of the SSPADD register bits. The address mask bits do not interact with those bits; they only affect the lower address bits.

- **Note 1:** ADMSK1 masks the two Least Significant bits of the address.

- 2: The two Most Significant bits of the address are not affected by address masking.

#### EXAMPLE 21-2: ADDRESS MASKING EXAMPLES IN 5-BIT MASKING MODE

#### 7-Bit Addressing:

SSPADD<7:1>= A0h (1010000) (SSPADD<0> is assumed to be '0')

ADMSK < 5:1 > = 00111

Addresses Acknowledged: A0h, A2h, A4h, A6h, A8h, AAh, ACh, AEh

#### 10-Bit Addressing:

SSPADD<7:0> = A0h (10100000) (The two MSb of the address are ignored in this example, since they are not affected by masking)

ADMSK<5:1> = 00111

Addresses Acknowledged: A0h, A1h, A2h, A3h, A4h, A5h, A6h, A7h, A8h, A9h, AAh, ABh, ACh, ADh, AEh, AFh

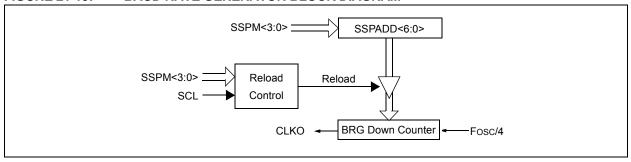

#### 21.4.7 BAUD RATE

In I<sup>2</sup>C Master mode, the Baud Rate Generator (BRG) reload value is placed in the 8 bits of the SSPADD register (Figure 21-19). When a write occurs to SSPBUF, the Baud Rate Generator will automatically begin counting. The BRG counts down to 0 and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (TcY) on the Q2 and Q4 clocks. In I<sup>2</sup>C Master mode, the BRG is reloaded automatically.

Once the given operation is complete (i.e., transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCL pin will remain in its last state.

Table 21-3 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPADD. The SSPADD BRG value of 00h is not supported.

FIGURE 21-19: BAUD RATE GENERATOR BLOCK DIAGRAM

TABLE 21-3: I<sup>2</sup>C™ CLOCK RATE w/BRG

|                       |        | _       |           |                           |

|-----------------------|--------|---------|-----------|---------------------------|

| Fosc                  | FcY    | Fcy * 2 | BRG Value | FSCL (2 Rollovers of BRG) |

| 40 MHz                | 10 MHz | 20 MHz  | 18h       | 400 kHz <sup>(1)</sup>    |

| 40 MHz                | 10 MHz | 20 MHz  | 1Fh       | 312.5 kHz                 |

| 40 MHz                | 10 MHz | 20 MHz  | 63h       | 100 kHz                   |

| 16 MHz                | 4 MHz  | 8 MHz   | 09h       | 400 kHz <sup>(1)</sup>    |

| 16 MHz                | 4 MHz  | 8 MHz   | 0Ch       | 308 kHz                   |

| 16 MHz                | 4 MHz  | 8 MHz   | 27h       | 100 kHz                   |

| 4 MHz                 | 1 MHz  | 2 MHz   | 02h       | 333 kHz <sup>(1)</sup>    |

| 4 MHz                 | 1 MHz  | 2 MHz   | 09h       | 100 kHz                   |

| 16 MHz <sup>(2)</sup> | 4 MHz  | 8 MHz   | 03h       | 1 MHz <sup>(1)</sup>      |

**Note 1:** The I<sup>2</sup>C interface does not conform to the 400 kHz I<sup>2</sup>C specification (which applies to rates greater than 100 kHz) in all details, but may be used with care where higher rates are required by the application.

2: A minimum 16-MHz Fosc is required for 1 MHz I<sup>2</sup>C.

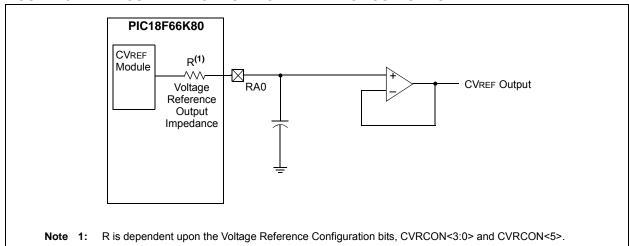

#### FIGURE 25-2: COMPARATOR VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

TABLE 25-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| CVRCON | CVREN  | CVROE  | CVRSS  | CVR4   | CVR3   | CVR2   | CVR1   | CVR0   |

| CM1CON | CON    | COE    | CPOL   | EVPOL1 | EVPOL0 | CREF   | CCH1   | CCH0   |

| CM2CON | CON    | COE    | CPOL   | EVPOL1 | EVPOL0 | CREF   | CCH1   | CCH0   |

| TRISA  | TRISA7 | TRISA6 | TRISA5 | _      | TRISA3 | TRISA2 | TRISA1 | TRISA0 |

| ANCON0 | ANSEL7 | ANSEL6 | ANSEL5 | ANSEL4 | ANSEL3 | ANSEL2 | ANSEL1 | ANSEL0 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used with the comparator voltage reference.

DS39977F-page 392

#### 27.2.4 CAN BAUD RATE REGISTERS

This section describes the CAN Baud Rate registers.

**Note:** These registers are writable in Configuration mode only.

#### **REGISTER 27-52: BRGCON1: BAUD RATE CONTROL REGISTER 1**

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SJW1  | SJW0  | BRP5  | BRP4  | BRP3  | BRP2  | BRP1  | BRP0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | I as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

```

bit 7-6 SJW<1:0>: Synchronized Jump Width bits 11 = \text{Synchronization jump width time} = 4 \times TQ 10 = \text{Synchronization jump width time} = 3 \times TQ 01 = \text{Synchronization jump width time} = 2 \times TQ 00 = \text{Synchronization jump width time} = 1 \times TQ bit 5-0 BRP<5:0>: Baud Rate Prescaler bits 111111 = TQ = (2 \times 64)/FOSC 111110 = TQ = (2 \times 63)/FOSC : \vdots 000001 = TQ = (2 \times 2)/FOSC 000000 = TQ = (2 \times 1)/FOSC

```

**BRA Unconditional Branch**

Syntax: BRA n

Operands:  $\text{-}1024 \leq n \leq 1023$  $(PC) + 2 + 2n \rightarrow PC$ Operation:

Status Affected: None

Encoding: 1101 0nnn nnnn nnnn

Add the 2's complement number, '2n', Description:

to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is a

two-cycle instruction.

Words: 1 2 Cycles:

Q Cycle Activity:

| Q1        | Q2               | Q3              | Q4             |

|-----------|------------------|-----------------|----------------|

| Decode    | Read literal 'n' | Process<br>Data | Write to<br>PC |

| No        | No               | No              | No             |

| operation | operation        | operation       | operation      |

Example: HERE BRA Jump

Before Instruction

PC address (HERE)

After Instruction

PC address (Jump)

| BSF              | Bit Set f                                             |               |        |      |  |  |  |

|------------------|-------------------------------------------------------|---------------|--------|------|--|--|--|

| Syntax:          | BSF f, b                                              | BSF f, b {,a} |        |      |  |  |  |

| Operands:        | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0,1]$ |               |        |      |  |  |  |

| Operation:       | $1 \rightarrow \text{f}$                              |               |        |      |  |  |  |

| Status Affected: | None                                                  |               |        |      |  |  |  |

| Encoding:        | 1000                                                  | bbba          | ffff   | ffff |  |  |  |

| Description:     | Bit 'b' in re                                         | gister 'f' is | s set. |      |  |  |  |

If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the

GPR bank.

If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever  $f \le 95$  (5Fh). See Section 29.2.3 "Byte-Oriented and **Bit-Oriented Instructions in Indexed** Literal Offset Mode" for details.

Words: Cycles:

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

Example: BSF FLAG\_REG, 7, 1

Before Instruction

FLAG\_REG 0Ah

After Instruction

FLAG\_REG 8Ah

# 30.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

# 30.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

#### 30.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

#### 30.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 30.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command line interface

- · Rich directive set

- · Flexible macro language

- MPLAB IDE compatibility

#### 30.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC® DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 30.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 30.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC® Flash microcontrollers and dsPIC® DSCs with the powerful, yet easy-to-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 30.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming ™.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

#### PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, such as pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                | <u> </u>                                    | /XX                                                   | <u>xxx</u>                                                   | Ex       | ample                                                                                                                                           | es:                                                                                         |

|-------------------------|---------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Device                  | Temperature<br>Range                        | Package                                               | Pattern                                                      | a)<br>b) | PIC18F66K80-I/MR 301 = Industrial temp.,<br>QFN package, Extended VDD limits, QTP<br>pattern #301.<br>PIC18F66K80-I/PT = Industrial temp., TQFP |                                                                                             |

| Device <sup>(1,2)</sup> | PIC18F65K80, F<br>VDD range 1.8             | PIC18F66K80<br>BV to 5V<br>PIC18LF26K8<br>PIC18F65K80 | PIC18F45K80, PIC18F46<br>80, PIC18LF45K80,<br>0, PIC18F66K80 |          |                                                                                                                                                 | rage, Extended VDD limits.                                                                  |

| Temperature Range       |                                             | C to +85°C<br>C to +125°C                             | (Industrial)<br>(Extended)                                   |          |                                                                                                                                                 |                                                                                             |

| Package                 | ML = QFI<br>SO = SO<br>SP = SPI<br>SS = SSO | IC Plastic Sma<br>DIP Skinny Pla<br>OP Plastic Shi    | d Flat, No Lead Package                                      | No       | ote 1:<br>2:                                                                                                                                    | F = Standard Voltage Range LF = Low Voltage Range T = in tape and reel, TQFP packages only. |

| Pattern                 | a) QTP, SQT<br>(blank othe                  |                                                       | ecial Requirements                                           |          |                                                                                                                                                 |                                                                                             |