Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | SH2A                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 100MHz                                                                             |

| Connectivity               | SCI                                                                                |

| Peripherals                | DMA, PWM, WDT                                                                      |

| Number of I/O              | 63                                                                                 |

| Program Memory Size        | 128KB (128K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 8K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                          |

| Data Converters            | A/D 8x12b                                                                          |

| Oscillator Type            | External                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 100-LQFP                                                                           |

| Supplier Device Package    | 100-LFQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f72433d100fp-u0 |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|       | 11.7.16   | Overflow Flags in Reset Synchronous PWM Mode                          | 654 |

|-------|-----------|-----------------------------------------------------------------------|-----|

|       | 11.7.17   | Contention between Overflow/Underflow and Counter Clearing            | 655 |

|       | 11.7.18   | Contention between TCNT Write and Overflow/Underflow                  | 656 |

|       | 11.7.19   | Cautions on Transition from Normal Operation or PWM Mode 1 to         |     |

|       |           | Reset-Synchronized PWM Mode                                           | 656 |

|       | 11.7.20   | Output Level in Complementary PWM Mode and Reset-Synchronized         |     |

|       |           | PWM Mode                                                              | 657 |

|       | 11.7.21   | Interrupts in Module Standby Mode                                     | 657 |

|       | 11.7.22   | Simultaneous Capture of TCNT_1 and TCNT_2 in Cascade Connection       | 657 |

|       | 11.7.23   | Note on Output Waveform Control at Synchronous Counter Clearing in    |     |

|       |           | Complementary PWM Mode                                                | 658 |

| 11.8  | MTU2 C    | Dutput Pin Initialization                                             | 660 |

|       | 11.8.1    | Operating Modes                                                       | 660 |

|       | 11.8.2    | Reset Start Operation                                                 | 660 |

|       | 11.8.3    | Operation in Case of Re-Setting Due to Error during Operation, etc    | 661 |

|       | 11.8.4    | Overview of Initialization Procedures and Mode Transitions in Case of |     |

|       |           | Error during Operation, etc.                                          | 662 |

|       |           |                                                                       |     |

| Secti | on 12 M   | Multi-Function Timer Pulse Unit 2S (MTU2S)                            | 693 |

| 12.1  |           | ıtput Pins                                                            |     |

| 12.2  | Register  | Descriptions                                                          | 697 |

| Cast  | ат 12 Г   | Deat Outrout England (DOE2)                                           | 701 |

|       |           | Port Output Enable 2 (POE2)                                           |     |

| 13.1  |           |                                                                       |     |

| 13.2  |           | itput Pins                                                            |     |

| 13.3  | -         | Descriptions                                                          |     |

|       | 13.3.1    | Input Level Control/Status Register 1 (ICSR1)                         |     |

|       | 13.3.2    | Output Level Control/Status Register 1 (OCSR1)                        |     |

|       | 13.3.3    | Input Level Control/Status Register 2 (ICSR2)                         |     |

|       | 13.3.4    | Output Level Control/Status Register 2 (OCSR2)                        |     |

|       | 13.3.5    | Input Level Control/Status Register 3 (ICSR3)                         |     |

|       | 13.3.6    | Software Port Output Enable Register (SPOER)                          |     |

|       | 13.3.7    | Port Output Enable Control Register 1 (POECR1)                        |     |

|       | 13.3.8    | Port Output Enable Control Register 2 (POECR2)                        |     |

| 13.4  | -         | n                                                                     |     |

|       | 13.4.1    | Input Level Detection Operation                                       |     |

|       | 13.4.2    | Output-Level Compare Operation                                        |     |

|       | 13.4.3    | Release from High-Impedance State                                     |     |

| 13.5  | Interrupt | S                                                                     | 731 |

| 13.6  | Usage N   | otes                                                                  | 732 |

#### Page xviii of xxx

# RENESAS

| Classification | Symbol       | I/O    | Name                         | Function                                                                                                                                                                                                           |

|----------------|--------------|--------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupts     | NMI          | Input  | Non-maskable<br>interrupt    | Non-maskable interrupt request pin.<br>Fix it high when not in use.                                                                                                                                                |

|                | IRQ7 to IRQ0 | Input  | Interrupt<br>requests 7 to 0 | Maskable interrupt request pins.<br>Level-input or edge-input detection<br>can be selected. When the edge-input<br>detection is selected, the rising edge,<br>falling edge, or both edges can also<br>be selected. |

|                | IRQOUT       | Output | Interrupt request<br>output  | Indicates that an interrupt has<br>occurred, enabling external devices to<br>be informed of an interrupt occurrence<br>even while the bus mastership is<br>released.                                               |

| Address bus    | A25 to A0    | Output | Address bus                  | Outputs addresses. (A25 to A21 are available only in the SH7286.)                                                                                                                                                  |

| Data bus       | D31 to D0    | I/O    | Data bus                     | Bidirectional data bus. (D31 to D16 are available only in the SH7286.)                                                                                                                                             |

| Bus control    | CS7 to CS0   | Output | Chip select 7<br>to 0        | Chip-select signals for external memory or devices.                                                                                                                                                                |

|                | RD           | Output | Read                         | Indicates that data is read from an external device.                                                                                                                                                               |

|                | RD/WR        | Output | Read/write                   | Read/write signal.                                                                                                                                                                                                 |

|                | BS           | Output | Bus start                    | Bus-cycle start signal.                                                                                                                                                                                            |

|                | ĀH           | Output | Address hold                 | Address hold timing signal for the device that uses the address/data-<br>multiplexed bus.                                                                                                                          |

|                | FRAME        | Output | Frame signal                 | In burst MPX-I/O interface mode,<br>negated before the last bus cycle to<br>indicate that the next bus cycle is the<br>last access (only in SH7286)                                                                |

|                | WAIT         | Input  | Wait                         | Input signal for inserting a wait cycle<br>into the bus cycles during access to<br>the external space.                                                                                                             |

|                | WRHH         | Output | Write to HH byte             | Indicates a write access to bits 31 to 24 of data of external memory or device (only in SH7286).                                                                                                                   |

|                | WRHL         | Output | Write to HL byte             | Indicates a write access to bits 23 to<br>16 of data of external memory or<br>device (only in SH7286).                                                                                                             |

# 7.3.9 Break Bus Cycle Register\_2 (BBR\_2)

BBR\_2 is a 16-bit readable/writable register, which specifies (1) disabling or enabling of user break interrupts, (2) including or excluding of the data bus value, (3) bus master of the I bus, (4) C bus cycle or I bus cycle, (5) instruction fetch or data access, (6) read or write, and (7) operand size as the break conditions of channel 2. BBR\_2 is initialized to H'0000 by a power-on reset, but retains its previous value by a manual reset or in software standby mode or sleep mode.

| Bit:           | 15 | 14 | 13    | 12 | 11 | 10  | 9       | 8   | 7   | 6      | 5   | 4     | 3   | 2      | 1   | 0     |

|----------------|----|----|-------|----|----|-----|---------|-----|-----|--------|-----|-------|-----|--------|-----|-------|

|                | -  | -  | UBID2 | -  | -  |     | CP2[2:0 | ]   | CD2 | 2[1:0] | ID2 | [1:0] | RW2 | 2[1:0] | SZ2 | [1:0] |

| Initial value: | 0  | 0  | 0     | 0  | 0  | 0   | 0       | 0   | 0   | 0      | 0   | 0     | 0   | 0      | 0   | 0     |

| R/W:           | R  | R  | R/W   | R  | R  | R/W | R/W     | R/W | R/W | R/W    | R/W | R/W   | R/W | R/W    | R/W | R/W   |

| Bit     | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                            |

|---------|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15, 14  |          | All 0            | R   | Reserved                                                                                                                                                                               |

|         |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                                                   |

| 13      | UBID2    | 0                | R/W | User Break Interrupt Disable 2                                                                                                                                                         |

|         |          |                  |     | Disables or enables user break interrupt requests when a channel-2 break condition is satisfied.                                                                                       |

|         |          |                  |     | 0: User break interrupt requests enabled                                                                                                                                               |

|         |          |                  |     | 1: User break interrupt requests disabled                                                                                                                                              |

| 12, 11  | _        | All 0            | R   | Reserved                                                                                                                                                                               |

|         |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                                                   |

| 10 to 8 | CP2[2:0] | 000              | R/W | I-Bus Bus Master Select 2                                                                                                                                                              |

|         |          |                  |     | Select the bus master when the bus cycle of the channel-2 break condition is the I bus cycle. However, when the C bus cycle is selected, this bit is invalidated (only the CPU cycle). |

|         |          |                  |     | xx1: CPU cycle is included in break conditions                                                                                                                                         |

|         |          |                  |     | x1x: DMAC cycle is included in break conditions                                                                                                                                        |

|         |          |                  |     | 1xx: DTC cycle is included in break conditions                                                                                                                                         |

# Section 9 Bus State Controller (BSC)

The bus state controller (BSC) outputs control signals for various types of memory that is connected to the external address space and external devices. BSC functions enable this LSI to connect directly with SRAM, SDRAM, and other memory storage devices, and external devices.

# 9.1 Features

The BSC has the following features.

- 1. External address space

- A maximum of 64 Mbytes for each of areas CS0 to CS7.

- Can specify the normal space interface, SRAM interface with byte selection, burst ROM (clock synchronous or asynchronous), MPX-I/O, and SDRAM for each address space.

- Can select the data bus width (8, 16, or 32 bits) for each address space.

- Controls insertion of wait cycles for each address space.

- Controls insertion of wait cycles for each read access and write access.

- Can set independent idle cycles during the continuous access for five cases: read-write (in same space/different spaces), read-read (in same space/different spaces), the first cycle is a write access.

- 2. Normal space interface

- Supports the interface that can directly connect to the SRAM.

- 3. Burst ROM interface (clock asynchronous)

- High-speed access to the ROM that has the page mode function.

- 4. MPX-I/O interface

- Can directly connect to a peripheral LSI that needs an address/data multiplexing.

- 5. SDRAM interface

- Can set the SDRAM in up to two areas.

- Multiplex output for row address/column address.

- Efficient access by single read/single write.

- High-speed access in bank-active mode.

- Supports an auto-refresh and self-refresh.

- Supports low-frequency and power-down modes.

- Issues MRS and EMRS commands.

| Table 9.2 | Address Map in On-Chip ROM-Enabled Mode |

|-----------|-----------------------------------------|

|-----------|-----------------------------------------|

| Address                    | Space       | Memory to be Connected                                                             | Size                                                                     |

|----------------------------|-------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| H'0000 0000 to H'000F FFFF | On-chip ROM | On-chip ROM                                                                        | 256 Kbytes<br>(SH7243)<br>768 Kbytes<br>(SH7285)<br>1 Mbytes<br>(SH7286) |

| H'0070 0000 to H'01FF FFFF | Other       | Reserved area                                                                      | _                                                                        |

| H'0200 0000 to H'03FF FFFF | CS0         | Normal space, SRAM with byte selection,<br>burst ROM (asynchronous or synchronous) | 32 Mbytes                                                                |

| H'0400 0000 to H'07FF FFFF | CS1         | Normal space, SRAM with byte selection                                             | 64 Mbytes                                                                |

| H'0800 0000 to H'0BFF FFFF | CS2         | Normal space, SRAM with byte selection, SDRAM                                      | 64 Mbytes                                                                |

| H'0C00 0000 to H'0FFF FFFF | CS3         | Normal space, SRAM with byte selection, SDRAM                                      | 64 Mbytes                                                                |

| H'1000 0000 to H'13FF FFFF | CS4         | Normal space, SRAM with byte selection, burst ROM (asynchronous)                   | 64 Mbytes                                                                |

| H'1400 0000 to H'17FF FFFF | CS5         | Normal space, SRAM with byte selection, MPX-I/O                                    | 64 Mbytes                                                                |

| H'1800 0000 to H'1BFF FFFF | CS6         | Normal space, SRAM with byte selection                                             | 64 Mbytes                                                                |

| H'1C00 0000 to H'1FFF FFFF | CS7         | Normal space, SRAM with byte selection                                             | 64 Mbytes                                                                |

| H'2000 0000 to H'FFF7 FFFF | Other       | Reserved area                                                                      |                                                                          |

| H'FFF8 0000 to H'FFFB FFFF | Other       | On-chip RAM, reserved area*                                                        | _                                                                        |

| H'FFFC 0000 to H'FFFF FFFF | Other       | On-chip peripheral modules, reserved area*                                         |                                                                          |

Note: \* For the on-chip RAM space, access the addresses shown in section 27, On-Chip RAM. For the on-chip peripheral module space, access the addresses shown in section 30, List of Registers. Do not access addresses which are not described in these sections. Otherwise, the correct operation cannot be guaranteed.

### 9.4.1 Common Control Register (CMNCR)

CMNCR is a 32-bit register that controls the common items for each area. This register is initialized to H'00001010 by a power-on reset and retains the value by a manual reset and in software standby mode.

| Bit:           | 31 | 30 | 29 | 28 | 27    | 26   | 25     | 24  | 23      | 22  | 21         | 20 | 19 | 18          | 17         | 16         |

|----------------|----|----|----|----|-------|------|--------|-----|---------|-----|------------|----|----|-------------|------------|------------|

|                | -  | -  | -  | -  | -     | -    | -      | -   | -       | -   | -          | -  | -  | -           | -          | -          |

| Initial value: | 0  | 0  | 0  | 0  | 0     | 0    | 0      | 0   | 0       | 0   | 0          | 0  | 0  | 0           | 0          | 0          |

| R/W:           | R  | R  | R  | R  | R     | R    | R      | R   | R       | R   | R          | R  | R  | R           | R          | R          |

|                |    |    |    |    |       |      |        |     |         |     |            |    |    |             |            |            |

| Bit:           | 15 | 14 | 13 | 12 | 11    | 10   | 9      | 8   | 7       | 6   | 5          | 4  | 3  | 2           | 1          | 0          |

|                | -  | -  | -  | -  | BLOCK | DPRT | Y[1:0] | D   | MAIW[2: | 0]  | DMA<br>IWA | -  | -  | HIZ<br>CKIO | HIZ<br>MEM | HIZ<br>CNT |

| Initial value: | 0  | 0  | 0  | 1  | 0     | 0    | 0      | 0   | 0       | 0   | 0          | 1  | 0  | 0           | 0          | 0          |

| R/W:           | R  | R  | R  | R  | R/W   | R/W  | R/W    | R/W | R/W     | R/W | R/W        | R  | R  | R/W         | R/W        | R/W        |

| Bit      | Bit Name   | Initial<br>Value | R/W | Description                                                                                              |

|----------|------------|------------------|-----|----------------------------------------------------------------------------------------------------------|

| 31 to 13 | _          | All 0            | R   | Reserved                                                                                                 |

|          |            |                  |     | These bits are always read as 0. The write value should always be 0.                                     |

| 12       | _          | 1                | R   | Reserved                                                                                                 |

|          |            |                  |     | This bit is always read as 1. The write value should always be 1.                                        |

| 11       | BLOCK      | 0                | R/W | Bus Lock                                                                                                 |

|          |            |                  |     | Specifies whether or not the BREQ signal is received.                                                    |

|          |            |                  |     | 0: Receives BREQ.                                                                                        |

|          |            |                  |     | 1: Does not receive BREQ.                                                                                |

| 10, 9    | DPRTY[1:0] | 00               | R/W | DMA Burst Transfer Priority                                                                              |

|          |            |                  |     | Specify the priority for a refresh request/bus mastership request during DMA burst transfer.             |

|          |            |                  |     | 00: Accepts a refresh request and bus mastership<br>request during DMA burst transfer.                   |

|          |            |                  |     | 01: Accepts a refresh request but does not accept a<br>bus mastership request during DMA burst transfer. |

|          |            |                  |     | 10: Accepts neither a refresh request nor a bus<br>mastership request during DMA burst transfer.         |

|          |            |                  |     | 11: Reserved (setting prohibited)                                                                        |

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                               |

|--------|----------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 3 | _        | All 0            | R   | Reserved                                                                                                                                                                                                                  |

|        |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                                                                                      |

| 2      | TTSE     | 0                | R/W | Timing Select E                                                                                                                                                                                                           |

|        |          |                  |     | Specifies the timing for transferring data from TGRF_0<br>to TGRE_0 when they are used together for buffer<br>operation.                                                                                                  |

|        |          |                  |     | In channels 3 and 4, bit 2 is reserved. It is always read<br>as 0 and the write value should always be 0. When<br>channel 0 is used in a mode other than PWM mode, do<br>not set this bit to 1.                           |

|        |          |                  |     | 0: When compare match E occurs in channel 0                                                                                                                                                                               |

|        |          |                  |     | 1: When TCNT_0 is cleared                                                                                                                                                                                                 |

| 1      | TTSB     | 0                | R/W | Timing Select B                                                                                                                                                                                                           |

|        |          |                  |     | Specifies the timing for transferring data from TGRD to<br>TGRB in each channel when they are used together for<br>buffer operation. When the channel is used in a mode<br>other than PWM mode, do not set this bit to 1. |

|        |          |                  |     | 0: When compare match B occurs in each channel                                                                                                                                                                            |

|        |          |                  |     | 1: When TCNT is cleared in each channel                                                                                                                                                                                   |

| 0      | TTSA     | 0                | R/W | Timing Select A                                                                                                                                                                                                           |

|        |          |                  |     | Specifies the timing for transferring data from TGRC to<br>TGRA in each channel when they are used together for<br>buffer operation. When the channel is used in a mode<br>other than PWM mode, do not set this bit to 1. |

|        |          |                  |     | 0: When compare match A occurs in each channel                                                                                                                                                                            |

|        |          |                  |     | 1: When TCNT is cleared in each channel                                                                                                                                                                                   |

| Рф                      |     |  |

|-------------------------|-----|--|

| Input capture<br>signal |     |  |

| TCNT                    | N   |  |

| TGR                     | X N |  |

| TGF flag                |     |  |

| TGI interrupt           |     |  |

| Figure 11.112  | <b>TGI Interrupt</b> | Timing (Input | Capture) ( | Channel 5) |

|----------------|----------------------|---------------|------------|------------|

| I Igui e IIIII | I OI Interrupt       | I ming (mput  | Cupture) ( | Chamber c) |

### (3) TCFV Flag/TCFU Flag Setting Timing

Figure 11.113 shows the timing for setting of the TCFV flag in TSR on overflow, and TCIV interrupt request signal timing.

Figure 11.114 shows the timing for setting of the TCFU flag in TSR on underflow, and TCIU interrupt request signal timing.

| Ρφ                 |               |

|--------------------|---------------|

| TCNT input clock   |               |

| TCNT<br>(overflow) | H'FFFF H'0000 |

| Overflow<br>signal |               |

| TCFV flag          |               |

| TCIV interrupt     |               |

Figure 11.113 TCIV Interrupt Setting Timing

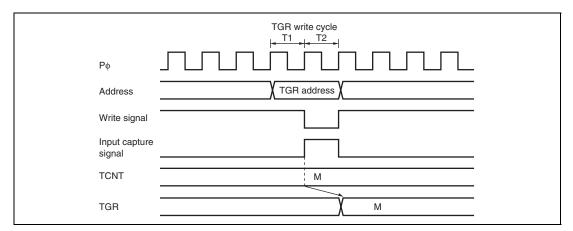

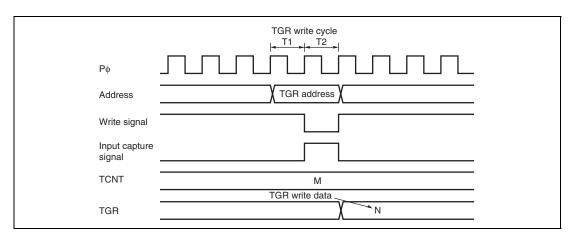

## 11.7.10 Contention between TGR Write and Input Capture

If an input capture signal is generated in the T2 state of a TGR write cycle, the input capture operation takes precedence and the write to TGR is not performed for channels 0 to 4. For channel 5, write to TGR is performed and the input capture signal is generated.

Figures 11.128 and 129 show the timing in this case.

Figure 11.128 Contention between TGR Write and Input Capture (Channels 0 to 4)

Figure 11.129 Contention between TGR Write and Input Capture (Channel 5)

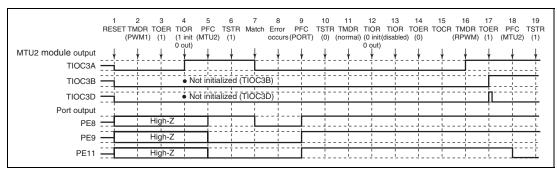

## (12) Operation when Error Occurs during PWM Mode 1 Operation, and Operation is Restarted in Reset-Synchronized PWM Mode

Figure 11.150 shows an explanatory diagram of the case where an error occurs in PWM mode 1 and operation is restarted in reset-synchronized PWM mode after re-setting.

# Figure 11.150 Error Occurrence in PWM Mode 1, Recovery in Reset-Synchronized PWM Mode

- 1 to 14 are the same as in figure 11.149.

- 15. Select the reset-synchronized PWM output level and cyclic output enabling/disabling with TOCR.

- 16. Set reset-synchronized PWM.

- 17. Enable channel 3 and 4 output with TOER.

- 18. Set MTU2 output with the PFC.

- 19. Operation is restarted by TSTR.

| Item                                                | Channel 3                                      | Channel 4                                                                                                                                                                                                | Channel 5 |

|-----------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| A/D converter start<br>request delaying<br>function |                                                | <ul> <li>A/D converter start<br/>request at a match<br/>between<br/>TADCORA_4S and<br/>TCNT_4S</li> <li>A/D converter start<br/>request at a match<br/>between<br/>TADCORB_4S and<br/>TCNT_4S</li> </ul> |           |

| Interrupt skipping function                         | Skips TGRA_3S     compare match     interrupts | Skips TCIV_4S interrupts                                                                                                                                                                                 | _         |

| [Legend] $\sqrt{2}$ Possible                        |                                                |                                                                                                                                                                                                          |           |

-: Not possible

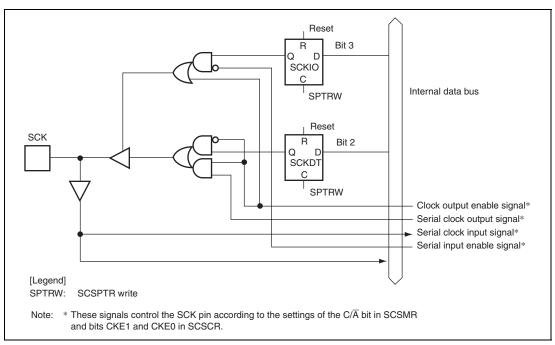

# 16.6 Serial Port Register (SCSPTR) and SCI Pins

The relationship between SCSPTR and the SCI pins is shown in figures 16.19 and 16.20.

Figure 16.19 SCKIO Bit, SCKDT Bit, and SCK Pin

# 18.4.7 Clock Synchronous Communication Mode

In clock synchronous communication mode, data communications are performed via three lines: clock line (SSCK), data input line (SSI), and data output line (SSO).

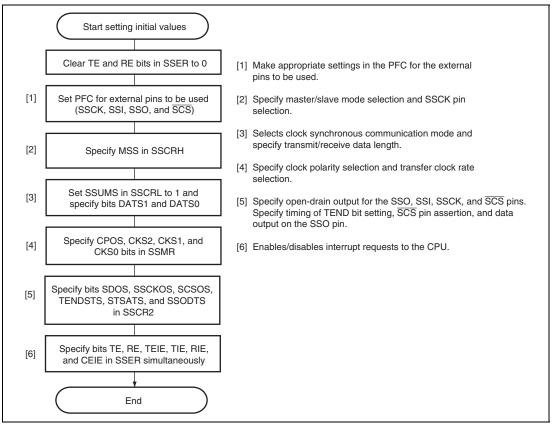

## (1) Initial Settings in Clock Synchronous Communication Mode

Figure 18.12 shows an example of the initial settings in clock synchronous communication mode. Before data transfer, clear both the TE and RE bits in SSER to 0 to set the initial values.

Note: Before changing operating modes and communications formats, clear both the TE and RE bits to 0. Although clearing the TE bit to 0 sets the TDRE bit to 1, clearing the RE bit to 0 does not change the values of the RDRF and ORER bits and SSRDR. Those bits retain the previous values.

Figure 18.12 Example of Initial Settings in Clock Synchronous Communication Mode

#### • BCR0 (Address = H'006)

| Bit           | : 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7   | 6   | 5   | 4   | 3     | 2   | 1   | 0   |

|---------------|------|----|----|----|----|----|---|---|-----|-----|-----|-----|-------|-----|-----|-----|

|               | -    | -  | -  | -  | -  | -  | - | - |     |     |     | BRP | [7:0] |     |     |     |

| Initial value | : 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0   | 0   | 0   | 0   | 0     | 0   | 0   | 0   |

| R/W           | : R  | R  | R  | R  | R  | R  | R | R | R/W | R/W | R/W | R/W | R/W   | R/W | R/W | R/W |

Bits 8 to 15 : Reserved. The written value should always be '0' and the returned value is '0'.

**Bits 7 to 0—Baud Rate Pre-scale (BRP[7:0] = BCR0 [7:0]):** These bits are used to define the peripheral bus clock periods contained in a Time Quantum.

| Bit 7:<br>BRP[7] | Bit 6:<br>BRP[6] | Bit 5:<br>BRP[5] | Bit 4:<br>BRP[4] | Bit 3:<br>BRP[3] | Bit 2:<br>BRP[2] | Bit 1:<br>BRP[1] | Bit 0:<br>BRP[0] | Description                                               |

|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|-----------------------------------------------------------|

| 0                | 0                | 0                | 0                | 0                | 0                | 0                | 0                | 2 × peripheral bus clock<br>(Initial value)               |

| 0                | 0                | 0                | 0                | 0                | 0                | 0                | 1                | $4 \times peripheral bus clock$                           |

| 0                | 0                | 0                | 0                | 0                | 0                | 1                | 0                | $6 \times peripheral bus clock$                           |

| :                | :                | :                | :                | :                | :                | :                | :                | $2 \times (register value+1) \times peripheral bus clock$ |

| 0                | 1                | 1                | 1                | 1                | 1                | 1                | 1                | $512 \times \text{peripheral bus clock}$                  |

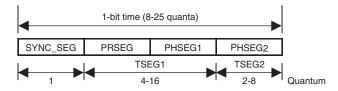

• Requirements of Bit Configuration Register

SYNC\_SEG: Segment for establishing synchronisation of nodes on the CAN bus. (Normal bit edge transitions occur in this segment.)

PRSEG: Segment for compensating for physical delay between networks.

PHSEG1: Buffer segment for correcting phase drift (positive). (This segment is extended when synchronisation (resynchronisation) is established.)

PHSEG2: Buffer segment for correcting phase drift (negative). (This segment is shortened when synchronisation (resynchronisation) is established)

TSEG1: TSG1 + 1

# Table 23.14 Multiplexed Pins (SH7286 Port E)

| Port | Function 1<br>(Related<br>Module) | Function 2<br>(Related<br>Module) | Function 3<br>(Related<br>Module) | Function 4<br>(Related<br>Module)    | Function 5<br>(Related<br>Module) | Function 6<br>(Related<br>Module) | Function 7<br>(Related<br>Module) | Function 8<br>(Related<br>Module) | Function 9<br>(Related<br>Module) |

|------|-----------------------------------|-----------------------------------|-----------------------------------|--------------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|

| E    | PE15 I/O<br>(Port)                | _                                 | DACK1<br>output<br>(DMAC)         | IRQOUT<br>output<br>(INTC)           | _                                 | _                                 | TIOC4D I/O<br>(MTU2)              |                                   | _                                 |

|      | PE14 I/O<br>(Port)                | AH output<br>(BSC)                | DACK0<br>output<br>(DMAC)         |                                      | _                                 |                                   | TIOC4C I/O<br>(MTU2)              |                                   | _                                 |

|      | PE13 I/O<br>(Port)                |                                   |                                   | MRES<br>input<br>(system<br>control) | _                                 |                                   | TIOC4B I/O<br>(MTU2)              |                                   | _                                 |

|      | PE12 I/O<br>(Port)                | —                                 | _                                 | _                                    | —                                 | _                                 | TIOC4A I/O<br>(MTU2)              |                                   | _                                 |

|      | PE11 I/O<br>(Port)                | —                                 | _                                 | _                                    | —                                 | _                                 | TIOC3D I/O<br>(MTU2)              | _                                 | _                                 |

|      | PE10 I/O<br>(Port)                | _                                 | _                                 | _                                    | _                                 | TXD2<br>output<br>(SCI)           | TIOC3C I/O<br>(MTU2)              | _                                 | _                                 |

|      | PE9 I/O<br>(Port)                 | —                                 | —                                 | _                                    | —                                 | —                                 | TIOC3B I/O<br>(MTU2)              |                                   | _                                 |

|      | PE8 I/O<br>(Port)                 | —                                 | _                                 | _                                    | —                                 | SCK2 I/O<br>(SCI)                 | TIOC3A I/O<br>(MTU2)              | _                                 | _                                 |

|      | PE7 I/O<br>(Port)                 | BS output<br>(BSC)                | _                                 | UBCTRG<br>output<br>(UBC)            | _                                 | RXD2 input<br>(SCI)               | TIOC2B I/O<br>(MTU2)              |                                   |                                   |

|      | PE6 I/O<br>(Port)                 |                                   |                                   |                                      | TIOC3DS<br>I/O<br>(MTU2S)         | SCK3 I/O<br>(SCIF)                | TIOC2A I/O<br>(MTU2)              |                                   | _                                 |

|      | PE5 I/O<br>(Port)                 | _                                 | _                                 | _                                    | TIOC3BS<br>I/O<br>(MTU2S)         | TXD3<br>output<br>(SCIF)          | TIOC1B I/O<br>(MTU2)              | _                                 | _                                 |

|      | PE4 I/O<br>(Port)                 | _                                 | _                                 | _                                    | _                                 | RXD3 input<br>(SCIF)              | TIOC1A I/O<br>(MTU2)              | _                                 | _                                 |

|      | PE3 I/O<br>(Port)                 | _                                 | TEND1<br>output<br>(DMAC)         | _                                    | TIOC4DS<br>I/O<br>(MTU2S)         | _                                 | TIOC0D I/O<br>(MTU2)              | _                                 | _                                 |

| Bit    | Bit Name   | Initial<br>Value | R/W | Description                                                       |

|--------|------------|------------------|-----|-------------------------------------------------------------------|

| 6 to 4 | PB1MD[2:0] | 000*             | R/W | PB1 Mode                                                          |

|        |            |                  |     | Select the function of the                                        |

|        |            |                  |     | 000: PB1 I/O (port)                                               |

|        |            |                  |     | 001: A17 output (BSC)                                             |

|        |            |                  |     | 010: REFOUT output (BSC)                                          |

|        |            |                  |     | 011: IRQ4 input (INTC)                                            |

|        |            |                  |     | 100: Setting prohibited                                           |

|        |            |                  |     | 101: Setting prohibited                                           |

|        |            |                  |     | 110: Setting prohibited                                           |

|        |            |                  |     | 111: ADTRG input (ADC)                                            |

| 3      | —          | 0                | R   | Reserved                                                          |

|        |            |                  |     | This bit is always read as 0. The write value should always be 0. |

| 2 to 0 | PB0MD[2:0] | 000*             | R/W | PB0 Mode                                                          |

|        |            |                  |     | Select the function of the PB0/A16/IRQ3 pin.                      |

|        |            |                  |     | 000: PB0 I/O (port)                                               |

|        |            |                  |     | 001: A16 output (BSC)                                             |

|        |            |                  |     | 010: Setting prohibited                                           |

|        |            |                  |     | 011: IRQ3 input (INTC)                                            |

|        |            |                  |     | 100: Setting prohibited                                           |

|        |            |                  |     | 101: Setting prohibited                                           |

|        |            |                  |     | 110: Setting prohibited                                           |

|        |            |                  |     | 111: Setting prohibited                                           |

Note: \* The initial value is 1 during the on-chip ROM disabled external extension mode.

# Table 24.4 Port B Data Registers H and L (PBDRH and PBDRL) Read/Write Operations

• PBDRH bits 3 to 0 and PBDRL bits 15 to 6 and 3 to 0

| PBDRH,<br>PBDRL | Pin Function                | Read                 | Write                                                           |

|-----------------|-----------------------------|----------------------|-----------------------------------------------------------------|

| 0               | General input               | Pin state            | Can write to PBDRH or PBDRL, but it has no effect on pin state. |

|                 | Other than<br>general input | Pin state            | Can write to PBDRH or PBDRL, but it has no effect on pin state. |

| 1               | General output              | PBDRH/PBDRL<br>value | The value written is output from the pin.                       |

|                 | Other than general output   | PBDRH/PBDRL<br>value | Can write to PBDRH or PBDRL, but it has no effect on pin state. |

# 25.3.6 USB Interrupt Enable Register 1 (USBIER1)

USBIER1 enables the interrupt requests indicated in USB interrupt flag register 1 (USBIFR1). When an interrupt flag is set while the corresponding bit in USBIER1 is set to 1, an interrupt request is sent to the CPU. The interrupt vector number is decided by the contents of USB interrupt select register 1 (USBISR1).

USBEPDR0I is initialized to H'00 by a power-on reset.

| Bit:           | 7 | 6 | 5 | 4 | 3 | 2     | 1     | 0     |

|----------------|---|---|---|---|---|-------|-------|-------|

|                | - | - | - | - | - | EP3TR | EP3TS | VBUSF |

| Initial value: | 0 | 0 | 0 | 0 | 0 | 0     | 0     | 0     |

| R/W:           | R | R | R | R | R | R/W   | R/W   | R/W   |

|        |          | Initial |     |                                     |

|--------|----------|---------|-----|-------------------------------------|

| Bit    | Bit Name | Value   | R/W | Description                         |

| 7 to 3 | _        | All 0   | R   | Reserved                            |

|        |          |         |     | The write value should always be 0. |

| 2      | EP3TR    | 0       | R/W | EP3 transfer request                |

| 1      | EP3TS    | 0       | R/W | EP3 transmit completion             |

| 0      | VBUSF    | 0       | R/W | USB bus connection                  |

# (2) Flash Program Code Select Register (FPCS)

FPCS selects the on-chip programming program to be downloaded.

| Bit:           | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0    |

|----------------|---|---|---|---|---|---|---|------|

|                | - | - | - | - | - | - | - | PPVS |

| Initial value: | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0    |

| R/W:           | R | R | R | R | R | R | R | R/W  |

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                          |

|--------|----------|------------------|-----|----------------------------------------------------------------------|

| 7 to 1 | _        | All 0            | R   | Reserved                                                             |

|        |          |                  |     | These bits are always read as 0. The write value should always be 0. |

| 0      | PPVS     | 0                | R/W | Program Pulse Single                                                 |

|        |          |                  |     | Selects the programming program.                                     |

|        |          |                  |     | 0: On-chip programming program is not selected                       |

|        |          |                  |     | [Clearing condition]                                                 |

|        |          |                  |     | When transfer is completed                                           |

|        |          |                  |     | 1: On-chip programming program is selected                           |

# (3) Flash Erase Code Select Register (FECS)

FECS selects download of the on-chip erasing program.

| Bit:           | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0    |

|----------------|---|---|---|---|---|---|---|------|

|                | - | - | - | - | - | - | - | EPVB |

| Initial value: | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0    |

| R/W:           | R | R | R | R | R | R | R | R/W  |

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                          |

|--------|----------|------------------|-----|----------------------------------------------------------------------|

| 7 to 1 | _        | All 0            | R   | Reserved                                                             |

|        |          |                  |     | These bits are always read as 0. The write value should always be 0. |

#### 1. Select Erasure

In response to the erasure selection command, the boot program transfers the program that performs erasure, i.e. erases data in the user MAT.

Command

• Command H'48 (1 byte): Selects erasure.

| Response | H'06 |

|----------|------|

|----------|------|

• Response H'06 (1 byte): Response to selection of erasure This ACK code is returned after transfer of the program that performs erasure.

| Error    |      |       |

|----------|------|-------|

| response | H'C8 | ERROR |

- Error response H'C8 (1 byte): Error response to selection of erasure

- ERROR (1 byte): Error code H'54: Error in selection processing (processing was not completed because of a transfer error.)

- 2. Block Erasure

In response to the block erasure command, the boot program erases the data in a specified block of the user MAT.

| Command | H'58 | Size | Block number | SUM |

|---------|------|------|--------------|-----|

|---------|------|------|--------------|-----|

- Command H'58 (1 byte): Erasure of a block

- Size (1 byte): The number of characters in the block number field (fixed at 1)

- Block number (1 byte): Block number of the block to be erased

- SUM (1 byte): Checksum

Response

• Response H'06 (1 byte): Response to the block erasure command This ACK code is returned when the block has been erased.