Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | SH2A                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 100MHz                                                                             |

| Connectivity               | SCI                                                                                |

| Peripherals                | DMA, PWM, WDT                                                                      |

| Number of I/O              | 63                                                                                 |

| Program Memory Size        | 256KB (256K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 12K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                          |

| Data Converters            | A/D 8x12b                                                                          |

| Oscillator Type            | External                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 100-LQFP                                                                           |

| Supplier Device Package    | 100-LFQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f72434d100fp-u0 |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Classification | Types | Operation<br>Code | Function                                                                    | No. of<br>Instructions |

|----------------|-------|-------------------|-----------------------------------------------------------------------------|------------------------|

| Arithmetic     | 26    | ADD               | Binary addition                                                             | 40                     |

| operations     |       | ADDC              | Binary addition with carry                                                  | _                      |

|                |       | ADDV              | Binary addition with overflow check                                         | _                      |

|                |       | CMP/cond          | Comparison                                                                  | _                      |

|                |       | CLIPS             | Signed saturation value comparison                                          | -                      |

|                |       | CLIPU             | Unsigned saturation value comparison                                        | -                      |

|                |       | DIVS              | Signed division (32 ÷ 32)                                                   | _                      |

|                |       | DIVU              | Unsigned division (32 ÷ 32)                                                 | -                      |

|                |       | DIV1              | One-step division                                                           | -                      |

|                |       | DIV0S             | Initialization of signed one-step division                                  | -                      |

|                |       | DIV0U             | Initialization of unsigned one-step division                                | _                      |

|                |       | DMULS             | Signed double-precision multiplication                                      | _                      |

|                |       | DMULU             | Unsigned double-precision multiplication                                    | -                      |

|                |       | DT                | Decrement and test                                                          | _                      |

|                |       | EXTS              | Sign extension                                                              | _                      |

|                |       | EXTU              | Zero extension                                                              | -                      |

|                |       | MAC               | Multiply-and-accumulate, double-precision multiply-and-accumulate operation | _                      |

|                |       | MUL               | Double-precision multiply operation                                         | _                      |

|                |       | MULR              | Signed multiplication with result storage in Rn                             | -                      |

|                |       | MULS              | Signed multiplication                                                       | _                      |

|                |       | MULU              | Unsigned multiplication                                                     | _                      |

|                |       | NEG               | Negation                                                                    | _                      |

|                |       | NEGC              | Negation with borrow                                                        | -                      |

|                |       | SUB               | Binary subtraction                                                          | -                      |

|                |       | SUBC              | Binary subtraction with borrow                                              | -                      |

|                |       | SUBV              | Binary subtraction with underflow                                           | _                      |

| Bit  | Bit Name | Initial<br>Value | R/W | Description                                                                                              |

|------|----------|------------------|-----|----------------------------------------------------------------------------------------------------------|

| 4    | DTS      | Undefined        | _   | DTC Transfer Mode Select                                                                                 |

|      |          |                  |     | Specifies either the source or destination as repeat or block area during repeat or block transfer mode. |

|      |          |                  |     | 0: Specifies the destination as repeat or block area                                                     |

|      |          |                  |     | 1: Specifies the source as repeat or block area                                                          |

| 3, 2 | DM[1:0]  | Undefined        |     | Destination Address Mode 1 and 0                                                                         |

|      |          |                  |     | Specify a DAR operation after a data transfer.                                                           |

|      |          |                  |     | 0x: DAR is fixed                                                                                         |

|      |          |                  |     | (DAR write-back is skipped)                                                                              |

|      |          |                  |     | 10: DAR is incremented after a transfer                                                                  |

|      |          |                  |     | (by 1 when Sz1 and Sz0 = B'00; by 2 when Sz1 and<br>Sz0 = B'01; by 4 when Sz1 and Sz0 = B'10)            |

|      |          |                  |     | 11: SAR is decremented after a transfer                                                                  |

|      |          |                  |     | (by 1 when Sz1 and Sz0 = B'00; by 2 when Sz1 and<br>Sz0 = B'01; by 4 when Sz1 and Sz0 = B'10)            |

| 1, 0 | _        | Undefined        | _   | Reserved                                                                                                 |

|      |          |                  |     | The write value should always be 0.                                                                      |

[Legend]

x: Don't care

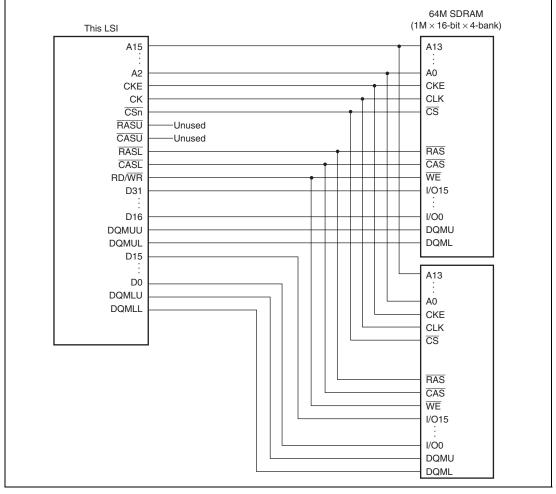

As shown in figure 9.16, two sets of SDRAMs of 32Mbytes or smaller can be connected to the same CS space by using  $\overline{RASU}$ ,  $\overline{RASL}$ ,  $\overline{CASU}$ , and  $\overline{CASL}$ . In this case, a total of 8 banks are assigned to the same CS space: 4 banks specified by  $\overline{RASL}$  and  $\overline{CASL}$ , and 4 banks specified by  $\overline{RASU}$  and  $\overline{CASU}$ . When accessing the address with A25 = 0,  $\overline{RASL}$  and  $\overline{CASL}$  are asserted. When accessing the address with A25 = 1,  $\overline{RASU}$  and  $\overline{CASU}$  are asserted.

Figure 9.14 Example of 32-Bit Data Width SDRAM Connection (RASU and CASU are Not Used)

Description

## Table 11.15 TIOR\_2 (Channel 2)

|               |               |               |               |                    | Description                    |

|---------------|---------------|---------------|---------------|--------------------|--------------------------------|

| Bit 7<br>IOB3 | Bit 6<br>IOB2 | Bit 5<br>IOB1 | Bit 4<br>IOB0 | TGRB_2<br>Function | TIOC2B Pin Function            |

| 0             | 0             | 0             | 0             | Output             | Output retained*               |

|               |               |               | 1             | compare register   | Initial output is 0            |

|               |               |               |               | register           | 0 output at compare match      |

|               |               | 1             | 0             | _                  | Initial output is 0            |

|               |               |               |               |                    | 1 output at compare match      |

|               |               |               | 1             | _                  | Initial output is 0            |

|               |               |               |               |                    | Toggle output at compare match |

|               | 1             | 0             | 0             | _                  | Output retained                |

|               |               |               | 1             | _                  | Initial output is 1            |

|               |               |               |               |                    | 0 output at compare match      |

|               |               | 1             | 0             | _                  | Initial output is 1            |

|               |               |               |               |                    | 1 output at compare match      |

|               |               |               | 1             | _                  | Initial output is 1            |

|               |               |               |               |                    | Toggle output at compare match |

| 1             | Х             | 0             | 0             |                    | Input capture at rising edge   |

|               |               |               | 1             | register           | Input capture at falling edge  |

|               |               | 1             | Х             | _                  | Input capture at both edges    |

| [Legen        | d]            |               | _             |                    |                                |

[Legend]

X: Don't care

Note: After power-on reset, 0 is output until TIOR is set. \*

| Bit | Bit Name | Initial<br>value | R/W | Description                                                                                                                |

|-----|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------|

| 0   | OLS1P    | 0                | R/W | Output Level Select 1P*                                                                                                    |

|     |          |                  |     | This bit selects the output level on TIOC3B in reset-<br>synchronized PWM mode/complementary PWM mode.<br>See table 11.38. |

Note: \* Setting the TOCS bit in TOCR1 to 1 makes this bit setting valid.

#### Table 11.32 Setting of Bits BF1 and BF0

| Bit 7 | Bit 6 | Description                                                                                           |                                                                                              |  |  |  |  |  |  |

|-------|-------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| BF1   | BF0   | Complementary PWM Mode                                                                                | Reset-Synchronized PWM Mode                                                                  |  |  |  |  |  |  |

| 0     | 0     | Does not transfer data from the buffer register (TOLBR) to TOCR2.                                     | Does not transfer data from the buffer register (TOLBR) to TOCR2.                            |  |  |  |  |  |  |

| 0     | 1     | Transfers data from the buffer register (TOLBR) to TOCR2 at the crest of the TCNT_4 count.            | Transfers data from the buffer<br>register (TOLBR) to TOCR2 when<br>TCNT_3/TCNT_4 is cleared |  |  |  |  |  |  |

| 1     | 0     | Transfers data from the buffer register (TOLBR) to TOCR2 at the trough of the TCNT_4 count.           | Setting prohibited                                                                           |  |  |  |  |  |  |

| 1     | 1     | Transfers data from the buffer register (TOLBR) to TOCR2 at the crest and trough of the TCNT_4 count. | Setting prohibited                                                                           |  |  |  |  |  |  |

#### Table 11.33 TIOC4D Output Level Select Function

| Bit 5 |                | Function     |            |                      |  |  |  |  |  |  |  |  |

|-------|----------------|--------------|------------|----------------------|--|--|--|--|--|--|--|--|

|       |                |              |            | Compare Match Output |  |  |  |  |  |  |  |  |

| OLS3N | Initial Output | Active Level | Up Count   | Down Count           |  |  |  |  |  |  |  |  |

| 0     | High level     | Low level    | High level | Low level            |  |  |  |  |  |  |  |  |

| 1     | Low level      | High level   | Low level  | High level           |  |  |  |  |  |  |  |  |

Note: The reverse phase waveform initial output value changes to the active level after elapse of the dead time after count start.

#### 11.3.27 Timer Cycle Buffer Register (TCBR)

TCBR is a 16-bit register used only in complementary PWM mode. It functions as a buffer register for the TCDR register. The TCBR register values are transferred to the TCDR register with the transfer timing set in the TMDR register.

Note: Accessing the TCBR in 8-bit units is prohibited. Always access in 16-bit units.

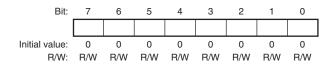

### 11.3.28 Timer Interrupt Skipping Set Register (TITCR)

TITCR is an 8-bit readable/writable register that enables or disables interrupt skipping and specifies the interrupt skipping count. The MTU2 has one TITCR.

|        |            | Bit:                   | 7        | 6        | 5        | 4        | 3                  | 2        | 1        | 0        | _                     |

|--------|------------|------------------------|----------|----------|----------|----------|--------------------|----------|----------|----------|-----------------------|

|        |            |                        | T3AEN    | 3        | ACOR[2:  | 0]       | T4VEN              | 4'       | VCOR[2:  | 0]       |                       |

|        |            | Initial value:<br>R/W: | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W           | 0<br>R/W | 0<br>R/W | 0<br>R/W |                       |

| Bit    | Bit Name   | Initial<br>value       | R/\      | N        | Desc     | riptic   | on                 |          |          |          |                       |

| 7      | T3AEN      | 0                      | R/\      | N        | ТЗАЕ     | EN       |                    |          |          |          |                       |

|        |            |                        |          |          | Enab     | les or   | <sup>,</sup> disab | les T    | GIA_3    | interr   | upt skipping.         |

|        |            |                        |          |          | 0: TO    | AIA_3    | interru            | ıpt ski  | pping    | disab    | led                   |

|        |            |                        |          |          | 1: TG    | alA_3    | interru            | ıpt ski  | pping    | enab     | led                   |

| 6 to 4 | 3ACOR[2:0] | 000                    | R/\      | N        |          |          | specif<br>range f  | -        |          |          | errupt skipping count |

|        |            |                        |          |          | For d    | letails  | , see t            | able 1   | 1.40.    |          |                       |

| 3      | T4VEN      | 0                      | R/\      | N        | T4VE     | EN       |                    |          |          |          |                       |

|        |            |                        |          |          | Enab     | les or   | <sup>,</sup> disab | les T    | CIV_4    | interr   | upt skipping.         |

|        |            |                        |          |          | 0: TC    | VIV_4    | interru            | ipt ski  | pping    | disab    | led                   |

|        |            |                        |          |          | 1: TC    | CIV_4    | interru            | ıpt ski  | pping    | enabl    | led                   |

#### (h) Register Data Updating

In complementary PWM mode, the buffer register is used to update the data in a compare register. The update data can be written to the buffer register at any time. There are five PWM duty and carrier cycle registers that have buffer registers and can be updated during operation.

There is a temporary register between each of these registers and its buffer register. When subcounter TCNTS is not counting, if buffer register data is updated, the temporary register value is also rewritten. Transfer is not performed from buffer registers to temporary registers when TCNTS is counting; in this case, the value written to a buffer register is transferred after TCNTS halts.

The temporary register value is transferred to the compare register at the data update timing set with bits MD3 to MD0 in the timer mode register (TMDR). Figure 11.43 shows an example of data updating in complementary PWM mode. This example shows the mode in which data updating is performed at both the counter crest and trough.

When rewriting buffer register data, a write to TGRD\_4 must be performed at the end of the update. Data transfer from the buffer registers to the temporary registers is performed simultaneously for all five registers after the write to TGRD\_4.

A write to TGRD\_4 must be performed after writing data to the registers to be updated, even when not updating all five registers, or when updating the TGRD\_4 data. In this case, the data written to TGRD\_4 should be the same as the data prior to the write operation.

| Bit | Bit Name | Initial<br>Value | R/W     | Description                                                                                                                                                                                                              |

|-----|----------|------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14  | POE6F    | 0                | R/(W)*1 | POE6 Flag                                                                                                                                                                                                                |

|     |          |                  |         | Indicates that a high impedance request has been input to the $\overline{\text{POE6}}$ pin.                                                                                                                              |

|     |          |                  |         | [Clearing conditions]                                                                                                                                                                                                    |

|     |          |                  |         | • By writing 0 to POE6F after reading POE6F = 1                                                                                                                                                                          |

|     |          |                  |         | (when the falling edge is selected by bits 5 and 4 in ICSR2)                                                                                                                                                             |

|     |          |                  |         | <ul> <li>By writing 0 to POE6F after reading POE6F = 1 after<br/>a high level input to POE6 is sampled at Pφ/8, Pφ/16,<br/>or Pφ/128 clock (when low-level sampling is selected<br/>by bits 5 and 4 in ICSR2)</li> </ul> |

|     |          |                  |         | [Setting condition]                                                                                                                                                                                                      |

|     |          |                  |         | • When the input condition set by bits 5 and 4 in ICSR2 occurs at the POE6 pin                                                                                                                                           |

| 13  | POE5F    | 0                | R/(W)*1 | POE5 Flag                                                                                                                                                                                                                |

|     |          |                  |         | Indicates that a high impedance request has been input to the $\overline{\text{POE5}}$ pin.                                                                                                                              |

|     |          |                  |         | [Clearing conditions]                                                                                                                                                                                                    |

|     |          |                  |         | <ul> <li>By writing 0 to POE5F after reading POE5F = 1<br/>(when the falling edge is selected by bits 3 and 2 in<br/>ICSR2)</li> </ul>                                                                                   |

|     |          |                  |         | <ul> <li>By writing 0 to POE5F after reading POE5F = 1 after<br/>a high level input to POE5 is sampled at Pφ/8, Pφ/16,<br/>or Pφ/128 clock (when low-level sampling is selected<br/>by bits 3 and 2 in ICSR2)</li> </ul> |

|     |          |                  |         | [Setting condition]                                                                                                                                                                                                      |

|     |          |                  |         | • When the input condition set by bits 3 and 2 in ICSR2 occurs at the POE5 pin                                                                                                                                           |

In serial transmission, the SCI operates as described below.

- 1. The SCI monitors the TDRE flag in the serial status register (SCSSR). If it is cleared to 0, the SCI recognizes that data has been written to the transmit data register (SCTDR) and transfers the data from SCTDR to the transmit shift register (SCTSR).

- 2. After transferring data from SCTDR to SCTSR, the SCI sets the TDRE flag to 1 and starts transmission. If the TIE bit in the serial control register (SCSCR) is set to 1 at this time, a transmit-data-empty interrupt (TXI) request is generated.

The serial transmit data is sent from the TXD pin in the following order.

- A. Start bit: One-bit 0 is output.

- B. Transmit data: 8-bit or 7-bit data is output in LSB-first order.

- C. Parity bit or multiprocessor bit: One parity bit (even or odd parity) or one multiprocessor bit is output. (A format in which neither parity nor multiprocessor bit is output can also be selected.)

- D. Stop bit(s): One or two 1 bits (stop bits) are output.

- E. Mark state: 1 is output continuously until the start bit that starts the next transmission is sent.

- 3. The SCI checks the TDRE flag at the timing for sending the stop bit. If the TDRE flag is 0, the data is transferred from SCTDR to SCTSR, the stop bit is sent, and then serial transmission of the next frame is started.

If the TDRE flag is 1, the TEND flag in SCSSR is set to 1, the stop bit is sent, and then the "mark state" is entered in which 1 is output. If the TEIE bit in SCSCR is set to 1 at this time, a TEI interrupt request is generated.

# 21.3 **Register Descriptions**

The D/A converter has the following registers.

#### Table 21.2 Register Configuration

| Register Name        | Abbreviation | R/W | Initial Value | Address    | Access Size |

|----------------------|--------------|-----|---------------|------------|-------------|

| D/A data register 0  | DADR0        | R/W | H'00          | H'FFFE6800 | 8, 16       |

| D/A data register 1  | DADR1        | R/W | H'00          | H'FFFE6801 | 8, 16       |

| D/A control register | DACR         | R/W | H'1F          | H'FFFE6802 | 8, 16       |

#### 21.3.1 D/A Data Registers 0 and 1 (DADR0 and DADR1)

DADR is an 8-bit readable/writable register that stores data to which D/A conversion is to be performed. Whenever analog output is enabled, the values in DADR are converted and output to the analog output pins.

DADR is initialized to H'00 by a power-on reset or in module standby mode.

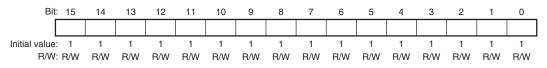

# (5) Interrupt Mask Register (IMR)

The interrupt mask register is a 16 bit register that protects all corresponding interrupts in the Interrupt Request Register (IRR) from generating an output signal on the IRQ. An interrupt request is masked if the corresponding bit position is set to '1'. This register can be read or written at any time. The IMR directly controls the generation of IRQ, but does not prevent the setting of the corresponding bit in the IRR.

• IMR (Address = H'00A)

| Bi            | t: 15  | 14    | 13    | 12    | 11    | 10    | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------------|--------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

|               | IMR15  | IMR14 | IMR13 | IMR12 | IMR11 | IMR10 | IMR9 | IMR8 | IMR7 | IMR6 | IMR5 | IMR4 | IMR3 | IMR2 | IMR1 | IMR0 |

| Initial value | e: 1   | 1     | 1     | 1     | 1     | 1     | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| R/W           | /: R/W | R/W   | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

**Bit 15 to 0:** Maskable interrupt sources corresponding to IRR[15:0] respectively. When a bit is set, the interrupt signal is not generated, although setting the corresponding IRR bit is still performed.

# Bit[15:0]: IMRn Description

|   | •                                                                           |

|---|-----------------------------------------------------------------------------|

| 0 | Corresponding IRR is not masked (IRQ is generated for interrupt conditions) |

| 1 | Corresponding interrupt of IRR is masked (Initial value)                    |

# (6) Transmit Error Counter (TEC) and Receive Error Counter (REC)

The Transmit Error Counter (TEC) and Receive Error Counter (REC) is a 16-bit read/(write) register that functions as a counter indicating the number of transmit/receive message errors on the CAN Interface. The count value is stipulated in the CAN protocol specification Refs. [1], [2], [3] and [4]. When not in (Write Error Counter) test mode this register is read only, and can only be modified by the CAN Interface. This register can be cleared by a Reset request (MCR0) or entering to bus off.

In Write Error Counter test mode (i.e. TST[2:0] = 3'b100), it is possible to write to this register. The same value can only be written to TEC/REC, and the value written into TEC is set to TEC and REC. When writing to this register, RCAN-ET needs to be put into Halt Mode. This feature is only intended for test purposes.

| Bit    | Bit Name    | Initial<br>Value | R/W | Description                                         |

|--------|-------------|------------------|-----|-----------------------------------------------------|

| 2 to 0 | PB16MD[2:0] | 000*             | R/W | PB16 Mode                                           |

|        |             |                  |     | Select the function of the PB16/A22/CASL/DACK3 pin. |

|        |             |                  |     | 000: PB16 I/O (port)                                |

|        |             |                  |     | 001: A22 output (BSC)                               |

|        |             |                  |     | 010: CASL output (BSC)                              |

|        |             |                  |     | 011: Setting prohibited                             |

|        |             |                  |     | 100: Setting prohibited                             |

|        |             |                  |     | 101: Setting prohibited                             |

|        |             |                  |     | 110: Setting prohibited                             |

|        |             |                  |     | 111: DACK3 input (DMAC)                             |

Note: \* The initial value is 1 during the on-chip ROM disabled external extension mode.

#### • Port B Control Register L4 (PBCRL4)

| Bit:           | 15 | 14  | 13      | 12  | 11 | 10  | 9       | 8   | 7 | 6   | 5       | 4   | 3 | 2   | 1       | 0   |

|----------------|----|-----|---------|-----|----|-----|---------|-----|---|-----|---------|-----|---|-----|---------|-----|

|                | -  | PE  | 315MD[2 | :0] | -  | PE  | 314MD[2 | :0] | - | PE  | 313MD[2 | :0] | - | PE  | 312MD[2 | :0] |

| Initial value: | 0  | 0   | 0       | 0*  | 0  | 0   | 0       | 0   | 0 | 0   | 0       | 0   | 0 | 0   | 0       | 0*  |

| R/W:           | R  | R/W | R/W     | R/W | R  | R/W | R/W     | R/W | R | R/W | R/W     | R/W | R | R/W | R/W     | R/W |

Note: \* The initial value is 1 during the on-chip ROM disabled external extension mode.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                       |

|-----|----------|------------------|-----|-------------------------------------------------------------------|

| 15  |          | 0                | R   | Reserved                                                          |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0. |

#### • PDDRL (SH7243, SH7285 and SH7286)

| Bit:           | 15         | 14         | 13         | 12         | 11         | 10         | 9         | 8         | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

|----------------|------------|------------|------------|------------|------------|------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

|                | PD15<br>DR | PD14<br>DR | PD13<br>DR | PD12<br>DR | PD11<br>DR | PD10<br>DR | PD9<br>DR | PD8<br>DR | PD7<br>DR | PD6<br>DR | PD5<br>DR | PD4<br>DR | PD3<br>DR | PD2<br>DR | PD1<br>DR | PD0<br>DR |

| Initial value: | 0          | 0          | 0          | 0          | 0          | 0          | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

| R/W:           | R/W        | R/W        | R/W        | R/W        | R/W        | R/W        | R/W       | R/W       | R/W       | R/W       | R/W       | R/W       | R/W       | R/W       | R/W       | R/W       |

| Bit | Bit Name | Initial<br>Value | R/W | Description     |

|-----|----------|------------------|-----|-----------------|

| 15  | PD15DR   | 0                | R/W | See table 24.8. |

| 14  | PD14DR   | 0                | R/W |                 |

| 13  | PD13DR   | 0                | R/W | _               |

| 12  | PD12DR   | 0                | R/W | _               |

| 11  | PD11DR   | 0                | R/W | -               |

| 10  | PD10DR   | 0                | R/W | -               |

| 9   | PD9DR    | 0                | R/W | _               |

| 8   | PD8DR    | 0                | R/W | _               |

| 7   | PD7DR    | 0                | R/W | _               |

| 6   | PD6DR    | 0                | R/W | _               |

| 5   | PD5DR    | 0                | R/W | _               |

| 4   | PD4DR    | 0                | R/W | _               |

| 3   | PD3DR    | 0                | R/W | _               |

| 2   | PD2DR    | 0                | R/W | _               |

| 1   | PD1DR    | 0                | R/W | _               |

| 0   | PD0DR    | 0                | R/W |                 |

|                                                      |                                                                                                                        | User<br>Program                      | User Boot                                                                    | USB Boot                                                                                    | Programmer                         |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------|

| Programming/<br>erasing                              | Boot Mode<br>On-board<br>programming                                                                                   | Mode<br>On-board<br>programming      | Mode* <sup>3</sup><br>On-board<br>programming                                | Mode* <sup>3</sup><br>On-board<br>programming                                               | Mode<br>Off-board<br>programming   |

| environment<br>Programming/<br>erasing enable<br>MAT | User MAT<br>User boot MAT                                                                                              | User MAT                             | User MAT                                                                     | User MAT                                                                                    | User MAT<br>User boot<br>MAT       |

| Programming/<br>erasing control                      | Command method                                                                                                         | Programming/<br>erasing<br>interface | Programming/<br>erasing<br>interface                                         | Command method                                                                              | _                                  |

| All erasure                                          | Possible<br>(Automatic)                                                                                                | Possible                             | Possible                                                                     | Possible<br>(Automatic)                                                                     | Possible<br>(Automatic)            |

| Block division<br>erasure                            | Possible*1                                                                                                             | Possible                             | Possible                                                                     | Possible*1                                                                                  | Not possible                       |

| Program data<br>transfer                             | From host via<br>SCI                                                                                                   | From optional<br>device via<br>RAM   | From optional<br>device via<br>RAM                                           | From host via<br>USB                                                                        | Via<br>programmer                  |

| User branch function                                 | Not possible                                                                                                           | Possible                             | Possible                                                                     | Not possible                                                                                | Not possible                       |

| Reset initiation<br>MAT                              | Embedded<br>program<br>storage MAT                                                                                     | User MAT                             | User boot<br>MAT* <sup>2</sup>                                               | Embedded<br>program<br>storage MAT                                                          | Embedded<br>program<br>storage MAT |

| Transition to user mode                              | Mode setting<br>change and<br>reset                                                                                    | FWE setting change                   | Mode setting<br>change and<br>reset                                          | Mode setting<br>change and<br>reset                                                         | _                                  |

| Pin state                                            | CK: output<br>Other pins:<br>input<br>(same as the<br>states in MCU<br>extension<br>mode 2)<br>RXD0 and<br>TXD0: valid | Dependent on<br>user settings        | CK: output<br>(initial setting)<br>Other pins:<br>input (initial<br>setting) | CK: output<br>Other pins:<br>input<br>(same as the<br>states in MCU<br>extension<br>mode 2) | Programmer<br>dedicated pins       |

#### Table 26.2 Comparison of Programming Modes

Notes: 1. All-erasure is performed. After that, the specified block can be erased.

2. Initiation starts from the embedded program storage MAT. After checking the flashmemory related registers, initiation starts from the reset vector of the user MAT.

3. Not available in the SH7243.

| Module<br>Name | Register Name                                 | Abbreviation | Number<br>of Bits | Address    | Access<br>Size |

|----------------|-----------------------------------------------|--------------|-------------------|------------|----------------|

| ADC            | A/D analog input channel select<br>register_1 | ADANSR_1     | 8                 | H'FFFFEC20 | 8              |

|                | A/D bypass control register_1                 | ADBYPSCR_1   | 8                 | H'FFFFEC30 | 8              |

|                | A/D data register 4                           | ADDR4        | 16                | H'FFFFEC40 | 16             |

|                | A/D data register 5                           | ADDR5        | 16                | H'FFFFEC42 | 16             |

|                | A/D data register 6                           | ADDR6        | 16                | H'FFFFEC44 | 16             |

|                | A/D data register 7                           | ADDR7        | 16                | H'FFFFEC46 | 16             |

|                | A/D control register_2                        | ADCR_2       | 8                 | H'FFFFEE00 | 8              |

|                | A/D status register_2                         | ADSR_2       | 8                 | H'FFFFEE02 | 8              |

|                | A/D start trigger select register_2           | ADSTRGR_2    | 8                 | H'FFFFEE1C | 8              |

|                | A/D analog input channel select register_2    | ADANSR_2     | 8                 | H'FFFFEE20 | 8              |

|                | A/D bypass control register_2                 | ADBYPSCR_2   | 8                 | H'FFFFEE30 | 8              |

|                | A/D data register 8                           | ADDR8        | 16                | H'FFFFEE40 | 16             |

|                | A/D data register 9                           | ADDR9        | 16                | H'FFFFEE42 | 16             |

|                | A/D data register 10                          | ADDR10       | 16                | H'FFFFEE44 | 16             |

|                | A/D data register 11                          | ADDR11       | 16                | H'FFFFEE46 | 16             |

| DAC            | D/A data register 0                           | DADR0        | 8                 | H'FFFE6800 | 8, 16          |

|                | D/A data register 1                           | DADR1        | 8                 | H'FFFE6801 | 8, 16          |

|                | D/A control register                          | DACR         | 8                 | H'FFFE6802 | 8, 16          |

| RCAN-ET        | Master control register                       | MCR          | 16                | H'FFFFD000 | 16             |

|                | General control register                      | GSR          | 16                | H'FFFFD002 | 16             |

|                | Bit configuration register 1                  | BCR1         | 16                | H'FFFFD004 | 16             |

|                | Bit configuration register 0                  | BCR0         | 16                | H'FFFFD006 | 16             |

|                | Interrupt request register                    | IRR          | 16                | H'FFFFD008 | 16             |

|                | Interrupt mask register                       | IMR          | 16                | H'FFFFD00A | 16             |

|                | Transmit error counter/Receive error counter  | TEC/REC      | 16                | H'FFFFD00C | 16             |

|                | Transmit wait register 1, 0                   | TXPR1, 0     | 32                | H'FFFFD020 | 32             |

|                | Transmit cancel register 0                    | TXCR0        | 16                | H'FFFFD02A | 16             |

|                | Transmit acknowledge register 0               | TXACK0       | 16                | H'FFFFD032 | 16             |

|                | Abort acknowledge register 0                  | ABACK0       | 16                | H'FFFFD03A | 16             |

|                | Data frame receive completion register        | RXPR0        | 16                | H'FFFFD042 | 16             |

|                | Remote frame receive completion register      | RFPR0        | 16                | H'FFFFD04A | 16             |

| Module<br>Name | Register<br>Abbreviation | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|----------------|--------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| DMAC           | DMATCR_6                 |                   |                   |                   |                   |                   |                   |                  |                  |

|                |                          |                   |                   |                   |                   |                   |                   |                  |                  |

|                |                          |                   |                   |                   |                   |                   |                   |                  |                  |

|                |                          |                   |                   |                   |                   |                   |                   |                  |                  |

|                | CHCR_6                   | TC                | —                 | —                 | RLD               |                   |                   | —                | _                |

|                |                          | _                 | _                 |                   | _                 | HE                | HIE               | _                | —                |

|                |                          | DM                | [1:0]             | SM                | [1:0]             |                   | RS[               | [3:0]            |                  |

|                |                          | —                 | —                 | ТВ                | TS[               | 1:0]              | IE                | TE               | DE               |

|                | RSAR_6                   |                   |                   |                   |                   |                   |                   |                  |                  |

|                |                          |                   |                   |                   |                   |                   |                   |                  |                  |

|                |                          |                   |                   |                   |                   |                   |                   |                  |                  |

|                |                          |                   |                   |                   |                   |                   |                   |                  |                  |

|                | RDAR_6                   |                   |                   |                   |                   |                   |                   |                  |                  |

|                |                          |                   |                   |                   |                   |                   |                   |                  |                  |

|                |                          |                   |                   |                   |                   |                   |                   |                  |                  |

|                |                          |                   |                   |                   |                   |                   |                   |                  |                  |

|                | RDMATCR_6                |                   |                   |                   |                   |                   |                   |                  |                  |

|                |                          |                   |                   |                   |                   |                   |                   |                  |                  |

|                |                          |                   |                   |                   |                   |                   |                   |                  |                  |

|                |                          |                   |                   |                   |                   |                   |                   |                  |                  |

|                | SAR_7                    |                   |                   |                   |                   |                   |                   |                  |                  |

|                |                          |                   |                   |                   |                   |                   |                   |                  |                  |

|                |                          |                   |                   |                   |                   |                   |                   |                  |                  |

|                |                          |                   |                   |                   |                   |                   |                   |                  |                  |

|                | DAR_7                    |                   |                   |                   |                   |                   |                   |                  |                  |

|                |                          |                   |                   |                   |                   |                   |                   |                  |                  |

|                |                          |                   |                   |                   |                   |                   |                   |                  |                  |

|                |                          |                   |                   |                   |                   |                   |                   |                  |                  |

|                | DMATCR_7                 |                   |                   |                   |                   |                   |                   |                  |                  |

|                |                          |                   |                   |                   |                   |                   |                   |                  |                  |

|                |                          |                   |                   |                   |                   |                   |                   |                  |                  |

|                |                          |                   |                   |                   |                   |                   |                   |                  |                  |

|                | CHCR_7                   | тс                | —                 | —                 | RLD               | _                 | —                 | —                | —                |

|                |                          | _                 | —                 | —                 | —                 | HE                | HIE               | —                |                  |

|                |                          | DM                | [1:0]             | SM                |                   |                   |                   | [3:0]            | 1                |

|                |                          | -                 | —                 | ТВ                | TS[               | 1:0]              | IE                | TE               | DE               |

# Section 31 Electrical Characteristics

Note: The current specifications of this section are provisional. Note that they are subject to change without notice.

# **31.1** Absolute Maximum Ratings

Table 31.1 lists the absolute maximum ratings.

#### Table 31.1 Absolute Maximum Ratings

| Item                     |                           | Symbol           | Value                       | Unit |

|--------------------------|---------------------------|------------------|-----------------------------|------|

| Power supply voltage     | e (Internal)              | V <sub>cc</sub>  | –0.3 to +7.0                | V    |

|                          |                           | $DrV_{cc}$       | -0.3 to +7.0                | V    |

| Input voltage (except    | analog input pins)        | Vin              | –0.3 to V $_{\rm cc}$ +0.3  | V    |

| Analog power supply      | voltage                   | $AV_{cc}$        | –0.3 to +7.0                | V    |

| Analog reference vol     | tage                      | AVREF            | –0.3 to AV $_{\rm cc}$ +0.3 | V    |

| Analog input voltage     |                           | V <sub>AN</sub>  | –0.3 to AV $_{\rm cc}$ +0.3 | V    |

| Operating<br>temperature | 0                         |                  | –20 to +85                  | °C   |

|                          | Industrial specifications |                  | -40 to +85                  | °C   |

| Storage temperature      |                           | T <sub>stg</sub> | –55 to +125                 | °C   |

Caution: Permanent damage to the LSI may result if absolute maximum ratings are exceeded.

| Pin      | Pin Function            |                  |         |             |         |        |                                                                  |       |                        |                     |                 |

|----------|-------------------------|------------------|---------|-------------|---------|--------|------------------------------------------------------------------|-------|------------------------|---------------------|-----------------|

|          |                         |                  |         | Reset State |         |        | Power-Down Sta                                                   |       |                        |                     |                 |

|          |                         |                  | Po      | ower-On     |         | _      |                                                                  |       | _                      |                     |                 |

|          |                         | Expans<br>withou |         | Expansion   | Single- | -      |                                                                  |       | Bus<br>Master-<br>ship | Oscillation<br>Stop | POE<br>Function |

| Туре     | Pin Name                | 8 bits           | 16 bits | with ROM    | chip    | Manual | Software Standby                                                 | Sleep | Release                | Detected            | Used            |

| I/O Port | PE4, PE7,<br>PE8, PE10  | Z                |         |             |         | I/O    | K* <sup>1</sup>                                                  | I/O   | I/O                    | I/O                 | I/O             |

|          | PE0 to PE3,<br>PE5, PE6 | Z                |         |             |         | I/O    | Z<br>(MZIZEL in HCPCR = 0)<br>$K^{*^1}$<br>(MZIZEL in HCPCR = 1) | I/O   | I/O                    | I/O* <sup>8</sup>   | Z               |

|          | PE9, PE11 to<br>PE15    | Z                |         |             |         | I/O    | Z<br>(MZIZEH in HCPCR = 0)<br>$K^{*^1}$<br>(MZIZEH in HCPCR = 1) | I/O   | I/O                    | I/O* <sup>7</sup>   | Z               |

|          | PF0 to PF11             | Z                |         |             |         | I      | Z                                                                | I     | I                      | 1                   | I               |

[Legend]

- I: Input

- O: Output

- H: High-level output

- L: Low-level output

- Z: High-impedance

- K: Input pins become high-impedance, and output pins retain their state.

- Notes: 1. Output pins become high-impedance when the HIZ bit in standby control register 3 (STBCR3) is set to 1.

- 2. Becomes output when the HIZCNT bit in the common control register (CMNCR) is set to 1.

- 3. Becomes output when the HIZMEM bit in the common control register (CMNCR) is set to 1.

- 4. Becomes output when the HIZCKIO bit in the common control register (CMNCR) is set to 1.

- 5. Becomes high-impedance when the MZIZDH bit in the high-current port control register (HCPCR) is cleared to 0.

- 6. Becomes high-impedance when the MZIZDL bit in the high-current port control register (HCPCR) is cleared to 0.

- 7. Becomes high-impedance when the MZIZEH bit in the high-current port control register (HCPCR) is cleared to 0.

- 8. Becomes high-impedance when the MZIZEL bit in the high-current port control register (HCPCR) is cleared to 0.

- 9. Becomes input during a power-on reset. Pull-up to prevent erroneous operation. Pull-down with a resistance of at least 1 M $\Omega$  as required.

- 10. Pulled-up inside the LSI when there is no input.

| Item                              | Page | Revi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | sion (Se | e Man                     | ual for                  | Details)                                                                                                                     |  |  |  |

|-----------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 16.5 SCI Interrupt Sources        | 823  | Ame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nded     |                           |                          |                                                                                                                              |  |  |  |

| and DTC                           |      | When the ORER, FER, or PER flag in SCSSR is set to an ERI interrupt request is generated. This request cannot be used to activate the DTC. In processing for data reception, generation of ERI interrupt requests can only enabled if generation of RXI interrupt requests is disable. In this case, set the RIE bit and the EIO bit in SCSPTR to 1. However, note that the DMAC or DTC will not transfer received data since RXI interrupt requests are not generated while the EIO bit is set to 1. |          |                           |                          |                                                                                                                              |  |  |  |

| Figure 17.1 Block Diagram of SCIF | 832  | Amei                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | nded     |                           |                          |                                                                                                                              |  |  |  |

|                                   |      | SCBRR<br>Baud rate<br>generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |                           |                          |                                                                                                                              |  |  |  |

| Table 17.2 Register               | 834  | Ame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nded     |                           |                          |                                                                                                                              |  |  |  |

| Configuration                     |      | Chan<br>3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | egister N<br>erial port i | <b>ame</b><br>register_3 | Initial Abbreviation R/W Value SCSPTR_3 R/W H'00xx                                                                           |  |  |  |

| 17.3.7 Serial Status Register     | 851  | Ame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nded     |                           |                          |                                                                                                                              |  |  |  |

| (SCFSR)                           |      | Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit Name | Initial<br>Value          | R/W                      | Description                                                                                                                  |  |  |  |

|                                   |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DR       | 0                         | R/(W)*                   | Receive Data Ready                                                                                                           |  |  |  |

|                                   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |                           |                          | :                                                                                                                            |  |  |  |

|                                   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |                           |                          | <ul> <li>[Clearing conditions]</li> <li>DR is cleared to 0 when the chip<br/>undergoes a power-on reset</li> </ul>           |  |  |  |

|                                   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |                           |                          | <ul> <li>DR is cleared to 0 when all receive data<br/>are read after 1 is read from DR and then<br/>0 is written.</li> </ul> |  |  |  |

|                                   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |                           |                          | <ul> <li>DR is cleared to 0 when all receive data<br/>in SCFRDR are read by the DMAC or<br/>DTC.</li> </ul>                  |  |  |  |