# E·XFL Renesas Electronics America Inc - <u>R5F72867N100FA#U2 Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | SH2A                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 100MHz                                                                             |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SSU, USB                                            |

| Peripherals                | DMA, PWM, WDT                                                                      |

| Number of I/O              | 101                                                                                |

| Program Memory Size        | 1MB (1M x 8)                                                                       |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | ·                                                                                  |

| RAM Size                   | 32K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                          |

| Data Converters            | A/D 12x12b, 2x8b                                                                   |

| Oscillator Type            | External                                                                           |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 176-LQFP                                                                           |

| Supplier Device Package    | 176-LFQFP (20x20)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f72867n100fa-u2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Secti | on 31   | Electrical Characteristics                        |  |

|-------|---------|---------------------------------------------------|--|

| 31.1  | Absolu  | te Maximum Ratings                                |  |

| 31.2  | DC Cha  | aracteristics                                     |  |

| 31.3  | AC Cha  | aracteristics                                     |  |

|       | 31.3.1  | Clock Timing                                      |  |

|       | 31.3.2  | Control Signal Timing                             |  |

|       | 31.3.3  | Bus Timing                                        |  |

|       | 31.3.4  | UBC Trigger Timing                                |  |

|       | 31.3.5  | DMAC Module Timing                                |  |

|       | 31.3.6  | Multi Function Timer Pulse Unit 2 (MTU2) Timing   |  |

|       | 31.3.7  | Multi Function Timer Pulse Unit 2S (MTU2S) Timing |  |

|       | 31.3.8  | POE2 Module Timing                                |  |

|       | 31.3.9  | Watchdog Timer Timing                             |  |

|       | 31.3.10 |                                                   |  |

|       | 31.3.11 | SCIF Module Timing                                |  |

|       | 31.3.12 |                                                   |  |

|       | 31.3.13 | Controller Area Network (RCAN-ET) Timing          |  |

|       | 31.3.14 | IIC3 Module Timing                                |  |

|       | 31.3.15 | -                                                 |  |

|       | 31.3.16 | I/O Port Timing                                   |  |

|       | 31.3.17 | H-UDI Related Pin Timing                          |  |

|       | 31.3.18 | AC Characteristics Measurement Conditions         |  |

| 31.4  | A/D Co  | onverter Characteristics                          |  |

| 31.5  | D/A Co  | onverter Characteristics                          |  |

| 31.6  | USB C   | haracteristics                                    |  |

| 31.7  | Flash M | Iemory Characteristics                            |  |

| 31.8  |         | Notes                                             |  |

|       | 31.8.1  | Notes on Connecting Capacitors                    |  |

| Appe  | endix   |                                                   |  |

| A.    |         | tes                                               |  |

| B.    | Product | t Code Lineup                                     |  |

| C.    |         | e Dimensions                                      |  |

| Main  | Revisi  | ons and Additions in this Edition                 |  |

| Index | κ       |                                                   |  |

#### Page xxx of xxx

# RENESAS

#### 7.4.3 Break on Data Access Cycle

- 1. If the C bus is specified as a break condition for data access break, condition comparison is performed for the virtual address accessed by the executed instructions, and a break occurs if the condition is satisfied. If the I bus is specified as a break condition, condition comparison is performed for the physical address of the data access cycles that are issued by the bus master specified by the bits to select the bus master of the I bus, and a break occurs if the condition is satisfied. For details on the CPU bus cycles issued on the I bus, see 6 in section 7.4.1, Flow of the User Break Operation.

- 2. The relationship between the data access cycle address and the comparison condition for each operand size is listed in table 7.3.

| Table 7.3 | Data Access Cycle Addres | ses and Operand Size ( | <b>Comparison Conditions</b> |

|-----------|--------------------------|------------------------|------------------------------|

|-----------|--------------------------|------------------------|------------------------------|

| Access Size | Address Compared                                                         |

|-------------|--------------------------------------------------------------------------|

| Longword    | Compares break address register bits 31 to 2 to address bus bits 31 to 2 |

| Word        | Compares break address register bits 31 to 1 to address bus bits 31 to 1 |

| Byte        | Compares break address register bits 31 to 0 to address bus bits 31 to 0 |

This means that when address H'00001003 is set in the break address register (BAR), for example, the bus cycle in which the break condition is satisfied is as follows (where other conditions are met).

Longword access at H'00001000 Word access at H'00001002 Byte access at H'00001003

3. If the data access cycle is selected, the instruction at which the break will occur cannot be determined.

# 9.5.2 Normal Space Interface

# (1) Basic Timing

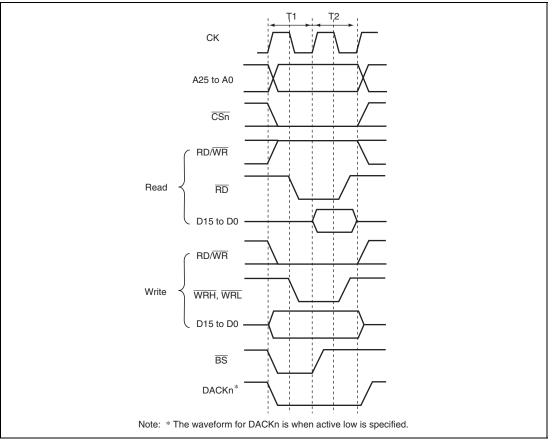

For access to a normal space, this LSI uses strobe signal output in consideration of the fact that mainly static RAM will be directly connected. When using SRAM with a byte-selection pin, see section 9.5.8, SRAM Interface with Byte Selection. Figure 9.2 shows the basic timings of normal space access. A no-wait normal access is completed in two cycles. The  $\overline{\text{BS}}$  signal is asserted for one cycle to indicate the start of a bus cycle.

Figure 9.2 Normal Space Basic Access Timing (Access Wait 0)

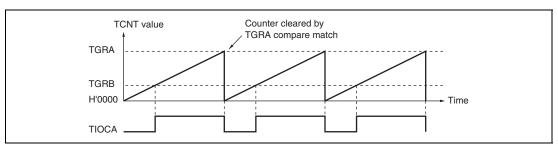

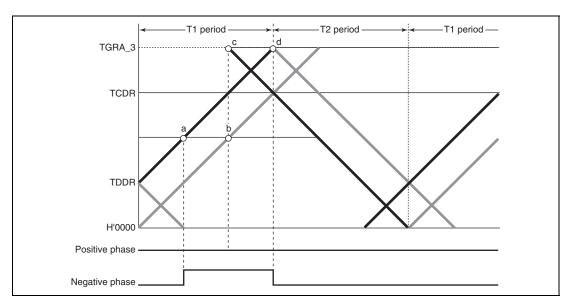

Figure 11.26 Example of PWM Mode Operation (1)

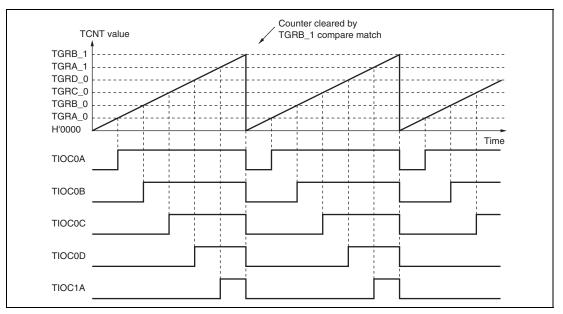

Figure 11.27 shows an example of PWM mode 2 operation.

In this example, synchronous operation is designated for channels 0 and 1, TGRB\_1 compare match is set as the TCNT clearing source, and 0 is set for the initial output value and 1 for the output value of the other TGR registers (TGRA\_0 to TGRD\_0, TGRA\_1), outputting a 5-phase PWM waveform.

In this case, the value set in TGRB\_1 is used as the cycle, and the values set in the other TGRs are used as the duty levels.

Figure 11.27 Example of PWM Mode Operation (2)

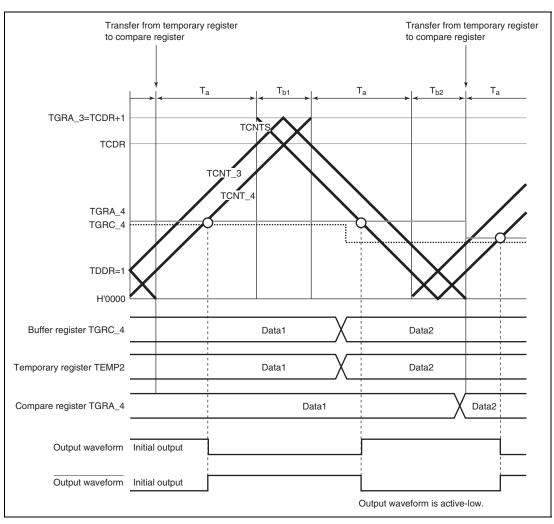

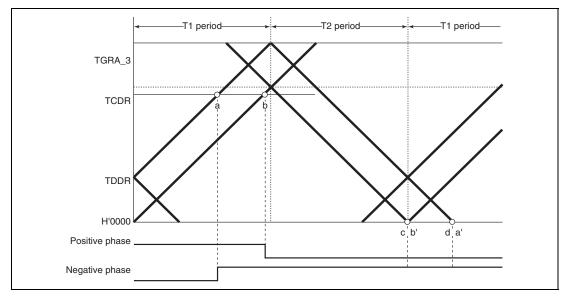

Figure 11.41 Example of Operation without Dead Time

Figure 11.51 Example of Complementary PWM Mode 0% and 100% Waveform Output (3)

Figure 11.52 Example of Complementary PWM Mode 0% and 100% Waveform Output (4)

of the DMAC transfer may be generated even if the activation sources are cleared. Also, when transferring DMAC burst by MTU2, the setting of bus function extension register (BSCEHR) is required. See section 9.4.8, Bus Function Extending Register (BSCEHR), for details.

#### 11.5.3 A/D Converter Activation

The A/D converter can be activated by one of the following three methods in the MTU2. Table 11.58 shows the relationship between interrupt sources and A/D converter start request signals.

#### (1) A/D Converter Activation by TGRA Input Capture/Compare Match or at TCNT\_4 Trough in Complementary PWM Mode

The A/D converter can be activated by the occurrence of a TGRA input capture/compare match in each channel. In addition, if complementary PWM operation is performed while the TTGE2 bit in TIER\_4 is set to 1, the A/D converter can be activated at the trough of TCNT\_4 count (TCNT\_4 = H'0000).

A/D converter start request signal TRGAN is issued to the A/D converter under either one of the following conditions.

- When the TGFA flag in TSR is set to 1 by the occurrence of a TGRA input capture/compare match on a particular channel while the TTGE bit in TIER is set to 1

- When the TCNT\_4 count reaches the trough (TCNT\_4 = H'0000) during complementary PWM operation while the TTGE2 bit in TIER\_4 is set to 1

When either condition is satisfied, if A/D converter start signal TRGAN from the MTU2 is selected as the trigger in the A/D converter, A/D conversion will start.

#### (2) A/D Converter Activation by Compare Match between TCNT\_0 and TGRE\_0

The A/D converter can be activated by generating A/D converter start request signal TRG0N when a compare match occurs between TCNT\_0 and TGRE\_0 in channel 0.

When the TGFE flag in TSR2\_0 is set to 1 by the occurrence of a compare match between TCNT\_0 and TGRE\_0 in channel 0 while the TTGE2 bit in TIER2\_0 is set to 1, A/D converter start request TGR0N is issued to the A/D converter. If A/D converter start signal TGR0N from the MTU2 is selected as the trigger in the A/D converter, A/D conversion will start.

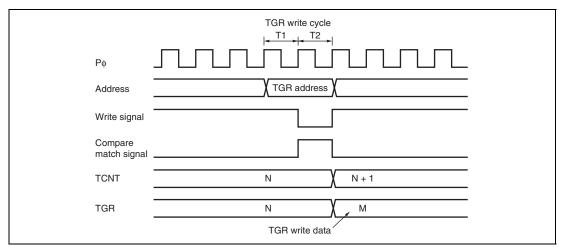

#### 11.7.6 Contention between TGR Write and Compare Match

If a compare match occurs in the T2 state of a TGR write cycle, the TGR write is executed and the compare match signal is also generated.

Figure 11.123 shows the timing in this case.

Figure 11.123 Contention between TGR Write and Compare Match

#### (4) Operation when Error Occurs during Normal Mode Operation, and Operation is Restarted in Phase Counting Mode

Figure 11.142 shows an explanatory diagram of the case where an error occurs in normal mode and operation is restarted in phase counting mode after re-setting.

1 to 10 are the same as in figure 11.139.

- 11. Set phase counting mode.

- 12. Initialize the pins with TIOR.

- 13. Set MTU2 output with the PFC.

- 14. Operation is restarted by TSTR.

- Note: Phase counting mode can only be set for channels 1 and 2, and therefore TOER setting is not necessary.

| Register Name                        | Abbrevia-<br>tion | R/W | Initial<br>value | Address    | Access<br>Size |

|--------------------------------------|-------------------|-----|------------------|------------|----------------|

| Timer counter U_5S                   | TCNTU_5S          | R/W | H'0000           | H'FFFE4880 | 16, 32         |

| Timer general register U_5S          | TGRU_5S           | R/W | H'FFFF           | H'FFFE4882 | 16             |

| Timer control register U_5S          | TCRU_5S           | R/W | H'00             | H'FFFE4884 | 8              |

| Timer I/O control register U_5S      | TIORU_5S          | R/W | H'00             | H'FFFE4886 | 8              |

| Timer counter V_5S                   | TCNTV_5S          | R/W | H'0000           | H'FFFE4890 | 16, 32         |

| Timer general register V_5S          | TGRV_5S           | R/W | H'FFFF           | H'FFFE4892 | 16             |

| Timer control register V_5S          | TCRV_5S           | R/W | H'00             | H'FFFE4894 | 8              |

| Timer I/O control register V_5S      | TIORV_5S          | R/W | H'00             | H'FFFE4896 | 8              |

| Timer counter W_5S                   | TCNTW_5S          | R/W | H'0000           | H'FFFE48A0 | 16, 32         |

| Timer general register W_5S          | TGRW_5S           | R/W | H'FFFF           | H'FFFE48A2 | 16             |

| Timer control register W_5S          | TCRW_5S           | R/W | H'00             | H'FFFE48A4 | 8              |

| Timer I/O control register W_5S      | TIORW_5S          | R/W | H'00             | H'FFFE48A6 | 8              |

| Timer status register_5S             | TSR_5S            | R/W | H'00             | H'FFFE48B0 | 8              |

| Timer interrupt enable register_5S   | TIER_5S           | R/W | H'00             | H'FFFE48B2 | 8              |

| Timer start register_5S              | TSTR_5S           | R/W | H'00             | H'FFFE48B4 | 8              |

| Timer compare match clear register S | TCNTCMPCLRS       | R/W | H'00             | H'FFFE48B6 | 8              |

Note: \* For detailed register descriptions, refer to section 11.3.9, Timer Synchronous Clear Register S (TSYCRS), and figure 11.85 in section 11, Multi-Function Timer Pulse Unit 2 (MTU2).

# 18.2 Input/Output Pins

Table 18.1 shows the SSU pin configuration.

### Table 18.1 Pin Configuration

| Symbol | I/O | Function                     |

|--------|-----|------------------------------|

| SSCK   | I/O | SSU clock input/output       |

| SSI    | I/O | SSU data input/output        |

| SSO    | I/O | SSU data input/output        |

| SCS    | I/O | SSU chip select input/output |

When RCAN-ET recognises the end of the Arbitration field while receiving a message, it starts comparing the received identifier to the identifiers set in the Mailboxes, starting from Mailbox-15 down to Mailbox-0. It first checks the MBC if it is configured as a receive box, and reads LAFM, and reads the CAN-ID of Mailbox-15 (if configured as receive) to finally compare them to the received ID. If it does not match, the same check takes place at Mailbox-14 (if configured as receive). Once RCAN-ET finds a matching identifier, it stores the number of Mailbox-[N] into an internal buffer, stops the search, and goes back to idle state, waiting for the EndOfFrame (EOF) to come. When the  $6^{th}$  bit of EOF is notified by the CAN Interface logic, the received message is written or abandoned, depending on the NMC bit. No modification of configuration during communication is allowed. Entering Halt Mode is one of ways to modify configuration. If it is written into the corresponding Mailbox, including the CAN-ID, i.e., there is a possibility that the CAN-ID is overwritten by a different CAN-ID of the received message due to the LAFM used. This also implies that, if the identifier of a received message matches to ID + LAFM of 2 or more Mailboxes, the higher numbered Mailbox will always store the relevant messages and the lower numbered Mailbox will never receive messages. Therefore, the settings of the identifiers and LAFMs need to be carefully selected.

With regards to the reception of data and remote frames described in the above flow diagram the clearing of the UMSR flag after the reading of IRR is to detect situations where a message is overwritten by a new incoming message stored in the same mailbox while the interrupt service routine is running. If during the final check of UMSR a overwrite condition is detected the message needs to be discarded and read again.

In case UMSR is set and the Mailbox is configured for overrun (NMC = 0) the message is still valid, however it is obsolete as it is not reflecting the latest message monitored on the CAN Bus. Please access the full Mailbox content before clearing the related RXPR/RFPR flag.

Please note that in the case a received remote frame is overwritten by a data frame, both the remote frame request interrupt (IRR2) and data frame received interrupt (IRR1) and also the Receive Flags (RXPR and RFPR) are set. In an analogous way, the overwriting of a data frame by a remote frame, leads to setting both IRR2 and IRR1.

In the Overrun Mode (NMC = '0'), only the first Mailbox will cause the flags to be asserted. So, if a Data Frame is initially received, then RXPR and IRR1 are both asserted. If a Remote Frame is then received before the Data Frame has been read, then RFPR and IRR2 are NOT set. In this case UMSR of the corresponding Mailbox will still be set.

# • Port A Control Register L1 (PACRL1)

| Bit:           | 15 | 14  | 13      | 12  | 11 | 10  | 9       | 8   | 7 | 6   | 5       | 4   | 3 | 2   | 1       | 0   |

|----------------|----|-----|---------|-----|----|-----|---------|-----|---|-----|---------|-----|---|-----|---------|-----|

| [              | -  | P   | A3MD[2: | 0]  | -  | P   | A2MD[2: | 0]  | - | P   | A1MD[2: | 0]  | - | P   | A0MD[2: | 0]  |

| Initial value: | 0  | 0   | 0       | 0   | 0  | 0   | 0       | 0   | 0 | 0   | 0       | 0   | 0 | 0   | 0       | 0   |

| R/W:           | R  | R/W | R/W     | R/W | R  | R/W | R/W     | R/W | R | R/W | R/W     | R/W | R | R/W | R/W     | R/W |

|          |            | Initial |     |                                                                                                                                                     |

|----------|------------|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit      | Bit Name   | Value   | R/W | Description                                                                                                                                         |

| 15       |            | 0       | R   | Reserved                                                                                                                                            |

|          |            |         |     | This bit is always read as 0. The write value should always be 0.                                                                                   |

| 14 to 12 | PA3MD[2:0] | 000     | R/W | PA3 Mode                                                                                                                                            |

|          |            |         |     | Select the function of the PA3/ $\overline{CS3}$ /RXD1/SSI/TMS pin. When using E10A ( $\overline{ASEMD0} = L$ ), these bits are fixed to TMS input. |

|          |            |         |     | 000: PA3 I/O (port)                                                                                                                                 |

|          |            |         |     | 001: CS3 output (BSC)                                                                                                                               |

|          |            |         |     | 010: Setting prohibited                                                                                                                             |

|          |            |         |     | 011: Setting prohibited                                                                                                                             |

|          |            |         |     | 100: Setting prohibited                                                                                                                             |

|          |            |         |     | 101: RXD1 input (SCI)                                                                                                                               |

|          |            |         |     | 110: Setting prohibited                                                                                                                             |

|          |            |         |     | 111: SSI I/O (SSU)                                                                                                                                  |

| 11       | _          | 0       | R   | Reserved                                                                                                                                            |

|          |            |         |     | This bit is always read as 0. The write value should always be 0.                                                                                   |

| Bit     | Bit Name   | Initial<br>Value | R/W | Description                                                          |

|---------|------------|------------------|-----|----------------------------------------------------------------------|

| 10 to 8 | PB6MD[2:0] | 000*             | R/W | PB6 Mode                                                             |

|         |            |                  |     | Select the function of the<br>PB6/A18/BACK/IRQ5/POE3/RXD0 pin.       |

|         |            |                  |     | 000: PB6 I/O (port)                                                  |

|         |            |                  |     | 001: A18 output (BSC)                                                |

|         |            |                  |     | 010: BACK input (BSC)                                                |

|         |            |                  |     | 011: IRQ5 input (INTC)                                               |

|         |            |                  |     | 100: POE3 I/O (POE2)                                                 |

|         |            |                  |     | 101: RXD0 input (SCI)                                                |

|         |            |                  |     | 110: Setting prohibited                                              |

|         |            |                  |     | 111: Setting prohibited                                              |

| 7 to 0  | _          | All 0            | R   | Reserved                                                             |

|         |            |                  |     | These bits are always read as 0. The write value should always be 0. |

Note: \* The initial value is 1 during the on-chip ROM disabled external extension mode.

#### • Port B Control Register L1 (PBCRL1)

| Bit:           | 15 | 14  | 13      | 12  | 11 | 10  | 9       | 8   | 7 | 6   | 5       | 4   | 3 | 2   | 1       | 0   |

|----------------|----|-----|---------|-----|----|-----|---------|-----|---|-----|---------|-----|---|-----|---------|-----|

|                | -  | Р   | B3MD[2: | 0]  | -  | P   | B2MD[2: | 0]  | - | Р   | B1MD[2: | 0]  | - | P   | B0MD[2: | 0]  |

| Initial value: | 0  | 0   | 0       | 0   | 0  | 0   | 0       | 0   | 0 | 0   | 0       | 0*  | 0 | 0   | 0       | 0*  |

| R/W:           | R  | R/W | R/W     | R/W | R  | R/W | R/W     | R/W | R | R/W | R/W     | R/W | R | R/W | R/W     | R/W |

Note: \* The initial value is 1 during the on-chip ROM disabled external extension mode.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                       |

|-----|----------|------------------|-----|-------------------------------------------------------------------|

| 15  | —        | 0                | R   | Reserved                                                          |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0. |

| Bit    | Bit Name   | Initial<br>Value | R/W | Description                                                       |

|--------|------------|------------------|-----|-------------------------------------------------------------------|

| 7      |            | 0                | R   | Reserved                                                          |

|        |            |                  |     | This bit is always read as 0. The write value should always be 0. |

| 6 to 4 | PC5MD[2:0] | 000*             | R/W | PC5 Mode                                                          |

|        |            |                  |     | Select the function of the PC5/A5 pin.                            |

|        |            |                  |     | 000: PC5 I/O (port)                                               |

|        |            |                  |     | 001: A5 output (BSC)                                              |

|        |            |                  |     | 010: Setting prohibited                                           |

|        |            |                  |     | 011: Setting prohibited                                           |

|        |            |                  |     | 100: Setting prohibited                                           |

|        |            |                  |     | 101: Setting prohibited                                           |

|        |            |                  |     | 110: Setting prohibited                                           |

|        |            |                  |     | 111: Setting prohibited                                           |

| 3      |            | 0                | R   | Reserved                                                          |

|        |            |                  |     | This bit is always read as 0. The write value should always be 0. |

| 2 to 0 | PC4MD[2:0] | 000*             | R/W | PC4 Mode                                                          |

|        |            |                  |     | Select the function of the PC4/A4 pin.                            |

|        |            |                  |     | 000: PC4 I/O (port)                                               |

|        |            |                  |     | 001: A4 output (BSC)                                              |

|        |            |                  |     | 010: Setting prohibited                                           |

|        |            |                  |     | 011: Setting prohibited                                           |

|        |            |                  |     | 100: Setting prohibited                                           |

|        |            |                  |     | 101: Setting prohibited                                           |

|        |            |                  |     | 110: Setting prohibited                                           |

|        |            |                  |     | 111: Setting prohibited                                           |

Note: \* The initial value is 1 during the on-chip ROM disabled external extension mode.

#### PBPRL (SH7285) . Bit: 15 7 14 13 12 10 9 8 6 5 3 2 1 0 11 4 PB12 PB11 PR PB10 PB9 PR PB8 PR PB7 PB6 PB3 PR PB2 PR PB1 PB0 --\_ \_ \_ PR PR PR PR PR PR 0 0 0 0 0 Initial value: \* \* \* \* \* \* \* \* \* \* \* R/W: R R R R R R R R R R R R R R R R Initial Bit Bit Name Value R/W Description 15 to 13 All 0 R Reserved These bits are always read as 0 and cannot be modified. 12 PB12PR Pin state R The pin state is returned regardless of the PFC setting. These bits cannot be modified. 11 PB11PR Pin state R 10 PB10PR Pin state R 9 R PB9PR Pin state 8 Pin state R PB8PR 7 PB7PR Pin state R 6 PB6PR Pin state R 5,4 \_\_\_\_ All 0 R Reserved These bits are always read as 0 and cannot be modified. З PB3PR Pin state R The pin state is returned regardless of the PFC setting. These bits cannot be modified. 2 PB2PR Pin state R 1 PB1PR Pin state R 0 PB0PR Pin state R

### 24.5.3 Port E Port Register L (PEPRL)

PEPRL is a 16-bit read-only register, which always return the states of the pins regardless of the PFC setting. In SH7243, SH7285 and SH7286, bits PE15PR to PE0PR correspond to pins PE15 to PE0 respectively (description of multiplexed functions are abbreviated here).

| Bit:           | 15         | 14         | 13         | 12         | 11         | 10         | 9         | 8         | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

|----------------|------------|------------|------------|------------|------------|------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

|                | PE15<br>PR | PE14<br>PR | PE13<br>PR | PE12<br>PR | PE11<br>PR | PE10<br>PR | PE9<br>PR | PE8<br>PR | PE7<br>PR | PE6<br>PR | PE5<br>PR | PE4<br>PR | PE3<br>PR | PE2<br>PR | PE1<br>PR | PE0<br>PR |

| Initial value: | *          | *          | *          | *          | *          | *          | *         | *         | *         | *         | *         | *         | *         | *         | *         | *         |

| R/W:           | R          | R          | R          | R          | R          | R          | R         | R         | R         | R         | R         | R         | R         | R         | R         | R         |

|     |          | Initial   |     |                                                          |

|-----|----------|-----------|-----|----------------------------------------------------------|

| Bit | Bit Name | Value     | R/W | Description                                              |

| 15  | PE15PR   | Pin state | R   | The pin state is returned regardless of the PFC setting. |

| 14  | PE14PR   | Pin state | R   | These bits cannot be modified.                           |

| 13  | PE13PR   | Pin state | R   | -                                                        |

| 12  | PE12PR   | Pin state | R   | -                                                        |

| 11  | PE11PR   | Pin state | R   | -                                                        |

| 10  | PE10PR   | Pin state | R   | -                                                        |

| 9   | PE9PR    | Pin state | R   | -                                                        |

| 8   | PE8PR    | Pin state | R   | -                                                        |

| 7   | PE7PR    | Pin state | R   |                                                          |

| 6   | PE6PR    | Pin state | R   | _                                                        |

| 5   | PE5PR    | Pin state | R   | -                                                        |

| 4   | PE4PR    | Pin state | R   | -                                                        |

| 3   | PE3PR    | Pin state | R   | -                                                        |

| 2   | PE2PR    | Pin state | R   | -                                                        |

| 1   | PE1PR    | Pin state | R   | -                                                        |

| 0   | PE0PR    | Pin state | R   | -                                                        |

|     |          |           |     |                                                          |

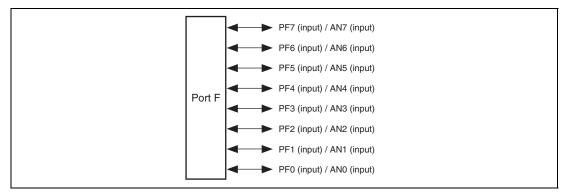

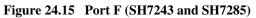

# 24.6 Port F

Port F in SH7243 and SH7285 is an I/O port with 8 pins shown in figure 24.15.

Port F in SH7286 is an I/O port with 12 pins shown in figure 24.16.

Figure 24.16 Port F (SH7286)

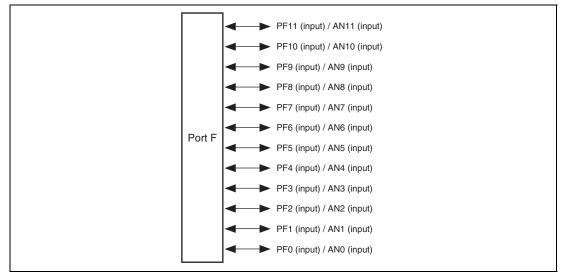

Figure 31.8 Bus Release Timing

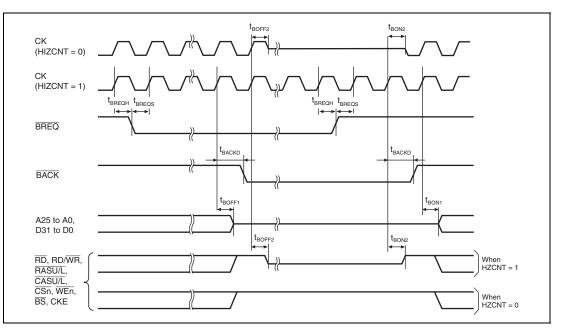

Figure 31.9 Interrupt Signal Output Timing

#### Page Revision (See Manual for Details)

Figure 14.1 Block Diagram of 733 Amended CMT

| Table 14.2 Interrupt Sources                                | 740 | Added                                                                                                                                                                                                                                                                                                           |  |  |

|-------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Figure 15.1 Block Diagram of WDT                            | 746 | Amended<br>Bus interface<br>Peripheral bus                                                                                                                                                                                                                                                                      |  |  |

| 15.3.2 Watchdog Timer<br>Control/Status Register<br>(WTCSR) | 749 | Added<br>WTCSR is initialized to H'18 by a power-on reset caused<br>by the RES pin, an internal reset caused by the WDT, or in<br>software standby mode.                                                                                                                                                        |  |  |

| 15.4.2 Using Watchdog<br>Timer Mode                         | 756 | <ul> <li>Added</li> <li>7. Since WTCSR is initialized by an internal reset caused by the WDT, the TME bit in WTCSR is cleared to 0. This makes the counter stop (be initialized). To use the WDT in watchdog timer mode again, after clearing the WOVF flag in WRCSR, set watchdog timer mode again.</li> </ul> |  |  |

| 15.5 Interrupt Source                                       | 759 | Added                                                                                                                                                                                                                                                                                                           |  |  |