# Enesas Electronics America Inc - R7FS124762A01CLM#AC0 Datasheet

Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                              |

| Core Processor             | ARM® Cortex®-M0+                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                    |

| Speed                      | 32MHz                                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI, UART/USART, USB                                   |

| Peripherals                | LVD, POR, PWM, WDT                                                                    |

| Number of I/O              | 25                                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                 |

| EPROM Size                 | 4K x 8                                                                                |

| RAM Size                   | 16K x 8                                                                               |

| /oltage - Supply (Vcc/Vdd) | 1.6V ~ 5.5V                                                                           |

| Data Converters            | A/D 11x14b; D/A 1x12b                                                                 |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 36-WFLGA                                                                              |

| Supplier Device Package    | 36-WFLGA (4x4)                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r7fs124762a01clm-ac0 |

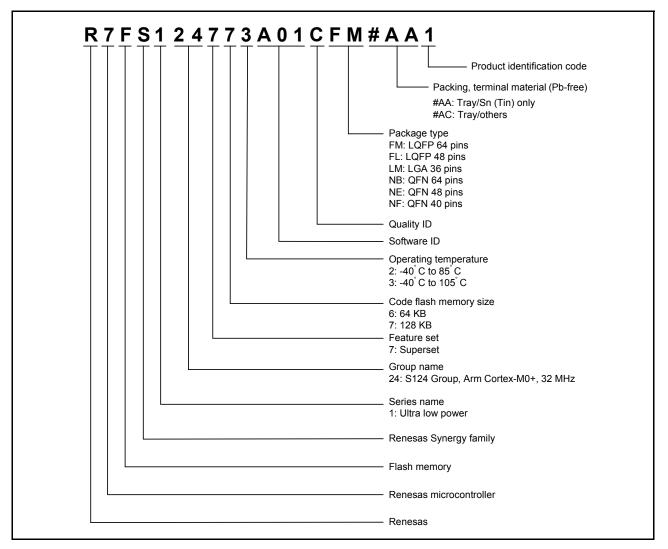

Figure 1.2 Part numbering scheme

Table 1.12 Product list

| Product part number | Orderable part number | Package code | Code flash | Data flash | SRAM  | Operating temperature |

|---------------------|-----------------------|--------------|------------|------------|-------|-----------------------|

| R7FS124773A01CFM    | R7FS124773A01CFM#AA1  | PLQP0064KB-C | 128 KB     | 4 KB       | 16 KB | -40 to +105°C         |

| R7FS124773A01CNB    | R7FS124773A01CNB#AC1  | PWQN0064LA-A |            |            |       | -40 to +105°C         |

| R7FS124773A01CFL    | R7FS124773A01CFL#AA1  | PLQP0048KB-B |            |            |       | -40 to +105°C         |

| R7FS124773A01CNE    | R7FS124773A01CNE#AC1  | PWQN0048KB-A |            |            |       | -40 to +105°C         |

| R7FS124773A01CNF    | R7FS124773A01CNF#AC1  | PWQN0040KC-A |            |            |       | -40 to +105°C         |

| R7FS124772A01CLM    | R7FS124772A01CLM#AC1  | PWLG0036KA-A |            |            |       | -40 to +85°C          |

| R7FS124763A01CFM    | R7FS124763A01CFM#AA1  | PLQP0064KB-C | 64 KB      |            |       | -40 to +105°C         |

| R7FS124763A01CFL    | R7FS124763A01CFL#AA1  | PLQP0048KB-B |            |            |       | -40 to +105°C         |

| R7FS124762A01CLM    | R7FS124762A01CLM#AC1  | PWLG0036KA-A |            |            |       | -40 to +85°C          |

Note: Earlier products with orderable part number suffix AA0 and AC0 have a restriction in AES functions. If AES functions are required for your application, refer to the products with orderable part number suffix AA1 or AC1. For details on the differences of AES functions between AA0/AC0 and AA1/AC1 products, see *Technical Update* (TN-SY\*-A024A/E). Contact your Renesas sales representative for additional information.

Table 1.14 Pin functions (3 of 3)

| Function  | Signal                               | I/O    | Description                                      |

|-----------|--------------------------------------|--------|--------------------------------------------------|

| ACMPLP    | VCOUT                                | Output | Comparator output pin.                           |

|           | CMPREF0,<br>CMPREF1                  | Input  | Reference voltage input pins.                    |

|           | CMPIN0,<br>CMPIN1                    | Input  | Analog voltage input pins.                       |

| CTSU      | TS00 to TS28,<br>TS30, TS31          | Input  | Capacitive touch detection pins (touch pins).    |

|           | TSCAP                                | -      | Secondary power supply pin for the touch driver. |

| KINT      | KR00 to KR07                         | Input  | Key interrupt input pins.                        |

| I/O ports | P000 to P004,<br>P010 to P015        | I/O    | General-purpose input/output pins.               |

|           | P100 to P113                         | I/O    | General-purpose input/output pins.               |

|           | P200                                 | Input  | General-purpose input pin.                       |

|           | P201, P204 to<br>P206, P212,<br>P213 | I/O    | General-purpose input/output pins.               |

|           | P214, P215                           | Input  | General-purpose input pins.                      |

|           | P300 to P304                         | I/O    | General-purpose input/output pins.               |

|           | P400 to P403,<br>P407 to P411        | I/O    | General-purpose input/output pins.               |

|           | P500 to P502                         | I/O    | General-purpose input/output pins.               |

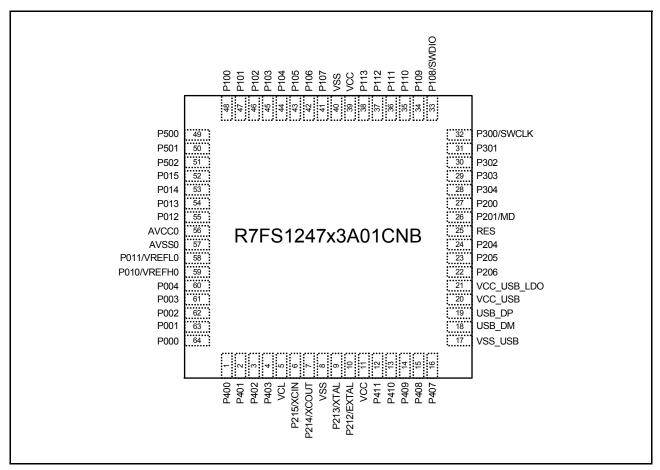

Figure 1.4 Pin assignment for QFN 64-pin (top view)

|               |        | Pin numbe | •     |       |                                        |           |              | Tin           | ners          |     | Co        | ommunicati                                                  | on Interfac | es           | Ana                    | logs          | Н       | МІ            |

|---------------|--------|-----------|-------|-------|----------------------------------------|-----------|--------------|---------------|---------------|-----|-----------|-------------------------------------------------------------|-------------|--------------|------------------------|---------------|---------|---------------|

| LQFP64, QFN64 | LQFP48 | QFN48     | QFN40 | LGA36 | Power, System,<br>Clock, Debug,<br>CAC | I/O ports | AGT          | GPT_OPS, POEG | GРТ           | RTC | USBFS,CAN | SCI                                                         | )IIC        | SPI          | ADC14                  | DAC12, ACMPLP | стѕи    | Interrupt     |

| 35            | 27     | 27        | 23    | D5    |                                        | P110      |              | GTOVLO<br>_A  | GTIOC1B<br>_A |     | CRX0_A    | CTS0_RT<br>S0_C/<br>SS0_C/<br>RXD9_B/<br>MISO9_B/<br>SCL9_B |             | MISOB_B      |                        | VCOUT         | TS11    | IRQ3          |

| 36            | 28     | 28        | 24    | D6    |                                        | P111      |              |               | GTIOC3A<br>_A |     |           | SCK0_C/<br>SCK9_B                                           |             | RSPCKB_<br>B |                        |               | TS12    | IRQ4          |

| 37            | 29     | 29        | 25    | C6    |                                        | P112      |              |               | GTIOC3B<br>_A |     |           | TXD0_C/<br>MOSI0_C/<br>SDA0_C                               |             |              |                        |               | TSCAP_C |               |

| 38            | -      | -         | -     | -     |                                        | P113      |              |               |               |     |           |                                                             |             |              |                        |               |         |               |

| 39            | 30     | 30        | -     | -     | VCC                                    |           |              |               |               |     |           |                                                             |             |              |                        |               |         |               |

| 40            | 31     | 31        | -     | -     | VSS                                    |           |              |               |               |     |           |                                                             |             |              |                        |               |         |               |

| 41            | -      | -         | -     | -     |                                        | P107      |              |               | GTIOC0A<br>_B |     |           |                                                             |             |              |                        |               |         | KR07          |

| 42            | -      | -         | -     | -     |                                        | P106      |              |               | GTIOC0B<br>_B |     |           |                                                             |             | SSLA3_A      |                        |               |         | KR06          |

| 43            | -      | -         | -     | -     |                                        | P105      |              | GTETRG<br>A_C | _5            |     |           |                                                             |             | SSLA2_A      |                        |               |         | KR05/<br>IRQ0 |

| 44            | 32     | 32        | 26    | -     |                                        | P104      |              | GTETRG<br>B_B |               |     |           | RXD0_C/<br>MISO0_C/<br>SCL0_C                               |             | SSLA1_A      |                        |               | TS13    | KR04/<br>IRQ1 |

| 45            | 33     | 33        | 27    | C3    |                                        | P103      |              | GTOWUP<br>_A  | GTIOC2A<br>_A |     | CTX0_C    | CTS0_RT<br>S0_A/<br>SS0_A                                   |             | SSLA0_A      | AN019                  | CMPREF<br>1   | TS14    | KR03          |

| 46            | 34     | 34        | 28    | C4    |                                        | P102      | AGTO0        | GTOWLO<br>_A  | GTIOC2B<br>_A |     | CRX0_C    | SCK0_A                                                      |             | RSPCKA_<br>A | AN020/<br>ADTRG0_<br>A | CMPIN1        | TS15    | KR02          |

| 47            | 35     | 35        | 29    | C5    |                                        | P101      | AGTEE0       | GTETRG<br>B_A | GTIOC5A<br>_A |     |           | TXD0_A/<br>MOSI0_A/<br>SDA0_A/<br>CTS1_RT<br>S1_A/<br>SS1_A | SDA1_B      | MOSIA_A      | AN021                  | CMPREF<br>0   | TS16    | KR01/<br>IRQ1 |

| 48            | 36     | 36        | 30    | B6    |                                        | P100      | AGTIO0_<br>A | GTETRG<br>A_A | GTIOC5B<br>_A |     |           | RXD0_A/<br>MISO0_A/<br>SCL0_A/<br>SCK1_A                    | SCL1_B      | MISOA_A      | AN022                  | CMPIN0        | TS26    | KR00/<br>IRQ2 |

| 49            | 37     | 37        | -     | -     |                                        | P500      | AGTOA0       | GTIU_B        | GTIOC2A<br>_B |     |           |                                                             |             |              | AN016                  |               | TS27    |               |

| 50            | -      | -         | -     | -     |                                        | P501      | AGTOB0       | GTIV_B        | GTIOC2B<br>_B |     |           |                                                             |             |              | AN017                  |               |         |               |

| 51            | -      | -         | -     | -     |                                        | P502      |              | GTIW_B        | GTIOC3B<br>_B |     |           |                                                             |             |              | AN018                  |               |         |               |

| 52            | 38     | 38        | 31    | A6    |                                        | P015      |              |               | _             |     |           |                                                             |             |              | AN010                  |               | TS28    | IRQ7          |

| 53            | 39     | 39        | 32    | A5    |                                        | P014      |              |               |               |     |           |                                                             |             |              | AN009                  | DA0           |         |               |

| 54            | 40     | 40        | 33    | B5    |                                        | P013      |              |               |               |     |           |                                                             |             |              | AN008                  |               |         |               |

| 55            | 41     | 41        | 34    | B4    |                                        | P012      |              |               |               |     |           |                                                             |             |              | AN007                  |               |         |               |

| 56            | 42     | 42        | 35    | A4    | AVCC0                                  |           |              |               |               |     |           |                                                             |             |              |                        |               |         |               |

| 57            | 43     | 43        | 36    | A3    | AVSS0                                  |           |              |               |               |     |           |                                                             |             |              |                        |               |         |               |

| 58            | 44     | 44        | 37    | В3    | VREFL0                                 | P011      |              |               |               |     |           |                                                             |             |              | AN006                  |               | TS31    |               |

| 59            | 45     | 45        | 38    | A2    | VREFH0                                 | P010      |              |               |               |     |           |                                                             |             |              | AN005                  |               | TS30    |               |

| 60            | -      | -         | -     | -     |                                        | P004      |              |               |               |     |           |                                                             |             |              | AN004                  |               | TS25    | IRQ3          |

| 61            | -      | -         | -     | -     |                                        | P003      |              |               |               |     |           |                                                             |             |              | AN003                  |               | TS24    |               |

| 62            | 46     | 46        | -     | -     |                                        | P002      |              |               |               |     |           |                                                             |             |              | AN002                  |               | TS23    | IRQ2          |

| 63            | 47     | 47        | 39    | -     |                                        | P001      |              |               |               |     |           |                                                             |             |              | AN001                  |               | TS22    | IRQ7          |

| 64            | 48     | 48        | 40    | B2    |                                        | P000      |              |               |               |     |           |                                                             |             |              | AN000                  |               | TS21    | IRQ6          |

Note: Several pin names have the added suffix of \_A, \_B, \_C, and \_D. The suffix can be ignored when assigning functionality.

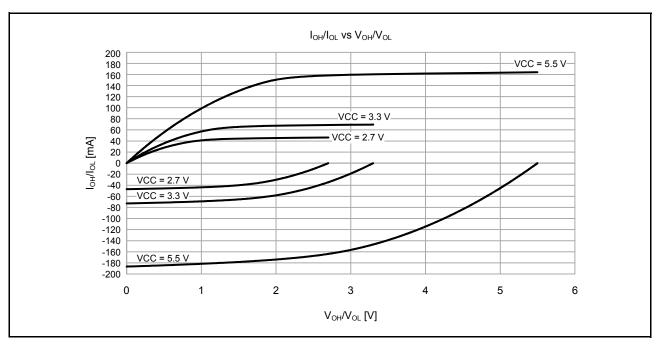

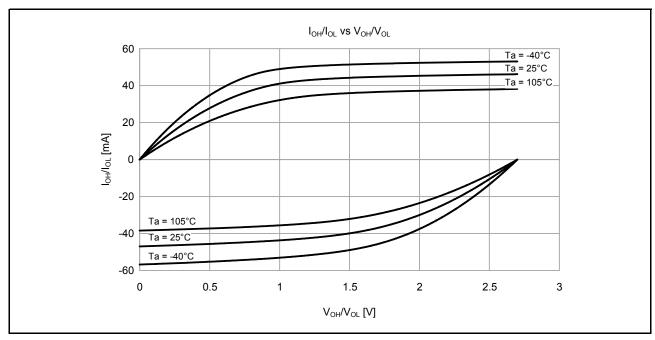

# 2.2.7 P408, P409 I/O Pin Output Characteristics of Middle Drive Capacity

Figure 2.12  $V_{OH}/V_{OL}$  and  $I_{OH}/I_{OL}$  voltage characteristics at Ta = 25°C when middle drive output is selected (reference data)

Figure 2.13  $V_{OH}/V_{OL}$  and  $I_{OH}/I_{OL}$  temperature characteristics at VCC = 2.7 V when middle drive output is selected (reference data)

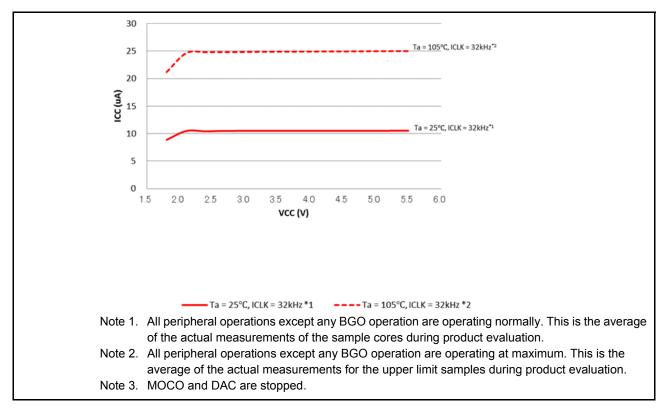

Figure 2.21 Voltage dependency in subosc-speed operating mode (reference data)

**Table 2.12** Operating and standby current (2) Conditions: VCC = AVCC0 = 1.6 to 5.5 V

| Parameter |                                        |                        | Symbol          | Typ*3 | Max  | Unit | Test conditions                             |

|-----------|----------------------------------------|------------------------|-----------------|-------|------|------|---------------------------------------------|

| Supply    | Software Standby                       | T <sub>a</sub> = 25°C  | I <sub>CC</sub> | 0.4   | 1.5  | μA   | -                                           |

| current*1 | mode*2                                 | T <sub>a</sub> = 55°C  |                 | 0.6   | 5.5  |      |                                             |

|           |                                        | T <sub>a</sub> = 85°C  |                 | 1.2   | 10.0 |      |                                             |

|           |                                        | T <sub>a</sub> = 105°C | 1               | 2.6   | 40.0 |      |                                             |

|           | Increment for RTC low-speed on-chip    | •                      |                 | 0.4   | -    |      | -                                           |

|           | Increment for RTC sub-clock oscillator | •                      |                 | 0.5   | -    |      | SOMCR.SODRV[1:0] are 11b (Low power mode 3) |

|           |                                        |                        |                 | 1.3   | -    |      | SOMCR.SODRV[1:0] are 00b (normal mode)      |

Note 1. Supply current values do not include output charge/discharge current from all pins. The values apply when internal pull-up MOS transistors are in the off state.

Note 2. The IWDT and LVD are not operating.

Note 3. VCC = 3.3 V.

Note 4. Includes the current of low-speed on-chip oscillator or sub-oscillation circuit.

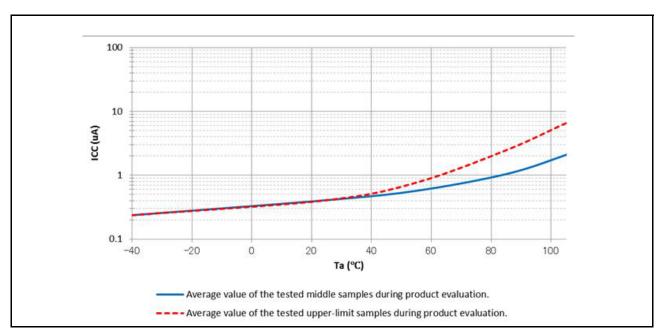

Figure 2.22 Temperature dependency in Software Standby mode (reference data)

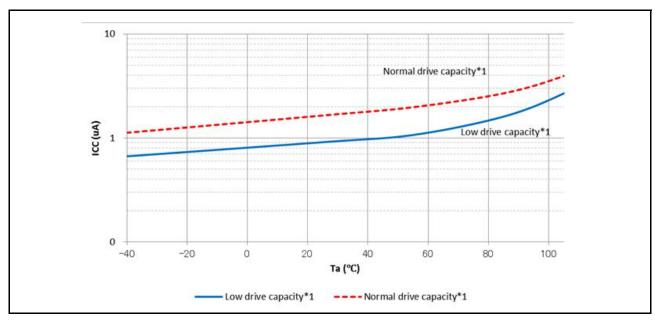

Figure 2.23 Temperature dependency of RTC operation (reference data)

Table 2.13 Operating and standby current (3) (1 of 2) Conditions: VCC = AVCC0 = 1.6 to 5.5 V

| Parameter               |                                                  | Symbol             | Min | Тур | Max | Unit | Test conditions |

|-------------------------|--------------------------------------------------|--------------------|-----|-----|-----|------|-----------------|

| Analog power            | During A/D conversion (at high-speed conversion) |                    | -   | -   | 3.0 | mA   | -               |

| supply current          | During A/D conversion (at low-power conversion)  |                    | -   | -   | 1.0 | mA   | -               |

|                         | During D/A conversion*1                          |                    | -   | 0.4 | 0.8 | mA   | -               |

|                         | Waiting for A/D and D/A conversion (all units)*5 |                    | -   | -   | 1.0 | μA   | -               |

| Reference               | During A/D conversion                            | I <sub>REFH0</sub> | -   | -   | 150 | μA   | -               |

| power supply<br>current | Waiting for A/D conversion (all units)           |                    | -   | -   | 60  | nA   | -               |

| Temperature sen         | sor                                              | I <sub>TNS</sub>   | -   | 75  | -   | μA   | -               |

# 2.2.10 VCC Rise and Fall Gradient and Ripple Frequency

Table 2.14 Rise and fall gradient characteristics

Conditions: VCC = AVCC0 = 0 to 5.5 V

| Parameter       |                                                  | Symbol | Min  | Тур | Max | Unit | Test conditions |

|-----------------|--------------------------------------------------|--------|------|-----|-----|------|-----------------|

| Power-on VCC    | Voltage monitor 0 reset disabled at startup      | SrVCC  | 0.02 | -   | 2   | ms/V | -               |

| rising gradient | Voltage monitor 0 reset enabled at startup*1, *2 |        | 0.02 | -   | -   |      |                 |

|                 | SCI Boot mode*2                                  |        | 0.02 | -   | 2   |      |                 |

Note 1. When OFS1.LVDAS = 0.

Note 2. At boot mode, the reset from voltage monitor 0 is disabled regardless of the value of OFS1.LVDAS bit.

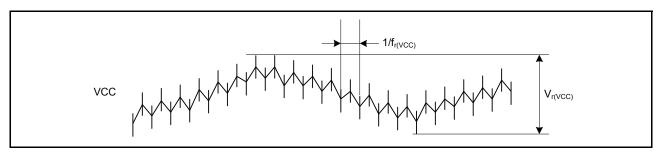

#### Table 2.15 Rising and falling gradient and ripple frequency characteristics

Conditions: VCC = AVCC0 = 1.6 to 5.5 V

The ripple voltage must meet the allowable ripple frequency  $f_{r(VCC)}$  within the range between the VCC upper limit (5.5 V) and lower limit (1.6 V).

When the VCC change exceeds VCC ±10%, the allowable voltage change rising and falling gradient dt/dVCC must be met.

| Parameter                                            | Symbol               | Min | Тур | Max | Unit | Test conditions                                  |

|------------------------------------------------------|----------------------|-----|-----|-----|------|--------------------------------------------------|

| Allowable ripple frequency                           | f <sub>r (VCC)</sub> | -   | -   | 10  | kHz  | Figure 2.24<br>V <sub>r (VCC)</sub> ≤ VCC × 0.2  |

|                                                      |                      | -   | -   | 1   | MHz  | Figure 2.24<br>V <sub>r (VCC)</sub> ≤ VCC × 0.08 |

|                                                      |                      | -   | -   | 10  | MHz  | Figure 2.24<br>V <sub>r (VCC)</sub> ≤ VCC × 0.06 |

| Allowable voltage change rising and falling gradient | dt/dVCC              | 1.0 | -   | -   | ms/V | When VCC change exceeds VCC ±10%                 |

Figure 2.24 Ripple waveform

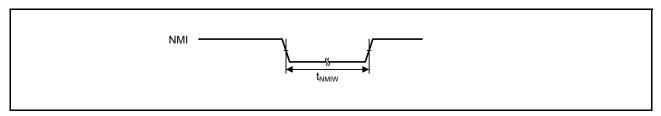

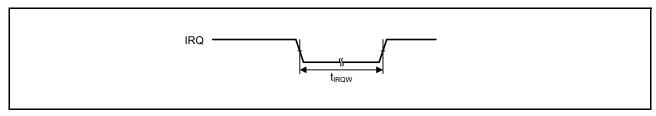

### 2.3.5 NMI and IRQ Noise Filter

Table 2.29 NMI and IRQ noise filter

| Parameter       | Symbol            | Symbol Min                 | Тур | Max | Unit | Test conditions             |                                 |  |  |  |

|-----------------|-------------------|----------------------------|-----|-----|------|-----------------------------|---------------------------------|--|--|--|

| NMI pulse width | t <sub>NMIW</sub> | 200                        | -   | -   | ns   | NMI digital filter disabled | t <sub>Pcyc</sub> × 2 ≤ 200 ns  |  |  |  |

|                 |                   | t <sub>Pcyc</sub> × 2*1    | -   | -   |      |                             | t <sub>Pcyc</sub> × 2 > 200 ns  |  |  |  |

|                 |                   | 200                        | -   | -   |      | NMI digital filter enabled  | t <sub>NMICK</sub> × 3 ≤ 200 ns |  |  |  |

|                 |                   | t <sub>NMICK</sub> × 3.5*2 | -   | -   |      |                             | t <sub>NMICK</sub> × 3 > 200 ns |  |  |  |

| IRQ pulse width | t <sub>IRQW</sub> | 200                        | -   | -   | ns   | IRQ digital filter disabled | t <sub>Pcyc</sub> × 2 ≤ 200 ns  |  |  |  |

|                 |                   | t <sub>Pcyc</sub> × 2*1    | -   | -   |      |                             | t <sub>Pcyc</sub> × 2 > 200 ns  |  |  |  |

|                 |                   | 200                        | -   | -   |      | IRQ digital filter enabled  | t <sub>IRQCK</sub> × 3 ≤ 200 ns |  |  |  |

|                 |                   | t <sub>IRQCK</sub> × 3.5*3 | -   | -   |      |                             | t <sub>IRQCK</sub> × 3 > 200 ns |  |  |  |

Note: 200 ns minimum in Software Standby mode.

Note 1.  $t_{\text{Pcyc}}$  indicates the PCLKB cycle.

Note 2.  $t_{\text{NMICK}}$  indicates the cycle of the NMI digital filter sampling clock.

Note 3.  $t_{IRQCK}$  indicates the cycle of the IRQi digital filter sampling clock (i = 0 to 7).

Figure 2.33 NMI interrupt input timing

Figure 2.34 IRQ interrupt input timing

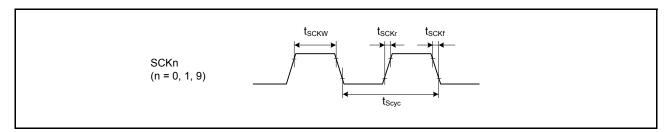

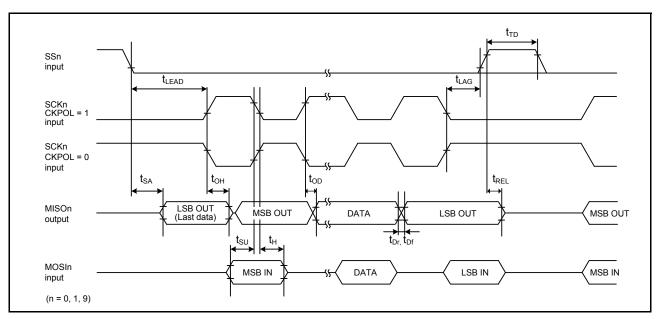

Figure 2.41 SCK clock input timing

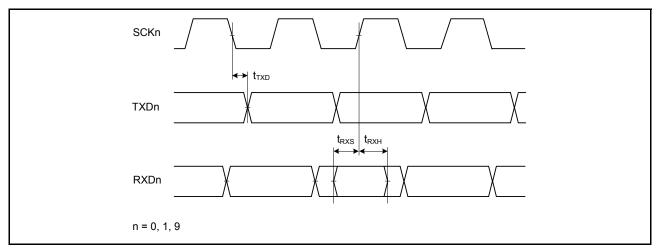

Figure 2.42 SCI input/output timing in clock synchronous mode

Figure 2.47 SCI simple SPI mode timing (slave, CKPH = 0)

Table 2.34 SCI timing (3)

Conditions: VCC = AVCC0 = 2.7 to 5.5 V

| Parameter       |                                    | Symbol            | Min | Max                     | Unit | Test conditions |  |

|-----------------|------------------------------------|-------------------|-----|-------------------------|------|-----------------|--|

| Simple IIC      | SDA input rise time                | t <sub>Sr</sub>   | -   | 1000                    | ns   | Figure 2.48     |  |

| (Standard mode) | SDA input fall time                | t <sub>Sf</sub>   | -   | 300                     | ns   |                 |  |

|                 | SDA input spike pulse removal time | t <sub>SP</sub>   | 0   | 4 × t <sub>IICcyc</sub> | ns   | ]               |  |

|                 | Data input setup time              | t <sub>SDAS</sub> | 250 | -                       | ns   | 1               |  |

|                 | Data input hold time               | t <sub>SDAH</sub> | 0   | -                       | ns   | 1               |  |

|                 | SCL, SDA capacitive load           | C <sub>b</sub> *1 | -   | 400                     | pF   |                 |  |

| Simple IIC*2    | SDA input rise time                | t <sub>Sr</sub>   | -   | 300                     | ns   | Figure 2.48     |  |

| (Fast mode)     | SDA input fall time                | t <sub>Sf</sub>   | -   | 300                     | ns   |                 |  |

|                 | SDA input spike pulse removal time | t <sub>SP</sub>   | 0   | 4 × t <sub>IICcyc</sub> | ns   | 1               |  |

|                 | Data input setup time              | t <sub>SDAS</sub> | 100 | -                       | ns   |                 |  |

|                 | Data input hold time               | t <sub>SDAH</sub> | 0   | -                       | ns   |                 |  |

|                 | SCL, SDA capacitive load           | C <sub>b</sub> *1 | -   | 400                     | pF   | ]               |  |

Note:  $t_{\text{IICcyc}}$ : Clock cycle selected by the SMR.CKS[1:0] bits.

Note 1. Cb indicates the total capacity of the bus line.

Note 2. Middle drive output is selected in the Port Drive Capability bit in the PmnPFS register.

Figure 2.55 SPI timing (slave, CPHA = 1)

# 2.3.10 IIC Timing

Table 2.36 IIC timing Conditions: VCC = AVCC0 = 2.7 to 5.5 V

| Parameter                 |                                                                    | Symbol            | Min* <sup>1</sup>                                            | Max                         | Unit | Test conditions |  |

|---------------------------|--------------------------------------------------------------------|-------------------|--------------------------------------------------------------|-----------------------------|------|-----------------|--|

| IIC                       | SCL input cycle time                                               | t <sub>SCL</sub>  | 6 (12) × t <sub>IICcyc</sub> + 1300                          | -                           | ns   | Figure 2.56     |  |

| (standard mode,<br>SMBus) | SCL input high pulse width                                         | t <sub>SCLH</sub> | 3 (6) × t <sub>IICcyc</sub> + 300                            | -                           | ns   |                 |  |

| ONDUO)                    | SCL input low pulse width                                          | t <sub>SCLL</sub> | 3 (6) × t <sub>IICcyc</sub> + 300                            | -                           | ns   |                 |  |

|                           | SCL, SDA input rise time                                           | t <sub>Sr</sub>   | -                                                            | 1000                        | ns   |                 |  |

|                           | SCL, SDA input fall time                                           | t <sub>Sf</sub>   | -                                                            | 300                         | ns   |                 |  |

|                           | SCL, SDA input spike pulse removal time                            | t <sub>SP</sub>   | 0                                                            | 1 (4) × t <sub>IICcyc</sub> | ns   |                 |  |

|                           | SDA input bus free time (When wakeup function is disabled)         | t <sub>BUF</sub>  | 3 (6) × t <sub>IICcyc</sub> + 300                            | -                           | ns   |                 |  |

|                           | SDA input bus free time<br>(When wakeup function is enabled)       | t <sub>BUF</sub>  | 3 (6) × t <sub>IICcyc</sub> + 4 × t <sub>Pcyc</sub><br>+ 300 | -                           | ns   |                 |  |

|                           | START condition input hold time (When wakeup function is disabled) | t <sub>STAH</sub> | t <sub>IICcyc</sub> + 300                                    | -                           | ns   |                 |  |

|                           | START condition input hold time (When wakeup function is enabled)  | t <sub>STAH</sub> | 1 (5) × t <sub>IICcyc</sub> + t <sub>Pcyc</sub> + 300        | -                           | ns   |                 |  |

|                           | Repeated START condition input setup time                          | t <sub>STAS</sub> | 1000                                                         | -                           | ns   |                 |  |

|                           | STOP condition input setup time                                    | t <sub>STOS</sub> | 1000                                                         | -                           | ns   |                 |  |

|                           | Data input setup time                                              | t <sub>SDAS</sub> | t <sub>IICcyc</sub> + 50                                     | -                           | ns   |                 |  |

|                           | Data input hold time                                               | t <sub>SDAH</sub> | 0                                                            | -                           | ns   |                 |  |

|                           | SCL, SDA capacitive load                                           | C <sub>b</sub>    | -                                                            | 400                         | pF   |                 |  |

| IIC*2                     | SCL input cycle time                                               | t <sub>SCL</sub>  | 6 (12) × t <sub>IICcyc</sub> + 600                           | -                           | ns   | Figure 2.5      |  |

| (Fast mode)               | SCL input high pulse width                                         | t <sub>SCLH</sub> | 3 (6) × t <sub>IICcyc</sub> + 300                            | -                           | ns   |                 |  |

|                           | SCL input low pulse width                                          | t <sub>SCLL</sub> | 3 (6) × t <sub>IICcyc</sub> + 300                            | -                           | ns   |                 |  |

|                           | SCL, SDA input rise time                                           | t <sub>Sr</sub>   | -                                                            | 300                         | ns   |                 |  |

|                           | SCL, SDA input fall time                                           | t <sub>Sf</sub>   | -                                                            | 300                         | ns   |                 |  |

|                           | SCL, SDA input spike pulse removal time                            | t <sub>SP</sub>   | 0                                                            | 1 (4) × t <sub>IICcyc</sub> | ns   |                 |  |

|                           | SDA input bus free time<br>(When wakeup function is disabled)      | t <sub>BUF</sub>  | 3 (6) × t <sub>IICcyc</sub> + 300                            | -                           | ns   |                 |  |

|                           | SDA input bus free time<br>(When wakeup function is enabled)       | t <sub>BUF</sub>  | 3 (6) × t <sub>IICcyc</sub> + 4 × t <sub>Pcyc</sub><br>+ 300 | -                           | ns   |                 |  |

|                           | START condition input hold time (When wakeup function is disabled) | t <sub>STAH</sub> | t <sub>IICcyc</sub> + 300                                    | -                           | ns   |                 |  |

|                           | START condition input hold time (When wakeup function is enabled)  | t <sub>STAH</sub> | 1(5) × t <sub>IICcyc</sub> + t <sub>Pcyc</sub> + 300         | -                           | ns   |                 |  |

|                           | Repeated START condition input setup time                          | t <sub>STAS</sub> | 300                                                          | -                           | ns   |                 |  |

|                           | STOP condition input setup time                                    | t <sub>STOS</sub> | 300                                                          | -                           | ns   | ]               |  |

|                           | Data input setup time                                              | t <sub>SDAS</sub> | t <sub>IICcyc</sub> + 50                                     | -                           | ns   | ]               |  |

|                           | Data input hold time                                               | t <sub>SDAH</sub> | 0                                                            | -                           | ns   | ]               |  |

|                           | SCL, SDA capacitive load                                           | C <sub>b</sub>    | -                                                            | 400                         | pF   | 1               |  |

Note:  $t_{\text{IICcyc}}$ : IIC internal reference clock (IIC $\phi$ ) cycle,  $t_{\text{Pcyc}}$ : PCLKB cycle

Note 1. Values in parentheses apply when ICMR3.NF[1:0] is set to 11b while the digital filter is enabled with ICFER.NFE set to 1.

Note 2. Middle drive output is selected in the Port Drive Capability bit in the PmnPFS register.

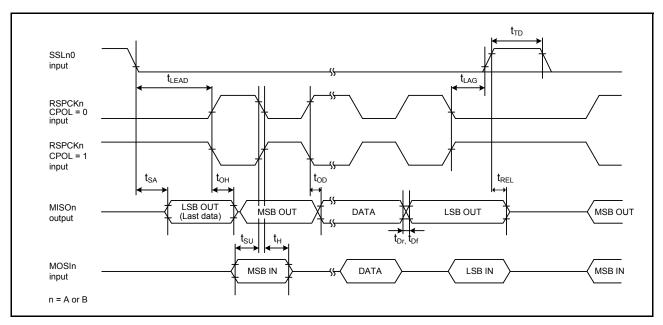

## 2.3.11 CLKOUT Timing

Table 2.37 CLKOUT timing

| Parameter |                               |                      | Symbol            | Min  | Max | Unit*1 | Test conditions |  |  |

|-----------|-------------------------------|----------------------|-------------------|------|-----|--------|-----------------|--|--|

| CLKOUT    | CLKOUT pin output cycle*1     | VCC = 2.7 V or above | t <sub>Ccyc</sub> | 62.5 | -   | ns     | Figure 2.57     |  |  |

|           |                               | VCC = 1.8 V or above |                   | 125  | -   |        |                 |  |  |

|           |                               | VCC = 1.6 V or above |                   | 250  | -   |        |                 |  |  |

|           | CLKOUT pin high pulse width*2 | VCC = 2.7 V or above | t <sub>CH</sub>   | 15   | -   | ns     |                 |  |  |

|           |                               | VCC = 1.8 V or above |                   | 30   | -   |        |                 |  |  |

|           |                               | VCC = 1.6 V or above |                   | 150  | -   |        |                 |  |  |

|           | CLKOUT pin low pulse width*2  | VCC = 2.7 V or above | t <sub>CL</sub>   | 15   | -   | ns     |                 |  |  |

|           |                               | VCC = 1.8 V or above |                   | 30   | -   |        |                 |  |  |

|           |                               | VCC = 1.6 V or above |                   | 150  | -   |        |                 |  |  |

|           | CLKOUT pin output rise time   | VCC = 2.7 V or above | t <sub>Cr</sub>   | -    | 12  | ns     |                 |  |  |

|           |                               | VCC = 1.8 V or above |                   | -    | 25  |        |                 |  |  |

|           |                               | VCC = 1.6 V or above |                   | -    | 50  |        |                 |  |  |

|           | CLKOUT pin output fall time   | VCC = 2.7 V or above | t <sub>Cf</sub>   | -    | 12  | ns     |                 |  |  |

|           |                               | VCC = 1.8 V or above |                   | -    | 25  |        |                 |  |  |

|           |                               | VCC = 1.6 V or above |                   | -    | 50  |        |                 |  |  |

- Note 1. When the EXTAL external clock input or an oscillator is used with division by 1 (the CKOCR.CKOSEL[2:0] bits are 011b and the CKOCR.CKODIV[2:0] bits are 000b) to output from CLKOUT, the above should be satisfied with an input duty cycle of 45 to 55%.

- Note 2. When the MOCO is selected as the clock output source (the CKOCR.CKOSEL[2:0] bits are 001b), set the clock output division ratio selection to be divided by 2 (the CKOCR.CKODIV[2:0] bits are 001b).

Figure 2.57 CLKOUT output timing

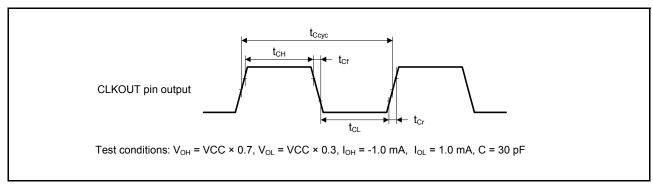

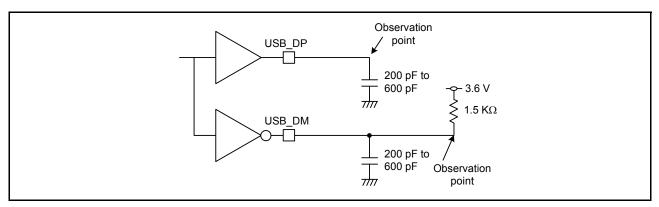

Figure 2.59 Test circuit for Full-Speed (FS) connection

Figure 2.60 Test circuit for Low-Speed (LS) connection

# 2.4.2 USB External Supply

Table 2.39 USB regulator

| Parameter              | Min                | Тур | Max | Unit | Test conditions |   |

|------------------------|--------------------|-----|-----|------|-----------------|---|

| VCC_USB supply current | VCC_USB_LDO ≥ 3.8V | -   | -   | 50   | mA              | - |

|                        | VCC_USB_LDO ≥ 4.5V | -   | -   | 100  | mA              | - |

| VCC_USB supply voltage |                    | 3.0 | -   | 3.6  | V               | - |

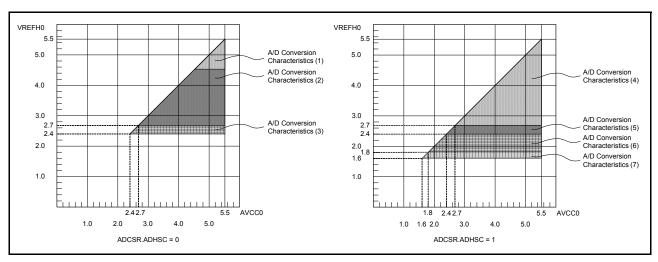

### 2.5 ADC14 Characteristics

Figure 2.61 AVCC0 to VREFH0 voltage range

Table 2.40 A/D conversion characteristics (1) in high-speed A/D conversion mode (1 of 2) Conditions: VCC = AVCC0 = 4.5 to 5.5 V, VREFH0 = 4.5 to 5.5 V, VSS = AVSS0 = VREFL0 = 0V Reference voltage range applied to the VREFH0 and VREFL0.

| Parameter<br>Frequency                                                             |  |        | Min   | Тур   | Max    | Unit                   | Test Conditions                                                       |

|------------------------------------------------------------------------------------|--|--------|-------|-------|--------|------------------------|-----------------------------------------------------------------------|

|                                                                                    |  |        | 1     | -     | 64     | MHz                    | -                                                                     |

| Analog input capacitance*2 Cs                                                      |  | -      | -     | 8*3   | pF     | High-precision channel |                                                                       |

|                                                                                    |  |        | -     | -     | 9*3    | pF                     | Normal-precision channel                                              |

| Analog input resistance Rs                                                         |  | -      | -     | 2.5*3 | kΩ     | High-precision channel |                                                                       |

|                                                                                    |  |        | -     | -     | 6.7*3  | kΩ                     | Normal-precision channel                                              |

| Analog input voltage range Ain                                                     |  | Ain    | 0     | -     | VREFH0 | V                      | -                                                                     |

| 12-bit mode                                                                        |  |        |       |       |        | I                      | <b>'</b>                                                              |

| Resolution                                                                         |  | -      | -     | 12    | Bit    | -                      |                                                                       |

| Conversion time*1 (Operation at PCLKD = 64 MHz)  Permissible source imp Max. = 0.3 |  | edance | 0.70  | -     | -      | μs                     | High-precision channel<br>ADCSR.ADHSC = 0<br>ADSSTRn.SST[7:0] = 0Dh   |

|                                                                                    |  |        | 1.13  | -     | -      | μs                     | Normal-precision channel<br>ADCSR.ADHSC = 0<br>ADSSTRn.SST[7:0] = 28h |

| Offset error                                                                       |  | -      | ±0.5  | ±4.5  | LSB    | High-precision channel |                                                                       |

|                                                                                    |  |        |       | ±6.0  | LSB    | Other than above       |                                                                       |

| Full-scale error                                                                   |  | -      | ±0.75 | ±4.5  | LSB    | High-precision channel |                                                                       |

|                                                                                    |  |        |       | ±6.0  | LSB    | Other than above       |                                                                       |

| Quantization error                                                                 |  | -      | ±0.5  | -     | LSB    | -                      |                                                                       |

| Absolute accuracy                                                                  |  | -      | ±1.25 | ±5.0  | LSB    | High-precision channel |                                                                       |

|                                                                                    |  |        |       | ±8.0  | LSB    | Other than above       |                                                                       |

| DNL differential nonlinearity error                                                |  | -      | ±1.0  | -     | LSB    | -                      |                                                                       |

| INL integral nonlinearity error                                                    |  | -      | ±1.0  | ±3.0  | LSB    | -                      |                                                                       |

| 14-bit mode                                                                        |  |        |       | •     | •      |                        | •                                                                     |

| Resolution                                                                         |  | -      | -     | 14    | Bit    | -                      |                                                                       |

Table 2.45 A/D conversion characteristics (6) in low-power A/D conversion mode (2 of 2)

Conditions: VCC = AVCC0 = 1.8 to 5.5 V (AVCC0 = VCC when VCC < 2.0 V), VREFH0 = 1.8 to 5.5 V, VSS = AVSS0 = VREFL0 = 0 V Reference voltage range applied to the VREFH0 and VREFL0.

| Parameter                                            |                                                                | Min   | Тур   | Max   | Unit | Test Conditions                                                       |

|------------------------------------------------------|----------------------------------------------------------------|-------|-------|-------|------|-----------------------------------------------------------------------|

| Conversion time*1<br>(Operation at<br>PCLKD = 8 MHz) | Permissible signal<br>source impedance<br>Max. = 5 kΩ          | 6.75  | -     | -     | μs   | High-precision channel<br>ADCSR.ADHSC = 1<br>ADSSTRn.SST[7:0] = 0Dh   |

|                                                      |                                                                | 10.13 | -     | -     | μs   | Normal-precision channel<br>ADCSR.ADHSC = 1<br>ADSSTRn.SST[7:0] = 28h |

| Offset error                                         |                                                                | -     | ±1.0  | ±7.5  | LSB  | High-precision channel                                                |

|                                                      |                                                                |       |       | ±10.0 | LSB  | Other than above                                                      |

| Full-scale error                                     |                                                                | -     | ±1.5  | ±7.5  | LSB  | High-precision channel                                                |

|                                                      |                                                                |       |       | ±10.0 | LSB  | Other than above                                                      |

| Quantization error                                   |                                                                | -     | ±0.5  | -     | LSB  | -                                                                     |

| Absolute accuracy                                    |                                                                | -     | ±3.0  | ±8.0  | LSB  | High-precision channel                                                |

|                                                      |                                                                |       |       | ±12.0 | LSB  | Other than above                                                      |

| DNL differential nonlinearity error                  |                                                                | -     | ±1.0  | -     | LSB  | -                                                                     |

| INL integral nonlinearity error                      |                                                                | -     | ±1.0  | ±3.0  | LSB  | -                                                                     |

| 14-bit mode                                          |                                                                | *     |       | •     | •    | <u> </u>                                                              |

| Resolution                                           |                                                                | -     | -     | 14    | Bit  | -                                                                     |

| Conversion time*1<br>(Operation at<br>PCLKD = 8 MHz) | Permissible signal source impedance Max. = $5 \text{ k}\Omega$ | 7.50  | -     | -     | μs   | High-precision channel<br>ADCSR.ADHSC = 1<br>ADSSTRn.SST[7:0] = 0Dh   |

|                                                      |                                                                | 10.88 | -     | -     | μs   | Normal-precision channel<br>ADCSR.ADHSC = 1<br>ADSSTRn.SST[7:0] = 28h |

| Offset error                                         |                                                                | -     | ±4.0  | ±30.0 | LSB  | High-precision channel                                                |

|                                                      |                                                                |       |       | ±40.0 | LSB  | Other than above                                                      |

| Full-scale error                                     |                                                                | -     | ±6.0  | ±30.0 | LSB  | High-precision channel                                                |

|                                                      |                                                                |       |       | ±40.0 | LSB  | Other than above                                                      |

| Quantization error                                   |                                                                | -     | ±0.5  | -     | LSB  | -                                                                     |

| Absolute accuracy                                    |                                                                | -     | ±12.0 | ±32.0 | LSB  | High-precision channel                                                |

|                                                      |                                                                |       |       | ±48.0 | LSB  | Other than above                                                      |

| DNL differential nonlinearity error                  |                                                                | -     | ±4.0  | -     | LSB  | -                                                                     |

| INL integral nonlinearity error                      |                                                                | -     | ±4.0  | ±12.0 | LSB  | -                                                                     |

Note: The characteristics apply when no pin functions other than 14-bit A/D converter input are used. Absolute accuracy does not include quantization errors. Offset error, full-scale error, DNL differential nonlinearity error, and INL integral nonlinearity error do not include quantization errors.

- Note 1. The conversion time is the sum of the sampling time and the comparison time. The number of sampling states is indicated for the test conditions.

- Note 2. Except for I/O input capacitance (Cin), see section 2.2.4, I/O VOH, VOL, and Other Characteristics.

- Note 3. Reference data.

Table 2.46 A/D conversion characteristics (7) in low-power A/D conversion mode (1 of 2)

Conditions: VCC = AVCC0 = 1.6 to 5.5 V (AVCC0 = VCC when VCC < 2.0 V), VREFH0 = 1.6 to 5.5 V, VSS = AVSS0 = VREFL0 = 0

Reference voltage range applied to the VREFH0 and VREFL0.

| Parameter<br>Frequency     |    | Min | Тур | Max                | Unit | Test Conditions          |

|----------------------------|----|-----|-----|--------------------|------|--------------------------|

|                            |    | 1   | -   | 4                  | MHz  |                          |

| Analog input capacitance*2 | Cs | -   | -   | 8*3                | pF   | High-precision channel   |

|                            |    | -   | -   | 9*3                | pF   | Normal-precision channel |

| Analog input resistance    | Rs | -   | -   | 13.1* <sup>3</sup> | kΩ   | High-precision channel   |

|                            |    | -   | -   | 14.3* <sup>3</sup> | kΩ   | Normal-precision channel |

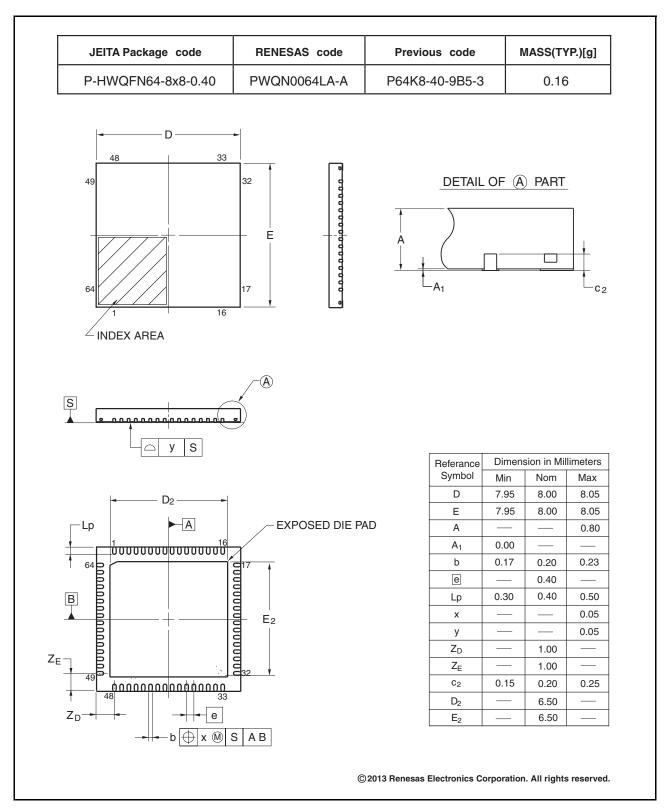

Figure 1.4 QFN 64-pin

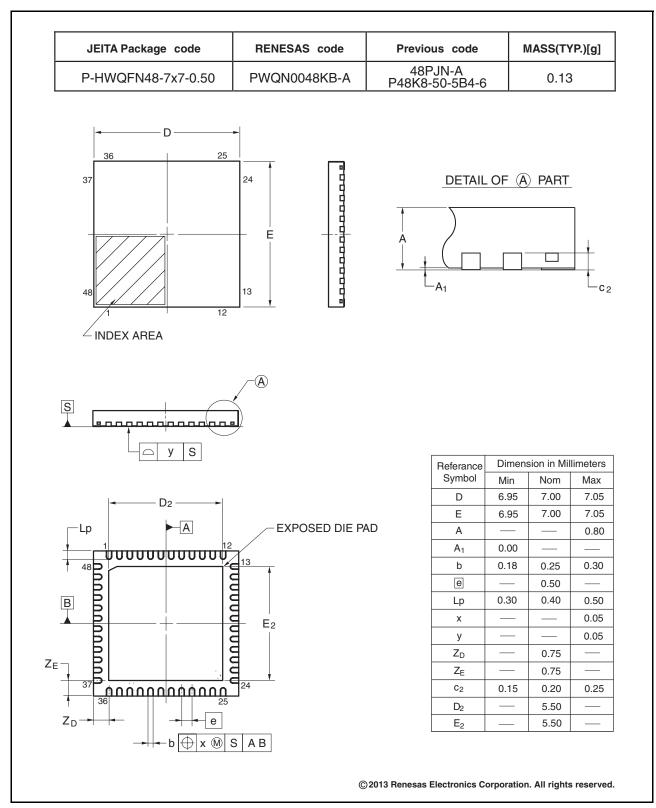

Figure 1.5 QFN 48-pin

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard" Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc. Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics

(Rev.4.0-1 November 2017)

#### SALES OFFICES

## Renesas Electronics Corporation

http://www.renesas.com

Refer to "http://www.renesas.com/" for the latest and detailed information

Renesas Electronics America Inc. 1001 Murphy Ranch Road, Milpitas, CA 95035, U.S.A Tel: +1-408-432-8888, Fax: +1-408-434-5351

Renesas Electronics Canada Limited 9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3 Tel: +1-905-237-2004

Renesas Electronics Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tel: +44-1628-651-700, Fax: +44-1628-651-804

Renesas Electronics Europe GmbH

Arcadiastrasse 10, 40472 Düsseldorf, Germany Tel: +49-211-6503-0, Fax: +49-211-6503-1327

Renesas Electronics (China) Co., Ltd.

Room 1709 Quantum Plaza, No.27 ZhichunLu, Haidian District, Beijing, 100191 P. R. China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679

Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, 200333 P. R. China Tel: +86-21-2226-0888, Fax: +86-21-2226-0999

Renesas Electronics Hong Kong Limited

Unit 1601-1611, 161F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong

Tel: +852-2265-6688, Fax: +852 2886-9022

Renesas Electronics Taiwan Co., Ltd.

13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670

Renesas Electronics Singapore Pte. Ltd.

80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949

Tel: +65-6213-0200, Fax: +65-6213-0300

Renesas Electronics Malaysia Sdn.Bhd.

Unit 1207, Block B, Menara Amcorp, Amcorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: +60-3-7955-9309, Fax: +60-3-7955-9501

Renesas Electronics India Pvt. Ltd. No.777C, 100 Feat Road, HAL 2nd Stage, Indiranagar, Bangalore 560 038, India Tel: +91-80-67208700, Fax: +91-80-67208777

Renesas Electronics Korea Co., Ltd.

17F, KAMCO Yangjae Tower, 262, Gangnam-daero, Gangnam-gu, Seoul, 06265 Korea Tel: +82-2-558-3737, Fax: +82-2-558-5338