# E. Kenesas Electronics America Inc - <u>R7FS124763A01CFM#AA1 Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                |

|----------------------------|---------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                    |

| Speed                      | 32MHz                                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI, UART/USART, USB                                   |

| Peripherals                | LVD, POR, PWM, WDT                                                                    |

| Number of I/O              | 51                                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | 4K x 8                                                                                |

| RAM Size                   | 16K × 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 5.5V                                                                           |

| Data Converters            | A/D 18x14b; D/A 1x12b                                                                 |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 64-LQFP                                                                               |

| Supplier Device Package    | 64-LFQFP (10x10)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r7fs124763a01cfm-aa1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## RENESAS

#### S124 Microcontroller Group

#### Datasheet

Ultra-low power 32-MHz Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ microcontroller, 128-KB code flash memory, 16-KB SRAM, Capacitive Touch Sensing Unit, 14-bit A/D Converter, 12-bit D/A Converter, security and safety features.

## Features

#### Arm Cortex-M0+ Core

- Armv6-M architecture

- Maximum operating frequency: 32 MHz

- Debug and Trace: DWT, BPU, CoreSight™ MTB-M0+

- CoreSight Debug Port: SW-DP

#### Memory

- 128-KB code flash memory

- 4-KB data flash memory (100,000 erase/write cycles)

- Up to 16-KB SRAM

- 128-bit unique ID

#### Connectivity

- USB 2.0 Full-Speed Module (USBFS)

- On-chip transceiver with voltage regulator

Compliant with USB Battery Charging Specification 1.2

- Serial Communications Interface (SCI) × 3

- UART

- Simple IIC

- Simple SPI

- Serial Peripheral Interface (SPI)  $\times 2$

- I<sup>2</sup>C bus interface (IIC)  $\times$  2

- CAN module (CAN)

#### Analog

- 14-Bit A/D Converter (ADC14)

- 12-Bit D/A Converter (DAC12)

- Low-Power Analog Comparator (ACMPLP) × 2

- Temperature Sensor (TSN)

#### Timers

- General PWM Timer 32-Bit (GPT32)

- General PWM Timer 16-Bit (GPT16)  $\times$  6

- Asynchronous General-Purpose Timer (AGT)  $\times\,2$

- Watchdog Timer (WDT)

#### Safety

- SRAM Parity Error Check

- Flash Area Protection

- ADC self-diagnosis function

- Clock Frequency Accuracy Measurement Circuit (CAC)

- Cyclic Redundancy Check (CRC) Calculator

- Data Operation Circuit (DOC)

- Port Output Enable for GPT (POEG)

- Independent Watchdog Timer (IWDT)

- GPIO Readback Level Detection

- Register Write Protection

- Main Oscillator Stop Detection

#### System and Power Management

- Low-power modes

- Realtime Clock (RTC)

- Event Link Controller (ELC)Data Transfer Controller (DTC)

- Key Interrupt Function (KINT)

- Power-on reset

- Low Voltage Detection with voltage settings

#### Security and Encryption

- AES128/256

- True Random Number Generator (TRNG)

- Human Machine Interface (HMI)

- Capacitive Touch Sensing Unit (CTSU)

- Capacitive Fouch Sensing Onit (

- Multiple Clock Sources

Main clock oscillator (MOSC)

- Main clock oscillator (MOSC)

(1 to 20 MHz when VCC = 2.4 to 5.5 V)

(1 to 8 MHz when VCC = 1.8 to 5.5 V)

(1 to 4 MHz when VCC = 1.6 to 5.5 V)

- Sub-clock oscillator (SOSC) (32.768 kHz)

- High-speed on-chip oscillator (HOCO)

- (24, 32, 48, 64 MHz when VCC = 2.4 to 5.5 V) (24, 32, 48 MHz when VCC = 1.8 to 5.5 V) (24, 32 MHz when VCC = 1.6 to 5.5 V)

- Middle-speed on-chip oscillator (MOCO) (8 MHz)

- Low-speed on-chip oscillator (LOCO) (32.768 kHz)

- Independent watchdog timer OCO (15 kHz)

- Clock trim function for HOCO/MOCO/LOCOClock out support

- General Purpose I/O Ports

- Up to 51 input/output pins - Up to 3 CMOS input

- Up to 48 CMOS input/output

- Up to 6 input/output 5 V tolerant

- Up to 16 pins high current (20 mA)

### Operating Voltage

#### VCC: 1.6 to 5.5 V

- Operating Temperature and Packages

- Ta =  $-40^{\circ}$ C to  $+85^{\circ}$ C

- 36-pin LGA (4 mm  $\times$  4 mm, 0.5 mm pitch)

- $Ta = -40^{\circ}C \text{ to } +105^{\circ}C$

- 64-pin LQFP (10 mm  $\times$  10 mm, 0.5 mm pitch)

- 48-pin LQFP (7 mm × 7 mm, 0.5 mm pitch)

- 64-pin QFN (8 mm × 8 mm, 0.4 mm pitch) - 48-pin QFN (7 mm × 7 mm, 0.5 mm pitch)

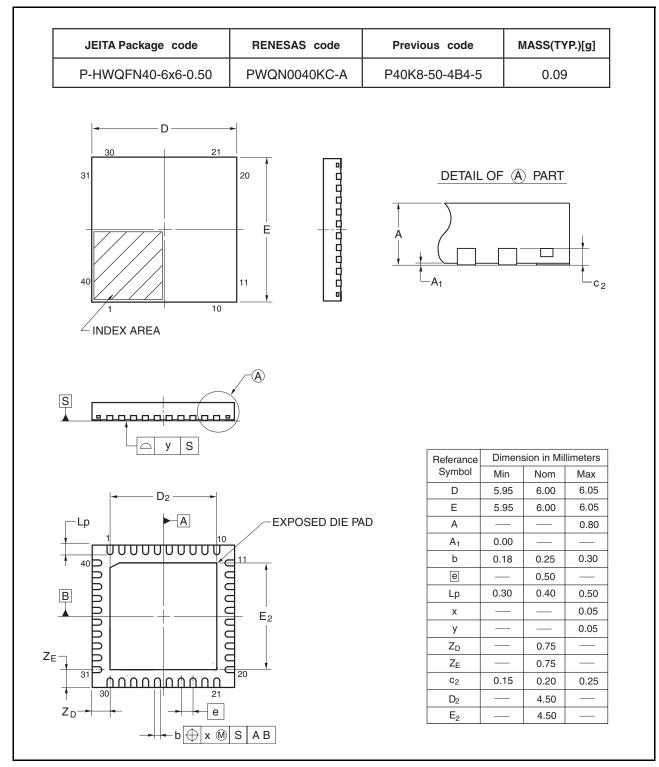

- 40-pin QFN (6 mm  $\times$  6 mm, 0.5 mm pitch)

## 1. Overview

The MCU integrates multiple series of software- and pin-compatible Arm<sup>®</sup>-based 32-bit MCUs that share a common set of Renesas peripherals to facilitate design scalability and efficient platform-based product development.

Based on the energy-efficient Arm Cortex<sup>®</sup>-M0+ core, the MCU is particularly well suited for cost-sensitive and low-power applications with the following features:

- 128-KB code flash memory

- 16-KB SRAM

- Capacitive Touch Sensing Unit (CTSU)

- 14-bit A/D Converter (ADC14)

- 12-bit D/A Converter (DAC12)

- Security features.

### 1.1 Function Outline

#### Table 1.1 Arm core

| Feature        | Functional description                                                                                                                                                                                                                                                                            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arm Cortex-M0+ | <ul> <li>Maximum operating frequency: up to 32 MHz</li> <li>Arm Cortex-M0+: <ul> <li>Revision: r0p1-00rel0</li> <li>Armv6-M architecture profile</li> <li>Single-cycle integer multiplier.</li> </ul> </li> <li>SysTick timer <ul> <li>Driven by SYSTICCLK (LOCO) or ICLK.</li> </ul> </li> </ul> |

| Feature               | Functional description                                                                                                          |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Code flash memory     | Maximum 128 KB code flash memory. See section 37, Flash Memory in User's Manual.                                                |

| Data flash memory     | 4 KB data flash memory. See section 37, Flash Memory in User's Manual.                                                          |

| Option-setting memory | The option-setting memory determines the state of the MCU after a reset. See section 6, Option-Setting Memory in User's Manual. |

| SRAM                  | On-chip high-speed SRAM with even parity bit. See section 36, SRAM in User's Manual.                                            |

#### Table 1.3 System (1 of 2)

| Feature                     | Functional description                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating mode              | Two operating modes:<br>• Single-chip mode<br>• SCI boot mode.<br>See section 3, Operating Modes in User's Manual.                                                                                                                                                                                                                                                          |

| Reset                       | <ul> <li>9 types of resets:</li> <li>RES pin reset</li> <li>Power-on reset</li> <li>Independent watchdog timer reset</li> <li>Watchdog timer reset</li> <li>Voltage monitor 0 reset</li> <li>Voltage monitor 1 reset</li> <li>Voltage monitor 2 reset</li> <li>SRAM parity error reset</li> <li>Software reset.</li> <li>See section 5, Resets in User's Manual.</li> </ul> |

| Low Voltage Detection (LVD) | The Low Voltage Detection (LVD) monitors the voltage level input to the VCC pin and the detection level can be selected using a software program. See section 7, Low Voltage Detection (LVD) in User's Manual.                                                                                                                                                              |

| Feature                                               | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock                                                 | <ul> <li>Main clock oscillator (MOSC)</li> <li>Sub-clock oscillator (SOSC)</li> <li>High-speed on-chip oscillator (HOCO)</li> <li>Middle-speed on-chip oscillator (MOCO)</li> <li>Low-speed on-chip oscillator (LOCO)</li> <li>Independent watchdog timer on-chip oscillator</li> <li>Clock out support.</li> <li>See section 8, Clock Generation Circuit in User's Manual.</li> </ul>                                                                                                                                                                                                                                                                                                     |

| Clock Frequency Accuracy<br>Measurement Circuit (CAC) | The Clock Frequency Accuracy Measurement Circuit (CAC) is used to check the system clock frequency with a reference clock signal by counting the number of pulses of the system clock to be measured. The reference clock can be provided externally through a CACREF pin or internally from various on-chip oscillators.<br>Event signals can be generated when the clock does not match or measurement ends. This feature is particularly useful in implementing a fail-safe mechanism for home and industrial automation applications.<br>See section 9, Clock Frequency Accuracy Measurement Circuit (CAC) in User's Manual.                                                           |

| Interrupt Controller Unit (ICU)                       | The Interrupt Controller Unit (ICU) controls which event signals are linked to the NVIC/DTC module and DMAC module. The ICU also controls NMI interrupts. See section 12, Interrupt Controller Unit (ICU) in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Key interrupt function (KINT)                         | A key interrupt can be generated by setting the Key Return Mode register (KRM) and inputting a rising or falling edge to the key interrupt input pins. See section 17, Key Interrupt Function (KINT) in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Low Power Mode                                        | Power consumption can be reduced in multiple ways, including setting clock dividers, stopping modules, selecting power control mode in normal operation, and transitioning to low power modes. See section 10, Low Power Modes in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Register Write Protection                             | The Register Write Protection function protects important registers from being overwritten due to software errors. See section 11, Register Write Protection in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Watchdog Timer (WDT)                                  | The Watchdog Timer (WDT) is a 14-bit down-counter. It can be used to reset the MCU when the counter underflows because the system has run out of control and is unable to refresh the WDT. In addition, a non-maskable interrupt or interrupt can be generated by an underflow. The refresh-permitted period can be set to refresh the counter and used as the condition to detect when the system runs out of control. See section 22, Watchdog Timer (WDT) in User's Manual.                                                                                                                                                                                                             |

| Independent Watchdog Timer (IWDT)                     | The Independent Watchdog Timer (IWDT) consists of a 14-bit down-counter that must be serviced periodically to prevent counter underflow. The IWDT provides functionality to reset the MCU or to generate a non-maskable interrupt/interrupt for a timer underflow. Because the timer operates with an independent, dedicated clock source, it is particularly useful in returning the MCU to a known state as a fail safe mechanism when the system runs out of control. The watchdog timer can be triggered automatically on reset, underflow, or refresh error, or by a refresh of the count value in the registers. See section 23, Independent Watchdog Timer (IWDT) in User's Manual. |

#### Table 1.4 Event Link

| Feature                     | Functional description                                                                                                                                                                                                                                                                             |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Event Link Controller (ELC) | The Event Link Controller (ELC) uses the interrupt requests generated by various peripheral modules as event signals to connect them to different modules, enabling direct interaction between the modules without CPU intervention. See section 15, Event Link Controller (ELC) in User's Manual. |

### Table 1.5 Direct memory access

| Feature                        | Functional description                                                                                                                                                                      |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Transfer Controller (DTC) | The MCU incorporates a Data Transfer Controller (DTC) that performs data transfers when activated by an interrupt request. See section 14, Data Transfer Controller (DTC) in User's Manual. |

| Feature                           | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB 2.0 Full-Speed Module (USBFS) | The MCU incorporates a USB 2.0 Full-Speed module (USBFS). The USBFS is a USB controller that is equipped to operate as a device controller. The module supports full-speed and low-speed transfer as defined in the Universal Serial Bus Specification 2.0. The module has an internal USB transceiver and supports all of the transfer types defined in the Universal Serial Bus Specification 2.0. The USB has buffer memory for data transfer, providing a maximum of 5 pipes. PIPE0 and PIPE4 to PIPE7 can be assigned any endpoint number based on the peripheral devices used for communication or based on the user system. The MCU supports revision 1.2 of the battery charging specification. Because the MCU can be powered at 5 V, the USB LDO regulator provides the internal USB transceiver power supply 3.3 V. See section 24, USB 2.0 Full-Speed Module (USBFS) in User's Manual. |

Table 1.7Communication interfaces (2 of 2)

#### Table 1.8 Analog

| Feature                                 | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14-bit A/D Converter (ADC14)            | The MCU incorporates up to one unit of a 14-bit successive approximation A/D converter. Up to 18 analog input channels are selectable. Temperature sensor output and internal reference voltage are selectable for conversion. The A/D conversion accuracy is selectable from 12-bit and 14-bit conversion making it possible to optimize the tradeoff between speed and resolution in generating a digital value. See section 30, 14-Bit A/D Converter (ADC14) in User's Manual.                                                                                                                 |

| 12-bit D/A Converter (DAC12)            | The MCU includes a 12-bit D/A converter with an output amplifier. See section 31, 12-Bit D/A Converter (DAC12) in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Temperature Sensor (TSN)                | The on-chip Temperature Sensor can be used to determine and monitor the die temperature for reliable operation of the device. The sensor outputs a voltage directly proportional to the die temperature, and the relationship between the die temperature and the output voltage is linear. The output voltage is provided to the ADC14 for conversion and can be further used by the end application. See section 32, Temperature Sensor (TSN) in User's Manual.                                                                                                                                 |

| Low-Power Analog Comparator<br>(ACMPLP) | Analog comparators can be used to compare a reference input voltage and analog input voltage. The comparison result can be read by software and also be output externally. The reference input voltage can be selected from either an input to the CMPREFi (i = 0, 1) pin or from the internal reference voltage (Vref) generated internally in the MCU. The ACMPLP response speed can be set before starting an operation. Setting high-speed mode decreases the response delay time, but increases current consumption. Sete section 33, Low-Power Analog Comparator (ACMPLP) in User's Manual. |

#### Table 1.9 Human machine interfaces

| Feature                                 | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Capacitive Touch Sensing Unit<br>(CTSU) | The Capacitive Touch Sensing Unit (CTSU) measures the electrostatic capacitance of the touch sensor. Changes in the electrostatic capacitance are determined by software, which enables the CTSU to detect whether a finger is in contact with the touch sensor. The electrode surface of the touch sensor is usually enclosed with an electrical insulator so that a finger does not come into direct contact with the electrode. See section 34, Capacitive Touch Sensing Unit (CTSU) in User's Manual. |

#### Table 1.10 Data processing

| Feature                                     | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cyclic Redundancy Check (CRC)<br>Calculator | The Cyclic Redundancy Check (CRC) calculator generates CRC codes to detect errors in the data. The bit order of CRC calculation results can be switched for LSB first or MSB first communication. Additionally, various CRC generation polynomials are available. The snoop function allows monitoring reads from and writes to specific addresses. This function is useful in applications that require CRC code to be generated automatically in certain events, such as monitoring writes to the serial transmit buffer and reads from the serial receive buffer. See section 29, Cyclic Redundancy Check (CRC) Calculator in User's Manual. |

| Data Operation Circuit (DOC)                | The Data Operation Circuit (DOC) is used to compare, add, and subtract 16-bit data. See section 35, Data Operation Circuit (DOC) in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### Table 1.12 Product list

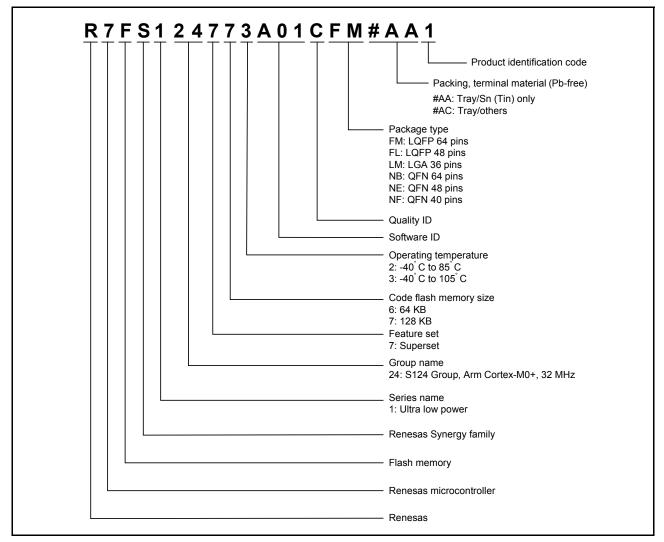

| Product part number | Orderable part number | Package code | Code flash | Data flash | SRAM  | Operating<br>temperature |

|---------------------|-----------------------|--------------|------------|------------|-------|--------------------------|

| R7FS124773A01CFM    | R7FS124773A01CFM#AA1  | PLQP0064KB-C | 128 KB     | 4 KB       | 16 KB | –40 to +105°C            |

| R7FS124773A01CNB    | R7FS124773A01CNB#AC1  | PWQN0064LA-A |            |            |       | -40 to +105°C            |

| R7FS124773A01CFL    | R7FS124773A01CFL#AA1  | PLQP0048KB-B | 1          |            |       | -40 to +105°C            |

| R7FS124773A01CNE    | R7FS124773A01CNE#AC1  | PWQN0048KB-A |            |            |       | -40 to +105°C            |

| R7FS124773A01CNF    | R7FS124773A01CNF#AC1  | PWQN0040KC-A |            |            |       | -40 to +105°C            |

| R7FS124772A01CLM    | R7FS124772A01CLM#AC1  | PWLG0036KA-A |            |            |       | -40 to +85°C             |

| R7FS124763A01CFM    | R7FS124763A01CFM#AA1  | PLQP0064KB-C | 64 KB      |            |       | -40 to +105°C            |

| R7FS124763A01CFL    | R7FS124763A01CFL#AA1  | PLQP0048KB-B | 1          |            |       | -40 to +105°C            |

| R7FS124762A01CLM    | R7FS124762A01CLM#AC1  | PWLG0036KA-A | 1          |            |       | -40 to +85°C             |

Note: Earlier products with orderable part number suffix AA0 and AC0 have a restriction in AES functions. If AES functions are required for your application, refer to the products with orderable part number suffix AA1 or AC1. For details on the differences of AES functions between AA0/AC0 and AA1/AC1 products, see *Technical Update* (*TN-SY\*-A024A/E*). Contact your Renesas sales representative for additional information.

RENESAS

## 1.5 Pin Functions

| Function               | Signal                                          | I/O    | Description                                                                                                                                                            |

|------------------------|-------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply           | VCC                                             | Input  | Power supply pin. Connect it to the system power supply. Connect this pin to VSS by a $0.1-\mu$ F capacitor. The capacitor should be placed close to the pin.          |

|                        | VCL                                             | Input  | Connect this pin to the VSS pin by the smoothing capacitor used to stabilize the internal power supply. Place the capacitor close to the pin.                          |

|                        | VSS                                             | Input  | Ground pin. Connect it to the system power supply (0 V).                                                                                                               |

| Clock                  | XTAL                                            | Output | Pins for a crystal resonator. An external clock signal can be input through                                                                                            |

|                        | EXTAL                                           | Input  | the EXTAL pin.                                                                                                                                                         |

|                        | XCIN                                            | Input  | Input/output pins for the sub-clock oscillator. Connect a crystal resonator                                                                                            |

|                        | XCOUT                                           | Output | between XCOUT and XCIN.                                                                                                                                                |

|                        | CLKOUT                                          | Output | Clock output pin.                                                                                                                                                      |

| Operating mode control | MD                                              | Input  | Pins for setting the operating mode. The signal levels on these pins must not be changed during operation mode transition at the time of release from the reset state. |

| System control         | RES                                             | Input  | Reset signal input pin. The MCU enters the reset state when this signal goes low.                                                                                      |

| CAC                    | CACREF                                          | Input  | Measurement reference clock input pin.                                                                                                                                 |

| On-chip debug          | SWDIO                                           | I/O    | Serial Wire debug Data Input/Output pin.                                                                                                                               |

|                        | SWCLK                                           | Input  | Serial Wire Clock pin.                                                                                                                                                 |

| Interrupt              | NMI                                             | Input  | Non-maskable interrupt request pin.                                                                                                                                    |

|                        | IRQ0 to IRQ7                                    | Input  | Maskable interrupt request pins.                                                                                                                                       |

| GPT                    | GTETRGA,<br>GTETRGB                             | Input  | External trigger input pin.                                                                                                                                            |

|                        | GTIOC0A to<br>GTIOC6A,<br>GTIOC0B to<br>GTIOC6B | I/O    | Input capture, Output Compare, or PWM output pin.                                                                                                                      |

|                        | GTIU                                            | Input  | Hall sensor input pin U.                                                                                                                                               |

|                        | GTIV                                            | Input  | Hall sensor input pin V.                                                                                                                                               |

|                        | GTIW                                            | Input  | Hall sensor input pin W.                                                                                                                                               |

|                        | GTOUUP                                          | Output | Three-phase PWM output for BLDC motor control (positive U phase).                                                                                                      |

|                        | GTOULO                                          | Output | Three-phase PWM output for BLDC motor control (negative U phase).                                                                                                      |

|                        | GTOVUP                                          | Output | Three-phase PWM output for BLDC motor control (positive V phase).                                                                                                      |

|                        | GTOVLO                                          | Output | Three-phase PWM output for BLDC motor control (negative V phase).                                                                                                      |

|                        | GTOWUP                                          | Output | Three-phase PWM output for BLDC motor control (positive W phase).                                                                                                      |

|                        | GTOWLO                                          | Output | Three-phase PWM output for BLDC motor control (negative W phase).                                                                                                      |

| AGT                    | AGTEE0,<br>AGTEE1                               | Input  | External event input enable.                                                                                                                                           |

|                        | AGTIO0, AGTIO1                                  | I/O    | External event input and pulse output.                                                                                                                                 |

|                        | AGTO0, AGTO1                                    | Output | Pulse output.                                                                                                                                                          |

|                        | AGTOA0,<br>AGTOA1                               | Output | Output compare match A output.                                                                                                                                         |

|                        | AGTOB0,<br>AGTOB1                               | Output | Output compare match B output.                                                                                                                                         |

| RTC                    | RTCOUT                                          | Output | Output pin for 1-Hz/64-Hz clock.                                                                                                                                       |

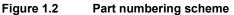

## 1.6 Pin Assignments

Figure 1.3 to Figure 1.8 show the pin assignments.

Figure 1.3 Pin assignment for LQFP 64-pin (top view)

|               |        | Pin numbe | r     |       |                                        |           |              | Tin           | ners          |     | C         | ommunicat                                                   | ion Interfa | ces          | Ana                    | logs          | н       | MI            |

|---------------|--------|-----------|-------|-------|----------------------------------------|-----------|--------------|---------------|---------------|-----|-----------|-------------------------------------------------------------|-------------|--------------|------------------------|---------------|---------|---------------|

| LQFP64, QFN64 | LQFP48 | QFN48     | QFN40 | LGA36 | Power, System,<br>Clock, Debug,<br>CAC | I/O ports | AGT          | GPT_OPS, POEG | GРТ           | RTC | USBFS,CAN | sci                                                         | S           | SPI          | ADC14                  | DAC12, ACMPLP | CTSU    | Interrupt     |

| 35            | 27     | 27        | 23    | D5    |                                        | P110      |              | GTOVLO<br>_A  | GTIOC1B<br>_A |     | CRX0_A    | CTS0_RT<br>S0_C/<br>SS0_C/<br>RXD9_B/<br>MISO9_B/<br>SCL9_B |             | MISOB_B      |                        | VCOUT         | TS11    | IRQ3          |

| 36            | 28     | 28        | 24    | D6    |                                        | P111      |              |               | GTIOC3A<br>_A |     |           | SCK0_C/<br>SCK9_B                                           |             | RSPCKB_<br>B |                        |               | TS12    | IRQ4          |

| 37            | 29     | 29        | 25    | C6    |                                        | P112      |              |               | GTIOC3B<br>_A |     |           | TXD0_C/<br>MOSI0_C/<br>SDA0_C                               |             |              |                        |               | TSCAP_C |               |

| 38            | -      | -         | -     | -     |                                        | P113      |              |               |               |     |           |                                                             |             |              |                        |               |         |               |

| 39            | 30     | 30        | -     | -     | VCC                                    |           |              |               |               |     |           |                                                             |             |              |                        |               |         |               |

| 40            | 31     | 31        | -     | -     | VSS                                    |           |              |               |               |     |           |                                                             |             |              |                        |               |         |               |

| 41            | -      | -         | -     | -     |                                        | P107      |              |               | GTIOC0A<br>_B |     |           |                                                             |             |              |                        |               |         | KR07          |

| 42            | -      | -         | -     | -     |                                        | P106      |              |               | GTIOC0B<br>_B |     |           |                                                             |             | SSLA3_A      |                        |               |         | KR06          |

| 43            | -      | -         | -     | -     |                                        | P105      |              | GTETRG<br>A_C |               |     |           |                                                             |             | SSLA2_A      |                        |               |         | KR05/<br>IRQ0 |

| 44            | 32     | 32        | 26    | -     |                                        | P104      |              | GTETRG<br>B_B |               |     |           | RXD0_C/<br>MISO0_C/<br>SCL0_C                               |             | SSLA1_A      |                        |               | TS13    | KR04/<br>IRQ1 |

| 45            | 33     | 33        | 27    | C3    |                                        | P103      |              | GTOWUP<br>_A  | _A            |     | CTX0_C    | S0_A/<br>SS0_A                                              |             | SSLA0_A      | AN019                  | CMPREF<br>1   | TS14    | KR03          |

| 46            | 34     | 34        | 28    | C4    |                                        | P102      | AGTO0        | GTOWLO<br>_A  | GTIOC2B<br>_A |     | CRX0_C    | SCK0_A                                                      |             | RSPCKA_<br>A | AN020/<br>ADTRG0_<br>A | CMPIN1        | TS15    | KR02          |

| 47            | 35     | 35        | 29    | C5    |                                        | P101      | AGTEE0       | GTETRG<br>B_A | GTIOC5A<br>_A |     |           | TXD0_A/<br>MOSI0_A/<br>SDA0_A/<br>CTS1_RT<br>S1_A/<br>SS1_A | SDA1_B      | MOSIA_A      | AN021                  | CMPREF<br>0   | TS16    | KR01/<br>IRQ1 |

| 48            | 36     | 36        | 30    | B6    |                                        | P100      | AGTIO0_<br>A | GTETRG<br>A_A | GTIOC5B<br>_A |     |           | RXD0_A/<br>MISO0_A/<br>SCL0_A/<br>SCK1_A                    | SCL1_B      | MISOA_A      | AN022                  | CMPIN0        | TS26    | KR00/<br>IRQ2 |

| 49            | 37     | 37        | -     | -     |                                        | P500      | AGTOA0       | GTIU_B        | GTIOC2A<br>_B |     |           |                                                             |             |              | AN016                  |               | TS27    |               |

| 50            | -      | -         | -     | -     |                                        | P501      | AGTOB0       | GTIV_B        | GTIOC2B<br>_B |     |           |                                                             |             |              | AN017                  |               |         |               |

| 51            | -      | -         | -     | -     |                                        | P502      |              | GTIW_B        |               |     |           |                                                             |             |              | AN018                  |               |         |               |

| 52            | 38     | 38        | 31    | A6    |                                        | P015      |              |               |               |     |           |                                                             |             |              | AN010                  |               | TS28    | IRQ7          |

| 53            | 39     | 39        | 32    | A5    |                                        | P014      |              |               |               |     |           |                                                             |             |              | AN009                  | DA0           |         |               |

| 54            | 40     | 40        | 33    | B5    |                                        | P013      |              |               |               |     |           |                                                             |             |              | AN008                  |               |         |               |

| 55            | 41     | 41        | 34    | B4    |                                        | P012      |              |               |               |     |           |                                                             |             | 1            | AN007                  |               |         |               |

| 56            | 42     | 42        | 35    | A4    | AVCC0                                  |           |              |               |               |     |           |                                                             |             | 1            | 1                      |               |         |               |

| 57            | 43     | 43        | 36    | A3    | AVSS0                                  |           |              |               |               |     |           |                                                             |             | 1            | 1                      |               |         |               |

| 58            | 44     | 44        | 37    | B3    | VREFL0                                 | P011      |              |               |               |     |           |                                                             |             | 1            | AN006                  |               | TS31    |               |

| 59            | 45     | 45        | 38    | A2    | VREFH0                                 | P010      |              |               |               |     |           |                                                             |             | 1            | AN005                  |               | TS30    |               |

| 60            | -      | -         | -     | -     |                                        | P004      |              |               |               |     |           |                                                             |             |              | AN004                  |               | TS25    | IRQ3          |

| 61            | -      | -         | -     | -     |                                        | P003      |              |               |               |     |           |                                                             |             |              | AN003                  |               | TS24    |               |

| 62            | 46     | 46        | -     | -     |                                        | P002      |              |               |               |     |           |                                                             |             |              | AN002                  |               | TS23    | IRQ2          |

| 63            | 47     | 47        | 39    | -     |                                        | P001      |              |               |               |     |           |                                                             |             |              | AN001                  |               | TS22    | IRQ7          |

| 64            | 48     | 48        | 40    | B2    |                                        | P000      |              |               |               |     |           |                                                             |             |              | AN000                  |               | TS21    | IRQ6          |

|               |        |           |       |       | 1                                      | 1         | 1            | 1             | 1             |     | 1         | 1                                                           |             |              |                        |               |         | L             |

Note: Several pin names have the added suffix of \_A, \_B, \_C, and \_D. The suffix can be ignored when assigning functionality.

## 2. Electrical Characteristics

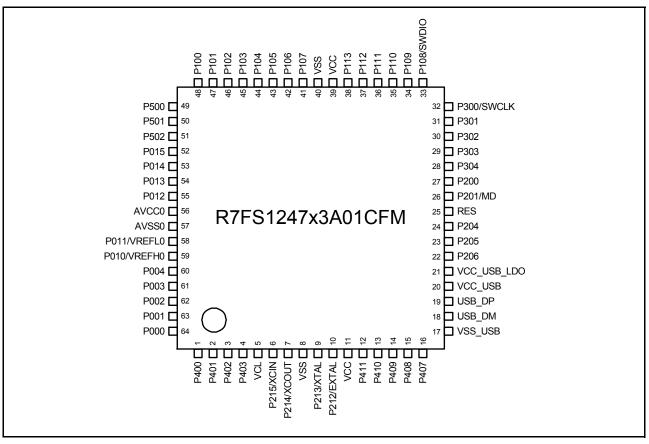

Unless otherwise specified, the electrical characteristics of the MCU are defined under the following conditions:

$VCC^{*1} = AVCC0 = VCC\_USB^{*2} = VCC\_USB\_LDO^{*2} = 1.6$  to 5.5V, VREFH0 = 1.6 to AVCC0,

$VSS = AVSS0 = VREFL0 = VSS\_USB = 0 V, Ta = T_{opr}$

Note 1. The typical condition is set to VCC = 3.3V.

Note 2. When USBFS is not used.

Figure 2.1 shows the timing conditions.

#### Figure 2.1 Input or output timing measurement conditions

The measurement conditions of timing specification in each peripherals are recommended for the best peripheral operation. However, make sure to adjust driving abilities of each pins to meet your conditions.

Each function pin used for the same function must select the same drive ability. If I/O drive ability of each function is mixed, the AC specification of the function is not guaranteed.

## 2.2 DC Characteristics

## 2.2.1 Tj/Ta Definition

#### Table 2.3DC characteristics

Conditions: Products with operating temperature  $(T_a)$  –40 to +105°C

| Parameter                        | Symbol | Тур | Max               | Unit | Test conditions                                         |

|----------------------------------|--------|-----|-------------------|------|---------------------------------------------------------|

| Permissible junction temperature | Tj     | -   | 125               | °C   | High-speed mode                                         |

|                                  |        |     | 105* <sup>1</sup> |      | Middle-speed mode<br>Low-voltage mode<br>Low-speed mode |

|                                  |        |     |                   |      | Subosc-speed mode                                       |

Note: Make sure that  $Tj = T_a + \theta ja \times total power consumption (W)$ , where total power consumption = (VCC - V<sub>OH</sub>) ×  $\Sigma I_{OH} + V_{OL} \times \Sigma I_{OL} + I_{CC}max \times VCC$ .

Note 1. The upper limit of operating temperature is 85°C or 105°C, depending on the product. For details, see section 1.3, Part Numbering. If the part number shows the operation temperature at 85°C, then the maximum value of Tj is 105°C, otherwise, it is 125°C.

2.2.2 I/O V<sub>IH</sub>, V<sub>IL</sub>

## Table 2.4 I/O V<sub>IH</sub>, V<sub>IL</sub> (1) Conditions: VCC = AVCC0 = 2.7 to 5.5 V

| Parameter                     |                                                           | Symbol          | Min         | Тур | Мах         | Unit | Test<br>Conditions    |  |  |

|-------------------------------|-----------------------------------------------------------|-----------------|-------------|-----|-------------|------|-----------------------|--|--|

| Schmitt trigger               | IIC (except for SMBus)*1                                  | V <sub>IH</sub> | VCC × 0.7   | -   | 5.8         | V    | -                     |  |  |

| input voltage                 |                                                           | V <sub>IL</sub> | -           | -   | VCC × 0.3   |      |                       |  |  |

|                               |                                                           | $\Delta V_T$    | VCC × 0.05  | -   | -           |      |                       |  |  |

|                               | RES, NMI                                                  | V <sub>IH</sub> | VCC × 0.8   | -   | -           |      |                       |  |  |

|                               | Other peripheral input pins                               | V <sub>IL</sub> | -           | -   | VCC × 0.2   |      |                       |  |  |

|                               | excluding IIC                                             | $\Delta V_T$    | VCC × 0.1   | -   | -           |      |                       |  |  |

| Input voltage<br>(except for  | IIC (SMBus)*2                                             | V <sub>IH</sub> | 2.2         | -   | -           | -    | VCC = 3.6 to<br>5.5 V |  |  |

| Schmitt trigger<br>input pin) |                                                           | V <sub>IH</sub> | 2.0         | -   | -           |      | VCC =2.7 to<br>3.6 V  |  |  |

|                               |                                                           | V <sub>IL</sub> | -           | -   | 0.8         |      | -                     |  |  |

|                               | 5V-tolerant ports*3                                       | V <sub>IH</sub> | VCC × 0.8   | -   | 5.8         | 1    |                       |  |  |

|                               |                                                           | V <sub>IL</sub> | -           | -   | VCC × 0.2   |      |                       |  |  |

|                               | P000 to P004                                              | V <sub>IH</sub> | AVCC0 × 0.8 | -   | -           |      |                       |  |  |

|                               | P010 to P015                                              | V <sub>IL</sub> | -           | -   | AVCC0 × 0.2 | 1    |                       |  |  |

|                               | EXTAL                                                     | V <sub>IH</sub> | VCC × 0.8   | -   | -           | 1    |                       |  |  |

|                               | Input ports pins except for<br>P000 to P004, P010 to P015 | V <sub>IL</sub> | -           | -   | VCC × 0.2   | 1    |                       |  |  |

Note 1. SCL0\_A, SDA0\_A, SDA0\_B, SCL1\_A, SDA1\_A (total 5 pins)

Note 2. SCL0\_A, SDA0\_A, SCL0\_B, SDA0\_B, SCL1\_A, SDA1\_A, SCL1\_B, SDA1\_B (total 8 pins)

Note 3. P205, P206, P400, P401, P407 (total 5pins)

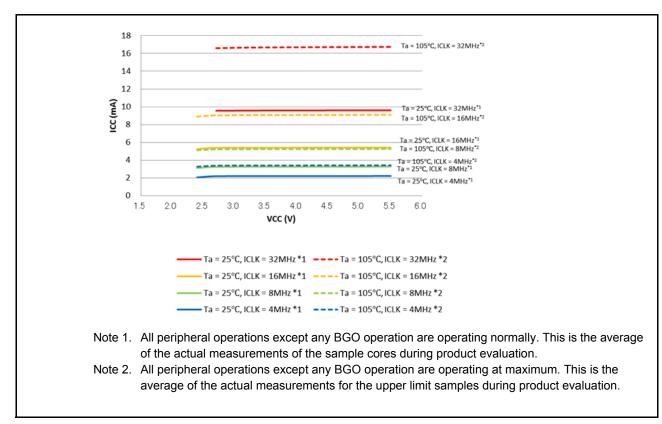

Figure 2.17 Voltage dependency in high-speed operating mode (reference data)

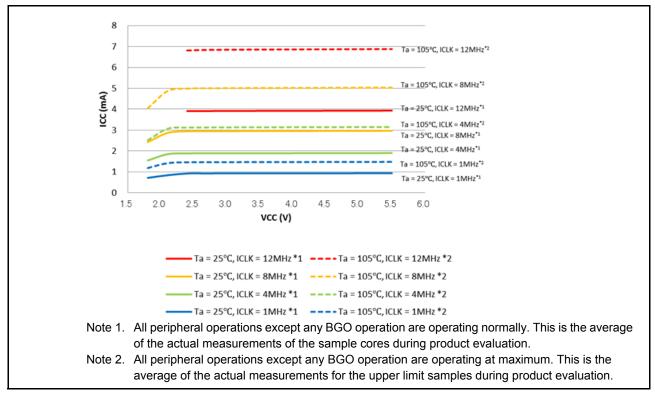

Figure 2.18 Voltage dependency in middle-speed operating mode (reference data)

RENESAS

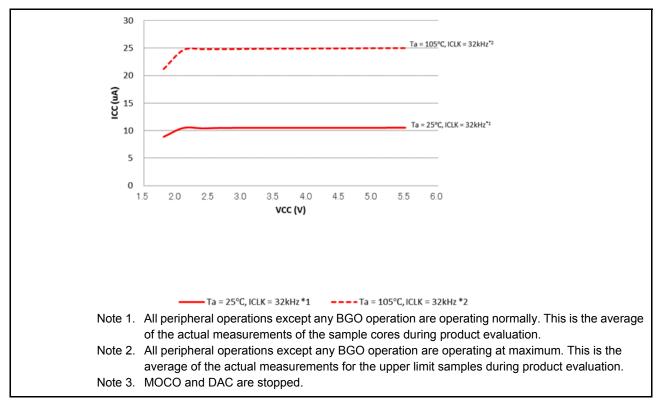

Figure 2.21 Voltage dependency in subosc-speed operating mode (reference data)

#### Table 2.12Operating and standby current (2)

Conditions: VCC = AVCC0 = 1.6 to 5.5 V

| Parameter              | Parameter                              |                                                      |                 | Typ* <sup>3</sup> | Max  | Unit | Test conditions                                |

|------------------------|----------------------------------------|------------------------------------------------------|-----------------|-------------------|------|------|------------------------------------------------|

| Supply Software Standb |                                        | T <sub>a</sub> = 25°C                                | I <sub>CC</sub> | 0.4               | 1.5  | μA   | -                                              |

| current*1              | mode*2                                 | T <sub>a</sub> = 55°C                                |                 | 0.6               | 5.5  |      |                                                |

|                        |                                        | T <sub>a</sub> = 85°C                                |                 | 1.2               | 10.0 |      |                                                |

|                        |                                        | T <sub>a</sub> = 105°C                               |                 | 2.6               | 40.0 |      |                                                |

|                        | Increment for RTC low-speed on-chip    | •                                                    |                 | 0.4               | -    |      | -                                              |

|                        | Increment for RTC sub-clock oscillator | rement for RTC operation with<br>-clock oscillator*4 |                 | 0.5               | -    |      | SOMCR.SODRV[1:0] are 11b<br>(Low power mode 3) |

|                        |                                        |                                                      |                 | 1.3               | -    | 1    | SOMCR.SODRV[1:0] are 00b<br>(normal mode)      |

Note 1. Supply current values do not include output charge/discharge current from all pins. The values apply when internal pull-up MOS transistors are in the off state.

Note 2. The IWDT and LVD are not operating.

Note 3. VCC = 3.3 V.

Note 4. Includes the current of low-speed on-chip oscillator or sub-oscillation circuit.

#### Table 2.18 Operation frequency in low-speed mode

Conditions: VCC = AVCC0 = 1.8 to 5.5 V

| Parameter |                                       |              |   | Min      | Тур | Max*5 | Unit |

|-----------|---------------------------------------|--------------|---|----------|-----|-------|------|

| Operation | System clock (ICLK)*1, *2, *4         | 1.8 to 5.5 V | f | 0.032768 | -   | 1     | MHz  |

| frequency | Peripheral module clock (PCLKB)*4     | 1.8 to 5.5 V |   | -        | -   | 1     |      |

|           | Peripheral module clock (PCLKD)*3, *4 | 1.8 to 5.5 V |   | -        | -   | 1     |      |

Note 1. The lower-limit frequency of ICLK is 1 MHz while programming or erasing the flash memory.

Note 2. The frequency accuracy of ICLK must be ±3.5% while programming or erasing the flash memory. Confirm the frequency accuracy of the clock source.

Note 3. The lower-limit frequency of PCLKD is 1 MHz when the A/D converter is in use.

- Note 4. See section 8, Clock Generation Circuit in User's Manual for the relationship of frequencies between ICLK, PCLKB, and PCLKD.

- Note 5. The maximum value of operation frequency does not include internal oscillator errors. For details on the range of guaranteed operation, see Table 2.21, Clock timing.

#### Table 2.19 Operation frequency in low-voltage mode

Conditions: VCC = AVCC0 = 1.6 to 5.5 V

| Parameter |                                       |              |   | Min      | Тур | Max*5 | Unit |

|-----------|---------------------------------------|--------------|---|----------|-----|-------|------|

| Operation | System clock (ICLK)*1, *2, *4         | 1.6 to 5.5 V | f | 0.032768 | -   | 4     | MHz  |

| frequency | Peripheral module clock (PCLKB)*4     | 1.6 to 5.5 V |   | -        | -   | 4     |      |

|           | Peripheral module clock (PCLKD)*3, *4 | 1.6 to 5.5 V | ] | -        | -   | 4     | 1    |

Note 1. The lower-limit frequency of ICLK is 1 MHz while programming or erasing the flash memory. When using ICLK for programming or erasing the flash memory at below 4 MHz, the frequency can be set to 1 MHz, 2 MHz, or 3 MHz. A non-integer frequency such as 1.5 MHz cannot be set.

- Note 2. The frequency accuracy of ICLK must be ±3.5% while programming or erasing the flash memory. Confirm the frequency accuracy of the clock source.

- Note 3. The lower-limit frequency of PCLKD is 4 MHz at 2.4 V or above and 1 MHz at below 2.4 V when the 14-bit A/D converter is in use.

- Note 4. See section 8, Clock Generation Circuit in User's Manual for the relationship of frequencies between ICLK, PCLKB, and PCLKD.

- Note 5. The maximum value of operation frequency does not include internal oscillator errors. For details on the range of guaranteed operation, see Table 2.21, Clock timing.

#### Table 2.20 Operation frequency in Subosc-speed mode

Conditions: VCC = AVCC0 = 1.8 to 5.5 V

| Parameter |                                       |              |   | Min     | Тур    | Max     | Unit |

|-----------|---------------------------------------|--------------|---|---------|--------|---------|------|

| Operation | System clock (ICLK)*1, *3             | 1.8 to 5.5 V | f | 27.8528 | 32.768 | 37.6832 | kHz  |

| frequency | Peripheral module clock (PCLKB)*3     | 1.8 to 5.5 V |   | -       | -      | 37.6832 |      |

|           | Peripheral module clock (PCLKD)*2, *3 | 1.8 to 5.5 V |   | -       | -      | 37.6832 |      |

Note 1. Programming and erasing the flash memory is not possible.

Note 2. The 14-bit A/D converter cannot be used.

Note 3. See section 8, Clock Generation Circuit in User's Manual for the relationship between ICLK, PCLKB, and PCLKD frequencies.

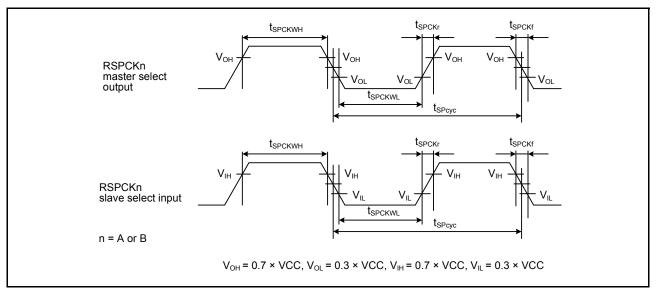

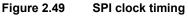

Figure 2.50 SPI timing (master, CPHA = 0) (bit rate: PCLKB division ratio is set to any value other than 1/2)

## Table 2.41A/D conversion characteristics (2) in high-speed A/D conversion mode (2 of 2)Conditions: VCC = AVCC0 = 2.7 to 5.5 V, VREFH0 = 2.7 to 5.5 V, VSS = AVSS0 = VREFL0 = 0V

Reference voltage range applied to the VREFH0 and VREFL0.

| Parameter                                                         |                                                         | Min  | Тур  | Max   | Unit | Test Conditions                                                       |

|-------------------------------------------------------------------|---------------------------------------------------------|------|------|-------|------|-----------------------------------------------------------------------|

| 14-bit mode                                                       |                                                         | •    |      |       |      |                                                                       |

| Resolution                                                        |                                                         | -    | -    | 14    | Bit  | -                                                                     |

| Conversion time <sup>*1</sup><br>(Operation at<br>PCLKD = 48 MHz) | Permissible signal<br>source impedance<br>Max. = 0.3 kΩ | 1.06 | -    | -     | μs   | High-precision channel<br>ADCSR.ADHSC = 0<br>ADSSTRn.SST[7:0] = 0Dh   |

|                                                                   |                                                         | 1.63 | -    | -     | μs   | Normal-precision channel<br>ADCSR.ADHSC = 0<br>ADSSTRn.SST[7:0] = 28h |

| Offset error                                                      |                                                         | -    | ±2.0 | ±18   | LSB  | High-precision channel                                                |

|                                                                   |                                                         |      |      | ±24.0 | LSB  | Other than above                                                      |

| Full-scale error                                                  |                                                         | -    | ±3.0 | ±18   | LSB  | High-precision channel                                                |

|                                                                   |                                                         |      |      | ±24.0 | LSB  | Other than above                                                      |

| Quantization error                                                |                                                         | -    | ±0.5 | -     | LSB  | -                                                                     |

| Absolute accuracy                                                 |                                                         | -    | ±5.0 | ±20   | LSB  | High-precision channel                                                |

|                                                                   |                                                         |      |      | ±32.0 | LSB  | Other than above                                                      |

| DNL differential nonline                                          | earity error                                            | -    | ±4.0 | -     | LSB  | -                                                                     |

| INL integral nonlinearit                                          | y error                                                 | -    | ±4.0 | ±12.0 | LSB  | -                                                                     |

Note: The characteristics apply when no pin functions other than 14-bit A/D converter input are used. Absolute accuracy does not include quantization errors. Offset error, full-scale error, DNL differential nonlinearity error, and INL integral nonlinearity error do not include quantization errors.

Note 1. The conversion time is the sum of the sampling time and the comparison time. The number of sampling states is indicated for the test conditions.

Note 2. Except for I/O input capacitance (Cin), see section 2.2.4, I/O VOH, VOL, and Other Characteristics.

Note 3. Reference data.

# Table 2.42 A/D conversion characteristics (3) in high-speed A/D conversion mode (1 of 2) Conditions: VCC = AVCC0 = 2.4 to 5.5 V, VREFH0 = 2.4 to 5.5 V, VSS = AVSS0 = VREFL0 = 0V Reference voltage range applied to the VREFH0 and VREFL0.

| Parameter                                                         |                                      |         | Min  | Тур   | Max               | Unit | Test Conditions                                                       |

|-------------------------------------------------------------------|--------------------------------------|---------|------|-------|-------------------|------|-----------------------------------------------------------------------|

| Frequency                                                         |                                      |         | 1    | -     | 32                | MHz  | -                                                                     |

| Analog input capacitan                                            | ce*2                                 | Cs      | -    | -     | 8* <sup>3</sup>   | pF   | High-precision channel                                                |

|                                                                   |                                      |         | -    | -     | 9*3               | pF   | Normal-precision channel                                              |

| Analog input resistance                                           | Э                                    | Rs      | -    | -     | 2.5* <sup>3</sup> | kΩ   | High-precision channel                                                |

|                                                                   |                                      |         | -    | -     | 6.7* <sup>3</sup> | kΩ   | Normal-precision channel                                              |

| Analog input voltage ra                                           | inge                                 | Ain     | 0    | -     | VREFH0            | V    | -                                                                     |

| 12-bit mode                                                       |                                      | •       | •    | •     | 1                 |      |                                                                       |

| Resolution                                                        |                                      |         | -    | -     | 12                | Bit  | -                                                                     |

| Conversion time <sup>*1</sup><br>(Operation at<br>PCLKD = 32 MHz) | Permissib<br>source im<br>Max. = 1.3 | pedance | 1.41 | -     | -                 | μs   | High-precision channel<br>ADCSR.ADHSC = 0<br>ADSSTRn.SST[7:0] = 0Dh   |

|                                                                   |                                      |         | 2.25 | -     | -                 | μs   | Normal-precision channel<br>ADCSR.ADHSC = 0<br>ADSSTRn.SST[7:0] = 28h |

| Offset error                                                      | •                                    |         | -    | ±0.5  | ±4.5              | LSB  | High-precision channel                                                |

|                                                                   |                                      |         |      |       | ±6.0              | LSB  | Other than above                                                      |

| Full-scale error                                                  |                                      |         | -    | ±0.75 | ±4.5              | LSB  | High-precision channel                                                |

|                                                                   |                                      |         |      |       | ±6.0              | LSB  | Other than above                                                      |

| Quantization error                                                |                                      |         | -    | ±0.5  | -                 | LSB  | -                                                                     |

| Absolute accuracy                                                 |                                      |         | -    | ±1.25 | ±5.0              | LSB  | High-precision channel                                                |

|                                                                   |                                      |         |      |       | ±8.0              | LSB  | Other than above                                                      |

#### Figure 2.62 Equivalent circuit for analog input

| Classification                                                      | Channel        | Conditions           | Remarks                                                            |  |  |

|---------------------------------------------------------------------|----------------|----------------------|--------------------------------------------------------------------|--|--|

| High-precision channel AN000 to AN010                               |                | AVCC0 = 1.6 to 5.5 V | Pins AN000 to AN010 cannot be used                                 |  |  |

| Normal-precision channel                                            | AN016 to AN022 |                      | as general I/O, TS transmission, when the A/D converter is in use. |  |  |

| Internal reference voltage Internal reference voltage input channel |                | AVCC0 = 2.0 to 5.5 V | -                                                                  |  |  |

| Temperature sensor input channel Temperature sensor output          |                | AVCC0 = 2.0 to 5.5 V | -                                                                  |  |  |

#### Table 2.48 A/D internal reference voltage characteristics

Conditions: VCC = AVCC0 = VREFH0 = 2.0 to 5.5 V\*1

| Parameter                                                 | Min  | Тур  | Max  | Unit | Test conditions |

|-----------------------------------------------------------|------|------|------|------|-----------------|

| Internal reference voltage input<br>channel* <sup>2</sup> | 1.36 | 1.43 | 1.50 | V    | -               |

| Frequency                                                 | 1    | -    | 2    | MHz  | -               |

| Sampling time                                             | 5.0  | -    | -    | μs   | -               |

Note 1. The internal reference voltage cannot be selected for input channels when AVCC0 < 2.0 V.

Note 2. The 14-bit A/D internal reference voltage indicates the voltage when the internal reference voltage is input to the 14-bit A/D converter.

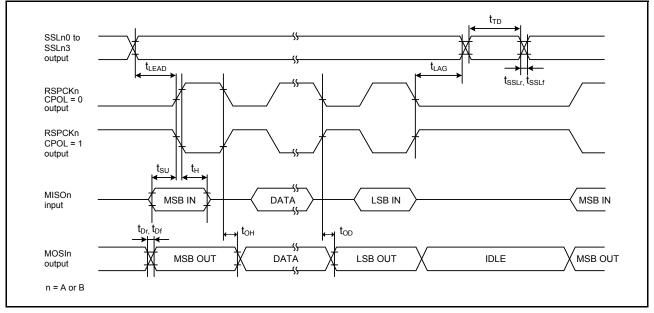

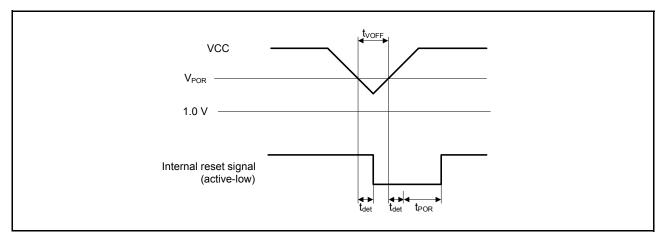

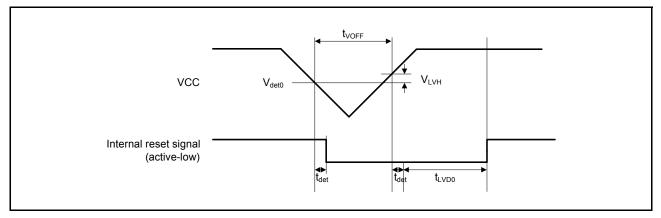

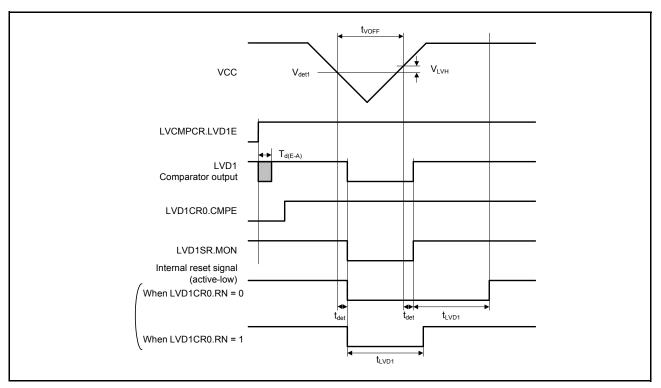

| Parameter                                               | Symbol               | Min | Тур | Max | Unit | Test Conditions                                      |

|---------------------------------------------------------|----------------------|-----|-----|-----|------|------------------------------------------------------|

| Power-on reset enable time                              | t <sub>W (POR)</sub> | 1   | -   | -   | ms   | Figure 2.67,<br>VCC = below 1.0 V                    |

| LVD operation stabilization time (after LVD is enabled) | T <sub>d (E-A)</sub> | -   | -   | 300 | μs   | Figure 2.69,<br>Figure 2.70                          |

| Hysteresis width (POR)                                  | V <sub>PORH</sub>    | -   | 110 | -   | mV   | -                                                    |

| Hysteresis width (LVD0, LVD1, and LVD2)                 | V <sub>LVH</sub>     | -   | 60  | -   | mV   | LVD0 selected                                        |

|                                                         |                      | -   | 100 | -   |      | $V_{det1_0}$ to $V_{det1_2}$ selected.               |

|                                                         |                      | -   | 60  | -   |      | V <sub>det1_3</sub> to V <sub>det1_9</sub> selected. |