# E:>< Filenesas Electronics America Inc - <u>R7FS124773A01CNB#AC0 Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                              |

|----------------------------|---------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                    |

| Speed                      | 32MHz                                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI, UART/USART, USB                                   |

| Peripherals                | LVD, POR, PWM, WDT                                                                    |

| Number of I/O              | 51                                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | 4K x 8                                                                                |

| RAM Size                   | 16K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 5.5V                                                                           |

| Data Converters            | A/D 18x14b; D/A 1x12b                                                                 |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 64-WFQFN Exposed Pad                                                                  |

| Supplier Device Package    | 64-HWQFN (8x8)                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r7fs124773a01cnb-ac0 |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

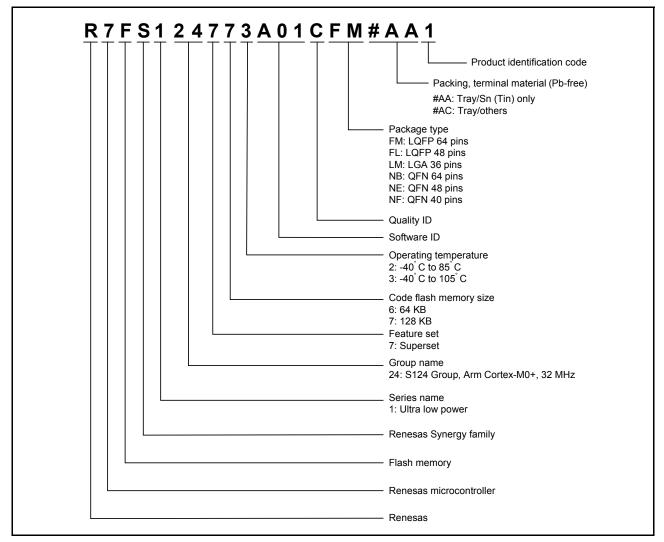

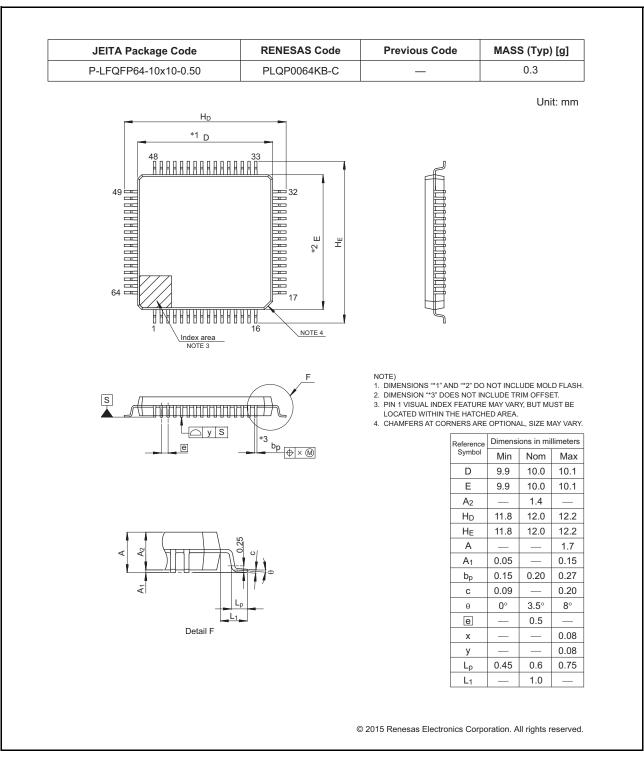

#### Table 1.12 Product list

| Product part number | Orderable part number | Package code | Code flash | Data flash | SRAM  | Operating<br>temperature |

|---------------------|-----------------------|--------------|------------|------------|-------|--------------------------|

| R7FS124773A01CFM    | R7FS124773A01CFM#AA1  | PLQP0064KB-C | 128 KB     | 4 KB       | 16 KB | –40 to +105°C            |

| R7FS124773A01CNB    | R7FS124773A01CNB#AC1  | PWQN0064LA-A |            |            |       | -40 to +105°C            |

| R7FS124773A01CFL    | R7FS124773A01CFL#AA1  | PLQP0048KB-B | 1          |            |       | -40 to +105°C            |

| R7FS124773A01CNE    | R7FS124773A01CNE#AC1  | PWQN0048KB-A |            |            |       | -40 to +105°C            |

| R7FS124773A01CNF    | R7FS124773A01CNF#AC1  | PWQN0040KC-A |            |            |       | -40 to +105°C            |

| R7FS124772A01CLM    | R7FS124772A01CLM#AC1  | PWLG0036KA-A |            |            |       | -40 to +85°C             |

| R7FS124763A01CFM    | R7FS124763A01CFM#AA1  | PLQP0064KB-C | 64 KB      |            |       | -40 to +105°C            |

| R7FS124763A01CFL    | R7FS124763A01CFL#AA1  | PLQP0048KB-B | 1          |            |       | -40 to +105°C            |

| R7FS124762A01CLM    | R7FS124762A01CLM#AC1  | PWLG0036KA-A | 1          |            |       | -40 to +85°C             |

Note: Earlier products with orderable part number suffix AA0 and AC0 have a restriction in AES functions. If AES functions are required for your application, refer to the products with orderable part number suffix AA1 or AC1. For details on the differences of AES functions between AA0/AC0 and AA1/AC1 products, see *Technical Update* (*TN-SY\*-A024A/E*). Contact your Renesas sales representative for additional information.

RENESAS

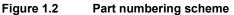

Figure 1.4 Pin assignment for QFN 64-pin (top view)

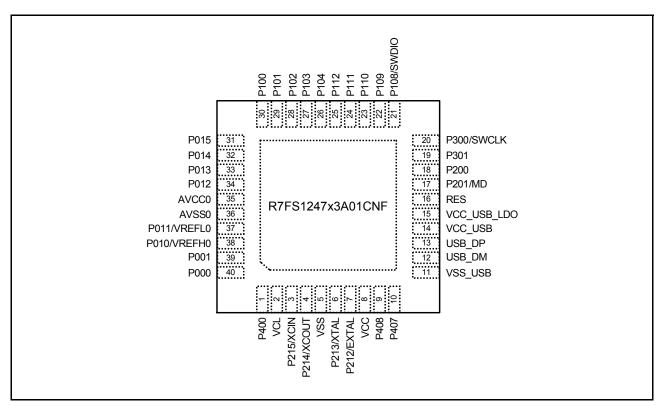

Figure 1.7 Pin assignment for QFN 40-pin (top view)

| R7FS1247x2A01CLM |                   |                 |                |                |                |                 |  |  |  |

|------------------|-------------------|-----------------|----------------|----------------|----------------|-----------------|--|--|--|

|                  | A                 | В               | c              | D              | E              | F               |  |  |  |

|                  | 6 P015            | P100            | P112           | P111           | P108<br>/SWDIO | P300<br>/SWCLK  |  |  |  |

|                  | 5 P014            | P013            | P101           | P110           | P200           | VCC_USB<br>_LDO |  |  |  |

|                  | 4 AVCC0           | P012            | P102           | P109           | P201/MD        | VCC_USB         |  |  |  |

|                  | 3 AVSS0           | P011<br>/VREFL0 | P103           | P213<br>/XTAL  | RES            | USB_DP          |  |  |  |

|                  | 2 P010<br>/VREFH0 | P000            | P400           | P212<br>/EXTAL | P407           | USB_DM          |  |  |  |

|                  | 1 VCL             | P215<br>/XCIN   | P214<br>/XCOUT | VSS            | VCC            | VSS_USB         |  |  |  |

|                  | A                 | В               | С              | D              | E              | F               |  |  |  |

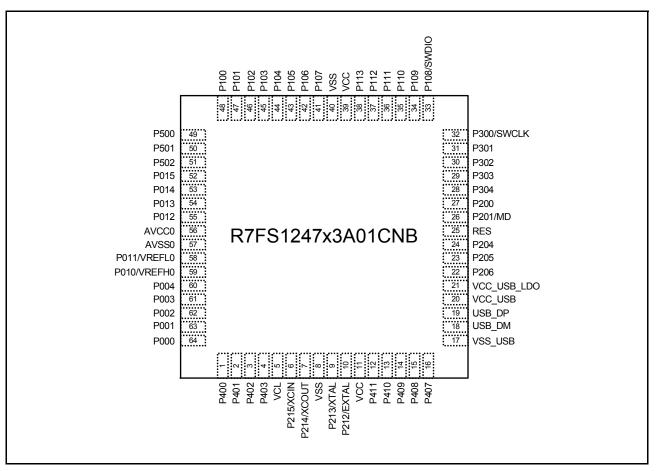

Figure 1.8

Pin assignment for LGA 36-pin (top view, pad side down)

### 2.2 DC Characteristics

### 2.2.1 Tj/Ta Definition

#### Table 2.3DC characteristics

Conditions: Products with operating temperature  $(T_a)$  –40 to +105°C

| Parameter                        | Symbol | Тур | Max               | Unit | Test conditions                                         |

|----------------------------------|--------|-----|-------------------|------|---------------------------------------------------------|

| Permissible junction temperature | Tj     | -   | 125               | °C   | High-speed mode                                         |

|                                  |        |     | 105* <sup>1</sup> |      | Middle-speed mode<br>Low-voltage mode<br>Low-speed mode |

|                                  |        |     |                   |      | Subosc-speed mode                                       |

Note: Make sure that  $Tj = T_a + \theta ja \times total power consumption (W)$ , where total power consumption = (VCC - V<sub>OH</sub>) ×  $\Sigma I_{OH} + V_{OL} \times \Sigma I_{OL} + I_{CC}max \times VCC$ .

Note 1. The upper limit of operating temperature is 85°C or 105°C, depending on the product. For details, see section 1.3, Part Numbering. If the part number shows the operation temperature at 85°C, then the maximum value of Tj is 105°C, otherwise, it is 125°C.

2.2.2 I/O V<sub>IH</sub>, V<sub>IL</sub>

## Table 2.4 I/O V<sub>IH</sub>, V<sub>IL</sub> (1) Conditions: VCC = AVCC0 = 2.7 to 5.5 V

| Parameter                     |                                                           | Symbol          | Min         | Тур | Мах         | Unit | Test<br>Conditions    |

|-------------------------------|-----------------------------------------------------------|-----------------|-------------|-----|-------------|------|-----------------------|

| Schmitt trigger               | IIC (except for SMBus)*1                                  | V <sub>IH</sub> | VCC × 0.7   | -   | 5.8         | V    | -                     |

| input voltage                 |                                                           | V <sub>IL</sub> | -           | -   | VCC × 0.3   |      |                       |

|                               |                                                           | $\Delta V_T$    | VCC × 0.05  | -   | -           |      |                       |

|                               | RES, NMI                                                  | V <sub>IH</sub> | VCC × 0.8   | -   | -           |      |                       |

|                               | Other peripheral input pins<br>excluding IIC              | V <sub>IL</sub> | -           | -   | VCC × 0.2   |      |                       |

|                               |                                                           | $\Delta V_T$    | VCC × 0.1   | -   | -           |      |                       |

| Input voltage<br>(except for  | IIC (SMBus)*2                                             | V <sub>IH</sub> | 2.2         | -   | -           | -    | VCC = 3.6 to<br>5.5 V |

| Schmitt trigger<br>input pin) |                                                           | V <sub>IH</sub> | 2.0         | -   | -           |      | VCC =2.7 to<br>3.6 V  |

|                               |                                                           | V <sub>IL</sub> | -           | -   | 0.8         |      | -                     |

|                               | 5V-tolerant ports*3                                       | V <sub>IH</sub> | VCC × 0.8   | -   | 5.8         |      |                       |

|                               |                                                           | V <sub>IL</sub> | -           | -   | VCC × 0.2   |      |                       |

|                               | P000 to P004                                              | V <sub>IH</sub> | AVCC0 × 0.8 | -   | -           |      |                       |

|                               | P010 to P015                                              | V <sub>IL</sub> | -           | -   | AVCC0 × 0.2 | -    |                       |

|                               | EXTAL                                                     | V <sub>IH</sub> | VCC × 0.8   | -   | -           |      |                       |

|                               | Input ports pins except for<br>P000 to P004, P010 to P015 | V <sub>IL</sub> | -           | -   | VCC × 0.2   | 1    |                       |

Note 1. SCL0\_A, SDA0\_A, SDA0\_B, SCL1\_A, SDA1\_A (total 5 pins)

Note 2. SCL0\_A, SDA0\_A, SCL0\_B, SDA0\_B, SCL1\_A, SDA1\_A, SCL1\_B, SDA1\_B (total 8 pins)

Note 3. P205, P206, P400, P401, P407 (total 5pins)

## Table 2.9 I/O V<sub>OH</sub>, V<sub>OL</sub> (3)

| Conditions: VCC = AVC | CO = | 1.6 to 2.7 V |

|-----------------------|------|--------------|

| Parameter      |                                    |                | Symbol          | Min            | Тур | Max | Unit | Test conditions           |

|----------------|------------------------------------|----------------|-----------------|----------------|-----|-----|------|---------------------------|

| Output voltage | Ports P000 to P004<br>P010 to P015 | Low drive      | V <sub>OH</sub> | AVCC0 –<br>0.3 | -   | -   |      | I <sub>OH</sub> = -0.5 mA |

|                |                                    |                | V <sub>OL</sub> | -              | -   | 0.3 |      | I <sub>OL</sub> = 0.5 mA  |

|                |                                    | Middle drive   | V <sub>OH</sub> | AVCC0 –<br>0.3 | -   | -   |      | I <sub>OH</sub> = -1.0 mA |

|                |                                    |                | V <sub>OL</sub> | -              | -   | 0.3 |      | I <sub>OL</sub> = 1.0 mA  |

|                | Other output pins*1                | Low drive      | V <sub>OH</sub> | VCC - 0.3      | -   | -   | V    | I <sub>OH</sub> = -0.5 mA |

|                |                                    |                | V <sub>OL</sub> | -              | -   | 0.3 |      | I <sub>OL</sub> = 0.5 mA  |

|                |                                    | Middle drive*2 | V <sub>OH</sub> | VCC - 0.3      | -   | -   |      | I <sub>OH</sub> = -1.0 mA |

|                |                                    |                | V <sub>OL</sub> | -              | -   | 0.3 |      | I <sub>OL</sub> = 1.0 mA  |

Note 1. Except for Ports P200, P214, P215, which are input ports.

Note 2. Except for P212, P213.

#### Table 2.10I/O other characteristics

Conditions: VCC = AVCC0 = 1.6 to 5.5 V

| Parameter                               |                                            | Symbol           | Min | Тур | Max | Unit | Test conditions                                  |  |

|-----------------------------------------|--------------------------------------------|------------------|-----|-----|-----|------|--------------------------------------------------|--|

| Input leakage current                   | RES, Ports P200, P214, P215                | I <sub>in</sub>  | -   | -   | 1.0 | μA   | V <sub>in</sub> = 0 V<br>V <sub>in</sub> = VCC   |  |

| Three-state leakage current (off state) | 5V-tolerant ports                          | I <sub>TSI</sub> | -   | -   | 1.0 | μA   | V <sub>in</sub> = 0 V<br>V <sub>in</sub> = 5.8 V |  |

|                                         | Other ports                                |                  | -   | -   | 1.0 |      | V <sub>in</sub> = 0 V<br>V <sub>in</sub> = VCC   |  |

| Input pull-up resistor                  | All ports<br>(except for P200, P214, P215) | R <sub>U</sub>   | 10  | 20  | 50  | kΩ   | V <sub>in</sub> = 0 V                            |  |

| Input capacitance                       | USB_DP, USB_DM, P200                       | C <sub>in</sub>  | -   | -   | 30  | pF   | V <sub>in</sub> = 0 V                            |  |

|                                         | Other input pins                           |                  | -   | -   | 15  | ]    | f = 1 MHz<br>T <sub>a</sub> = 25°C               |  |

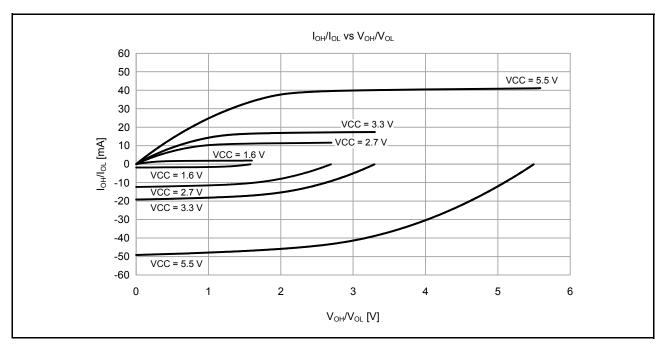

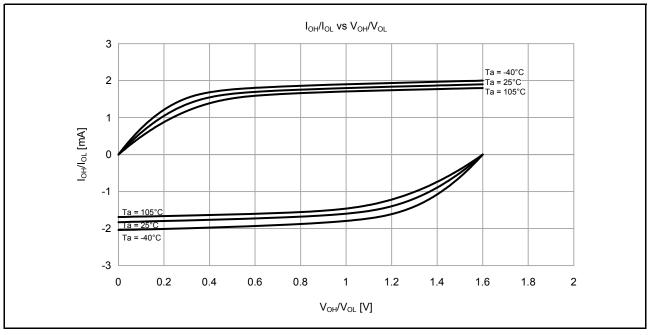

## 2.2.5 I/O Pin Output Characteristics of Low Drive Capacity

Figure 2.2 V<sub>OH</sub>/V<sub>OL</sub> and I<sub>OH</sub>/I<sub>OL</sub> voltage characteristics at Ta = 25°C when low drive output is selected (reference data)

Figure 2.3 V<sub>OH</sub>/V<sub>OL</sub> and I<sub>OH</sub>/I<sub>OL</sub> temperature characteristics at VCC = 1.6 V when low drive output is selected (reference data)

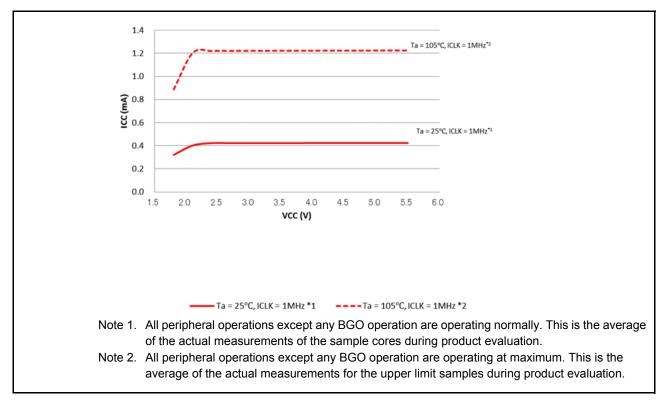

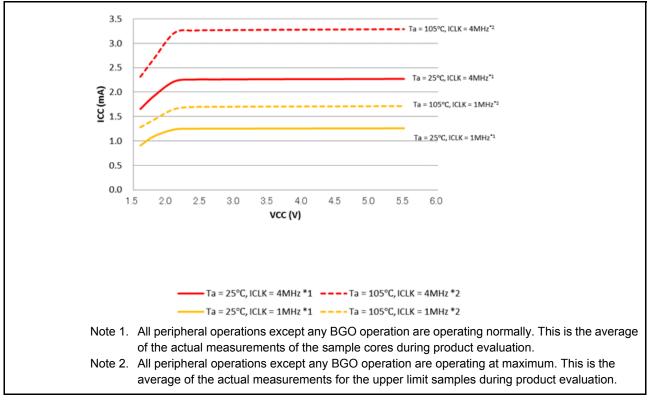

Figure 2.19 Voltage dependency in low-speed operating mode (reference data)

RENESAS

#### Table 2.18 Operation frequency in low-speed mode

Conditions: VCC = AVCC0 = 1.8 to 5.5 V

| Parameter |                                       |              |   | Min      | Тур | Max*5 | Unit |

|-----------|---------------------------------------|--------------|---|----------|-----|-------|------|

| Operation | System clock (ICLK)*1, *2, *4         | 1.8 to 5.5 V | f | 0.032768 | -   | 1     | MHz  |

| frequency | Peripheral module clock (PCLKB)*4     | 1.8 to 5.5 V |   | -        | -   | 1     |      |

|           | Peripheral module clock (PCLKD)*3, *4 | 1.8 to 5.5 V |   | -        | -   | 1     |      |

Note 1. The lower-limit frequency of ICLK is 1 MHz while programming or erasing the flash memory.

Note 2. The frequency accuracy of ICLK must be ±3.5% while programming or erasing the flash memory. Confirm the frequency accuracy of the clock source.

Note 3. The lower-limit frequency of PCLKD is 1 MHz when the A/D converter is in use.

- Note 4. See section 8, Clock Generation Circuit in User's Manual for the relationship of frequencies between ICLK, PCLKB, and PCLKD.

- Note 5. The maximum value of operation frequency does not include internal oscillator errors. For details on the range of guaranteed operation, see Table 2.21, Clock timing.

#### Table 2.19 Operation frequency in low-voltage mode

Conditions: VCC = AVCC0 = 1.6 to 5.5 V

| Parameter |                                       |              | Symbol | Min      | Тур | Max*5 | Unit |

|-----------|---------------------------------------|--------------|--------|----------|-----|-------|------|

| Operation | System clock (ICLK)*1, *2, *4         | 1.6 to 5.5 V | f      | 0.032768 | -   | 4     | MHz  |

| frequency | Peripheral module clock (PCLKB)*4     | 1.6 to 5.5 V |        | -        | -   | 4     |      |

|           | Peripheral module clock (PCLKD)*3, *4 | 1.6 to 5.5 V |        | -        | -   | 4     |      |

Note 1. The lower-limit frequency of ICLK is 1 MHz while programming or erasing the flash memory. When using ICLK for programming or erasing the flash memory at below 4 MHz, the frequency can be set to 1 MHz, 2 MHz, or 3 MHz. A non-integer frequency such as 1.5 MHz cannot be set.

- Note 2. The frequency accuracy of ICLK must be ±3.5% while programming or erasing the flash memory. Confirm the frequency accuracy of the clock source.

- Note 3. The lower-limit frequency of PCLKD is 4 MHz at 2.4 V or above and 1 MHz at below 2.4 V when the 14-bit A/D converter is in use.

- Note 4. See section 8, Clock Generation Circuit in User's Manual for the relationship of frequencies between ICLK, PCLKB, and PCLKD.

- Note 5. The maximum value of operation frequency does not include internal oscillator errors. For details on the range of guaranteed operation, see Table 2.21, Clock timing.

#### Table 2.20 Operation frequency in Subosc-speed mode

Conditions: VCC = AVCC0 = 1.8 to 5.5 V

| Parameter              |                                       |              | Symbol | Min     | Тур    | Max     | Unit |

|------------------------|---------------------------------------|--------------|--------|---------|--------|---------|------|

| Operation<br>frequency | System clock (ICLK)*1, *3             | 1.8 to 5.5 V | f      | 27.8528 | 32.768 | 37.6832 | kHz  |

|                        | Peripheral module clock (PCLKB)*3     | 1.8 to 5.5 V |        | -       | -      | 37.6832 |      |

|                        | Peripheral module clock (PCLKD)*2, *3 | 1.8 to 5.5 V |        | -       | -      | 37.6832 |      |

Note 1. Programming and erasing the flash memory is not possible.

Note 2. The 14-bit A/D converter cannot be used.

Note 3. See section 8, Clock Generation Circuit in User's Manual for the relationship between ICLK, PCLKB, and PCLKD frequencies.

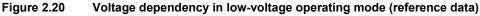

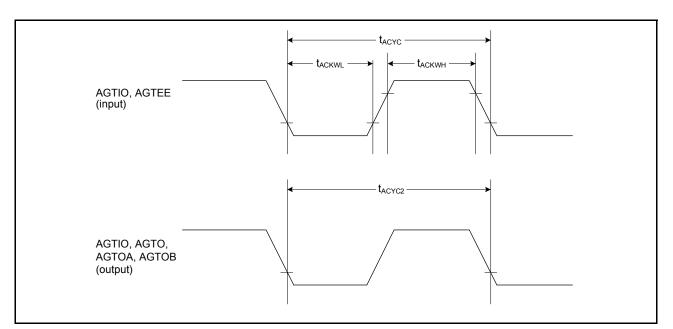

#### Figure 2.38 AGT I/O timing

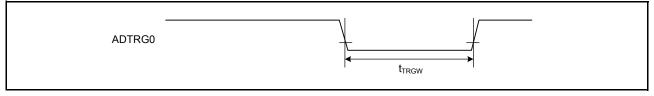

#### Figure 2.39 ADC14 trigger input timing

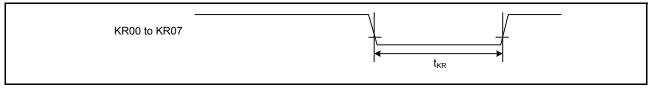

#### Figure 2.40 Key interrupt input timing

2.3.7 CAC Timing

#### Table 2.31CAC timing

| Paramete | Parameter                |                                         |                     | Min                                       | Тур | Max | Unit | Test<br>conditions |

|----------|--------------------------|-----------------------------------------|---------------------|-------------------------------------------|-----|-----|------|--------------------|

| CAC      | CACREF input pulse width | t <sub>PBcyc</sub> ≤ tcac*²             | t <sub>CACREF</sub> | $4.5 \times t_{cac} + 3 \times t_{PBcyc}$ | -   | -   | ns   | -                  |

|          |                          | t <sub>PBcyc</sub> > tcac* <sup>2</sup> |                     | $5 \times t_{cac} + 6.5 \times t_{PBcyc}$ | -   | -   | ns   |                    |

Note 1. t<sub>PBcyc</sub>: PCLKB cycle.

Note 2.  $t_{cac}\!\!:$  CAC count clock source cycle.

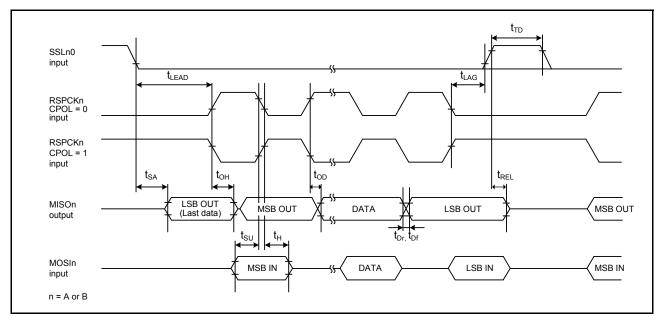

#### 2.3.8 SCI Timing

## Table 2.32SCI timing (1)Conditions: VCC = AVCC0 = 1.6 to 5.5 V

-

| Paran | Parameter                       |                 |                   | Symbol            | Min | Max | Unit <sup>*1</sup> | Test conditions |

|-------|---------------------------------|-----------------|-------------------|-------------------|-----|-----|--------------------|-----------------|

| SCI   | Input clock cycle               | Asynchro        | nous              | t <sub>Scyc</sub> | 4   | -   | t <sub>Pcyc</sub>  | Figure 2.41     |

|       |                                 | Clock syn       | chronous          |                   | 6   | -   |                    |                 |

|       | Input clock pulse wid           | lth             |                   | t <sub>SCKW</sub> | 0.4 | 0.6 | t <sub>Scyc</sub>  | -               |

|       | Input clock rise time           |                 |                   | t <sub>SCKr</sub> | -   | 20  | ns                 | -               |

|       | Input clock fall time           |                 |                   | t <sub>SCKf</sub> | -   | 20  | ns                 |                 |

|       | Output clock cycle              | Asynchro        | nous              | t <sub>Scyc</sub> | 6   | -   | t <sub>Pcyc</sub>  |                 |

|       |                                 | Clock syn       | Clock synchronous |                   | 4   | -   |                    |                 |

|       | Output clock pulse w            | ridth           |                   | t <sub>SCKW</sub> | 0.4 | 0.6 | t <sub>Scyc</sub>  |                 |

|       | Output clock rise time          | е               | 1.8V or above     | t <sub>SCKr</sub> | -   | 20  | ns                 |                 |

|       |                                 |                 | 1.6V or above     |                   | -   | 30  |                    |                 |

|       | Output clock fall time          | ;               | 1.8V or above     | t <sub>SCKf</sub> | -   | 20  | ns                 |                 |

|       |                                 |                 | 1.6V or above     |                   | -   | 30  |                    |                 |

|       |                                 | Clock           | 1.8V or above     | t <sub>TXD</sub>  | -   | 40  | ns                 | Figure 2.42     |

|       | (master)                        | synchro<br>nous | 1.6V or above     |                   | -   | 45  |                    | -               |

|       | Transmit data delay             | Clock           | 2.7V or above     | -                 | -   | 55  | ns                 |                 |

|       | (slave)                         | synchro<br>nous | 2.4V or above     |                   | -   | 60  |                    |                 |

|       |                                 |                 | 1.8V or above     |                   | -   | 100 |                    |                 |

|       |                                 |                 | 1.6V or above     |                   | -   | 125 |                    |                 |

|       | Receive data setup              | Clock           | 2.7V or above     | t <sub>RXS</sub>  | 45  | -   | ns                 | -               |

|       | time (master)                   | synchro<br>nous | 2.4V or above     |                   | 55  | -   |                    |                 |

|       |                                 | 11000           | 1.8V or above     |                   | 90  | -   |                    |                 |

|       |                                 |                 | 1.6V or above     |                   | 110 | -   |                    |                 |

|       | Receive data setup              | Clock           | 2.7V or above     |                   | 40  | -   | ns                 |                 |

|       | time (slave)                    | synchro<br>nous | 1.6V or above     |                   | 45  | -   |                    |                 |

|       | Receive data hold time (master) | Clock syn       | ichronous         | t <sub>RXH</sub>  | 5   | -   | ns                 |                 |

|       | Receive data hold time (slave)  | Clock syn       | chronous          | t <sub>RXH</sub>  | 40  | -   | ns                 |                 |

Note 1. t<sub>Pcyc</sub>: PCLKB cycle.

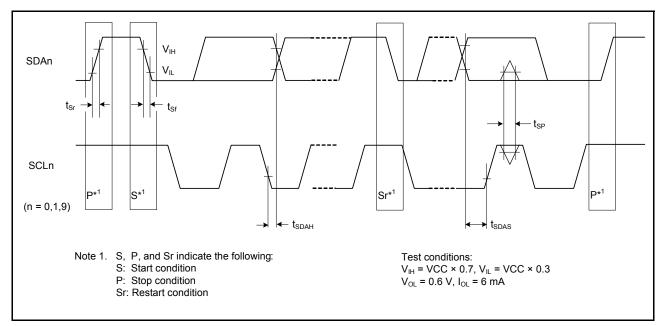

Figure 2.48 SCI simple IIC mode timing

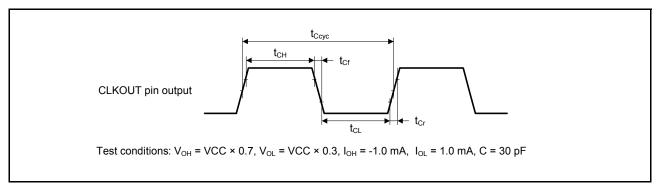

## 2.3.11 CLKOUT Timing

#### Table 2.37 CLKOUT timing

| Parameter | Parameter                     |                      |                   |      | Max | Unit*1 | Test conditions |

|-----------|-------------------------------|----------------------|-------------------|------|-----|--------|-----------------|

| CLKOUT    | CLKOUT pin output cycle*1     | VCC = 2.7 V or above | t <sub>Ccyc</sub> | 62.5 | -   | ns     | Figure 2.57     |

|           |                               | VCC = 1.8 V or above |                   | 125  | -   |        |                 |

|           |                               | VCC = 1.6 V or above |                   | 250  | -   |        |                 |

|           | CLKOUT pin high pulse width*2 | VCC = 2.7 V or above | t <sub>CH</sub>   | 15   | -   | ns     |                 |

|           |                               | VCC = 1.8 V or above |                   | 30   | -   |        |                 |

|           |                               | VCC = 1.6 V or above |                   | 150  | -   |        |                 |

|           | CLKOUT pin low pulse width*2  | VCC = 2.7 V or above | t <sub>CL</sub>   | 15   | -   | ns     |                 |

|           |                               | VCC = 1.8 V or above |                   | 30   | -   |        |                 |

|           |                               | VCC = 1.6 V or above |                   | 150  | -   |        |                 |

|           | CLKOUT pin output rise time   | VCC = 2.7 V or above | t <sub>Cr</sub>   | -    | 12  | ns     |                 |

|           |                               | VCC = 1.8 V or above |                   | -    | 25  |        |                 |

|           |                               | VCC = 1.6 V or above |                   | -    | 50  |        |                 |

|           | CLKOUT pin output fall time   | VCC = 2.7 V or above | t <sub>Cf</sub>   | -    | 12  | ns     |                 |

|           |                               | VCC = 1.8 V or above | 1                 | -    | 25  | 1      |                 |

|           |                               | VCC = 1.6 V or above |                   | -    | 50  |        |                 |

Note 1. When the EXTAL external clock input or an oscillator is used with division by 1 (the CKOCR.CKOSEL[2:0] bits are 011b and the CKOCR.CKODIV[2:0] bits are 000b) to output from CLKOUT, the above should be satisfied with an input duty cycle of 45 to 55%.

Note 2. When the MOCO is selected as the clock output source (the CKOCR.CKOSEL[2:0] bits are 001b), set the clock output division ratio selection to be divided by 2 (the CKOCR.CKODIV[2:0] bits are 001b).

Figure 2.57 CLKOUT output timing

# Table 2.40 A/D conversion characteristics (1) in high-speed A/D conversion mode (2 of 2) Conditions: VCC = AVCC0 = 4.5 to 5.5 V, VREFH0 = 4.5 to 5.5 V, VSS = AVSS0 = VREFL0 = 0V Reference voltage range applied to the VREFH0 and VREFL0.

| Parameter                                                         |                                                                  | Min  | Тур  | Max   | Unit | Test Conditions                                                       |

|-------------------------------------------------------------------|------------------------------------------------------------------|------|------|-------|------|-----------------------------------------------------------------------|

| Conversion time* <sup>1</sup><br>(Operation at<br>PCLKD = 64 MHz) | Permissible signal source impedance Max. = $0.3 \text{ k}\Omega$ | 0.80 | -    | -     | μs   | High-precision channel<br>ADCSR.ADHSC = 0<br>ADSSTRn.SST[7:0] = 0Dh   |

|                                                                   |                                                                  | 1.22 | -    | -     | μs   | Normal-precision channel<br>ADCSR.ADHSC = 0<br>ADSSTRn.SST[7:0] = 28h |

| Offset error                                                      |                                                                  | -    | ±2.0 | ±18   | LSB  | High-precision channel                                                |

|                                                                   |                                                                  |      |      | ±24.0 | LSB  | Other than above                                                      |

| Full-scale error                                                  |                                                                  | -    | ±3.0 | ±18   | LSB  | High-precision channel                                                |

|                                                                   |                                                                  |      |      | ±24.0 | LSB  | Other than above                                                      |

| Quantization error                                                |                                                                  | -    | ±0.5 | -     | LSB  | -                                                                     |

| Absolute accuracy                                                 |                                                                  | -    | ±5.0 | ±20   | LSB  | High-precision channel                                                |

|                                                                   |                                                                  |      |      | ±32.0 | LSB  | Other than above                                                      |

| DNL differential nonlinearity error                               |                                                                  | -    | ±4.0 | -     | LSB  | -                                                                     |

| INL integral nonlinearit                                          | y error                                                          | -    | ±4.0 | ±12.0 | LSB  | -                                                                     |

Note: The characteristics apply when no pin functions other than 14-bit A/D converter input are used. Absolute accuracy does not include quantization errors. Offset error, full-scale error, DNL differential nonlinearity error, and INL integral nonlinearity error do not include quantization errors.

Note 1. The conversion time is the sum of the sampling time and the comparison time. The number of sampling states is indicated for the test conditions.

Note 2. Except for I/O input capacitance (Cin), see section 2.2.4, I/O VOH, VOL, and Other Characteristics.

Note 3. Reference data.

## Table 2.41A/D conversion characteristics (2) in high-speed A/D conversion mode (1 of 2)Conditions: VCC = AVCC0 = 2.7 to 5.5 V, VREFH0 = 2.7 to 5.5 V, VSS = AVSS0 = VREFL0 = 0V

Reference voltage range applied to the VREFH0 and VREFL0.

| Parameter<br>Frequency     |     | Min | Тур | Max               | Unit<br>MHz | Test Conditions          |  |

|----------------------------|-----|-----|-----|-------------------|-------------|--------------------------|--|

|                            |     | 1   | -   | 48                |             |                          |  |

| Analog input capacitance*2 | Cs  | -   | -   | 8* <sup>3</sup>   | pF          | High-precision channel   |  |

|                            |     | -   | -   | 9* <sup>3</sup>   | pF          | Normal-precision channel |  |

| Analog input resistance    | Rs  | -   | -   | 2.5* <sup>3</sup> | kΩ          | High-precision channel   |  |

|                            |     | -   | -   | 6.7* <sup>3</sup> | kΩ          | Normal-precision channel |  |

| Analog input voltage range | Ain | 0   | -   | VREFH0            | V           | -                        |  |

12-bit mode

| Resolution                                                        |                                                         | -    | -     | 12   | Bit | -                                                                     |

|-------------------------------------------------------------------|---------------------------------------------------------|------|-------|------|-----|-----------------------------------------------------------------------|

| Conversion time* <sup>1</sup><br>(Operation at<br>PCLKD = 48 MHz) | Permissible signal<br>source impedance<br>Max. = 0.3 kΩ | 0.94 | -     | -    | μs  | High-precision channel<br>ADCSR.ADHSC = 0<br>ADSSTRn.SST[7:0] = 0Dh   |

|                                                                   |                                                         | 1.50 | -     | -    | μs  | Normal-precision channel<br>ADCSR.ADHSC = 0<br>ADSSTRn.SST[7:0] = 28h |

| Offset error                                                      |                                                         | -    | ±0.5  | ±4.5 | LSB | High-precision channel                                                |

|                                                                   |                                                         |      |       | ±6.0 | LSB | Other than above                                                      |

| Full-scale error                                                  |                                                         | -    | ±0.75 | ±4.5 | LSB | High-precision channel                                                |

|                                                                   |                                                         |      |       | ±6.0 | LSB | Other than above                                                      |

| Quantization error                                                |                                                         | -    | ±0.5  | -    | LSB | -                                                                     |

| Absolute accuracy                                                 |                                                         | -    | ±1.25 | ±5.0 | LSB | High-precision channel                                                |

|                                                                   |                                                         |      |       | ±8.0 | LSB | Other than above                                                      |

| DNL differential nonline                                          | earity error                                            | -    | ±1.0  | -    | LSB | -                                                                     |

| INL integral nonlinearit                                          | y error                                                 | -    | ±1.0  | ±3.0 | LSB | -                                                                     |

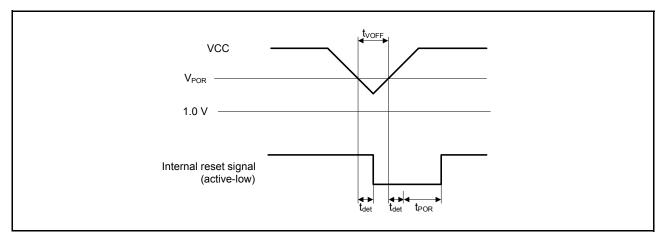

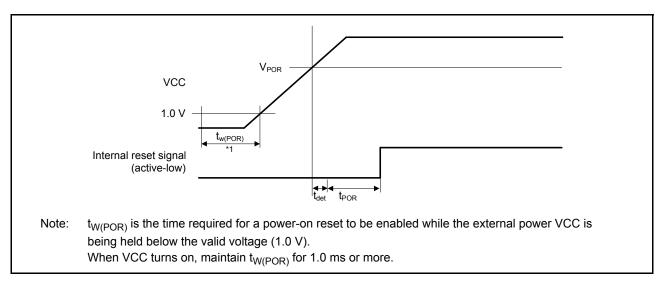

| Parameter                                               | Symbol               | Min | Тур | Max | Unit | Test Conditions                                      |

|---------------------------------------------------------|----------------------|-----|-----|-----|------|------------------------------------------------------|

| Power-on reset enable time                              | t <sub>W (POR)</sub> | 1   | -   | -   | ms   | Figure 2.67,<br>VCC = below 1.0 V                    |

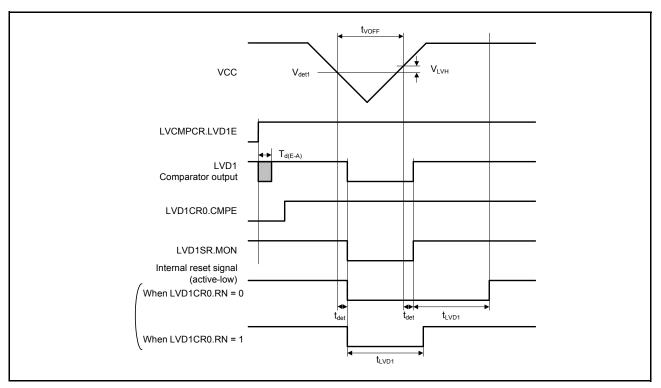

| LVD operation stabilization time (after LVD is enabled) | T <sub>d (E-A)</sub> | -   | -   | 300 | μs   | Figure 2.69,<br>Figure 2.70                          |

| Hysteresis width (POR)                                  | V <sub>PORH</sub>    | -   | 110 | -   | mV   | -                                                    |

| Hysteresis width (LVD0, LVD1, and LVD2)                 | V <sub>LVH</sub>     | -   | 60  | -   | mV   | LVD0 selected                                        |

|                                                         |                      | -   | 100 | -   |      | $V_{det1_0}$ to $V_{det1_2}$ selected.               |

|                                                         |                      | -   | 60  | -   |      | V <sub>det1_3</sub> to V <sub>det1_9</sub> selected. |

|                                                         |                      | -   | 50  | -   |      | $V_{det1\_A}$ to $V_{det1\_B}$ selected.             |

|                                                         |                      | -   | 40  | -   |      | V <sub>det1_C</sub> to V <sub>det1_F</sub> selected. |

|                                                         |                      | -   | 60  | -   |      | LVD2 selected                                        |

Note 1. When OFS1.LVDAS = 0

Note 2. When OFS1.LVDAS = 1

Note 3. The minimum VCC down time indicates the time when VCC is below the minimum value of voltage detection levels  $V_{POR}$ ,  $V_{det0}$ ,  $V_{det1}$ , and  $V_{det2}$  for the POR/LVD.

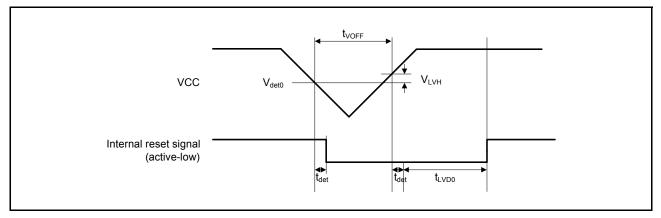

Figure 2.66 Voltage detection reset timing

Figure 2.67 Power-on reset timing

Figure 2.68 Voltage detection circuit timing (V<sub>det0</sub>)

Figure 2.69 Voltage detection circuit timing (V<sub>det1</sub>)

#### Table 2.58 Code flash characteristics (3)

Middle-speed operating mode

Conditions: VCC = AVCC0 = 1.8 to 5.5 V, Ta = -40 to +85°C

|                                          |                 |                   |     | ICLK = 1 I | MHz  |     | ICLK = 8 | MHz  |      |

|------------------------------------------|-----------------|-------------------|-----|------------|------|-----|----------|------|------|

| Parameter                                |                 | Symbol            | Min | Тур        | Max  | Min | Тур      | Max  | Unit |

| Programming time                         | 4-byte          | t <sub>P4</sub>   | -   | 157        | 1411 | -   | 101      | 966  | μs   |

| Erasure time                             | 1-KB            | t <sub>E1K</sub>  | -   | 9.10       | 289  | -   | 6.10     | 228  | ms   |

| Blank check time                         | 2-byte          | t <sub>BC4</sub>  | -   | -          | 87.7 | -   | -        | 52.5 | μs   |

|                                          | 1-KB            | t <sub>BC1K</sub> | -   | -          | 1930 | -   | -        | 414  | μs   |

| Erase suspended time                     |                 | t <sub>SED</sub>  | -   | -          | 32.7 | -   | -        | 21.6 | μs   |

| Startup area switching s                 | etting time     | t <sub>SAS</sub>  | -   | 22.8       | 592  | -   | 14.2     | 465  | ms   |

| Access window time                       |                 | t <sub>AWS</sub>  | -   | 22.8       | 592  | -   | 14.2     | 465  | ms   |

| OCD/serial programmer                    | ID setting time | t <sub>OSIS</sub> | -   | 22.8       | 592  | -   | 14.2     | 465  | ms   |

| Flash memory mode transition wait time 1 |                 | t <sub>DIS</sub>  | 2   | -          | -    | 2   | -        | -    | μs   |

| Flash memory mode transition wait time 2 |                 | t <sub>MS</sub>   | 720 | -          | -    | 720 | -        | -    | ns   |

Note 1. Does not include the time until each operation of the flash memory is started after instructions are executed by the software.

Note 2. The lower-limit frequency of ICLK is 1 MHz during programming or erasing the flash memory. When using ICLK at below 4 MHz, the frequency can be set to 1 MHz, 2 MHz, or 3 MHz. A non-integer frequency such as 1.5 MHz cannot be set.

Note 3. The frequency accuracy of ICLK must be ±3.5% while programming or erasing the flash memory. Confirm the frequency accuracy of the clock source.

### 2.12.2 Data Flash Memory Characteristics

#### Table 2.59Data flash characteristics (1)

| Parameter<br>Reprogramming/erasure cycle*1 |                                          | Parameter         |                     | Symbol              | Min | Тур   | Мах        | Unit | Conditions |

|--------------------------------------------|------------------------------------------|-------------------|---------------------|---------------------|-----|-------|------------|------|------------|

|                                            |                                          | N <sub>DPEC</sub> | 100000              | 1000000             | -   | Times | -          |      |            |

| Data hold time                             | After 10000 times of N <sub>DPEC</sub>   | t <sub>DDRP</sub> | 20*2, *3            | -                   | -   | Year  | Ta = +85°C |      |            |

|                                            | After 100000 times of N <sub>DPEC</sub>  |                   | 5* <sup>2, *3</sup> | -                   | -   | Year  |            |      |            |

|                                            | After 1000000 times of N <sub>DPEC</sub> |                   | -                   | 1* <sup>2, *3</sup> | -   | Year  | Ta = +25°C |      |            |

Note 1. The reprogram/erase cycle is the number of erasure for each block. When the reprogram/erase cycle is n times (n = 100,000), erasing can be performed n times for each block. For instance, when 1-byte programming is performed 1,000 times for different addresses in 1-byte blocks, and then the entire block is erased, the reprogram/erase cycle is counted as 1. However, programming the same address for several times as one erasure is not enabled. (overwriting is prohibited.)

Note 2. Characteristics when using the flash memory programmer and the self-programming library provided by Renesas Electronics.

Note 3. These results are obtained from reliability testing.

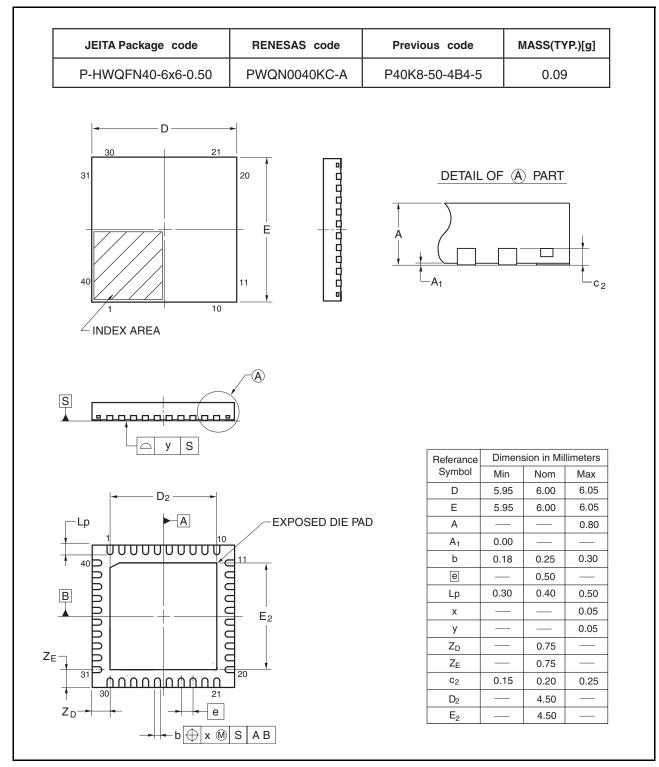

## Appendix 1. Package Dimensions

Information on the latest version of the package dimensions or mountings is displayed in "Packages" on the Renesas Electronics Corporation website.

Figure 1.6 QFN 40-pin

| Revision History | S124 Microcontroller Group Datasheet |

|------------------|--------------------------------------|

|------------------|--------------------------------------|

| Rev. | Date         | Summary     |

|------|--------------|-------------|

| 1.00 | May 19, 2016 | 1st release |

| 1.01 | Oct 3, 2016  | 2nd release |

| 1.30 | Feb 5, 2018  | 3rd release |

#### **Proprietary Notice**

All text, graphics, photographs, trademarks, logos, artwork and computer code, collectively known as content, contained in this document is owned, controlled or licensed by or to Renesas, and is protected by trade dress, copyright, patent and trademark laws, and other intellectual property rights and unfair competition laws. Except as expressly provided herein, no part of this document or content may be copied, reproduced, republished, posted, publicly displayed, encoded, translated, transmitted or distributed in any other medium for publication or distribution or for any commercial enterprise, without prior written consent from Renesas.

Arm<sup>®</sup> and Cortex<sup>®</sup> are registered trademarks of Arm Limited. CoreSight<sup>™</sup> is a trademark of Arm Limited.

CoreMark® is a registered trademark of the Embedded Microprocessor Benchmark Consortium.

Magic Packet<sup>™</sup> is a trademark of Advanced Micro Devices, Inc.

SuperFlash<sup>®</sup> is a registered trademark of Silicon Storage Technology, Inc. in several countries including the United States and Japan.

Other brands and names mentioned in this document may be the trademarks or registered trademarks of their respective holders.