Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                             |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 40MHz                                                                        |

| Connectivity               | CSIO, I <sup>2</sup> C, LINbus, UART/USART, USB                              |

| Peripherals                | I <sup>2</sup> S, LVD, POR, PWM, WDT                                         |

| Number of I/O              | 38                                                                           |

| Program Memory Size        | 64KB (64K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 12K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x12b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 48-LQFP                                                                      |

| Supplier Device Package    | 48-LQFP (7x7)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/s6e1c31c0agv20000 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- □ Generating START, EOM, ACK automatically to output CEC transmission by setting 1 byte data

- □ Generating transmission status interrupt when transmitting 1 block (1 byte data and EOM/ACK)

- ■HDMI-CEC receiver □ Automatic ACK reply function available □ Line error detection function available

- Remote control receiver

4 bytes reception buffer

Repeat code detection function available

### Smart Card Interface (Max 1 Channel)

- Compliant with ISO7816-3 specification

- Card Reader only/B class card only

- Available protocols

□ Transmitter: 8E2, 8O2, 8N2

□ Receiver: 8E1, 8O1, 8N2, 8N1, 9N1

□ Inverse mode

- TX/RX FIFO integrated (RX: 16-bytes, TX:16-bytes)

# **Clock and Reset**

#### Clocks

A clock can be selected from five clock sources (two external oscillators, two built-in CR oscillator, and main PLL).

|                                 | , ,                                                |

|---------------------------------|----------------------------------------------------|

| □ Main clock:                   | 8 MHz to 48 MHz                                    |

| □ Sub clock:                    | 32.768 kHz                                         |

| □ Built-in high-speed CR clock: | : 8 MHz                                            |

| □ Built-in low-speed CR clock:  | 100 kHz                                            |

| □ Main PLL clock                | 8MHz to 16MHz (Input),<br>75MHz to 150MHz (Output) |

|                                 |                                                    |

#### Resets

□ Reset request from the INITX pin □ Power on reset □ Software reset

- □ Software reset

- Watchdog timer reset

Low-voltage detection reset

- Low-voltage detection rese

- Clock supervisor reset

# **Clock Supervisor (CSV)**

The Clock Supervisor monitors the failure of external clocks with a clock generated by a built-in CR oscillator.

- If an external clock failure (clock stop) is detected, a reset is asserted.

- If an external frequency anomaly is detected, an interrupt or a reset is asserted.

#### Low-Voltage Detector (LVD)

This series monitors the voltage on the VCC pin with a 2-stage mechanism. When the voltage falls below a designated voltage, the Low-voltage Detector generates an interrupt or a reset.

- LVD1: monitor V<sub>CC</sub> and error reporting via an interrupt

- ■LVD2: auto-reset operation

#### Low Power Consumption Mode

This series has six low power consumption modes.

- ■Sleep

- ■Timer

- ■RTC

- Stop

- Deep standby RTC (selectable between keeping the value of RAM and not)

- Deep standby Stop (selectable between keeping the value of RAM and not)

### **Peripheral Clock Gating**

The system can reduce the current consumption of the total system with gating the operation clocks of peripheral functions not used.

#### Debug

- ■Serial Wire Debug Port (SW-DP)

- ■Micro Trace Buffer (MTB)

#### **Unique ID**

A 41-bit unique value of the device has been set.

#### **Power Supply**

■Wide voltage range: VCC = 1.65V to 3.6 V

VCC = 3.0V to 3.6V (when USB is used)

| Sales, Solutions, and Legal Information |

|-----------------------------------------|

|-----------------------------------------|

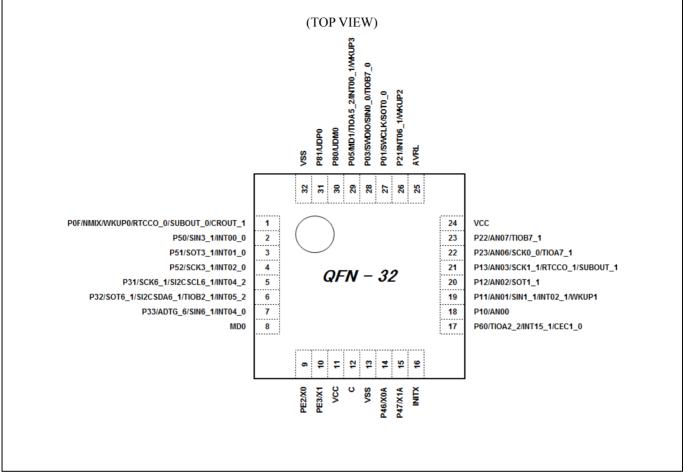

#### LCC-32P-M73

#### Note:

The number after the underscore ("\_") in a pin name such as XXX\_1 and XXX\_2 indicates the relocated port number. The channel on such pin has multiple functions, each of which has its own pin name. Use the Extended Port Function Register (EPFR) to select the pin to be used.

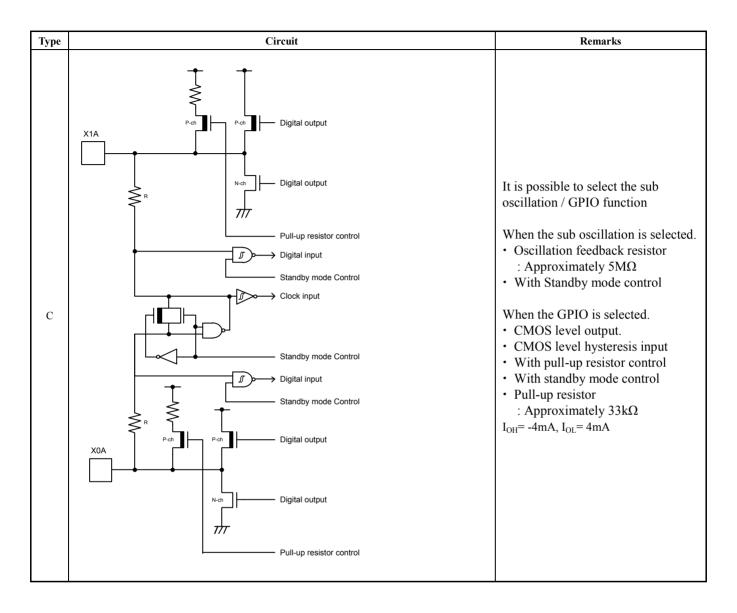

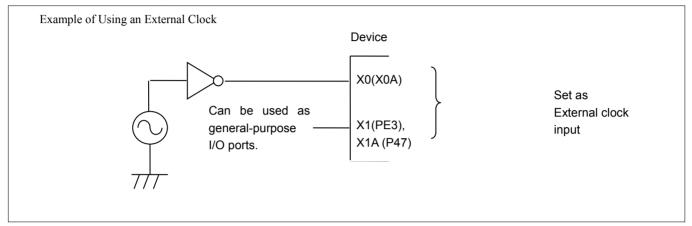

### **Using an External Clock**

When using an external clock as an input of the main clock, set X0/X1 to the external clock input, and input the clock to X0. X1(PE3) can be used as a general-purpose I/O port.

Similarly, when using an external clock as an input of the sub clock, set X0A/X1A to the external clock input, and input the clock to X0A. X1A (P47) can be used as a general-purpose I/O port.

However in the Deep Standby mode, an external clock as an input of the sub clock cannot be used.

### Handling when Using Multi-Function Serial Pin as I<sup>2</sup>C Pin

If it is using the multi-function serial pin as  $I^2C$  pins, P-ch transistor of digital output is always disabled. However,  $I^2C$  pins need to keep the electrical characteristic like other pins and not to connect to the external  $I^2C$  bus system with power OFF.

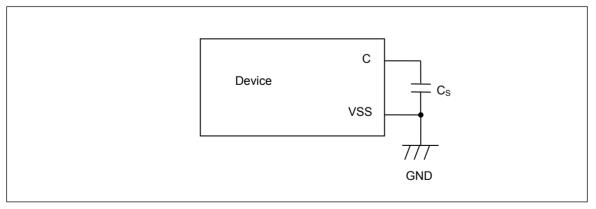

#### C Pin

This series contains the regulator. Be sure to connect a smoothing capacitor ( $C_S$ ) for the regulator between the C pin and the GND pin. Please use a ceramic capacitor or a capacitor of equivalent frequency characteristics as a smoothing capacitor. However, some laminated ceramic capacitors have the characteristics of capacitance variation due to thermal fluctuation (F characteristics and Y5V characteristics). Please select the capacitor that meets the specifications in the operating conditions to use by evaluating the temperature characteristics of a capacitor.

A smoothing capacitor of about 4.7  $\mu$ F would be recommended for this series.

Incidentally, the C pin becomes floating in Deep standby mode.

#### Mode Pins (MD0)

Connect the MD pin (MD0) directly to VCC or VSS pins. Design the printed circuit board such that the pull-up/down resistance stays low, as well as the distance between the mode pins and VCC pins or VSS pins is as short as possible and the connection impedance is low, when the pins are pulled-up/down such as for switching the pin level and rewriting the Flash memory data. It is because of preventing the device erroneously switching to test mode due to noise.

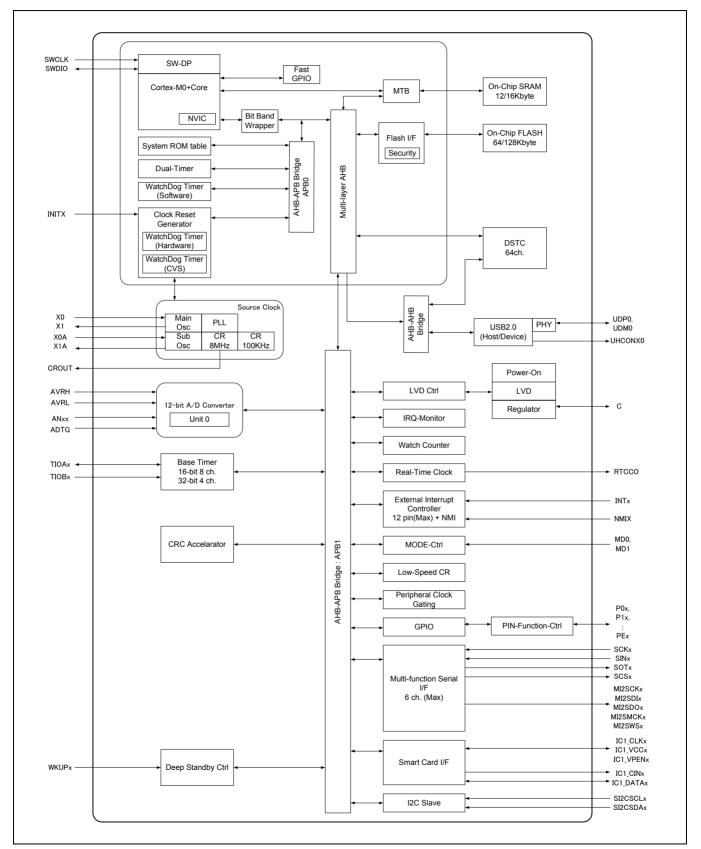

# 8. Block Diagram

# Memory Map (2)

|                            | S6E1C31B0A<br>S6E1C31C0A<br>S6E1C31D0A      | S6E1C32B0A<br>S6E1C32C0A<br>S6E1C32D0A                   |

|----------------------------|---------------------------------------------|----------------------------------------------------------|

| 0x2008_0000                | Reserved                                    | 0x2008_0000<br>Reserved                                  |

| 0x2000_4000                |                                             | 0x2000_4000                                              |

| 0x2000_3000                | SRAM<br>4K byte                             | SRAM<br><sub>0x2000_3000</sub> 4K byte                   |

| 0x2000_1000                | SRAM<br>8K byte                             | SRAM<br>12K byte                                         |

|                            | Reserved                                    | 0x2000_0000<br>Reserved                                  |

| 0x0010_0004<br>0x0010_0000 | CR trimming<br>Security                     | 0x0010_0004 CR trimming<br>0x0010_0000 Security          |

|                            | Reserved                                    | Reserved                                                 |

| 0-0000 FFF0                |                                             | 0x0001_FFF0                                              |

| 0x0000_FFF0                | Flash<br>65520 Byte<br>(64Kbyte - 16Byte) * | Flash<br>131056 Byte<br>(128Kbyte - 16Byte) <sup>*</sup> |

| 0x0000_0000                | (entoyie fobyie)                            | 0×0000_0000                                              |

\*: See "S6E1C1/C3 Series Flash Programming Manual" to check details of the Flash memory.

|                           | Symbol                    |                                                       |                                                        | Va   | lue  |        |         |  |

|---------------------------|---------------------------|-------------------------------------------------------|--------------------------------------------------------|------|------|--------|---------|--|

| Parameter                 | (Pin<br>Name)             | Co                                                    | nditions                                               | Тур  | Max  | Unit   | Remarks |  |

|                           |                           |                                                       | Ta=25°C<br>Vcc=3.3 V                                   | 12.4 | 52.4 | μA     | *1, *2  |  |

|                           | I <sub>ССН</sub><br>(VCC) | Stop mode                                             | Ta=25°C<br>Vcc=1.65 V                                  | 12.0 | 52.0 | μA     | *1, *2  |  |

|                           |                           |                                                       | Ta=105°C<br>Vcc=3.6 V                                  | -    | 597  | μA     | *1, *2  |  |

| I <sub>CCT</sub><br>(VCC) |                           | Ta=25°C<br>Vcc=3.3 V<br>32 kHz Crystal<br>oscillation | 15.6                                                   | 55.6 | μA   | *1, *2 |         |  |

|                           |                           |                                                       | Ta=25°C<br>Vcc=1.65 V<br>32 kHz Crystal<br>oscillation | 15.0 | 55.0 | μA     | *1, *2  |  |

| supply<br>current         | supply<br>current         |                                                       | Ta=105°C<br>Vcc=3.6 V<br>32 kHz Crystal<br>oscillation | -    | 601  | μA     | *1, *2  |  |

|                           |                           |                                                       | Ta=25°C<br>Vcc=3.3 V<br>32 kHz Crystal<br>oscillation  | 13.2 | 53.2 | μA     | *1, *2  |  |

|                           | I <sub>CCR</sub><br>(VCC) | RTC mode                                              | Ta=25°C<br>Vcc=1.65 V<br>32 kHz Crystal<br>oscillation | 12.7 | 52.7 | μA     | *1, *2  |  |

|                           |                           |                                                       | Ta=105℃<br>Vcc=3.6 V<br>32 kHz Crystal<br>oscillation  | -    | 598  | μA     | *1, *2  |  |

\*1: All ports are fixed. LVD off. Flash off.

\*2: When CALDONE bit(CAL\_CTL:CALDONE) is "1". In case of "0", Bipolar Vref current is added.

|                   | Symbol            |              | Va                    | alue                  |      |      |        |         |

|-------------------|-------------------|--------------|-----------------------|-----------------------|------|------|--------|---------|

| Parameter         | (Pin<br>Name)     |              | Conditions            |                       |      |      | Unit   | Remarks |

|                   |                   |              |                       | Ta=25°C<br>Vcc=3.3 V  | 0.58 | 1.85 | μA     | *1, *2  |

|                   |                   |              | RAM off               | Ta=25°C<br>Vcc=1.65 V | 0.56 | 1.83 | μA     | *1, *2  |

|                   | I <sub>CCHD</sub> | Deep standby |                       | Ta=105°C<br>Vcc=3.6 V | -    | 46   | μA     | *1, *2  |

|                   | (VCC) Stop mode   | Stop mode    |                       | Ta=25°C<br>Vcc=3.3 V  | 0.78 | 6.6  | μA     | *1, *2  |

|                   |                   | RAM on       | Ta=25°C<br>Vcc=1.65 V | 0.76                  | 6.6  | μA   | *1, *2 |         |

| Power             |                   |              |                       | Ta=105°C<br>Vcc=3.6 V | -    | 88   | μA     | *1, *2  |

| supply<br>current |                   |              | RAM off               | Ta=25°C<br>Vcc=3.3 V  | 1.16 | 2.4  | μA     | *1, *2  |

|                   |                   |              |                       | Ta=25°C<br>Vcc=1.65 V | 1.15 | 2.4  | μA     | *1, *2  |

|                   | Deep standby      |              | Ta=105°C<br>Vcc=3.6 V | -                     | 46   | μA   | *1, *2 |         |

|                   | RTC mode          |              | Ta=25°C<br>Vcc=3.3 V  | 1.37                  | 7.2  | μA   | *1, *2 |         |

|                   |                   | RAM on       | Ta=25°C<br>Vcc=1.65 V | 1.35                  | 7.2  | μA   | *1, *2 |         |

|                   |                   |              |                       | Ta=105°C<br>Vcc=3.6 V | -    | 88   | μA     | *1, *2  |

\*1: All ports are fixed. LVD off.

\*2: When CALDONE bit(CAL\_CTL:CALDONE) is "1". In case of "0", Bipolar Vref current is added.

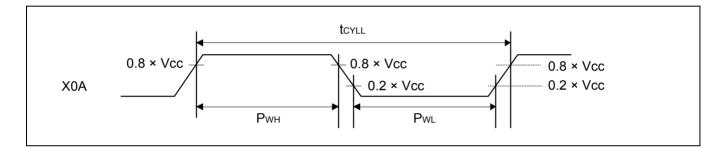

### 11.4.2 Sub Clock Input Characteristics

(V<sub>CC</sub>= 1.65 V to 3.6 V, V<sub>SS</sub>= 0 V, T<sub>A</sub>=- 40°C to +105°C)

| Parameter               | Symbol            | Pin  | Conditions              | Value |        |       | Unit | Remarks                                        |                                    |

|-------------------------|-------------------|------|-------------------------|-------|--------|-------|------|------------------------------------------------|------------------------------------|

| Falameter               | Symbol            | Name | Name                    |       | Тур    | Max   | Onit | Remarks                                        |                                    |

| Input frequency         | f <sub>CL</sub>   |      | -                       | -     | 32.768 | -     | kHz  | When the crystal<br>oscillator is<br>connected |                                    |

|                         |                   | X0A, | X0A,<br>X1A             | -     | 32     | -     | 100  | kHz                                            | When the external<br>clock is used |

| Input clock cycle       | t <sub>CYLL</sub> | AIA  | -                       | 10    | -      | 31.25 | μs   | When the external<br>clock is used             |                                    |

| Input clock pulse width | -                 |      | Pwh/tcyll,<br>Pwl/tcyll | 45    | -      | 55    | %    | When the external<br>clock is used             |                                    |

\*: See "Sub crystal oscillator" in "7. Handling Devices" for the crystal oscillator used.

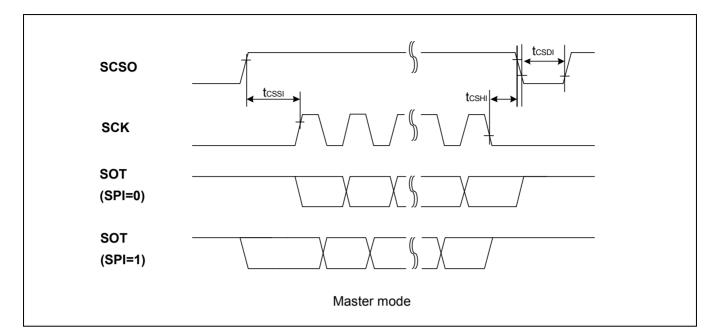

#### 11.4.9 CSIO/SPI/UART Timing

#### CSIO (SPI=0, SCINV=0)

|                                                           |                    |               |             | (V <sub>CC</sub> = 1.6      | 65 V to 3.6 | V, V <sub>SS</sub> = 0 V    | , T <sub>A</sub> =- 40°0 | C to +10 |

|-----------------------------------------------------------|--------------------|---------------|-------------|-----------------------------|-------------|-----------------------------|--------------------------|----------|

| Parameter                                                 | Symbol             | Pin           | Conditions  | V <sub>cc</sub> < 2.7 V     |             | V <sub>cc</sub> ≥ 2.7 V     |                          | Unit     |

| i didineter                                               | Oymbol             | name          | oonaniona   | Min                         | Max         | Min                         | Max                      | Unit     |

| Serial clock cycle time                                   | t <sub>SCYC</sub>  | SCKx          |             | 4 t <sub>CYCP</sub>         | -           | 4 t <sub>CYCP</sub>         | -                        | ns       |

| $\text{SCK} \downarrow \rightarrow \text{SOT}$ delay time | t <sub>SLOVI</sub> | SCKx,<br>SOTx |             | - 30                        | + 30        | - 20                        | + 20                     | ns       |

| $SIN \to SCK \uparrow setup \ time$                       | t <sub>ivshi</sub> | SCKx,<br>SINx | Master mode | 50                          | -           | 36                          | -                        | ns       |

| $SCK \uparrow \to SIN \text{ hold time}$                  | t <sub>shixi</sub> | SCKx,<br>SINx |             | 0                           | -           | 0                           | -                        | ns       |

| Serial clock "L" pulse width                              | t <sub>sLSH</sub>  | SCKx          |             | 2 t <sub>CYCP</sub> -<br>10 | -           | 2 t <sub>CYCP</sub> -<br>10 | -                        | ns       |

| Serial clock "H" pulse width                              | t <sub>SHSL</sub>  | SCKx          |             | t <sub>CYCP</sub> + 10      | -           | t <sub>CYCP</sub> +<br>10   | -                        | ns       |

| $SCK \downarrow \to SOT \text{ delay time}$               | t <sub>SLOVE</sub> | SCKx,<br>SOTx | Slave mode  | -                           | 50          | -                           | 30                       | ns       |

| $SIN \to SCK \uparrow setup \ time$                       | t <sub>IVSHE</sub> | SCKx,<br>SINx | Slave mode  | 10                          | -           | 10                          | -                        | ns       |

| $SCK \uparrow \to SIN \text{ hold time}$                  | t <sub>SHIXE</sub> | SCKx,<br>SINx |             | 20                          | -           | 20                          | -                        | ns       |

| SCK falling time                                          | tF                 | SCKx          |             | -                           | 5           | -                           | 5                        | ns       |

| SCK rising time                                           | tR                 | SCKx          | 1           | -                           | 5           | -                           | 5                        | ns       |

#### Notes:

- The above AC characteristics are for clock synchronous mode.

t<sub>CYCP</sub> represents the APB bus clock cycle time.

For the number of the APB bus to which Multi-function Serial has been connected, see "8. Block Diagram".

- The characteristics are only applicable when the relocate port numbers are the same. For instance, they are not applicable for the combination of SCKx\_0 and SOTx\_1.

- External load capacitance C<sub>L</sub>=30 pF

# SPI (SPI=1, SCINV=0)

| _                                                                |                    | Pin           |             | V <sub>cc</sub> < 2         | 7 V  | V <sub>cc</sub> ≥           | 2 7 V |      |

|------------------------------------------------------------------|--------------------|---------------|-------------|-----------------------------|------|-----------------------------|-------|------|

| Parameter                                                        | Symbol             | name          | Conditions  | Min                         | Max  | Min                         | Max   | Unit |

| Serial clock cycle time                                          | tscyc              | SCKx          |             | 4 t <sub>CYCP</sub>         | -    | 4 t <sub>CYCP</sub>         | -     | ns   |

| $SCK \uparrow \to SOT \text{ delay time}$                        | t <sub>shovi</sub> | SCKx,<br>SOTx |             | - 30                        | + 30 | - 20                        | + 20  | ns   |

| $SIN \to SCK \downarrow setup time$                              | t <sub>IVSLI</sub> | SCKx,<br>SINx | Master mode | 50                          | -    | 36                          | -     | ns   |

| $SCK \downarrow \to SIN \text{ hold time}$                       | t <sub>sLixi</sub> | SCKx,<br>SINx |             | 0                           | -    | 0                           | -     | ns   |

| $\text{SOT} \rightarrow \text{SCK} \downarrow \text{delay time}$ | t <sub>SOVLI</sub> | SCKx,<br>SOTx |             | 2 t <sub>CYCP</sub> -<br>30 | -    | 2 t <sub>CYCP</sub> -<br>30 | -     | ns   |

| Serial clock "L" pulse width                                     | t <sub>sLSH</sub>  | SCKx          |             | 2 t <sub>CYCP</sub> -<br>10 | -    | 2 t <sub>CYCP</sub> -<br>10 | -     | ns   |

| Serial clock "H" pulse width                                     | t <sub>SHSL</sub>  | SCKx          |             | t <sub>CYCP</sub> + 10      | -    | t <sub>CYCP</sub> + 10      | -     | ns   |

| $SCK \uparrow \to SOT$ delay time                                | t <sub>shove</sub> | SCKx,<br>SOTx |             | -                           | 50   | -                           | 33    | ns   |

| $SIN \to SCK \downarrow setup time$                              | t <sub>IVSLE</sub> | SCKx,<br>SINx | Slave mode  | 10                          | -    | 10                          | -     | ns   |

| $SCK \downarrow \to SIN \text{ hold time}$                       | t <sub>SLIXE</sub> | SCKx,<br>SINx |             | 20                          | -    | 20                          | -     | ns   |

| SCK falling time                                                 | tF                 | SCKx          | 1           | -                           | 5    | -                           | 5     | ns   |

| SCK rising time                                                  | tR                 | SCKx          | ]           | -                           | 5    | -                           | 5     | ns   |

#### (V<sub>CC</sub>= 1.65 V to 3.6 V, V<sub>SS</sub>= 0 V, T<sub>A</sub>=- 40°C to +105°C)

#### Notes:

- The above AC characteristics are for clock synchronous mode.

t<sub>CYCP</sub> represents the APB bus clock cycle time.

For the number of the APB bus to which Multi-function Serial has been connected, see "8. Block Diagram".

- The characteristics are only applicable when the relocate port numbers are the same. For instance, they are not applicable for the combination of SCKx\_0 and SOTx\_1.

- External load capacitance C<sub>L</sub>=30 pF

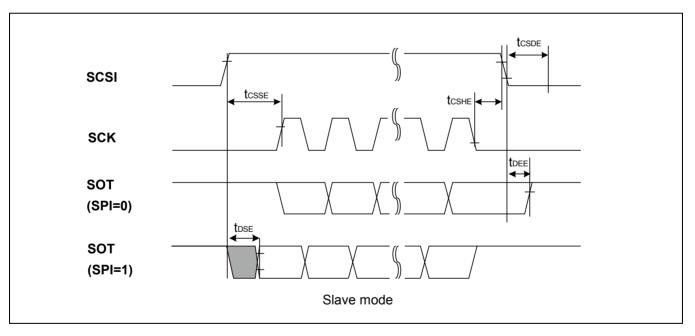

### 11.4.14 SW-DP Timing

(V<sub>CC</sub>= 1.65 V to 3.6 V, V<sub>SS</sub>= 0 V, T<sub>A</sub>=- 40°C to +105°C)

| Parameter        | Symbol           | Pin Name        | Conditions | Value |     | Unit | Remarks   |

|------------------|------------------|-----------------|------------|-------|-----|------|-----------|

| Faranieter       | Symbol           | Fill Name       | Conditions | Min   | Max | Unit | Reillarks |

| SWDIO setup time | t <sub>sws</sub> | SWCLK,<br>SWDIO | -          | 15    | -   | ns   |           |

| SWDIO hold time  | t <sub>SWH</sub> | SWCLK,<br>SWDIO | -          | 15    | -   | ns   |           |

| SWDIO delay time | t <sub>SWD</sub> | SWCLK,<br>SWDIO | -          | -     | 45  | ns   |           |

#### Note:

- External load capacitance C<sub>L</sub>=30 pF

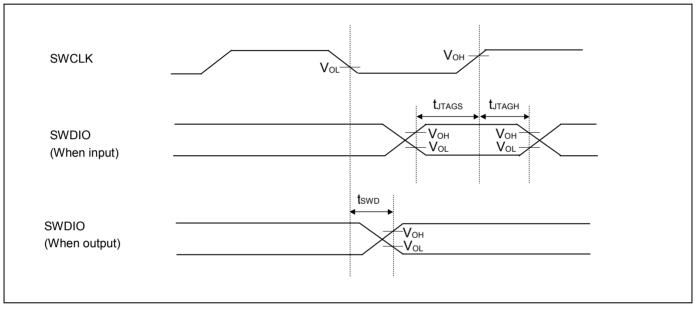

| (Equation | 1) t <sub>S</sub> ≥ | (R <sub>AIN</sub> + | R <sub>EXT</sub> ) | $\times C_{AIN} \times 9$ |  |

|-----------|---------------------|---------------------|--------------------|---------------------------|--|

|-----------|---------------------|---------------------|--------------------|---------------------------|--|

| t <sub>s</sub> :   | Sampling time                                                                       |

|--------------------|-------------------------------------------------------------------------------------|

| R <sub>AIN</sub> : | Input resistance of A/D Converter = 2.2 k $\Omega$ with 2.7 $\leq$ VCC $\leq$ 3.6   |

|                    | Input resistance of A/D Converter = 5.5 k $\Omega$ with 1.8 $\leq$ VCC $\leq$ 2.7   |

|                    | Input resistance of A/D Converter = 10.5 k $\Omega$ with 1.65 $\leq$ VCC $\leq$ 1.8 |

| C <sub>AIN</sub> : | Input capacitance of A/D Converter = 7.5 pF with 1.65 < VCC < 3.6                   |

| utput impedance of | external circuit                                                                    |

| <sub>ск</sub> × 14 |                                                                                     |

| t <sub>C</sub> :   | Compare time                                                                        |

| t <sub>сск</sub> : | Compare clock cycle                                                                 |

|                    | $R_{AIN}$ :<br>$C_{AIN}$ :<br>utput impedance of<br>$_{CK} \times 14$<br>$t_{C}$ :  |

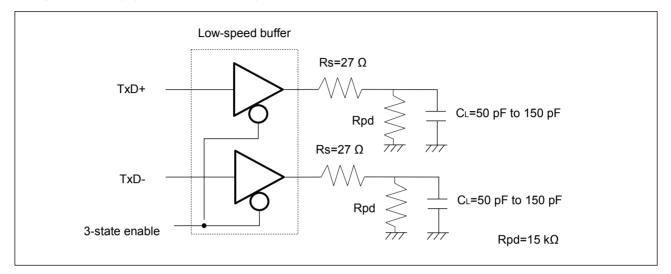

# · Low-Speed Load (Upstream Port Load) – Reference 1

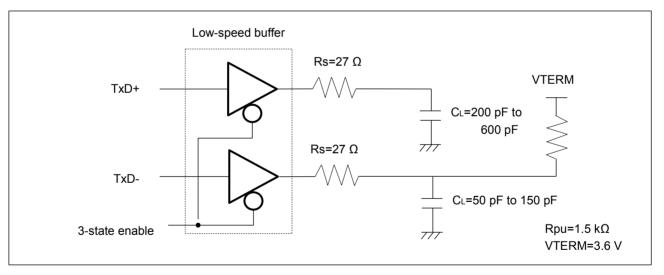

# · Low-Speed Load (Downstream Port Load) – Reference 2

# 11.7.2 Low-Voltage Detection Interrupt

(T<sub>A</sub>=-40°C to +105°C)

| Parameter                   | Symbo              | Conditions | Value |      |                                  | Uni | Domorko            |

|-----------------------------|--------------------|------------|-------|------|----------------------------------|-----|--------------------|

|                             | 1                  |            | Min   | Тур  | Max                              | t   | Remarks            |

| Detected voltage            | VDL                | SVHI=00100 | 1.56  | 1.70 | 1.84                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 1.61  | 1.75 | 1.89                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=00101 | 1.61  | 1.75 | 1.89                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 1.66  | 1.80 | 1.94                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=00110 | 1.66  | 1.80 | 1.94                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 1.70  | 1.85 | 2.00                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=00111 | 1.70  | 1.85 | 2.00                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 1.75  | 1.90 | 2.05                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=01000 | 1.75  | 1.90 | 2.05                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 1.79  | 1.95 | 2.11                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=01001 | 1.79  | 1.95 | 2.11                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 1.84  | 2.00 | 2.16                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=01010 | 1.84  | 2.00 | 2.16                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 1.89  | 2.05 | 2.21                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=01011 | 1.89  | 2.05 | 2.21                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 1.93  | 2.10 | 2.27                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=01100 | 2.30  | 2.50 | 2.70                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 2.39  | 2.60 | 2.81                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=01101 | 2.39  | 2.60 | 2.81                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 2.48  | 2.70 | 2.92                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=01110 | 2.48  | 2.70 | 2.92                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 2.58  | 2.80 | 3.02                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=01111 | 2.58  | 2.80 | 3.02                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 2.67  | 2.90 | 3.13                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=10000 | 2.67  | 2.90 | 3.13                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 2.76  | 3.00 | 3.24                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=10001 | 2.76  | 3.00 | 3.24                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 2.85  | 3.10 | 3.35                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=10010 | 2.85  | 3.10 | 3.35                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 2.94  | 3.20 | 3.46                             | V   | When voltage rises |

| Detected voltage            | VDL                | SVHI=10011 | 2.94  | 3.20 | 3.46                             | V   | When voltage drops |

| Released voltage            | VDH                |            | 3.04  | 3.30 | 3.56                             | V   | When voltage rises |

| LVD stabilization wait time | T <sub>LVDW</sub>  | -          | -     | -    | 8160<br>×<br>t <sub>CYCP</sub> * | μs  |                    |

| LVD detection delay time    | T <sub>LVDDL</sub> | -          | -     | -    | 200                              | μs  |                    |

\*: t<sub>CYCP</sub> represents the APB1 bus clock cycle time.

# 12. Ordering Information

| Part number       | On-chip<br>Flash<br>memory<br>[Kbyte] | On-Chip<br>SRAM<br>[Kbyte] | Package                                  | Packing |

|-------------------|---------------------------------------|----------------------------|------------------------------------------|---------|

| S6E1C32D0AGV20000 | 128                                   | 16                         | Plastic • LQFP (0.50 mm pitch), 64 pins  | Trov    |

| S6E1C31D0AGV20000 | 64                                    | 12                         | (FPT-64P-M38)                            | Tray    |

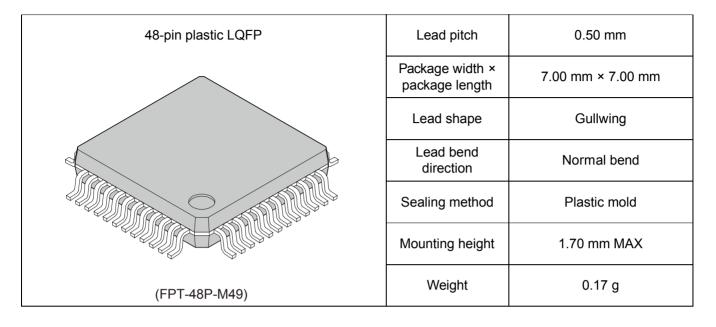

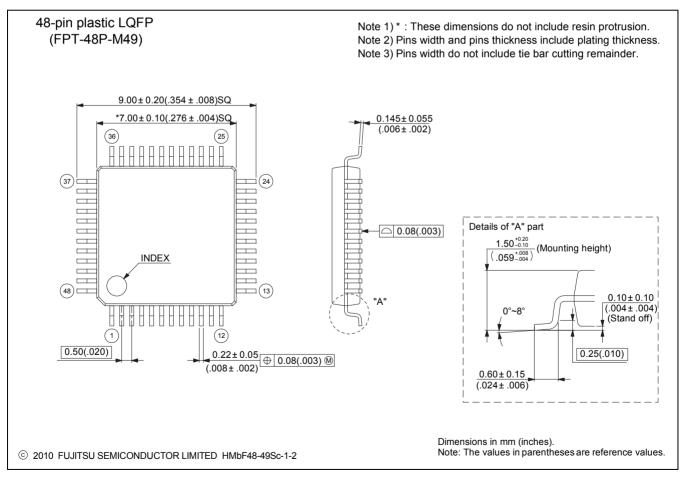

| S6E1C32C0AGV20000 | 128                                   | 16                         | Plastic • LQFP (0.50 mm pitch), 48 pins  | Tray    |

| S6E1C31C0AGV20000 | 64                                    | 12                         | (FPT-48P-M49)                            |         |

| S6E1C32B0AGP20000 | 128                                   | 16                         | Plastic • LQFP (0.80 mm pitch), 32 pins  | Tray    |

| S6E1C31B0AGP20000 | 64                                    | 12                         | (FPT-32P-M30)                            |         |

| S6E1C32D0AGN20000 | 128                                   | 16                         | Plastic • QFN64 (0.50 mm pitch), 64 pins | Tray    |

| S6E1C31D0AGN20000 | 64                                    | 12                         | (LCC-64P-M25)                            |         |

| S6E1C32C0AGN20000 | 128                                   | 16                         | Plastic • QFN48 (0.50 mm pitch), 48 pins | Tray    |

| S6E1C31C0AGN20000 | 64                                    | 12                         | (LCC-48P-M74)                            |         |

| S6E1C32B0AGN20000 | 128                                   | 16                         | Plastic • QFN32 (0.50 mm pitch), 32 pins | Tray    |

| S6E1C31B0AGN20000 | 64                                    | 12                         | (LCC-32P-M73)                            | _       |

| (TBD)             | 128                                   | 16                         | WLCSP (TBD)                              | (TBD)   |

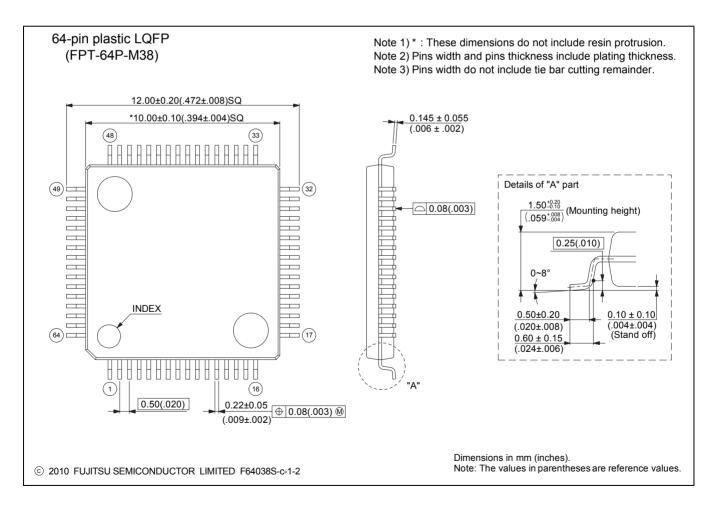

| 64-pin plastic LQFP | Lead pitch                     | 0.50 mm             |  |

|---------------------|--------------------------------|---------------------|--|

|                     | Package width × package length | 10.00 mm × 10.00 mm |  |

|                     | Lead shape                     | Gullwing            |  |

|                     | Lead bend direction            | Normal bend         |  |

|                     | Sealing method                 | Plastic mold        |  |

|                     | Mounting height                | 1.70 mm MAX         |  |

| (FPT-64P-M38)       | Weight                         | 0.32 g              |  |