### Microchip Technology - PIC16F15325-E/P Datasheet

# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 14-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15325-e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4-2: MEMORY ACCESS PARTITION

|         |                                                                                                     |                                     | Part                         | tition                       |                                     |

|---------|-----------------------------------------------------------------------------------------------------|-------------------------------------|------------------------------|------------------------------|-------------------------------------|

| REG     | Address                                                                                             | <u>BBEN</u> = 1<br>SAFEN = 1        | <u>BBEN</u> = 1<br>SAFEN = 0 | <u>BBEN</u> = 0<br>SAFEN = 1 | <u>BBEN</u> = 0<br>SAFEN = 0        |

|         | 00 0000h<br>•••<br>Last Boot Block Memory<br>Address                                                |                                     | APPLICATION                  | BOOT BLOCK <sup>(4)</sup>    | BOOT BLOCK <sup>(4)</sup>           |

| PFM     | Last Boot Block Memory<br>Address + 1 <sup>(1)</sup><br>•••<br>Last Program Memory<br>Address - 80h | APPLICATION<br>BLOCK <sup>(4)</sup> | BLOCK <sup>(4)</sup>         | APPLICATION                  | APPLICATION<br>BLOCK <sup>(4)</sup> |

|         | Last Program Memory<br>Address - 7Fh <sup>(2)</sup><br>•••<br>Last Program Memory<br>Address        |                                     | SAF <sup>(4)</sup>           | BLOCK <sup>(4)</sup>         | SAF <sup>(4)</sup>                  |

| CONF IG | Config Memory Address <sup>(3)</sup>                                                                |                                     | COI                          | NFIG                         | 1                                   |

Note 1: Last Boot Block Memory Address is based on BBSIZE<2:0> given in Table 5-1.

2: Last Program Memory Address is the Flash size given in Table 4-1.

3: Config Memory Address are the address locations of the Configuration Words given in Table 13-2.

**4:** Each memory block has a corresponding write protection fuse defined by the WRTAPP, WRTB and WRTC bits in the Configuration Word (Register 5-4).

| Address | Name                 | Bit 7                 | Bit 6                 | Bit 5   | Bit 4         | Bit 3             | Bit 2     | Bit 1  | Bit 0  | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|----------------------|-----------------------|-----------------------|---------|---------------|-------------------|-----------|--------|--------|-----------------------|----------------------------|

| Bank 0  |                      | •                     | •                     |         | •             | •                 |           | •      |        |                       |                            |

|         |                      |                       |                       | CPU COF | RE REGISTERS; | see Table 4-9 for | specifics |        |        |                       |                            |

| 00Ch    | PORTA                | _                     |                       | RA5     | RA4           | RA3               | RA2       | RA1    | RA0    | xx xxxx               | uu uuuu                    |

| 00Dh    | PORTB <sup>(1)</sup> | RB7                   | RB6                   | RB5     | RB4           | —                 | _         | _      | _      | xxxx                  | uuuu                       |

| 00Eh    | PORTC                | RC7 <sup>(1)</sup>    | RC6 <sup>(1)</sup>    | RC5     | RC4           | RC3               | RC2       | RC1    | RC0    | xxxx xxxx             | uuuu uuuu                  |

| 00Fh    | _                    |                       | Unimplemented         |         |               |                   |           |        |        |                       | _                          |

| 010h    | _                    |                       | Unimplemented         |         |               |                   |           |        |        |                       | _                          |

| 011h    | _                    |                       |                       |         | Unimple       | mented            |           |        |        |                       |                            |

| 012h    | TRISA                | _                     | _                     | TRISA5  | TRISA4        | —                 | TRISA2    | TRISA1 | TRISA0 | 11 1111               | 11 1111                    |

| 013h    | TRISB <sup>(1)</sup> | TRISB7                | TRISB6                | TRISB5  | TRISB4        | —                 | _         | —      | _      | xxxx                  | uuuu                       |

| 014h    | TRISC                | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5  | TRISC4        | TRISC3            | TRISC2    | TRISC1 | TRISC0 | 1111 1111             | 1111 1111                  |

| 015h    | —                    |                       |                       |         | Unimple       | mented            |           |        |        | —                     | _                          |

| 016h    | —                    |                       |                       |         | Unimple       | mented            |           |        |        | —                     | —                          |

| 017h    | —                    |                       |                       |         | Unimple       | mented            |           |        |        | —                     | —                          |

| 018h    | LATA                 | —                     | —                     | LATA5   | LATA4         | —                 | LATA2     | LATA1  | LATA0  | xx xxxx               | uu uuuu                    |

| 019h    | LATB <sup>(1)</sup>  | LATB7                 | LATB6                 | LATB5   | LATB4         | —                 |           | —      |        | xxxx                  | uuuu                       |

| 01Ah    | LATC                 | LATC7 <sup>(1)</sup>  | LATC6 <sup>(1)</sup>  | LATC5   | LATC4         | LATC3             | LATC2     | LATC1  | LATC0  | xxxx xxxx             | uuuu uuuu                  |

| 01Eh    | —                    |                       | Unimplemented         |         |               |                   |           |        |        | —                     | —                          |

| 01Fh    | _                    |                       | Unimplemented         |         |               |                   |           |        |        | _                     | _                          |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Present only in PIC16(L)F15345.

| Address            | Name            | Bit 7         | Bit 6            | Bit 5   | Bit 4         | Bit 3               | Bit 2     | Bit 1 | Bit 0     | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|--------------------|-----------------|---------------|------------------|---------|---------------|---------------------|-----------|-------|-----------|-----------------------|----------------------------|

| Bank 61            |                 |               |                  |         |               |                     |           |       |           |                       |                            |

|                    |                 |               |                  | CPU COF | RE REGISTERS  | ; see Table 4-3 for | specifics |       |           |                       |                            |

| 1E8Ch              | _               |               |                  |         | Unimple       | emented             |           |       |           | _                     | _                          |

| 1E8Dh              | _               |               |                  |         | Unimple       | emented             |           |       |           | —                     | —                          |

| 1E8Eh              | _               |               |                  |         | Unimple       | emented             |           |       |           | —                     | —                          |

| 1E8Fh              | PPSLOCK         | —             | —                | —       | —             | —                   | —         | —     | PPSLOCKED | 0                     | 0                          |

| 1E90h              | INTPPS          | —             | —                |         |               | INTP                | PS<5:0>   |       |           | 00 1000               | uu uuuu                    |

| 1E91h              | <b>T0CKIPPS</b> | —             | —                |         |               | TOCKI               | PPS<5:0>  |       |           | 00 0100               | uu uuuu                    |

| 1E92h              | T1CKIPPS        | —             | —                |         |               | TICKI               | PPS<5:0>  |       |           | 01 0000               | uu uuuu                    |

| 1E93h              | T1GPPS          | _             | —                |         |               | T1GF                | PPS<5:0>  |       |           | 00 1101               | uu uuuu                    |

| 1E94h<br><br>1E9Bh | _               | Unimplemented |                  |         |               |                     |           | -     | -         |                       |                            |

| 1E9Ch              | T2INPPS         | _             | _                |         | T2INPPS<5:0>  |                     |           |       |           | 01 0011               | uu uuuu                    |

| 1E9Dh<br><br>1EA0h | _               | Unimplemented |                  |         |               |                     |           | _     | _         |                       |                            |

| 1EA1h              | CCP1PPS         | _             | _                |         |               | CCP1                | PPS<5:0>  |       |           | 01 0010               | uu uuuu                    |

| 1EA2h              | CCP2PPS         | _             | _                |         |               | CCP2                | PPS<5:0>  |       |           | 01 0001               | uu uuuu                    |

| 1EA3h<br><br>1EB0h | _               |               |                  |         | Unimple       | emented             |           |       |           | _                     | _                          |

| 1EB1h              | CWG1PPS         | _             | _                |         |               | CWG1                | PPS<5:0>  |       |           | 00 1000               | uu uuuu                    |

| 1EB2h<br>1EBAh     | _               |               | ·                |         | Unimple       | emented             |           |       |           | _                     | _                          |

| 1EBBh              | CLCIN0PPS       | _             | _                |         |               | CLCIN               | 0PPS<5:0> |       |           | 00 0000               | uu uuuu                    |

| 1EBCh              | CLCIN1PPS       | _             | _                |         |               | CLCIN               | 1PPS<5:0> |       |           | 00 0001               | uu uuuu                    |

| 1EBDh              | CLCIN2PPS       |               | _                |         |               | CLCIN               | 2PPS<5:0> |       |           | 00 1110               | uu uuuu                    |

| 1EBEh              | CLCIN3PPS       | _             | - CLCIN3PPS<5:0> |         |               |                     |           |       | 00 1111   | uu uuuu               |                            |

| 1EBFh<br>1EC2h     | _               |               | Unimplemented    |         |               |                     |           |       | _         | -                     |                            |

| 1EC3h              | ADACTPPS        | _             | _                |         |               | CLCIN               | 3PPS<5:0> |       |           | 001100                | uuuuuu                     |

| 1EC4h              | _               |               |                  | ·       | Unimplemented |                     |           |       |           |                       |                            |

#### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

### 8.3 Register Definitions: Brown-out Reset Control

Legend:

REGISTER 8-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u               | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|-----------------------|-----|-----|-----|-----|-----|-----|--------|

| SBOREN <sup>(1)</sup> | _   | —   | —   | —   | —   | —   | BORRDY |

| bit 7                 |     |     |     |     |     |     | bit 0  |

|                       |     |     |     |     |     |     |        |

| Logona.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | SBOREN: Software Brown-out Reset Enable bit <sup>(1)</sup> |

|---------|------------------------------------------------------------|

|         | If BOREN <1:0> in Configuration Words $\neq 01$ :          |

|         | SBOREN is read/write, but has no effect on the BOR.        |

|         | If BOREN <1:0> in Configuration Words = 01:                |

|         | 1 = BOR Enabled                                            |

|         | 0 = BOR Disabled                                           |

| bit 6-1 | Unimplemented: Read as '0'                                 |

| bit 0   | BORRDY: Brown-out Reset Circuit Ready Status bit           |

|         | 1 = The Brown-out Reset circuit is active                  |

0 = The Brown-out Reset circuit is inactive

**Note 1:** BOREN<1:0> bits are located in Configuration Words.

#### 8.13 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON registers are updated to indicate the cause of the Reset. Table 8-3 and Table 8-4 show the Reset conditions of these registers.

| STOVF | STKUNF | RWDT | RMCLR | RI | POR | BOR | <u>10</u> | DA | MEMV | Condition                          |

|-------|--------|------|-------|----|-----|-----|-----------|----|------|------------------------------------|

| 0     | 0      | 1    | 1     | 1  | 0   | x   | 1         | 1  | 1    | Power-on Reset                     |

| 0     | 0      | 1    | 1     | 1  | 0   | x   | 0         | x  | u    | Illegal, TO is set on POR          |

| 0     | 0      | 1    | 1     | 1  | 0   | x   | x         | 0  | u    | Illegal, PD is set on POR          |

| 0     | 0      | u    | 1     | 1  | u   | 0   | 1         | 1  | u    | Brown-out Reset                    |

| u     | u      | 0    | u     | u  | u   | u   | 0         | u  | u    | WWDT Reset                         |

| u     | u      | u    | u     | u  | u   | u   | 0         | 0  | u    | WWDT Wake-up from Sleep            |

| u     | u      | u    | u     | u  | u   | u   | 1         | 0  | u    | Interrupt Wake-up from Sleep       |

| u     | u      | u    | 0     | u  | u   | u   | u         | u  | 1    | MCLR Reset during normal operation |

| u     | u      | u    | 0     | u  | u   | u   | 1         | 0  | u    | MCLR Reset during Sleep            |

| u     | u      | u    | u     | 0  | u   | u   | u         | u  | u    | RESET Instruction Executed         |

| 1     | u      | u    | u     | u  | u   | u   | u         | u  | u    | Stack Overflow Reset (STVREN = 1)  |

| u     | 1      | u    | u     | u  | u   | u   | u         | u  | u    | Stack Underflow Reset (STVREN = 1) |

| u     | u      | u    | u     | u  | u   | u   | u         | u  | 0    | Memory violation Reset             |

#### TABLE 8-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

### TABLE 8-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                                        | Program<br>Counter    | STATUS<br>Register | PCON0<br>Register | PCON1<br>Register |

|--------------------------------------------------|-----------------------|--------------------|-------------------|-------------------|

| Power-on Reset                                   | 0000h                 | 1 1000             | 0011 110x         | 1-                |

| MCLR Reset during normal operation               | 0000h                 | u uuuu             | uuuu Ouuu         | 1-                |

| MCLR Reset during Sleep                          | 0000h                 | 1 Ouuu             | uuuu Ouuu         | u-                |

| WWDT Timeout Reset                               | 0000h                 | 0 uuuu             | uuu0 uuuu         | u-                |

| WWDT Wake-up from Sleep                          | PC + 1                | 0 Ouuu             | uuuu uuuu         | u-                |

| WWDT Window Violation                            | 0000h                 | u uuuu             | uu0u uuuu         | u-                |

| Brown-out Reset                                  | 0000h                 | 1 1000             | 0011 11u0         | u-                |

| Interrupt Wake-up from Sleep                     | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uuuu uuuu         | u-                |

| RESET Instruction Executed                       | 0000h                 | u uuuu             | uuuu u0uu         | u-                |

| Stack Overflow Reset (STVREN = 1)                | 0000h                 | u uuuu             | luuu uuuu         | u-                |

| Stack Underflow Reset (STVREN = 1)               | 0000h                 | u uuuu             | uluu uuuu         | u-                |

| Memory Violation Reset ( $\overline{MEMV} = 0$ ) | 0                     | -uuu uuuu          | uuuu uuuu         | 0-                |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

# PIC16(L)F15325/45

| REGISTER         | 16-2: PMD                                                                                       | 1: PMD CON                                                                     |      | STER 1         |                  |                  |              |

|------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------|----------------|------------------|------------------|--------------|

| R/W-0/0          | U-0                                                                                             | U-0                                                                            | U-0  | U-0            | R/W-0/0          | R/W-0/0          | R/W-0/0      |

| NCO1MD           |                                                                                                 | _                                                                              | _    | —              | TMR2MD           | TMR1MD           | TMR0MD       |

| bit 7            |                                                                                                 |                                                                                |      |                |                  |                  | bit 0        |

| r                |                                                                                                 |                                                                                |      |                |                  |                  |              |

| Legend:          |                                                                                                 |                                                                                |      |                |                  |                  |              |

| R = Readab       | le bit                                                                                          | W = Writable                                                                   | bit  | U = Unimplem   | nented bit, read | as '0'           |              |

| u = Bit is un    | changed                                                                                         | x = Bit is unk                                                                 | nown | -n/n = Value a | t POR and BO     | R/Value at all c | other Resets |

| '1' = Bit is se  | et                                                                                              | '0' = Bit is cle                                                               | ared | q = Value dep  | ends on condit   | ion              |              |

| bit 7<br>bit 6-3 | 1 = NCO1 m<br>0 = NCO1 m                                                                        | isable Numeric<br>nodule disabled<br>nodule enabled<br>n <b>ted:</b> Read as ' |      | scillator bit  |                  |                  |              |

| bit 2            |                                                                                                 |                                                                                |      |                |                  |                  |              |

| bit 1            | bit 1 TMR1MD: Disable Timer TMR1 bit<br>1 = Timer1 module disabled<br>0 = Timer1 module enabled |                                                                                |      |                |                  |                  |              |

| bit 0            | 1 = Timer0 r                                                                                    | isable Timer TM<br>nodule disabled<br>nodule enabled                           | 1    |                |                  |                  |              |

| R/W/HS-0/0                           | R/W/HS-0/0 | R/W/HS-0/0      | R/W/HS-0/0     | U-0                                                   | U-0 | U-0 | U-0   |  |  |

|--------------------------------------|------------|-----------------|----------------|-------------------------------------------------------|-----|-----|-------|--|--|

| IOCBF7                               | IOCBF6     | IOCBF5          | IOCBF4         | _                                                     | —   | —   | _     |  |  |

| bit 7                                |            |                 |                |                                                       |     |     | bit 0 |  |  |

|                                      |            |                 |                |                                                       |     |     |       |  |  |

| Legend:                              |            |                 |                |                                                       |     |     |       |  |  |

| R = Readable                         | bit        | W = Writable    | bit            | U = Unimplemented bit, read as '0'                    |     |     |       |  |  |

| u = Bit is unch                      | anged      | x = Bit is unkr | nown           | -n/n = Value at POR and BOR/Value at all other Resets |     |     |       |  |  |

| '1' = Bit is set '0' = Bit is cleare |            | ared            | HS - Bit is se | t in hardware                                         |     |     |       |  |  |

|                                      |            |                 |                |                                                       |     |     |       |  |  |

| L:1 7 4                              |            |                 |                |                                                       |     |     |       |  |  |

#### REGISTER 17-6: IOCBF: INTERRUPT-ON-CHANGE PORTB FLAG REGISTER

| bit 7-4 | <ul> <li>IOCBF&lt;7:4&gt;: Interrupt-on-Change PORTB Flag bits</li> <li>1 = An enabled change was detected on the associated pin.<br/>Set when IOCBPx = 1 and a rising edge was detected on RBx, or when IOCBNx = 1 and a falling edge was detected on RBx.</li> <li>0 = No change was detected, or the user cleared the detected change.</li> </ul> |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-0 | Unimplemented: read as '0'                                                                                                                                                                                                                                                                                                                           |

| Name     | Bit 7  | Bit 6  | Bit 5     | Bit 4   | Bit 3        | Bit 2 | Bit 1 Bit 0 |         | Register<br>on page |  |

|----------|--------|--------|-----------|---------|--------------|-------|-------------|---------|---------------------|--|

| FVRCON   | FVREN  | FVRRDY | TSEN      | TSRNG   | CDAFVR<1:0>  |       | ADFVR<1:0>  |         | 220                 |  |

| ADCON0   |        |        | CHS<      | 5:0>    |              |       | GO/DONE     | ADON    | 233                 |  |

| ADCON1   | ADFM   |        | ADCS<2:0> |         | _            | _     | ADPRE       | F<1:0>  | 234                 |  |

| DAC1CON0 | DAC1EN | -      | DAC10E1   | DAC10E2 | DAC1PSS<1:0> |       | _           | DAC1NSS | 242                 |  |

TABLE 18-1: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

Legend: - = unimplemented locations read as '0'. Shaded cells are not used with the Fixed Voltage Reference.

| Name     | Bit 7        | Bit 6           | Bit 5          | Bit 4            | Bit 3             | Bit 2      | Bit 1    | Bit 0 | Register<br>on Page |

|----------|--------------|-----------------|----------------|------------------|-------------------|------------|----------|-------|---------------------|

| TMR0L    | Holding Regi | ster for the Le | ast Significa  | nt Byte of the 1 | 6-bit TMR0 Regis  | ter        |          |       | 270*                |

| TMR0H    | Holding Regi | ster for the Me | ost Significar | t Byte of the 1  | 6-bit TMR0 Regist | er         |          |       | 270*                |

| T0CON0   | T0EN         | —               | TOOUT          | T016BIT          |                   | T0OUTPS    | <3:0>    |       | 273                 |

| T0CON1   |              | T0CS<2:0>       |                | T0ASYNC          |                   | T0CKPS<    | 3:0>     |       | 274                 |

| T0CKIPPS | _            | _               |                |                  | T0CKIPPS          | <5:0>      |          |       | 199                 |

| TMR0PPS  | —            | _               |                |                  | TMR0PPS<          | <5:0>      |          |       | 199                 |

| T1GCON   | GE           | GPOL            | GTM            | GSPM             | GGO/DONE          | GVAL       |          | _     | 285                 |

| INTCON   | GIE          | PEIE            | _              | _                | _                 | _          | — INTEDG |       | 124                 |

| PIR0     | —            | _               | TMR0IF         | IOCIF            | _                 | _          | _        | INTF  | 133                 |

| PIE0     | —            | —               | TMR0IE         | IOCIE            | _                 | — — — INTE |          | 125   |                     |

#### TABLE 25-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the Timer0 module.

\* Page with Register information.

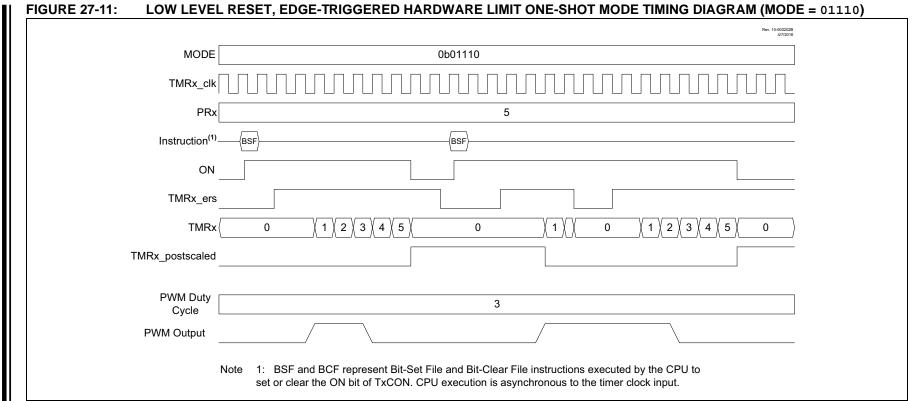

#### 27.5.2 HARDWARE GATE MODE

The Hardware Gate modes operate the same as the Software Gate mode except the TMRx\_ers external signal gates the timer. When used with the CCP the gating extends the PWM period. If the timer is stopped when the PWM output is high then the duty cycle is also extended.

When MODE<4:0> = 00001 then the timer is stopped when the external signal is high. When MODE<4:0> = 00010 then the timer is stopped when the external signal is low.

Figure 27-5 illustrates the Hardware Gating mode for MODE<4:0> = 00001 in which a high input level starts the counter.

|                                 | Rev. 10.000 1998<br>\$500/2014                                                                                                                                                                                                                                                                                            |  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MODE                            | 0b00001                                                                                                                                                                                                                                                                                                                   |  |

| TMRx_clk                        |                                                                                                                                                                                                                                                                                                                           |  |

| TMRx_ers_                       |                                                                                                                                                                                                                                                                                                                           |  |

| PRx                             | 5                                                                                                                                                                                                                                                                                                                         |  |

| TMRx(                           | $0 \qquad \begin{pmatrix} 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \\ 1 \\ 1 \\ 2 \\ 1 \\ 1 \\ 2 \\ 1 \\ 1 \\ 1 \\ 2 \\ 1 \\ 1$ |  |

| TMRx_postscaled_                |                                                                                                                                                                                                                                                                                                                           |  |

| PWM Duty<br>Cycle<br>PWM Output | 3                                                                                                                                                                                                                                                                                                                         |  |

| Name     | Bit 7       | Bit 6       | Bit 5          | Bit 4        | Bit 3     | Bit 2       | Bit 1    | Bit 0  | Register<br>on Page |

|----------|-------------|-------------|----------------|--------------|-----------|-------------|----------|--------|---------------------|

| INTCON   | GIE         | PEIE        | —              | _            | —         | —           | —        | INTEDG | 124                 |

| PIR4     | —           | —           | —              | _            | —         | _           | TMR2IF   | TMR1IF | 137                 |

| PIE4     | _           | —           | —              | _            | _         | _           | TMR2IE   | TMR1IE | 129                 |

| CCP1CON  | EN          | _           | OUT            | FMT          |           | MODE        | =<3:0>   |        | 321                 |

| CCP1CAP  | —           | _           | —              | _            | _         |             | CTS<2:0> |        | 323                 |

| CCPR1L   | Capture/Con | npare/PWM F | Register 1 (LS | B)           |           |             |          |        | 323                 |

| CCPR1H   | Capture/Con | npare/PWM F | Register 1 (MS | ter 1 (MSB)  |           |             |          |        |                     |

| CCP2CON  | EN          | —           | OUT            | FMT          | MODE<3:0> |             |          |        | 321                 |

| CCP2CAP  | —           | _           | —              | _            | _         |             | CTS<2:0> |        | 323                 |

| CCPR2L   | Capture/Con | npare/PWM F | Register 1 (LS | B)           |           |             |          |        | 323                 |

| CCPR2H   | Capture/Con | npare/PWM F | Register 1 (MS | SB)          |           |             |          |        | 323                 |

| CCP1PPS  | _           | —           |                |              | CCP1P     | PS<5:0>     |          |        | 199                 |

| CCP2PPS  | —           | —           |                |              | CCP2P     | PS<5:0>     |          |        | 199                 |

| RxyPPS   | _           | _           | _              |              |           | RxyPPS<4:0> | >        |        | 200                 |

| ADACT    | —           | _           | _              | - ADACT<3:0> |           |             |          |        | 235                 |

| CLCxSELy | —           | —           | —              |              |           | LCxDyS<4:0> | >        |        | 367                 |

| CWG1ISM  | _           | _           | _              | _            |           | IS<         | 3:0>     |        | 356                 |

#### TABLE 28-5: SUMMARY OF REGISTERS ASSOCIATED WITH CCPx

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used by the CCP module.

| R/W-0/0          | U-0       | U-0                                     | U-0            | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u      |

|------------------|-----------|-----------------------------------------|----------------|----------------|------------------|------------------|--------------|

| LCxPOL           | —         |                                         |                | LCxG4POL       | LCxG3POL         | LCxG2POL         | LCxG1POL     |

| bit 7            |           |                                         |                |                |                  |                  | bit 0        |

|                  |           |                                         |                |                |                  |                  |              |

| Legend:          |           |                                         |                |                |                  |                  |              |

| R = Readable I   | bit       | W = Writable                            | bit            | U = Unimpler   | mented bit, read | l as '0'         |              |

| u = Bit is uncha | anged     | x = Bit is unkn                         | own            | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set |           | '0' = Bit is clea                       | ared           |                |                  |                  |              |

|                  |           |                                         |                |                |                  |                  |              |

| bit 7            |           | CxOUT Output                            | 5              |                |                  |                  |              |

|                  |           | ut of the logic o                       |                |                |                  |                  |              |

| bit 6-4          | •         | ut of the logic o                       |                | nea            |                  |                  |              |

|                  | -         | ted: Read as '                          |                |                |                  |                  |              |

| bit 3            |           | Gate 3 Output I                         | •              |                |                  |                  |              |

|                  |           | ut of gate 3 is i<br>ut of gate 3 is r  |                | applied to the | logic cell       |                  |              |

| bit 2            | •         | Gate 2 Output I                         |                | rol bit        |                  |                  |              |

|                  |           | -                                       | -              | applied to the | logic cell       |                  |              |

|                  | •         | ut of gate 2 is r                       |                |                | 5                |                  |              |

| bit 1            | LCxG2POL: | Gate 1 Output I                         | Polarity Conti | rol bit        |                  |                  |              |

|                  |           | ut of gate 1 is i<br>ut of gate 1 is r  |                | applied to the | logic cell       |                  |              |

| bit 0            | LCxG1POL: | Gate 0 Output I                         | Polarity Conti | rol bit        |                  |                  |              |

|                  |           | ut of gate 0 is in<br>ut of gate 0 is r |                | applied to the | logic cell       |                  |              |

#### REGISTER 31-2: CLCxPOL: SIGNAL POLARITY CONTROL REGISTER

#### 32.5.2.2 7-bit Reception with AHEN and DHEN

Slave device reception with AHEN and DHEN set operate the same as without these options with extra interrupts and clock stretching added after the eighth falling edge of SCL. These additional interrupts allows time for the slave software to decide whether it wants to ACK the receive address or data byte.

This list describes the steps that need to be taken by slave software to use these options for  $I^2C$  communication. Figure 32-16 displays a module using both address and data holding. Figure 32-17 includes the operation with the SEN bit of the SSP1CON2 register set.

- 1. S bit of SSP1STAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit clear is clocked in. SSP1IF is set and CKP cleared after the eighth falling edge of SCL.

- 3. Slave clears the SSP1IF.

- Slave can look at the ACKTIM bit of the SSP1CON3 register to <u>determine</u> if the SSP1IF was after or before the ACK.

- 5. Slave reads the address value from SSP1BUF, clearing the BF flag.

- 6. Slave sets ACK value clocked out to the master by setting ACKDT.

- 7. Slave releases the clock by setting CKP.

- 8. SSP1IF is set after an  $\overline{ACK}$ , not after a NACK.

- 9. If SEN = 1 the slave hardware will stretch the clock after the ACK.

- 10. Slave clears SSP1IF.

Note: SSP1IF is still set after the ninth falling edge of SCL even if there is no clock stretching and BF has been cleared. Only if NACK is sent to master is SSP1IF not set

- 11. SSP1IF set and CKP cleared after eighth falling edge of SCL for a received data byte.

- 12. Slave looks at ACKTIM bit of SSP1CON3 to determine the source of the interrupt.

- 13. Slave reads the received data from SSP1BUF clearing BF.

- 14. Steps 7-14 are the same for each received data byte.

- 15. Communication is ended by either the slave sending an ACK = 1, or the master sending a Stop condition. If a Stop is sent and Interrupt on Stop Detect is disabled, the slave will only know by polling the P bit of the SSP1STAT register.

#### 33.4.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXxSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXxSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCxSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCxSTA register enables the EUSART.

#### 33.4.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see **Section 33.4.1.3 "Synchronous Master Transmission")**, except in the case of the Sleep mode.

If two words are written to the TXxREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in the TXxREG register.

- 3. The TXxIF bit will not be set.

- After the first character has been shifted out of TSR, the TXxREG register will transfer the second character to the TSR and the TXxIF bit will now be set.

- 5. If the PEIE and TXxIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 33.4.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- 4. If interrupts are desired, set the TXxIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXxREG register.

| U-0            | U-0                    | U-0               | U-0     | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|----------------|------------------------|-------------------|---------|----------------|------------------|------------------|--------------|

|                | _                      | _                 |         |                | CLKRC            | LK<3:0>          |              |

| bit 7          |                        |                   |         |                |                  |                  | bit (        |

| Legend:        |                        |                   |         |                |                  |                  |              |

| R = Readal     | ble bit                | W = Writable b    | bit     | U = Unimplen   | nented bit, read | d as '0'         |              |

| u = Bit is ur  | nchanged               | x = Bit is unkn   | own     | -n/n = Value a | at POR and BC    | R/Value at all o | other Resets |

| '1' = Bit is s | -                      | '0' = Bit is clea | red     |                |                  |                  |              |

|                |                        |                   |         |                |                  |                  |              |

| bit 7-4        | Unimplem               | ented: Read as '0 | ,       |                |                  |                  |              |

| bit 3-0        | CLKRCLK                | <                 | it bits |                |                  |                  |              |

|                | Clock Sele             | ction             |         |                |                  |                  |              |

|                | 1111 <b>= Re</b>       | served            |         |                |                  |                  |              |

|                | •                      |                   |         |                |                  |                  |              |

|                | •                      |                   |         |                |                  |                  |              |

|                | •                      |                   |         |                |                  |                  |              |

|                | 1011 <b>= Re</b>       |                   |         |                |                  |                  |              |

|                | 1010 = LC<br>1001 = LC |                   |         |                |                  |                  |              |

|                | 1001 = LC<br>1000 = LC |                   |         |                |                  |                  |              |

|                | 0111 = LC              |                   |         |                |                  |                  |              |

|                | 0110 = NC              |                   |         |                |                  |                  |              |

|                | 0101 = SC              |                   |         |                |                  |                  |              |

|                | 0100 <b>= MF</b>       | INTOSC (31.25 kl  | Hz)     |                |                  |                  |              |

|                |                        | INTOSC (500 kHz   |         |                |                  |                  |              |

|                | 0010 = LF              | INTOSC            |         |                |                  |                  |              |

|                | 0001 = HF              |                   |         |                |                  |                  |              |

|                | 0000 <b>= F</b> O      | SC                |         |                |                  |                  |              |

#### TABLE 34-1: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK REFERENCE OUTPUT

| Name     | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3       | Bit 2               | Bit 2 Bit 1 Bit 0 |  | Register<br>on Page |  |

|----------|--------|-------|-------|-------|-------------|---------------------|-------------------|--|---------------------|--|

| CLKRCON  | CLKREN | _     | _     | CLKRD | C<1:0>      | C<1:0> CLKRDIV<2:0> |                   |  |                     |  |

| CLKRCLK  | —      | —     | _     | _     |             | CLKRCLK<3:0>        |                   |  |                     |  |

| CLCxSELy | —      | —     |       |       | LCxDyS<5:0> |                     |                   |  |                     |  |

| RxyPPS   | —      | _     | _     |       | RxyPPS<4:0> |                     |                   |  |                     |  |

|          |        |       |       |       |             |                     |                   |  |                     |  |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the CLKR module.

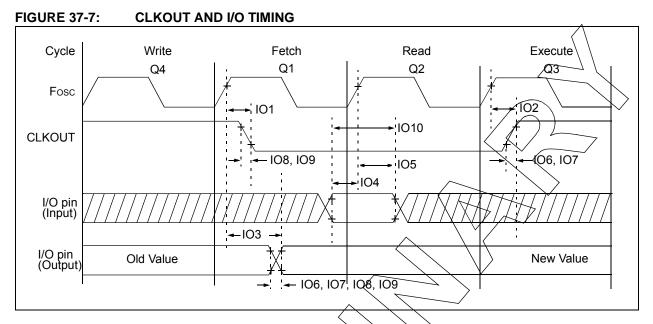

| TABLE 37-10: | I/O AND CLKOUT TIMING SPECIFICATIONS |

|--------------|--------------------------------------|

|--------------|--------------------------------------|

| Param.<br>No. | Sym.                  | Characteristic                                                                     | Min. | Тур† | Max. | Units | Conditions |

|---------------|-----------------------|------------------------------------------------------------------------------------|------|------|------|-------|------------|

| IO1*          | T <sub>CLKOUTH</sub>  | CLKOUT rising edge delay (rising<br>edge Fosc (Q1 cycle) to falling edge<br>CLKOUT | > -  | -    | 70   | ns    |            |

| 102*          | T <sub>CLKOUTL</sub>  | CLKOUT falling edge delay (rising<br>edge Fosc (Q3 cycle) to rising edge<br>CLKOUT | _    | —    | 72   | ns    |            |

| 103*          | T <sub>IO_VALID</sub> | Port output valid time (rising edge<br>Fose (Q1 cycle) to port valid)              | —    | 50   | 70   | ns    |            |

| 104*          | T <sub>IO_SETUP</sub> | Port input setup time (Setup time<br>before rising edge Fosc – Q2 cycle)           | 20   | —    | —    | ns    |            |

| 105*          | T <sub>IO_HOLD</sub>  | Port input hold time (Hold time after rising edge Fosc – Q2 cycle)                 | 50   | —    | —    | ns    |            |

| 106*          | TIOR_SLREN            | Port I/O rise time, slew rate enabled                                              | _    | 25   | —    | ns    | VDD = 3.0V |

| 107*          | TIOR SLADIS           | Port I/O rise time, slew rate disabled                                             | _    | 5    | —    | ns    | VDD = 3.0V |

| 08*           | FIOF SLREN            | Port I/O fall time, slew rate enabled                                              | _    | 25   | —    | ns    | VDD = 3.0V |

| 09*/          |                       | Port I/O fall time, slew rate disabled                                             | —    | 5    | —    | ns    | VDD = 3.0V |

|               | FINT                  | INT pin high or low time to trigger an interrupt                                   | 25   | -    | _    | ns    |            |

| 011*          | T.OC                  | Interrupt-on-Change minimum high or<br>low time to trigger interrupt               | 25   | —    | —    | ns    |            |

| Standard Operating Conditions (unless otherwise st | ate  | db | $\angle$ |

|----------------------------------------------------|------|----|----------|

| Standard Operating Conditions (unless otherwise si | ιαις | u) |          |

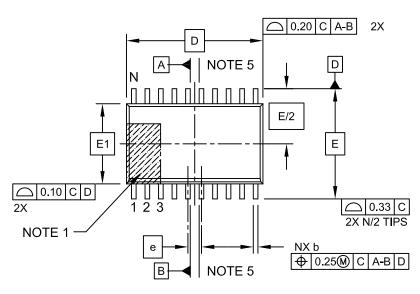

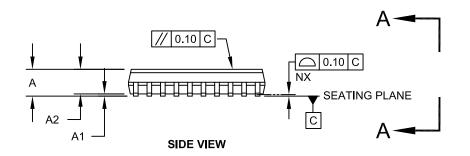

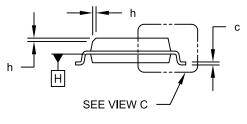

#### 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

VIEW A-A

Microchip Technology Drawing C04-094C Sheet 1 of 2

© 2016 Microchip Technology Inc.

# THE MICROCHIP WEBSITE

Microchip provides online support via our website at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip website at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://www.microchip.com/support

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BeaconThings, BitCloud, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KEELoa, KEELoa logo, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, RightTouch, SAM-BA, SpyNIC, SST, SST Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, CryptoAuthentication, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, QMatrix, RightTouch logo, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2016, Microchip Technology Incorporated, All Rights Reserved. ISBN: 978-1-5224-1220-5