Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

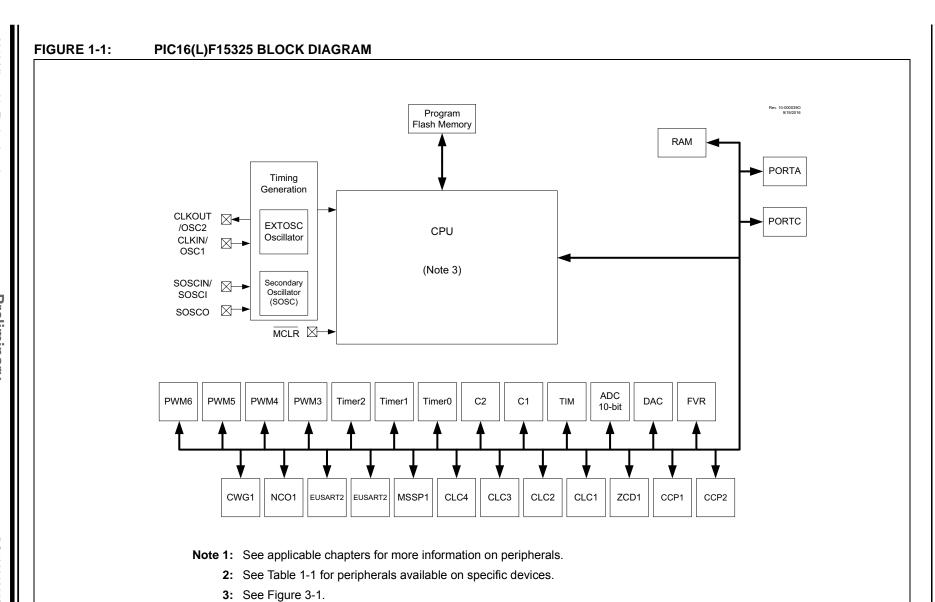

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                            |

| Supplier Device Package    | 14-TSSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15325-e-st |

PIC16(L)F15325/45

TABLE 1-2: PIC16(L)F15325 PINOUT DESCRIPTION (CONTINUED)

| Name                                                                                             | Function              | Input<br>Type | Output Type | Description                                                         |

|--------------------------------------------------------------------------------------------------|-----------------------|---------------|-------------|---------------------------------------------------------------------|

| RC3/ANC3/C1IN3-/C2IN3-/CCP2 <sup>(1)</sup> /<br>SS1 <sup>(1)</sup> /CLCIN0 <sup>(1)</sup> /IOCC3 | RC3                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                                |

| 331 7CLCINO 7IOCC3                                                                               | ANC3                  | AN            | -           | ADC Channel C3 input.                                               |

|                                                                                                  | C1IN3-                | AN            | ı           | Comparator 1 positive input.                                        |

|                                                                                                  | C2IN3-                | AN            | _           | Comparator 2 positive input.                                        |

|                                                                                                  | CCP2 <sup>(1)</sup>   | TTL/ST        | CMOS/OD     | Capture/compare/PWM2 (default input location for capture function). |

|                                                                                                  | SS1 <sup>(1)</sup>    | TTL/ST        | _           | MSSP1 SPI slave select input.                                       |

|                                                                                                  | CLCINO <sup>(1)</sup> | TTL/ST        |             | Configurable Logic Cell source input.                               |

|                                                                                                  | IOCC3                 | TTL/ST        | I           | Interrupt-on-change input.                                          |

| RC4/ANC4/TX1 <sup>(1)</sup> /CK1 <sup>(1)</sup> /CLCIN1 <sup>(1)</sup> /<br>IOCC4                | RC4                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                                |

| 10004                                                                                            | ANC4                  | AN            | _           | ADC Channel C4 input.                                               |

|                                                                                                  | TX1                   |               | CMOS        | EUSART1 asynchronous transmit.                                      |

|                                                                                                  | CLCIN1 <sup>(1)</sup> | TTL/ST        |             | Configurable Logic Cell source input.                               |

|                                                                                                  | CK1 <sup>(1)</sup>    | TTL/ST        | CMOS/OD     | EUSART1 synchronous mode clock input/output.                        |

|                                                                                                  | IOCC4                 | TTL/ST        |             | Interrupt-on-change input.                                          |

| RC5/ANC5/CCP1 <sup>(1)</sup> /RX1 <sup>(1)</sup> /DT1 <sup>(1)</sup> /<br>IOCC5                  | RC5                   | TTL/ST        | CMOS/OD     | General purpose I/O.                                                |

| 10003                                                                                            | ANC5                  | AN            | _           | ADC Channel C5 input.                                               |

|                                                                                                  | CCP1 <sup>(1)</sup>   | TTL/ST        | CMOS/OD     | Capture/compare/PWM1 (default input location for capture function). |

|                                                                                                  | RX1 <sup>(1)</sup>    | TTL/ST        |             | EUSART1 Asynchronous mode receiver data input.                      |

|                                                                                                  | DT1 <sup>(1)</sup>    | TTL/ST        | CMOS/OD     | EUSART1 Synchronous mode data input/output.                         |

|                                                                                                  | IOCC5                 | TTL/ST        |             | Interrupt-on-change input.                                          |

| VDD                                                                                              | Vdd                   | Power         | _           | Positive supply voltage input.                                      |

| Vss                                                                                              | Vss                   | Power         | _           | Ground reference.                                                   |

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 15-3 for details on which PORT pins may be used for this signal.

- 2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 15-3.

- 3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

- 4: These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

## 4.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- · Program Memory

- Configuration Words

- Device ID

- User ID

- Program Flash Memory

- Device Information Area (DIA)

- Device Configuration Information (DCI)

- Revision ID

- · Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

The following features are associated with access and control of program memory and data memory:

- · PCL and PCLATH

- Stack

- · Indirect Addressing

- · NVMREG access

## 4.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing 32K x 14 program memory space. Table 4-1 shows the memory sizes implemented. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 4-1).

## TABLE 4-1: DEVICE SIZES AND ADDRESSES

| Device            | Program Memory Size (Words) | Last Program Memory Address |

|-------------------|-----------------------------|-----------------------------|

| PIC16(L)F15325/45 | 8192                        | 1FFFh                       |

TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address  | Name                                            | Bit 7                  | Bit 6                                        | Bit 5     | Bit 4    | Bit 3  | Bit 2      | Bit 1  | Bit 0 | Value on: | Value on: |  |

|----------|-------------------------------------------------|------------------------|----------------------------------------------|-----------|----------|--------|------------|--------|-------|-----------|-----------|--|

| Addicas  | Name                                            | Dit 7                  | Dit 0                                        | Dit 3     | Dit 4    | Dit 0  | Dit 2      | Dit 1  | Dit 0 | POR, BOR  | MCLR      |  |

| Bank 5   | ank 5                                           |                        |                                              |           |          |        |            |        |       |           |           |  |

|          | CPU CORE REGISTERS; see Table 4-3 for specifics |                        |                                              |           |          |        |            |        |       |           |           |  |

|          | OF C CONE NEGOTERO, COS TUBIO TO TO OF OPPOSITO |                        |                                              |           |          |        |            |        |       |           |           |  |

| 28Ch     | T2TMR                                           | Holding Register for t | lolding Register for the 8-bit TMR2 Register |           |          |        |            |        |       | 0000 0000 | 0000 0000 |  |

| 28Dh     | T2PR                                            | TMR2 Period Registe    | er                                           |           |          |        |            |        |       | 1111 1111 | 1111 1111 |  |

| 28Eh     | T2CON                                           | ON                     |                                              | CKPS<2:0> |          |        | OUTPS<3:0> |        |       | 0000 0000 | 0000 0000 |  |

| 28Fh     | T2HLT                                           | PSYNC                  | CKPOL                                        | CKSYNC    |          |        | MODE<4:0>  |        |       | 0000 0000 | 0000 0000 |  |

| 290h     | T2CLKCON                                        | _                      | _                                            | _         | _        |        | C          | S<3:0> |       | 0000      | 0000      |  |

| 291h     | T2RST                                           | _                      | _                                            | _         | _        |        | RSI        | 0000   | 0000  |           |           |  |

| 292h     |                                                 |                        |                                              |           |          |        |            |        |       |           |           |  |

| <br>29Fh | I                                               |                        |                                              |           | Unimpler | nentea |            |        |       | _         | ı         |  |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

| <b>TABLE 4-10:</b> | SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED) |

|--------------------|----------------------------------------------------------|

|--------------------|----------------------------------------------------------|

| Address           | Name                                            | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |  |

|-------------------|-------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|----------------------------|--|

| Bank 13           | Bank 13                                         |       |       |       |       |       |       |       |       |                       |                            |  |

|                   | CPU CORE REGISTERS; see Table 4-3 for specifics |       |       |       |       |       |       |       |       |                       |                            |  |

| 68Ch<br>—<br>69Fh | — Unimplemented                                 |       |       |       |       |       |       |       | 1     | _                     |                            |  |

PIC16(L)F15325/45

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

## 9.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (ECH, ECM, ECL mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes).

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators and a dedicated Phase Lock Loop (PLL) that are used to generate internal system clock sources. The High-Frequency Internal Oscillator (HFINTOSC) can produce a range from 1 to 32 MHz. The Low-Frequency Internal Oscillator (LFINTOSC) generates a 31 kHz frequency. The external oscillator block can also be used with the PLL. See **Section 9.2.1.4** "4x PLL" for more details.

The system clock can be selected between external or internal clock sources via the NOSC bits in the OSCCON1 register. See **Section 9.3** "Clock **Switching**" for additional information.

#### 9.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the RSTOSC<2:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset

- Write the NOSC<2:0> and NDIV<4:0> bits in the OSCCON1 register to switch the system clock source

See **Section 9.3 "Clock Switching"** for more information.

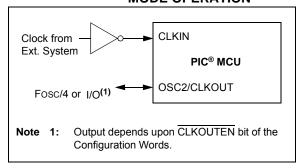

## 9.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 9-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through Configuration Words:

- ECH High power, ≤ 32 MHz

- ECM Medium power, ≤ 8 MHz

- ECL Low power, ≤ 0.5 MHz

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC® MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

FIGURE 9-2: EXTERNAL CLOCK (EC) MODE OPERATION

### 9.2.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 9-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

XT Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive crystals and resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 9-3 and Figure 9-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

# 10.6 Register Definitions: Interrupt Control

## REGISTER 10-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-1/1 |

|---------|---------|-----|-----|-----|-----|-----|---------|

| GIE     | PEIE    | _   | _   | _   | _   | _   | INTEDG  |

| bit 7   |         |     |     |     |     |     | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | <b>GIE:</b> Global Interrupt Enable bit 1 = Enables all active interrupts 0 = Disables all interrupts                                  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | <b>PEIE:</b> Peripheral Interrupt Enable bit<br>1 = Enables all active peripheral interrupts<br>0 = Disables all peripheral interrupts |

| bit 5-1 | Unimplemented: Read as '0'                                                                                                             |

| bit 0   | INTEDG: Interrupt Edge Select bit  1 = Interrupt on rising edge of INT pin  0 = Interrupt on falling edge of INT pin                   |

Note:

| Interrupt flag bits are set when an interrupt |

|-----------------------------------------------|

| condition occurs, regardless of the state of  |

| its corresponding enable bit or the Global    |

| Enable bit, GIE, of the INTCON register.      |

| User software should ensure the               |

| appropriate interrupt flag bits are clear     |

| prior to enabling an interrupt.               |

# 14.4 PORTB Registers (PIC16(L)F15345 only)

#### 14.4.1 DATA REGISTER

PORTB is a 4-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 14-10). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., disable the output driver). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Figure 14-1 shows how to initialize PORTB.

Reading the PORTB register (Register 14-9) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

The PORT data latch LATB (Register 14-11) holds the output port data, and contains the latest value of a LATB or PORTB write.

#### 14.4.2 DIRECTION CONTROL

The TRISB register (Register 14-10) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

### 14.4.3 OPEN-DRAIN CONTROL

The ODCONB register (Register 14-14) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONB bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONB bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

Note:

It is not necessary to set open-drain control when using the pin for  $I^2C$ ; the  $I^2C$  module controls the pin and makes the pin open-drain.

### 14.4.4 SLEW RATE CONTROL

The SLRCONB register (Register 14-15) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONB bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONB bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

#### 14.4.5 INPUT THRESHOLD CONTROL

The INLVLB register (Register 14-8) controls the input voltage threshold for each of the available PORTB input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTB register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 37-4 for more information on threshold levels.

Note:

Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

#### 14.4.6 ANALOG CONTROL

The ANSELB register (Register 14-12) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with its TRIS bit clear and its ANSEL bit set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note:

The ANSELB bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

#### 14.4.7 WEAK PULL-UP CONTROL

The WPUB register (Register 14-5) controls the individual weak pull-ups for each PORT pin.

# 14.4.8 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each PORTB pin is multiplexed with other functions.

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic or by enabling an analog output, such as the DAC. See **Section 15.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

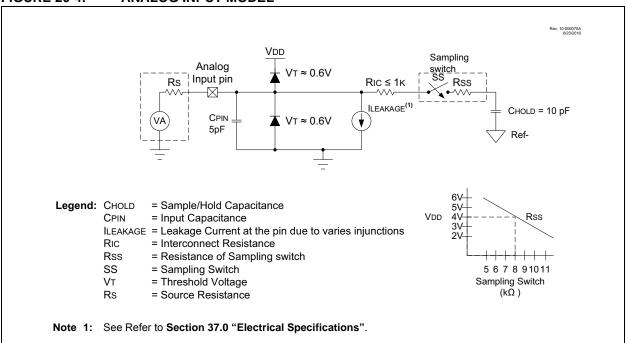

FIGURE 20-4: ANALOG INPUT MODEL

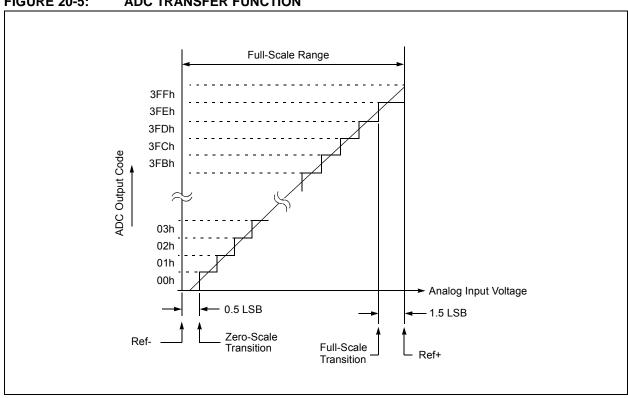

## FIGURE 20-5: ADC TRANSFER FUNCTION

TABLE 21-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC1 MODULE

| Name     | Bit 7  | Bit 6 | Bit 5   | Bit 4   | Bit 3      | Bit 2   | Bit 1 | Bit 0   | Register on page |  |

|----------|--------|-------|---------|---------|------------|---------|-------|---------|------------------|--|

| DAC1CON0 | DAC1EN | _     | DAC10E1 | DAC10E2 | DAC1PS     | SS<1:0> | _     | DAC1NSS | 242              |  |

| DAC1CON1 | _      | _     | _       |         | DAC1R<4:0> |         |       |         |                  |  |

| CM1PSEL  | _      | _     | _       | -       | — PCH<2:0> |         |       |         |                  |  |

| CM2PSEL  | _      | _     | _       | _       | — PCH<2:0> |         |       |         |                  |  |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used with the DAC module.

## REGISTER 23-2: CMxCON1: COMPARATOR Cx CONTROL REGISTER 1

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|-----|-----|---------|---------|

| _     | _   | _   | _   | _   | _   | INTP    | INTN    |

| bit 7 |     |     |     |     |     |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7-2 **Unimplemented:** Read as '0'

bit 1 INTP: Comparator Interrupt on Positive-Going Edge Enable bits

1 = The CxIF interrupt flag will be set upon a positive-going edge of the CxOUT bit

0 = No interrupt flag will be set on a positive-going edge of the CxOUT bit

bit 0 INTN: Comparator Interrupt on Negative-Going Edge Enable bits

1 = The CxIF interrupt flag will be set upon a negative-going edge of the CxOUT bit

0 = No interrupt flag will be set on a negative-going edge of the CxOUT bit

## 26.1 Timer1 Operation

The Timer1 modules are 16-bit incrementing counters which are accessed through the TMR1H:TMR1L register pairs. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

The timer is enabled by configuring the TMR1ON and GE bits in the T1CON and T1GCON registers, respectively. Table 26-1 displays the Timer1 enable selections.

TABLE 26-1: TIMER1 ENABLE SELECTIONS

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 1      | 1      | Count Enabled       |

| 1      | 0      | Always On           |

| 0      | 1      | Off                 |

| 0      | 0      | Off                 |

#### 26.2 Clock Source Selection

The T1CLK register is used to select the clock source for the timer. Register 26-3 shows the possible clock sources that may be selected to make the timer increment.

#### 26.2.1 INTERNAL CLOCK SOURCE

When the internal clock source Fosc is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the respective Timer1 prescaler.

When the Fosc internal clock source is selected, the timer register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the TMR1H:TMR1L value. To utilize the full resolution of the timer in this mode, an asynchronous input signal must be used to gate the timer clock input.

Out of the total timer gate signal sources, the following subset of sources can be asynchronous and may be useful for this purpose:

- · CLC4 output

- · CLC3 output

- · CLC2 output

- · CLC1 output

- · Zero-Cross Detect output

- · Comparator2 output

- Comparator1 output

- · TxG PPS remappable input pin

#### 26.2.2 EXTERNAL CLOCK SOURCE

When the timer is enabled and the external clock input source (ex: T1CKI PPS remappable input) is selected as the clock source, the timer will increment on the rising edge of the external clock input.

When using an external clock source, the timer can be configured to run synchronously or asynchronously, as described in Section 26.5 "Timer Operation in Asynchronous Counter Mode".

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used connected to the SOSCI/SOSCO pins.

Note:

In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- · The timer is first enabled after POR

- Firmware writes to TMR1H or TMR1L

- The timer is disabled

- The timer is re-enabled (e.g., TMR1ON-->1) when the T1CKI signal is currently logic low.

# 27.5.10 LEVEL-TRIGGERED HARDWARE LIMIT ONE-SHOT MODES

The Level-Triggered Hardware Limit One-Shot modes hold the timer in Reset on an external Reset level and start counting when both the ON bit is set and the external signal is not at the Reset level. If one of either the external signal is not in Reset or the ON bit is set then the other signal being set/made active will start the timer. Reset levels are selected as follows:

- Low Reset level (MODE<4:0> = 10110)

- High Reset level (MODE<4:0> = 10111)

When the timer count matches the PRx period count, the timer is reset and the ON bit is cleared. When the ON bit is cleared by either a PRx match or by software control the timer will stay in Reset until both the ON bit is set and the external signal is not at the Reset level.

When Level-Triggered Hardware Limit One-Shot modes are used in conjunction with the CCP PWM operation the PWM drive goes active with either the external signal edge or the setting of the ON bit, whichever of the two starts the timer.

## 30.3 Selectable Input Sources

The CWG generates the output waveforms from the input sources in Table 30-2.

TABLE 30-2: SELECTABLE INPUT SOURCES

| Source Peripheral | Signal Name |

|-------------------|-------------|

| CWG input PPS pin | CWG1IN PPS  |

| CCP1              | CCP1_out    |

| CCP2              | CCP2_out    |

| PWM3              | PWM3_out    |

| PWM4              | PWM4_out    |

| PWM5              | PWM5_out    |

| PWM6              | PWM6_out    |

| NCO               | NCO1_out    |

| Comparator C1     | C1OUT_sync  |

| Comparator C2     | C2OUT_sync  |

| CLC1              | LC1_out     |

| CLC2              | LC2_out     |

| CLC3              | LC3_out     |

| CLC4              | LC4_out     |

The input sources are selected using the CWG1ISM register.

## **30.4 Output Control**

#### 30.4.1 POLARITY CONTROL

The polarity of each CWG output can be selected independently. When the output polarity bit is set, the corresponding output is active-high. Clearing the output polarity bit configures the corresponding output as active-low. However, polarity does not affect the override levels. Output polarity is selected with the POLx bits of the CWG1CON1. Auto-shutdown and steering options are unaffected by polarity.

## 30.13 Register Definitions: CWG Control

Long bit name prefixes for the CWG peripherals are shown in Section 1.1 "Register and Bit Naming Conventions".

#### REGISTER 30-1: CWG1CON0: CWG1 CONTROL REGISTER 0

| R/W-0/0 | R/W/HC-0/0        | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0   | R/W-0/0 |

|---------|-------------------|-----|-----|-----|---------|-----------|---------|

| EN      | LD <sup>(1)</sup> |     | _   | _   |         | MODE<2:0> |         |

| bit 7   |                   |     |     |     | •       |           | bit 0   |

Legend: HC = Bit is cleared by hardware HS = Bit is set by hardware R = Readable bit U = Unimplemented bit, read as '0' W = Writable bit -n/n = Value at POR and BOR/Value at all other Resets u = Bit is unchanged x = Bit is unknown'1' = Bit is set '0' = Bit is cleared q = Value depends on condition

bit 7 EN: CWG1 Enable bit 1 = Module is enabled 0 = Module is disabled LD: CWG1 Load Buffer bits(1) bit 6 1 = Buffers to be loaded on the next rising/falling event

0 = Buffers not loaded

bit 5-3 Unimplemented: Read as '0' bit 2-0 MODE<2:0>: CWG1 Mode bits

111 = Reserved 110 = Reserved

101 = CWG outputs operate in Push-Pull mode 100 = CWG outputs operate in Half-Bridge mode

011 = CWG outputs operate in Reverse Full-Bridge mode 010 = CWG outputs operate in Forward Full-Bridge mode 001 = CWG outputs operate in Synchronous Steering mode

000 = CWG outputs operate in Steering mode

**Note 1:** This bit can only be set after EN = 1 and cannot be set in the same instruction that EN is set.

**Preliminary** © 2016 Microchip Technology Inc. DS40001865B-page 350

# 31.7 Register Definitions: CLC Control

## REGISTER 31-1: CLCxCON: CONFIGURABLE LOGIC CELL CONTROL REGISTER

| R/W-0/0 | U-0 | R-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0      | R/W-0/0 |

|---------|-----|--------|---------|---------|---------|--------------|---------|

| LCxEN   | _   | LCxOUT | LCxINTP | LCxINTN | L       | .CxMODE<2:0> | •       |

| bit 7   |     |        |         |         |         |              | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | LCxEN: Configurable Logic Cell Enable bit                                                                                                                   |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul><li>1 = Configurable logic cell is enabled and mixing input signals</li><li>0 = Configurable logic cell is disabled and has logic zero output</li></ul> |

| bit 6   | Unimplemented: Read as '0'                                                                                                                                  |

| bit 5   | LCxOUT: Configurable Logic Cell Data Output bit                                                                                                             |

|         | Read-only: logic cell output data, after LCPOL; sampled from CLCxOUT                                                                                        |

| bit 4   | LCxINTP: Configurable Logic Cell Positive Edge Going Interrupt Enable bit                                                                                   |

|         | <ul><li>1 = CLCxIF will be set when a rising edge occurs on CLCxOUT</li><li>0 = CLCxIF will not be set</li></ul>                                            |

| bit 3   | LCxINTN: Configurable Logic Cell Negative Edge Going Interrupt Enable bit                                                                                   |

|         | <ul><li>1 = CLCxIF will be set when a falling edge occurs on CLCxOUT</li><li>0 = CLCxIF will not be set</li></ul>                                           |

| bit 2-0 | LCxMODE<2:0>: Configurable Logic Cell Functional Mode bits                                                                                                  |

|         | 111 = Cell is 1-input transparent latch with S and R                                                                                                        |

|         | 110 = Cell is J-K flip-flop with R                                                                                                                          |

|         | 101 = Cell is 2-input D flip-flop with R                                                                                                                    |

|         | 100 = Cell is 1-input D flip-flop with S and R                                                                                                              |

|         | 011 = Cell is S-R latch                                                                                                                                     |

|         | 010 = Cell is 4-input AND                                                                                                                                   |

|         | 001 = Cell is OR-XOR                                                                                                                                        |

|         | 000 = Cell is AND-OR                                                                                                                                        |

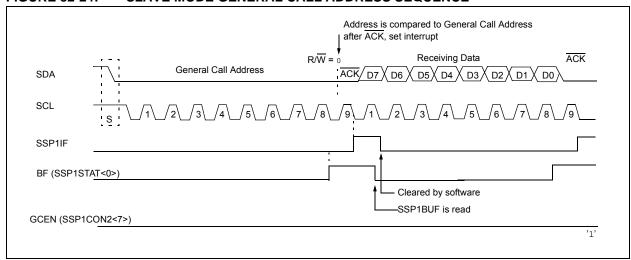

#### 32.5.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the I<sup>2</sup>C bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the  $I^2C$  protocol, defined as address  $0 \times 0.0$ . When the GCEN bit of the SSP1CON2 register is set, the slave module will automatically ACK the reception of this address regardless of the value stored in SSP1ADD. After the slave clocks in an address of all zeros with the R/W bit clear, an interrupt is generated and slave software can read SSP1BUF and respond. Figure 32-24 shows a general call reception sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode.

If the AHEN bit of the SSP1CON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the eighth falling edge of SCL. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

#### 32.5.9 SSP MASK REGISTER

An SSP Mask (SSP1MSK) register (Register 32-5) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSP1SR register during an address comparison operation. A zero ('0') bit in the SSP1MSK register has the effect of making the corresponding bit of the received address a "don't care".

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP operation until written with a mask value.

The SSP Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0>

only. The SSP mask has no effect during the

reception of the first (high) byte of the address.

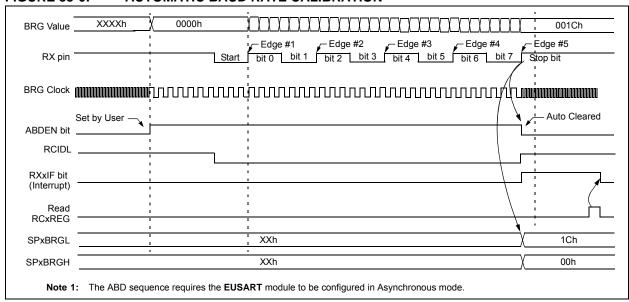

#### 33.3.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDxCON register starts the auto-baud calibration sequence. While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPxBRG begins counting up using the BRG counter clock as shown in Figure 33-6. The fifth rising edge will occur on the RX pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPxBRGH, SPxBRGL register pair, the ABDEN bit is automatically cleared and the RXxIF interrupt flag is set. The value in the RCxREG needs to be read to clear the RXxIF interrupt. RCxREG content should be discarded. When calibrating for modes that do not use the SPxBRGH register the user can verify that the SPxBRGL register did not overflow by checking for 00h in the SPxBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 33-1. During ABD, both the SPxBRGH and SPxBRGL registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPxBRGH and SPxBRGL registers are clocked at

1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte following the Break character (see Section 33.3.3 "Auto-Wake-up on Break").

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the auto-baud counter starts counting at one. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPxBRGH:SPxBRGL register pair.

TABLE 33-1: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

Note: During the ABD sequence, SPxBRGL and SPxBRGH registers are both used as a 16-bit counter, independent of the BRG16 setting.

FIGURE 33-6: AUTOMATIC BAUD RATE CALIBRATION

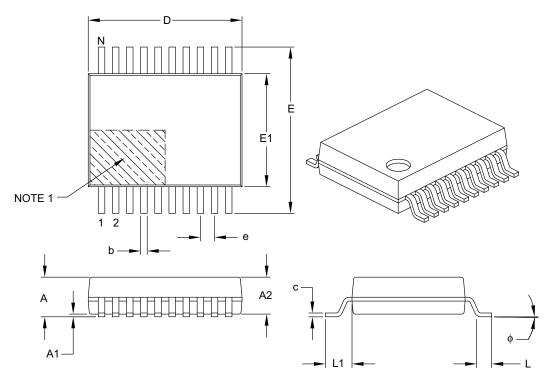

## 20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |      | MILLIMETERS | 3    |  |  |

|--------------------------|------------------|------|-------------|------|--|--|

| Dime                     | Dimension Limits |      |             | MAX  |  |  |

| Number of Pins           | N                | 20   |             |      |  |  |

| Pitch                    | е                |      | 0.65 BSC    |      |  |  |

| Overall Height           | Α                | _    | _           | 2.00 |  |  |

| Molded Package Thickness | A2               | 1.65 | 1.75        | 1.85 |  |  |

| Standoff                 | A1               | 0.05 | _           | _    |  |  |

| Overall Width            | Е                | 7.40 | 7.80        | 8.20 |  |  |

| Molded Package Width     |                  | 5.00 | 5.30        | 5.60 |  |  |

| Overall Length           | D                | 6.90 | 7.20        | 7.50 |  |  |

| Foot Length              | L                | 0.55 | 0.75        | 0.95 |  |  |

| Footprint                | Footprint L1     |      | 1.25 REF    |      |  |  |

| Lead Thickness c         |                  | 0.09 | _           | 0.25 |  |  |

| Foot Angle               |                  | 0°   | 4°          | 8°   |  |  |

| Lead Width b             |                  | 0.22 | _           | 0.38 |  |  |

## Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-072B

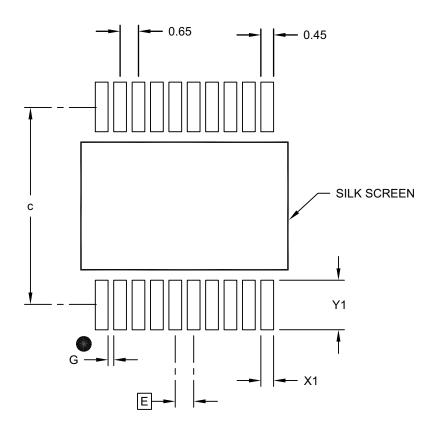

## 20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                          | MILLIMETERS      |          |      |      |

|--------------------------|------------------|----------|------|------|

| Dimensior                | Dimension Limits |          | NOM  | MAX  |

| Contact Pitch            | Е                | 0.65 BSC |      |      |

| Contact Pad Spacing C    |                  |          | 7.20 |      |

| Contact Pad Width (X20)  | X1               |          |      | 0.45 |

| Contact Pad Length (X20) | Y1               |          |      | 1.75 |

| Distance Between Pads    | G                | 0.20     |      |      |

## Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2072B