#### Microchip Technology - PIC16F15325-I/P Datasheet

# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 14-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15325-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

The PIC16(L)F15325/45 are described within this data sheet. The PIC16(L)F15325/45 devices are available in 14/20-pin PDIP, SSOP, SOIC, TSSOP, and UQFN packages. Figure 1-1 and Figure 1-2 shows the block diagrams of the PIC16(L)F15325/45 devices. Table 1-2 and Table 1-3 shows the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

#### TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| JUNIMARI                                                                      |               |                   |

|-------------------------------------------------------------------------------|---------------|-------------------|

| Peripheral                                                                    |               | PIC16(L)F15325/45 |

| Analog-to-Digital Converter                                                   |               | ٠                 |

| Digital-to-Analog Converter (DAC1)                                            |               | ٠                 |

| Fixed Voltage Reference (FVR)                                                 |               | ٠                 |

| Enhanced Universal Synchronous/Asynchron<br>Transmitter (EUSART1 and EUSART2) | ous Receiver/ | •                 |

| Numerically Controlled Oscillator (NCO1)                                      |               | ٠                 |

| Temperature Indicator Module (TIM)                                            |               | ٠                 |

| Zero-Cross Detect (ZCD1)                                                      |               | ٠                 |

| Capture/Compare/PWM Modules (CCP)                                             |               |                   |

|                                                                               | CCP1          | ٠                 |

|                                                                               | CCP2          | ٠                 |

| Comparator Module (Cx)                                                        |               |                   |

|                                                                               | C1            | ٠                 |

|                                                                               | C2            | ٠                 |

| Configurable Logic Cell (CLC)                                                 | -             |                   |

|                                                                               | CLC1          | ٠                 |

|                                                                               | CLC2          | ٠                 |

|                                                                               | CLC3          | ٠                 |

|                                                                               | CLC4          | ٠                 |

| Complementary Waveform Generator (CWG)                                        |               |                   |

|                                                                               | CWG1          | ٠                 |

| Master Synchronous Serial Ports (MSSP)                                        |               |                   |

|                                                                               | MSSP1         | ٠                 |

| Pulse-Width Modulator (PWM)                                                   |               |                   |

|                                                                               | PWM3          | ٠                 |

|                                                                               | PWM4          | ٠                 |

|                                                                               | PWM5          | ٠                 |

|                                                                               | PWM6          | ٠                 |

| Timers                                                                        |               |                   |

|                                                                               | Timer0        | •                 |

|                                                                               | Timer1        | ٠                 |

|                                                                               | Timer2        | ٠                 |

|          | ABLE 4-10. SPECIAL FUNCTION REGISTER SUMMART BAINES 0-03 (CONTINUED) |                                                                                                         |                     |                   |               |                   |           |       |       |           |                            |  |  |

|----------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------|-------------------|---------------|-------------------|-----------|-------|-------|-----------|----------------------------|--|--|

| Address  | Name                                                                 | Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0 |                     |                   |               |                   |           |       |       |           | V <u>alue o</u> n:<br>MCLR |  |  |

| Bank 3   |                                                                      |                                                                                                         |                     |                   |               |                   |           |       |       |           |                            |  |  |

|          |                                                                      |                                                                                                         |                     | CPU COF           | RE REGISTERS; | see Table 4-3 for | specifics |       |       |           |                            |  |  |

| 18Ch     | SSP1BUF                                                              | Synchronous Serial Po                                                                                   | ort Receive Buffer/ | Transmit Register |               |                   |           |       |       | xxxx xxxx | xxxx xxxx                  |  |  |

| 18Dh     | SSP1ADD                                                              |                                                                                                         |                     |                   | ADD<          | 7:0>              |           |       |       | 0000 0000 | 0000 0000                  |  |  |

| 18Eh     | SSP1MSK                                                              |                                                                                                         |                     |                   | MSK<          | 7:0>              |           |       |       | 1111 1111 | 1111 1111                  |  |  |

| 18Fh     | SSP1STAT                                                             | SMP                                                                                                     | CKE                 | D/Ā               | Р             | S                 | R/W       | UA    | BF    | 0000 0000 | 0000 0000                  |  |  |

| 190h     | SSP1CON1                                                             | WCOL                                                                                                    | SSPOV               | SSPEN             | CKP           | SSPM3             | SSPM2     | SSPM1 | SSPM0 | 0000 0000 | 0000 0000                  |  |  |

| 191h     | SSP1CON2                                                             | GCEN                                                                                                    | ACKSTAT             | ACKDT             | ACKEN         | RCEN              | PEN       | RSEN  | SEN   | 0000 0000 | 0000 0000                  |  |  |

| 192h     | SSP1CON3                                                             | ACKTIM                                                                                                  | PCIE                | SCIE              | BOEN          | SDAHT             | SBCDE     | AHEN  | DHEN  | 0000 0000 | 0000 0000                  |  |  |

| 193h<br> | _                                                                    | Unimplemented                                                                                           |                     |                   |               |                   |           |       |       | _         | _                          |  |  |

#### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

|         | ABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED) |       |       |       |          |        |       |          |        |                       |                            |  |  |

|---------|---------------------------------------------------------------------|-------|-------|-------|----------|--------|-------|----------|--------|-----------------------|----------------------------|--|--|

| Address | Name                                                                | Bit 7 | Bit 6 | Bit 5 | Bit 4    | Bit 3  | Bit 2 | Bit 1    | Bit 0  | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |  |  |

| Bank 19 | iank 19                                                             |       |       |       |          |        |       |          |        |                       |                            |  |  |

|         | CPU CORE REGISTERS; see Table 4-3 for specifics                     |       |       |       |          |        |       |          |        |                       |                            |  |  |

| 98Ch    | _                                                                   |       |       |       | Unimpler | mented |       |          |        | —                     | —                          |  |  |

| 98Dh    | 98Dh — Unimplemented                                                |       |       |       |          |        |       |          |        | —                     | _                          |  |  |

| 98Eh    | ih — Unimplemented                                                  |       |       |       |          |        |       |          |        | —                     | —                          |  |  |

| 98Fh    | CMOUT                                                               | —     | _     | —     | —        | —      | —     | MC2OUT   | MC1OUT | 00                    | 00                         |  |  |

| 990h    | CM1CON0                                                             | EN    | OUT   | —     | POL      | —      | —     | HYS      | SYNC   | 00-000                | 00-000                     |  |  |

| 991h    | CM1CON1                                                             | —     | _     | —     | —        | —      | —     | INTP     | INTN   | 00                    | 00                         |  |  |

| 992h    | CM1NCH                                                              | —     | _     | —     | —        | —      |       | NCH<2:0> |        | 000                   | 000                        |  |  |

| 993h    | CM1PCH                                                              | —     | _     | —     | —        | —      |       | PCH<2:0> |        | 000                   | 000                        |  |  |

| 994h    | CM2CON0                                                             | EN    | OUT   | —     | POL      | —      | —     | HYS      | SYNC   | 00-000                | 00-000                     |  |  |

| 995h    | CM2CON1                                                             | _     | _     | —     | —        | _      | —     | INTP     | INTN   | 00                    | 00                         |  |  |

| 996h    | CM2NCH                                                              | —     | _     | —     | _        | —      |       | NCH<2:0> |        | 000                   | 000                        |  |  |

| 997h    | CM2PCH                                                              | —     | _     | —     | _        | _      |       | PCH<2:0> |        | 000                   | 000                        |  |  |

| 998h    |                                                                     |       |       |       |          |        |       |          | _      | _                     |                            |  |  |

#### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

| TABLE 4            |                        | AL FUNCTION REGISTER SUMMART BANKS 0-03 (CONTINUED) |                        |         |         |         |         |         |         |                       |                            |

|--------------------|------------------------|-----------------------------------------------------|------------------------|---------|---------|---------|---------|---------|---------|-----------------------|----------------------------|

| Address            | Name                   | Bit 7                                               | Bit 6                  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

| Bank 62 (C         | Continued)             |                                                     |                        |         |         |         |         |         |         |                       |                            |

| 1F38h              | ANSELA                 | —                                                   | _                      | ANSA5   | ANSA4   | —       | ANSA2   | ANSA1   | ANSA0   | 11 1111               | 11 1111                    |

| 1F39h              | WPUA                   | _                                                   | —                      | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 00 0000               | 00 0000                    |

| 1F3Ah              | ODCONA                 | _                                                   | —                      | ODCA5   | ODCA4   | _       | ODCA2   | ODCA1   | ODCA0   | 00 0000               | 00 0000                    |

| 1F3Bh              | SLRCONA                | _                                                   | —                      | SLRA5   | SLRA4   | _       | SLRA2   | SLRA1   | SLRA0   | 11 1111               | 11 1111                    |

| 1F3Ch              | INLVLA                 | _                                                   | —                      | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 11 1111               | 11 1111                    |

| 1F3Dh              | IOCAP                  | _                                                   | —                      | IOCAP5  | IOCAP4  | IOCAP3  | IOCAP2  | IOCAP1  | IOCAP0  | 00 0000               | 00 0000                    |

| 1F3Eh              | IOCAN                  | _                                                   | —                      | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  | 00 0000               | 00 0000                    |

| 1F3Fh              | IOCAF                  | _                                                   | _                      | IOCAF5  | IOCAF4  | IOCAF3  | IOCAF2  | IOCAF1  | IOCAF0  | 00 0000               | 00 0000                    |

| 1F40h              | _                      |                                                     |                        |         | Unimple | mented  |         | •       |         | _                     | —                          |

| 1F41h              | _                      |                                                     |                        |         | Unimple | mented  |         |         |         | _                     | _                          |

| 1F42h              | _                      |                                                     |                        |         | Unimple | mented  |         |         |         | _                     | —                          |

| 1F43h              | ANSELB <sup>(1)</sup>  | ANSB7                                               | ANSB6                  | ANSB5   | ANSB4   | _       | _       | —       | _       | 1 1111                | 1 1111                     |

| 1F44h              | WPUB <sup>(1)</sup>    | WPUB7                                               | WPUB6                  | WPUB5   | WPUB4   | _       | _       | _       | _       | 0 0000                | 0 0000                     |

| 1F45h              | ODCONB <sup>(1)</sup>  | ODCB7                                               | ODCB6                  | ODCB5   | ODCB4   | _       | _       | _       | _       | 0 0000                | 0 0000                     |

| 1F46h              | SLRCONB <sup>(1)</sup> | SLRB7                                               | SLRB6                  | SLRB5   | SLRB4   | _       | _       | _       | _       | 1 1111                | 1 1111                     |

| 1F47h              | INLVLB <sup>(1)</sup>  | INLVLB7                                             | INLVLB6                | INLVLB5 | INLVLB4 | _       | _       | _       | _       | 1 1111                | 1 1111                     |

| 1F48h              | IOCBP <sup>(1)</sup>   | IOCBP7                                              | IOCBP6                 | IOCBP5  | IOCBP4  | _       | _       | _       | _       | 0 0000                | 0 0000                     |

| 1F49h              | IOCBN <sup>(1)</sup>   | IOCBN7                                              | IOCBN6                 | IOCBN5  | IOCBN4  | _       | _       | _       | _       | 0 0000                | 0 0000                     |

| 1F4Ah              | IOCBF <sup>(1)</sup>   | IOCBF7                                              | IOCBF6                 | IOCBF5  | IOCBF4  | _       | —       | _       | _       | 0 0000                | 0 0000                     |

| 1F4Bh              | _                      |                                                     |                        |         | Unimple | mented  |         |         |         | _                     | _                          |

| 1F4Ch              | _                      |                                                     |                        |         | Unimple | mented  |         |         |         | _                     | _                          |

| 1F4Dh              | _                      |                                                     |                        |         | Unimple | mented  |         |         |         | _                     | _                          |

| 1F4Eh              | ANSELC                 | ANSC7 <sup>(1)</sup>                                | ANSC6 <sup>(1)</sup>   | ANSC5   | ANSC4   | ANSC3   | ANSC2   | ANSC1   | ANSC0   | 1111 1111             | 1111 1111                  |

| 1F4Fh              | WPUC                   | WPUC7 <sup>(1)</sup>                                | WPUC6 <sup>(1)</sup>   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   | 0000 0000             | 0000 0000                  |

| 1F50h              | ODCONC                 | ODCC7 <sup>(1)</sup>                                | ODCC6 <sup>(1)</sup>   | ODCC5   | ODCC4   | ODCC3   | ODCC2   | ODCC1   | ODCC0   | 0000 0000             | 0000 0000                  |

| 1F51h              | SLRCONC                | SLRC7 <sup>(1)</sup>                                | SLRC6 <sup>(1)</sup>   | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   | 1111 1111             | 1111 1111                  |

| 1F52h              | INLVLC                 | INLVLC7 <sup>(1)</sup>                              | INLVLC6 <sup>(1)</sup> | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 | 1111 1111             | 1111 1111                  |

| 1F53h              | IOCCP                  | IOCCP7 <sup>(1)</sup>                               | IOCCP6 <sup>(1)</sup>  | IOCCP5  | IOCCP4  | IOCCP3  | IOCCP2  | IOCCP1  | IOCCP0  | 0000 0000             | 0000 0000                  |

| 1F54h              | IOCCN                  | IOCCN7 <sup>(1)</sup>                               | IOCCN6 <sup>(1)</sup>  | IOCCN5  | IOCCN4  | IOCCN3  | IOCCN2  | IOCCN1  | IOCCN0  | 0000 0000             | 0000 0000                  |

| 1F55h              | IOCCF                  | IOCCF7 <sup>(1)</sup>                               | IOCCF6 <sup>(1)</sup>  | IOCCF5  | IOCCF4  | IOCCF3  | IOCCF2  | IOCCF1  | IOCCF0  | 0000 0000             | 0000 0000                  |

| 1F56h<br><br>1F6Fh | _                      |                                                     |                        |         |         |         |         |         |         |                       | _                          |

#### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

PIC16(L)F15325/45

Legend:

Note 1:

Present only in PIC16(L)F15345.

#### 6.1 Microchip Unique identifier (MUI)

The PIC16(L)F15325/45 devices are individually encoded during final manufacturing with a Microchip Unique Identifier, or MUI. The MUI cannot be erased by a Bulk Erase command or any other user-accessible means. This feature allows for manufacturing traceability of Microchip Technology devices in applications where this is a required. It may also be used by the application manufacturer for a number of functions that require unverified unique identification, such as:

- Tracking the device

- Unique serial number

The MUI consists of nine program words. When taken together, these fields form a unique identifier. The MUI is stored in nine read-only locations, located between 8100h to 8109h in the DIA space. Table 6-1 lists the addresses of the identifier words.

| Note: | For applications that require verified unique |

|-------|-----------------------------------------------|

|       | identification, contact your Microchip Tech-  |

|       | nology sales office to create a Serialized    |

|       | Quick Turn Programming option.                |

#### 6.2 External Unique Identifier (EUI)

The EUI data is stored at locations 810Ah to 8111h in the program memory region. This region is an optional space for placing application specific information. The data is coded per customer requirements during manufacturing. The EUI cannot be erased by a Bulk Erase command.

Note: Data is stored in this address range on receiving a request from the customer. The customer may contact the local sales representative or Field Applications Engineer, and provide them the unique identifier information that is required to be stored in this region.

### 6.3 Analog-to-Digital Conversion Data of the Temperature Sensor

The purpose of the temperature indicator module is to provide a temperature-dependent voltage that can be measured by an analog module. **Section 19.0 "Temperature Indicator Module**" explains the operation of the Temperature Indicator module and defines terms such as the low range and high range settings of the sensor.

The DIA table contains the internal ADC measurement values of the temperature sensor for low and high range at fixed points of reference. The values are measured during test and are unique to each device. The right-justified ADC readings are stored in the DIA memory region. The calibration data can be used to plot the approximate sensor output voltage, VTSENSE vs. Temperature curve.

- **TSLR<3:1>**: Address 8112h to 8114h store the measurements for the low range setting of the temperature sensor at VDD = 3V.

- TSHR<3:1>: Address 8115h to 8117h store the measurements for the high range setting of the temperature sensor at VDD = 3V.

The stored measurements are made by the device ADC using the internal VREF = 2.048V.

#### 6.4 Fixed Voltage Reference Data

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- ADC input channel

- ADC positive reference

- Comparator positive input

- Digital-to-Analog Converter

For more information on the FVR, refer to **Section 18.0 "Fixed Voltage Reference (FVR)"**.

The DIA stores measured FVR voltages for this device in mV for the different buffer settings of 1x, 2x or 4x at program memory locations 8118h to 811Dh.

- FVRA1X stores the value of ADC FVR1 Output voltage for 1x setting (in mV)

- FVRA2X stores the value of ADC FVR1 Output Voltage for 2x setting (in mV)

- FVRA4X stores the value of ADC FVR1 Output Voltage for 4x setting (in mV)

- FVRC1X stores the value of Comparator FVR2 output voltage for 1x setting (in mV)

- FVRC2X stores the value of Comparator FVR2 output voltage for 2x setting (in mV)

- FVRC4X stores the value of Comparator FVR2 output voltage for 4x setting (in mV)

| R/W/HS-0/0       | R/W/HS-0/0                        | R/W/HS-0/0                                       | R/W/HS-0/0                        | U-0                             | U-0               | R/W/HS-0/0                                                | R/W/HS-0/0     |

|------------------|-----------------------------------|--------------------------------------------------|-----------------------------------|---------------------------------|-------------------|-----------------------------------------------------------|----------------|

| RC2IF            | TX2IF                             | RC1IF                                            | TX1IF                             | —                               | _                 | BCL1IF                                                    | SSP1IF         |

| bit 7            |                                   |                                                  |                                   |                                 |                   |                                                           | bit C          |

|                  |                                   |                                                  |                                   |                                 |                   |                                                           |                |

| Legend:          |                                   |                                                  |                                   |                                 |                   |                                                           |                |

| R = Readable     | bit                               | W = Writable                                     | bit                               | U = Unimpler                    | mented bit, rea   | ad as '0'                                                 |                |

| u = Bit is uncha | anged                             | x = Bit is unkr                                  | nown                              | -n/n = Value a                  | at POR and B      | OR/Value at all c                                         | other Resets   |

| '1' = Bit is set |                                   | '0' = Bit is clea                                | ared                              | HS = Hardwa                     | re clearable      |                                                           |                |

| bit 7            | RC2IF: EUSA                       | ART2 Receive I                                   | nterrupt Flag (                   | (Read-Only) b                   | (1)               |                                                           |                |

|                  | 1 = The EUS                       | ART2 receive<br>ART2 receive                     | buffer is not er                  | npty (contains                  |                   | oyte)                                                     |                |

| bit 6            |                                   | RT2 Transmit I                                   |                                   |                                 | it(2)             |                                                           |                |

|                  | 1 = The EUS                       | ART2 transmit                                    | buffer contain                    | s at least one                  | unoccupied s      | pace<br>firmware shoul                                    | d not write to |

| bit 5            | RC1IF: EUSA                       | RT1 Receive I                                    | nterrupt Flag (                   | (read-only) bit                 | (1)               |                                                           |                |

|                  | 1 = The EUS                       | ART1 receive  <br>ART1 receive                   | buffer is not er                  | mpty (contains                  |                   | oyte)                                                     |                |

| bit 4            | TX1IF: EUSA                       | RT1 Transmit I                                   | Interrupt Flag                    | (read-only) bit                 | (2)               |                                                           |                |

|                  | 0 = The EUS                       | SART1 transmi<br>SART1 transm<br>again, until mo | it buffer is cu                   | rrently full. Th                | ne application    | firmware shoul                                            | d not write to |

| bit 3-2          | Unimplemen                        | ted: Read as '                                   | כ'                                |                                 |                   |                                                           |                |

| bit 1            | BCL1IF: MSS                       | SP1 Bus Collisi                                  | on Interrupt FI                   | ag bit                          |                   |                                                           |                |

|                  |                                   | llision was dete<br>ollision was de              |                                   | cleared in sof                  | ťware)            |                                                           |                |

| bit 0            | SSP1IF: Sync                      | chronous Seria                                   | I Port (MSSP1                     | ) Interrupt Fla                 | g bit             |                                                           |                |

|                  |                                   | smission/Rece<br>or the Transmis                 |                                   |                                 |                   | cleared in softwa                                         | are)           |

|                  | RCxIF flag is a<br>s to remove al |                                                  |                                   | 0,                              | firmware mus      | t read from RCx                                           | REG enough     |

| 2: The the       | TXxIF flag is a                   | a read-only bit,<br>write enough d               | indicating if th<br>lata to TXxRE | ere is room in<br>G to complete | y fill all availa | uffer. To clear the<br>ble bytes in the b<br>re instead). |                |

|                  | rrupt flag bits a                 | re set when an                                   |                                   |                                 |                   |                                                           |                |

| Note: | Interrupt flag bits are set when an interrupt |  |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | condition occurs, regardless of the state of  |  |  |  |  |  |  |  |  |  |

|       | its corresponding enable bit or the Global    |  |  |  |  |  |  |  |  |  |

|       | Enable bit, GIE, of the INTCON register.      |  |  |  |  |  |  |  |  |  |

|       | User software should ensure the               |  |  |  |  |  |  |  |  |  |

|       | appropriate interrupt flag bits are clear     |  |  |  |  |  |  |  |  |  |

|       | prior to enabling an interrupt.               |  |  |  |  |  |  |  |  |  |

| R/W/HS-0/0       | R/W/HS-0/0                                                                                                                                         | R/W/HS-0/0        | R/W/HS-0/0      | U-0            | U-0              | U-0            | R/W/HS-0/0   |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|----------------|------------------|----------------|--------------|--|--|--|

| CLC4IF           | CLC3IF                                                                                                                                             | CLC2IF            | CLC1IF          | _              | _                | _              | TMR1GIF      |  |  |  |

| bit 7            | ·                                                                                                                                                  |                   |                 |                |                  |                | bit 0        |  |  |  |

|                  |                                                                                                                                                    |                   |                 |                |                  |                |              |  |  |  |

| Legend:          |                                                                                                                                                    |                   |                 |                |                  |                |              |  |  |  |

| R = Readable     | bit                                                                                                                                                | W = Writable      | bit             | U = Unimpler   | nented bit, read | as '0'         |              |  |  |  |

| u = Bit is uncha | anged                                                                                                                                              | x = Bit is unkr   | iown            | -n/n = Value a | at POR and BOI   | R/Value at all | other Resets |  |  |  |

| '1' = Bit is set |                                                                                                                                                    | '0' = Bit is clea | ared            | HS = Hardwa    | are set          |                |              |  |  |  |

|                  |                                                                                                                                                    |                   |                 |                |                  |                |              |  |  |  |

| bit 7            |                                                                                                                                                    | 4 Interrupt Flag  | -               |                |                  |                |              |  |  |  |

|                  | 1 = A CLC4OUT interrupt condition has occurred (must be cleared in software)                                                                       |                   |                 |                |                  |                |              |  |  |  |

|                  | 0 = No CLC4 interrupt event has occurred                                                                                                           |                   |                 |                |                  |                |              |  |  |  |

| bit 6            | CLC3IF: CLC3 Interrupt Flag bit                                                                                                                    |                   |                 |                |                  |                |              |  |  |  |

|                  | <ul> <li>1 = A CLC3OUT interrupt condition has occurred (must be cleared in software)</li> <li>0 = No CLC3 interrupt event has occurred</li> </ul> |                   |                 |                |                  |                |              |  |  |  |

| bit 5            |                                                                                                                                                    | 2 Interrupt Flag  |                 |                |                  |                |              |  |  |  |

| Sit 0            | 1 = A CLC2OUT interrupt condition has occurred (must be cleared in software)                                                                       |                   |                 |                |                  |                |              |  |  |  |

|                  | 0 = No CLC2 interrupt event has occurred                                                                                                           |                   |                 |                |                  |                |              |  |  |  |

| bit 4            | CLC1IF: CLC                                                                                                                                        | 1 Interrupt Flag  | g bit           |                |                  |                |              |  |  |  |

|                  | 1 = A CLC1OUT interrupt condition has occurred (must be cleared in software)                                                                       |                   |                 |                |                  |                |              |  |  |  |

|                  | 0 = No CLC1 interrupt event has occurred                                                                                                           |                   |                 |                |                  |                |              |  |  |  |

| bit 3-1          | Unimplemen                                                                                                                                         | ted: Read as '    | o'              |                |                  |                |              |  |  |  |

| bit 0            | TMR1GIF: Tir                                                                                                                                       | mer1 Gate Inte    | rrupt Flag bit  |                |                  |                |              |  |  |  |

|                  | 1 = The Timer1 Gate has gone inactive (the acquisition is complete)                                                                                |                   |                 |                |                  |                |              |  |  |  |

|                  | 0 = The Time                                                                                                                                       | r1 Gate has no    | t gone inactive | 9              |                  |                |              |  |  |  |

|                  |                                                                                                                                                    |                   |                 |                |                  |                |              |  |  |  |

| Note: Inte       | errupt flag bits a                                                                                                                                 | re set when an    | interrunt       |                |                  |                |              |  |  |  |

|                  |                                                                                                                                                    | egardless of the  | -               |                |                  |                |              |  |  |  |

#### REGISTER 10-15: PIR5: PERIPHERAL INTERRUPT REQUEST REGISTER 5

| Note: | Interrupt flag bits are set when an interrupt |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|--|

|       | condition occurs, regardless of the state of  |  |  |  |  |  |  |  |  |

|       | its corresponding enable bit or the Global    |  |  |  |  |  |  |  |  |

|       | Enable bit, GIE, of the INTCON register.      |  |  |  |  |  |  |  |  |

|       | User software should ensure the               |  |  |  |  |  |  |  |  |

|       | appropriate interrupt flag bits are clear     |  |  |  |  |  |  |  |  |

|       | prior to enabling an interrupt.               |  |  |  |  |  |  |  |  |

#### 12.7 Register Definitions: Windowed Watchdog Timer Control

#### REGISTER 12-1: WDTCON0: WATCHDOG TIMER CONTROL REGISTER 0

| U-0           | U-0              | R/W <sup>(3)</sup> -q/q <sup>(2)</sup>                             | R/W <sup>(3)</sup> -q/q <sup>(2)</sup>            | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W-0/0    |  |  |  |  |

|---------------|------------------|--------------------------------------------------------------------|---------------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|------------|--|--|--|--|

| -             | -                |                                                                    |                                                   | WDTPS<4:0>(1)                          |                                        |                                        | SWDTEN     |  |  |  |  |

| bit 7         |                  |                                                                    |                                                   |                                        |                                        |                                        | bit C      |  |  |  |  |

|               |                  |                                                                    |                                                   |                                        |                                        |                                        |            |  |  |  |  |

| Legend:       |                  |                                                                    |                                                   |                                        |                                        |                                        |            |  |  |  |  |

| R = Reada     | ble bit          | W = Writable b                                                     | pit                                               | U = Unimplem                           | nented bit, read                       | l as '0'                               |            |  |  |  |  |

| u = Bit is u  | nchanged         | x = Bit is unkno                                                   | own                                               | -n/n = Value a                         | t POR and BO                           | R/Value at all ot                      | her Resets |  |  |  |  |

| 1' = Bit is s | set              | ʻ0' = Bit is clea                                                  | red                                               | q = Value dep                          | ends on condit                         | ion                                    |            |  |  |  |  |

| bit 7-6       | Unimplome        | ntod. Dood oo 'o                                                   | 3                                                 |                                        |                                        |                                        |            |  |  |  |  |

|               | -                | ented: Read as '0<br>0>: Watchdog Tin                              |                                                   | alaat hita(1)                          |                                        |                                        |            |  |  |  |  |

| bit 5-1       |                  | Prescale Rate                                                      | nel Prescale S                                    |                                        |                                        |                                        |            |  |  |  |  |

|               |                  |                                                                    |                                                   | tom (a) (1.20)                         |                                        |                                        |            |  |  |  |  |

|               | •                | eserved. Results                                                   | in minimum in                                     | iterval (1:32)                         |                                        |                                        |            |  |  |  |  |

|               | •                |                                                                    |                                                   |                                        |                                        |                                        |            |  |  |  |  |

|               | •                |                                                                    |                                                   |                                        |                                        |                                        |            |  |  |  |  |

|               | 10011 <b>=</b> R | 0011 = Reserved. Results in minimum interval (1:32)                |                                                   |                                        |                                        |                                        |            |  |  |  |  |

|               | 10010 = <b>1</b> | 10010 = 1:8388608 (2 <sup>23</sup> ) (Interval 256s nominal)       |                                                   |                                        |                                        |                                        |            |  |  |  |  |

|               | 10001 = 1        | = 1:4194304 (2 <sup>22</sup> ) (Interval 128s nominal)             |                                                   |                                        |                                        |                                        |            |  |  |  |  |

|               | 10000 <b>= 1</b> | :2097152 (2 <sup>21</sup> ) (II                                    | 2097152 (2 <sup>21</sup> ) (Interval 64s nominal) |                                        |                                        |                                        |            |  |  |  |  |

|               | 01111 = 1        | 1048576 (2 <sup>20</sup> ) (Interval 32s nominal)                  |                                                   |                                        |                                        |                                        |            |  |  |  |  |

|               | 01110 = 1        | :524288 (2 <sup>19</sup> ) (Int<br>:262144 (2 <sup>18</sup> ) (Int | terval 16s nom                                    | inal)                                  |                                        |                                        |            |  |  |  |  |

|               | 01101 = 1        | :262144 (2 <sup>10</sup> ) (Ini                                    | terval 8s nomin                                   | nal)                                   |                                        |                                        |            |  |  |  |  |

|               |                  | :131072 (2 <sup>17</sup> ) (Int<br>:65536 (Interval 2              |                                                   |                                        |                                        |                                        |            |  |  |  |  |

|               |                  | :32768 (Interval 2                                                 |                                                   | eset value)                            |                                        |                                        |            |  |  |  |  |

|               |                  | :16384 (Interval 5                                                 | ,                                                 | d)                                     |                                        |                                        |            |  |  |  |  |

|               |                  | :8192 (Interval 25                                                 |                                                   |                                        |                                        |                                        |            |  |  |  |  |

|               |                  | :4096 (Interval 12                                                 |                                                   |                                        |                                        |                                        |            |  |  |  |  |

|               | 00110 = 1        | :2048 (Interval 64                                                 | ms nominal)                                       |                                        |                                        |                                        |            |  |  |  |  |

|               |                  | :1024 (Interval 32                                                 | ,                                                 |                                        |                                        |                                        |            |  |  |  |  |

|               |                  | :512 (Interval 16)                                                 | ,                                                 |                                        |                                        |                                        |            |  |  |  |  |

|               |                  | :256 (Interval 8 m                                                 | ,                                                 |                                        |                                        |                                        |            |  |  |  |  |

|               |                  | :128 (Interval 4 m                                                 |                                                   |                                        |                                        |                                        |            |  |  |  |  |

|               |                  | :64 (Interval 2 ms<br>:32 (Interval 1 ms                           | ,                                                 |                                        |                                        |                                        |            |  |  |  |  |

| oit O         |                  | Software Enable/                                                   |                                                   | tchdog Timer bi                        | it                                     |                                        |            |  |  |  |  |

|               | If WDTE<1:       |                                                                    |                                                   | U U                                    |                                        |                                        |            |  |  |  |  |

|               | This bit is ig   |                                                                    |                                                   |                                        |                                        |                                        |            |  |  |  |  |

|               | If WDTE<1:       |                                                                    |                                                   |                                        |                                        |                                        |            |  |  |  |  |

|               | 1 = WDT is       |                                                                    |                                                   |                                        |                                        |                                        |            |  |  |  |  |

|               | 0 = WDT is       |                                                                    |                                                   |                                        |                                        |                                        |            |  |  |  |  |

|               | If WDTE<1:       |                                                                    |                                                   |                                        |                                        |                                        |            |  |  |  |  |

|               | This bit is ig   | nored.                                                             |                                                   |                                        |                                        |                                        |            |  |  |  |  |

- **Note 1:** Times are approximate. WDT time is based on 31 kHz LFINTOSC.

- 2: When WDTCPS <4:0> in CONFIG3 = 11111, the Reset value of WDTPS<4:0> is 01011. Otherwise, the Reset value of WDTPS<4:0> is equal to WDTCPS<4:0> in CONFIG3.

- **3:** When WDTCPS <4:0> in CONFIG3  $\neq$  11111, these bits are read-only.

| Name    | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|-------|-------|---------|---------|---------|---------|---------|---------|---------------------|

| PORTA   | _     | —     | RA5     | RA4     | RA3     | RA2     | RA1     | RA0     | 178                 |

| TRISA   | _     | _     | TRISA5  | TRISA4  | —       | TRISA2  | TRISA1  | TRISA0  | 178                 |

| LATA    | _     | _     | LATA5   | LATA4   | —       | LATA2   | LATA1   | LATA0   | 179                 |

| ANSELA  | _     | _     | ANSA5   | ANSA4   | —       | ANSA2   | ANSA1   | ANSA0   | 179                 |

| WPUA    | _     | _     | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 180                 |

| ODCONA  | _     | _     | ODCA5   | ODCA4   | —       | ODCA2   | ODCA1   | ODCA0   | 180                 |

| SLRCONA | _     | _     | SLRA5   | SLRA4   | —       | SLRA2   | SLRA1   | SLRA0   | 181                 |

| INLVLA  | _     | _     | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 181                 |

#### TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Legend: x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

#### 14.6 PORTC Registers

#### 14.6.1 DATA REGISTER

PORTC is a 6 to 8-bit wide bidirectional port. The corresponding data direction register is TRISC (Register 14-18). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Figure 14-1 shows how to initialize an I/O port.

Reading the PORTC register (Register 14-17) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATC).

The PORT data latch LATC (Register 14-19) holds the output port data, and contains the latest value of a LATC or PORTC write.

#### 14.6.2 DIRECTION CONTROL

The TRISC register (Register 14-18) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 14.6.3 OPEN-DRAIN CONTROL

The ODCONC register (Register 14-22) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONC bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONC bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

| Note: | It is not necessary to set open-drain control when using the pin for $I^2C$ ; the $I^2C$ |

|-------|------------------------------------------------------------------------------------------|

|       | module controls the pin and makes the pin open-drain.                                    |

#### 14.6.4 SLEW RATE CONTROL

The SLRCONC register (Register 14-23) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONC bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONC bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

#### 14.6.5 INPUT THRESHOLD CONTROL

The INLVLC register (Register 14-24) controls the input voltage threshold for each of the available PORTC input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTC register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 37-4 for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

#### 14.6.6 ANALOG CONTROL

The ANSELC register (Register 14-20) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELC bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELC bits has no effect on digital output functions. A pin with TRIS clear and ANSELC set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELC bits default to the Analog        |  |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|--|

|       | mode after Reset. To use any pins as         |  |  |  |  |  |  |  |

|       | digital general purpose or peripheral        |  |  |  |  |  |  |  |

|       | inputs, the corresponding ANSEL bits         |  |  |  |  |  |  |  |

|       | must be initialized to '0' by user software. |  |  |  |  |  |  |  |

#### 14.6.7 WEAK PULL-UP CONTROL

The WPUC register (Register 14-21) controls the individual weak pull-ups for each port pin.

#### 14.6.8 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic. See **Section 15.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

| Name    | Bit 7                  | Bit 6                  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|------------------------|------------------------|---------|---------|---------|---------|---------|---------|---------------------|

| PORTC   | RC7 <sup>(1)</sup>     | RC6 <sup>(1)</sup>     | RC5     | RC4     | RC3     | RC2     | RC1     | RC0     | 189                 |

| TRISC   | TRISC7 <sup>(1)</sup>  | TRISC6 <sup>(1)</sup>  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  | 189                 |

| LATC    | LATC7 <sup>(1)</sup>   | LATC6 <sup>(1)</sup>   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   | 189                 |

| ANSELC  | ANSC7 <sup>(1)</sup>   | ANSC6 <sup>(1)</sup>   | ANSC5   | ANSC4   | ANSC3   | ANSC2   | ANSC1   | ANSC0   | 190                 |

| WPUC    | WPUC7 <sup>(1)</sup>   | WPUC6 <sup>(1)</sup>   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   | 190                 |

| ODCONC  | ODCC7 <sup>(1)</sup>   | ODCC6 <sup>(1)</sup>   | ODCC5   | ODCC4   | ODCC3   | ODCC2   | ODCC1   | ODCC0   | 191                 |

| SLRCONC | SLRC7 <sup>(1)</sup>   | SLRC6 <sup>(1)</sup>   | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   | 191                 |

| INLVLC  | INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 | 191                 |

#### TABLE 14-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

**Legend:** – = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

Note 1: Present on PIC16(L)F15345 only.

| Name     | Bit 7  | Bit 6  | Bit 5       | Bit 4       | Bit 3    | Bit 2    | Bit 1        | Bit 0    | Register<br>on Page |  |

|----------|--------|--------|-------------|-------------|----------|----------|--------------|----------|---------------------|--|

| INTCON   | GIE    | PEIE   | _           | _           | _        | _        | _            | INTEDG   | 124                 |  |

| PIR5     | CLC4IF | CLC3IF | CLC2IF      | CLC1IF      | _        | _        | _            | TMR1GIF  | 138                 |  |

| PIE5     | CLC4IE | CLC4IE | CLC2IE      | CLC1IE      | _        | _        | _            | TMR1GIE  | 130                 |  |

| CLC1CON  | LC1EN  | _      | LC10UT      | LC1INTP     | LC1INTN  |          | LC1MODE<2:0  | >        | 365                 |  |

| CLC1POL  | LC1POL | _      | _           | _           | LC1G4POL | LC1G3POL | LC1G2POL     | LC1G1POL | 366                 |  |

| CLC1SEL0 | _      |        |             | LC1D1S<5:0> |          |          |              |          |                     |  |

| CLC1SEL1 | _      | _      |             |             | LC1D     | 2S<5:0>  |              |          | 367                 |  |

| CLC1SEL2 | _      | _      |             |             | LC1D     | 3S<5:0>  |              |          | 367                 |  |

| CLC1SEL3 | _      | _      |             |             | LC1D     | 4S<5:0>  |              |          | 367                 |  |

| CLC1GLS0 | _      | _      | LC1G1D3T    | LC1G1D3N    | LC1G1D2T | LC1G1D2N | LC1G1D1T     | LC1G1D1N | 368                 |  |

| CLC1GLS1 | _      | _      | LC1G2D3T    | LC1G2D3N    | LC1G2D2T | LC1G2D2N | LC1G2D1T     | LC1G2D1N | 369                 |  |

| CLC1GLS2 | —      | _      | LC1G3D3T    | LC1G3D3N    | LC1G3D2T | LC1G3D2N | LC1G3D1T     | LC1G3D1N | 370                 |  |

| CLC1GLS3 | _      | _      | LC1G4D3T    | LC1G4D3N    | LC1G4D2T | LC1G4D2N | LC1G4D1T     | LC1G4D1N | 371                 |  |

| CLC2CON  | LC2EN  | _      | LC2OUT      | LC2INTP     | LC2INTN  |          | LC2MODE<2:0  | >        | 365                 |  |

| CLC2POL  | LC2POL |        | _           | _           | LC2G4POL | LC2G3POL | LC2G2POL     | LC2G1POL | 366                 |  |

| CLC2SEL0 | _      |        | LC2D1S<5:0> |             |          |          |              |          |                     |  |

| CLC2SEL1 | _      |        |             | LC2D2S<5:0> |          |          |              |          |                     |  |

| CLC2SEL2 | _      |        | LC2D3S<5:0> |             |          |          |              |          | 367                 |  |

| CLC2SEL3 | _      |        |             | LC2D4S<5:0> |          |          |              |          |                     |  |

| CLC2GLS0 | _      | _      | LC2G1D3T    | LC2G1D3N    | LC2G1D2T | LC2G1D2N | LC2G1D1T     | LC2G1D1N | 368                 |  |

| CLC2GLS1 | _      |        | LC2G2D3T    | LC2G2D3N    | LC2G2D2T | LC2G2D2N | LC2G2D1T     | LC2G2D1N | 369                 |  |

| CLC2GLS2 | _      |        | LC2G3D3T    | LC2G3D3N    | LC2G3D2T | LC2G3D2N | LC2G3D1T     | LC2G3D1N | 370                 |  |

| CLC2GLS3 | _      | _      | LC2G4D3T    | LC2G4D3N    | LC2G4D2T | LC2G4D2N | LC2G4D1T     | LC2G4D1N | 371                 |  |

| CLC3CON  | LC3EN  | _      | LC3OUT      | LC3INTP     | LC3INTN  |          | LC3MODE<2:02 | >        | 365                 |  |

| CLC3POL  | LC3POL | _      | _           | _           | LC3G4POL | LC3G3POL | LC3G2POL     | LC3G1POL | 366                 |  |

| CLC3SEL0 | _      | _      |             | L           | LC3D     | 1S<5:0>  | 1            |          | 367                 |  |

| CLC3SEL1 | _      | _      |             |             | LC3D     | 2S<5:0>  |              |          | 367                 |  |

| CLC3SEL2 | _      | _      |             |             | LC3D     | 3S<5:0>  |              |          | 367                 |  |

| CLC3SEL3 | _      | _      |             |             | LC3D     | 4S<5:0>  |              |          | 367                 |  |

| CLC3GLS0 | —      | _      | LC3G1D3T    | LC3G1D3N    | LC3G1D2T | LC3G1D2N | LC3G1D1T     | LC3G1D1N | 368                 |  |

| CLC3GLS1 | _      | _      | LC3G2D3T    | LC3G2D3N    | LC3G2D2T | LC3G2D2N | LC3G2D1T     | LC3G2D1N | 369                 |  |

| CLC3GLS2 | _      | _      | LC3G3D3T    | LC3G3D3N    | LC3G3D2T | LC3G3D2N | LC3G3D1T     | LC3G3D1N | 370                 |  |

| CLC3GLS3 | _      |        | LC3G4D3T    | LC3G4D3N    | LC3G4D2T | LC3G4D2N | LC3G4D1T     | LC3G4D1N | 371                 |  |

| CLC4CON  | LC4EN  | _      | LC4OUT      | LC4INTP     | LC4INTN  |          | LC4MODE<2:0  | >        | 365                 |  |

| CLC4POL  | LC4POL | _      | _           | _           | LC4G4POL | LC4G3POL | LC4G2POL     | LC4G1POL | 366                 |  |

| CLC4SEL0 | _      | _      |             |             | LC4D     | 1S<5:0>  | I            | 1        | 367                 |  |

| CLC4SEL1 | _      | _      |             |             | LC4D     | 2S<5:0>  |              |          | 367                 |  |

| CLC4SEL2 | _      | _      | LC4D3S<5:0> |             |          |          |              |          | 367                 |  |

| CLC4SEL3 | _      | _      | LC4D4S<5:0> |             |          |          |              |          | 367                 |  |

| CLC4GLS0 | _      |        | LC4G1D3T    | LC4G1D3N    | LC4G1D2T | LC4G1D2N | LC4G1D1T     | LC4G1D1N | 368                 |  |

TABLE 31-4: SUMMARY OF REGISTERS ASSOCIATED WITH CLCx

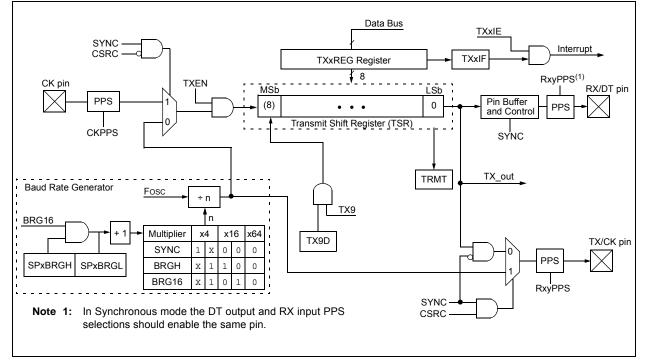

### 33.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

Note: Two identical EUSART modules are implemented on this device, EUSART1 and EUSART2. All references to EUSART1 apply to EUSART2 as well. The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- · Programmable 8-bit or 9-bit character length

- · Address detection in 9-bit mode

- · Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- · Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- Wake-up on Break reception

- · 13-bit Break character transmit

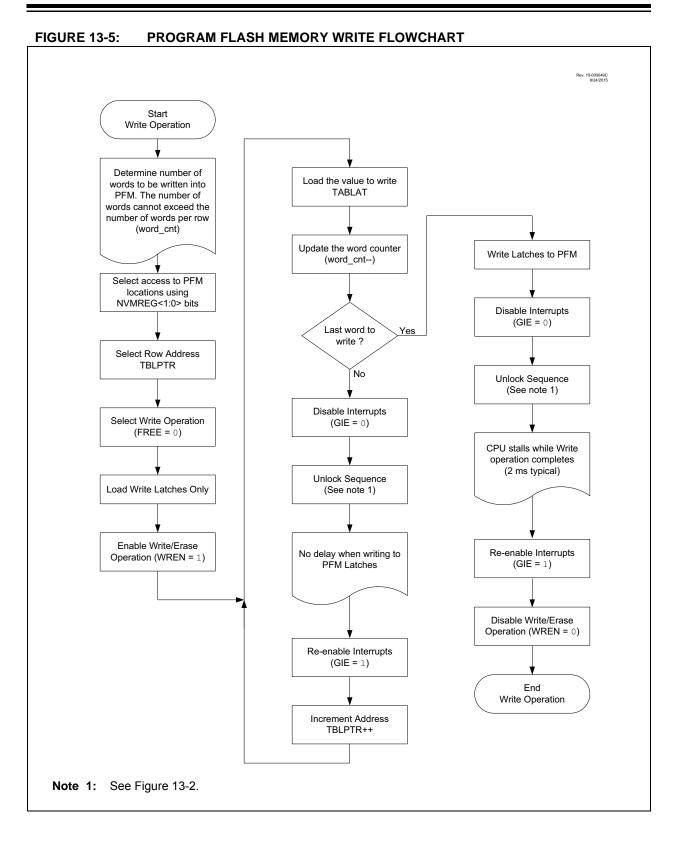

Block diagrams of the EUSART transmitter and receiver are shown in Figure 33-1 and Figure 33-2.

The EUSART transmit output (TX\_out) is available to the TX/CK pin and internally to the following peripherals:

Configurable Logic Cell (CLC)

#### FIGURE 33-1: EUSART TRANSMIT BLOCK DIAGRAM

#### 34.0 REFERENCE CLOCK OUTPUT MODULE

The reference clock output module provides the ability to send a clock signal to the clock reference output pin (CLKR).

The reference clock output module has the following features:

- Selectable input clock

- Programmable clock divider

- Selectable duty cycle

### 34.1 CLOCK SOURCE

The reference clock output module has a selectable clock source. The CLKRCLK register (Register 34-2) controls which input is used.

#### 34.1.1 CLOCK SYNCHRONIZATION

Once the reference clock enable (CLKREN) is set, the module is ensured to be glitch-free at start-up.

When the reference clock output is disabled, the output signal will be disabled immediately.

Clock dividers and clock duty cycles can be changed while the module is enabled, but glitches may occur on the output. To avoid possible glitches, clock dividers and clock duty cycles should be changed only when the CLKREN is clear.

#### 34.2 PROGRAMMABLE CLOCK DIVIDER

The module takes the system clock input and divides it based on the value of the CLKRDIV<2:0> bits of the CLKRCON register (Register 34-1).

The following configurations can be made based on the CLKRDIV<2:0> bits:

- Base clock value

- · Base clock value divided by 2

- · Base clock value divided by 4

- Base clock value divided by 8

- · Base clock value divided by 16

- Base clock value divided by 32

- Base clock value divided by 64

- Base clock value divided by 128

The clock divider values can be changed while the module is enabled; however, in order to prevent glitches on the output, the CLKRDIV<2:0> bits should only be changed when the module is disabled (CLKREN = 0).

#### 34.3 SELECTABLE DUTY CYCLE

The CLKRDC<1:0> bits of the CLKRCON register can be used to modify the duty cycle of the output clock. A duty cycle of 25%, 50%, or 75% can be selected for all clock rates, with the exception of the undivided base Fosc value.

The duty cycle can be changed while the module is enabled; however, in order to prevent glitches on the output, the CLKRDC<1:0> bits should only be changed when the module is disabled (CLKREN = 0).

Note: The CLKRDC1 bit is reset to '1'. This makes the default duty cycle 50% and not 0%.

#### 34.4 OPERATION IN SLEEP MODE

The reference clock output module clock is based on the system clock. When the device goes to Sleep, the module outputs will remain in their current state. This will have a direct effect on peripherals using the reference clock output as an input signal.

| RETLW            | Return with literal in W                                                                                                                                                      |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                      |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                                                             |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                  |  |  |  |  |