Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

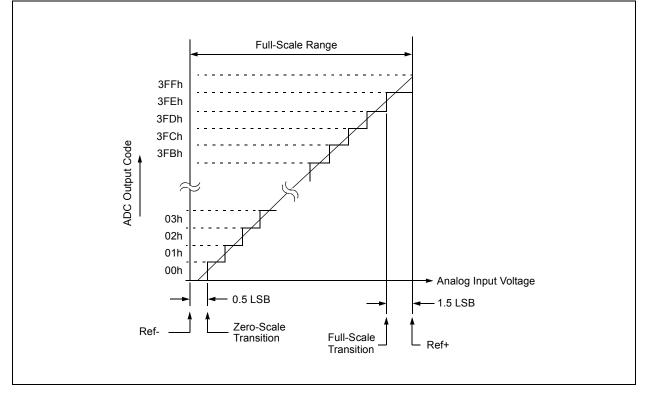

| Data Converters            | A/D 17x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 20-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15345-e-gz |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.3.2.1 STATUS Register

The STATUS register, shown in Register 4-1, contains:

- the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

# For example, CLRF STATUS will clear bits <4:3> and <1:0>, and set the Z bit. This leaves the STATUS register as '000u u1uu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits, refer to **Section 36.0** "Instruction Set Summary".

Note 1: The <u>C</u> and <u>DC</u> bits operate as Borrow and <u>Digit</u> Borrow out bits, respectively, in subtraction.

# REGISTER 4-1: STATUS: STATUS REGISTER

| U-0   | U-0 | U-0 | R-1/q | R-1/q | R/W-0/u | R/W-0/u           | R/W-0/u          |

|-------|-----|-----|-------|-------|---------|-------------------|------------------|

| —     | _   | _   | TO    | PD    | Z       | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7 |     |     |       |       |         |                   | bit 0            |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                                                           |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-Out bit                                                                                                                                                                                                     |

|         | 1 = After power-up, CLRWDT instruction or SLEEP instruction<br>0 = A WDT time-out occurred                                                                                                                           |

| bit 3   | PD: Power-Down bit                                                                                                                                                                                                   |

|         | 1 = After power-up or by the CLRWDT instruction                                                                                                                                                                      |

|         | 0 = By execution of the SLEEP instruction                                                                                                                                                                            |

| bit 2   | Z: Zero bit                                                                                                                                                                                                          |

|         | 1 = The result of an arithmetic or logic operation is zero                                                                                                                                                           |

|         | 0 = The result of an arithmetic or logic operation is not zero                                                                                                                                                       |

| bit 1   | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                                                                            |

|         | 1 = A carry-out from the 4th low-order bit of the result occurred                                                                                                                                                    |

|         | 0 = No carry-out from the 4th low-order bit of the result                                                                                                                                                            |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                                                                          |

|         | 1 = A carry-out from the Most Significant bit of the result occurred                                                                                                                                                 |

|         | 0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                |

| Note 1: | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order |

bit of the source register.

| TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED) |                                                                    |                                                   |                   |               |                               |        |           |           |           |                       |                            |

|----------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------|-------------------|---------------|-------------------------------|--------|-----------|-----------|-----------|-----------------------|----------------------------|

| Address                                                              | Name                                                               | Bit 7                                             | Bit 6             | Bit 5         | Bit 4                         | Bit 3  | Bit 2     | Bit 1     | Bit 0     | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

| Bank 63                                                              |                                                                    |                                                   |                   |               |                               |        |           |           |           |                       |                            |

|                                                                      | CPU CORE REGISTERS; see Table 4-3 for specifics                    |                                                   |                   |               |                               |        |           |           |           |                       |                            |

| 1F8Ch<br><br>1FE3h                                                   | _                                                                  |                                                   |                   |               | Unimple                       | mented |           |           |           | _                     | _                          |

| 1FE4h                                                                | STATUS_SHAD                                                        | —                                                 | —                 | —             | _                             | —      | Z         | DC        | С         | xxx                   | uuu                        |

| 1FE5h                                                                | WREG_SHAD                                                          | G_SHAD Working Register Shadow                    |                   |               |                               |        |           |           | xxxx xxxx | uuuu uuuu             |                            |

| 1FE6h                                                                | BSR_SHAD                                                           | —                                                 | —                 | _             | – Bank Select Register Shadow |        |           |           |           | x xxxx                | u uuuu                     |

| 1FE7h                                                                | PCLATH_SHAD                                                        | SHAD — Program Counter Latch High Register Shadow |                   |               |                               |        |           | -xxx xxxx | uuuu uuuu |                       |                            |

| 1FE8h                                                                | IFE8h FSR0L_SHAD Indirect Data Memory Address 0 Low Pointer Shadow |                                                   |                   |               |                               |        | xxxx xxxx | uuuu uuuu |           |                       |                            |

| 1FE9h                                                                | FSR0H_SHAD                                                         | Indirect Data Memory                              | Address 0 High Po | ointer Shadow |                               |        |           |           |           | xxxx xxxx             | uuuu uuuu                  |

| 1FEAh                                                                | EAh FSR1L_SHAD Indirect Data Memory Address 1 Low Pointer Shadow   |                                                   |                   |               |                               |        | xxxx xxxx | uuuu uuuu |           |                       |                            |

| 1FEBh                                                                | Bh FSR1H_SHAD Indirect Data Memory Address 1 High Pointer Shadow   |                                                   |                   |               |                               |        | xxxx xxxx | uuuu uuuu |           |                       |                            |

| 1FECh                                                                | _                                                                  | Unimplemented                                     |                   |               |                               |        |           | —         |           |                       |                            |

| 1FEDh                                                                | STKPTR                                                             | Current Stack Pointer                             |                   |               |                               |        | 1 1111    | 1 1111    |           |                       |                            |

| 1FEEh                                                                | TOSL                                                               | Top of Stack Low byte                             |                   |               |                               |        |           |           |           | XXXX XXXX             | uuuu uuuu                  |

| 1FEFh                                                                | TOSH — Top of Stack High byte                                      |                                                   |                   |               |                               |        |           | -xxx xxxx | -uuu uuuu |                       |                            |

# TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

| NOSC<2:0>/<br>COSC<2:0> | Clock Source                              |

|-------------------------|-------------------------------------------|

| 111                     | EXTOSC <sup>(1)</sup>                     |

| 110                     | HFINTOSC <sup>(2)</sup>                   |

| 101                     | LFINTOSC                                  |

| 100                     | SOSC                                      |

| 011                     | Reserved (operates like<br>NOSC = 110)    |

| 010                     | EXTOSC with 4x PLL <sup>(1)</sup>         |

| 001                     | HFINTOSC with 2x PLL <sup>(1)</sup>       |

| 000                     | Reserved (it operates like<br>NOSC = 110) |

| Note 1: EXTOSC config   | ured by the FEXTOSC bits of               |

## TABLE 9-1: NOSC/COSC BIT SETTINGS

**Note 1:** EXTOSC configured by the FEXTOSC bits of Configuration Word 1 (Register 5-1).

2: HFINTOSC settings are configured with the HFFRQ bits of the OSCFRQ register (Register 9-6).

# TABLE 9-2: NDIV/CDIV BIT SETTINGS

| NDIV<3:0>/<br>CDIV<3:0> | Clock divider |

|-------------------------|---------------|

| 1111-1010               | Reserved      |

| 1001                    | 512           |

| 1000                    | 256           |

| 0111                    | 128           |

| 0110                    | 64            |

| 0101                    | 32            |

| 0100                    | 16            |

| 0011                    | 8             |

| 0010                    | 4             |

| 0001                    | 2             |

| 0000                    | 1             |

# REGISTER 9-3: OSCCON3: OSCILLATOR CONTROL REGISTER 3

| R/W/HC-0/0  | R/W-0/0 | U-0 | R-0/0 | R-0/0 | U-0 | U-0 | U-0 |

|-------------|---------|-----|-------|-------|-----|-----|-----|

| CSWHOLD     | SOSCPWR | —   | ORDY  | NOSCR | —   | —   | —   |

| bit 7 bit C |         |     |       |       |     |     |     |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | CSWHOLD: Clock Switch Hold bit                                                                                                                                                                                 |  |  |  |  |  |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|         | <ul> <li>1 = Clock switch will hold (with interrupt) when the oscillator selected by NOSC is ready</li> <li>0 = Clock switch may proceed when the oscillator selected by NOSC is ready; if this bit</li> </ul> |  |  |  |  |  |  |  |

|         | is clear at the time that NOSCR becomes '1', the switch will occur                                                                                                                                             |  |  |  |  |  |  |  |

| bit 6   | SOSCPWR: Secondary Oscillator Power Mode Select bit                                                                                                                                                            |  |  |  |  |  |  |  |

|         | 1 = Secondary oscillator operating in High-power mode                                                                                                                                                          |  |  |  |  |  |  |  |

|         | 0 = Secondary oscillator operating in Low-power mode                                                                                                                                                           |  |  |  |  |  |  |  |

| bit 5   | Unimplemented: Read as '0'.                                                                                                                                                                                    |  |  |  |  |  |  |  |

| bit 4   | ORDY: Oscillator Ready bit (read-only)                                                                                                                                                                         |  |  |  |  |  |  |  |

|         | 1 = OSCCON1 = OSCCON2; the current system clock is the clock specified by NOSC                                                                                                                                 |  |  |  |  |  |  |  |

|         | 0 = A clock switch is in progress                                                                                                                                                                              |  |  |  |  |  |  |  |

| bit 3   | NOSCR: New Oscillator is Ready bit (read-only)                                                                                                                                                                 |  |  |  |  |  |  |  |

|         | 1 = A clock switch is in progress and the oscillator selected by NOSC indicates a "ready" condition                                                                                                            |  |  |  |  |  |  |  |

|         | 0 = A clock switch is not in progress, or the NOSC-selected oscillator is not yet ready                                                                                                                        |  |  |  |  |  |  |  |

| bit 2-0 | Unimplemented: Read as '0'                                                                                                                                                                                     |  |  |  |  |  |  |  |

# PIC16(L)F15325/45

| R/W-0/0                                                                                                                       | R/W-0/0                                                   | U-0                                              | R/W-0/0 | U-0            | U-0              | U-0            | R/W-0/0      |

|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------|---------|----------------|------------------|----------------|--------------|

| UART2MD                                                                                                                       | UART1MD                                                   | —                                                | MSSP1MD | —              | —                | _              | CWG1MD       |

| bit 7                                                                                                                         |                                                           |                                                  |         |                |                  |                | bit 0        |

|                                                                                                                               |                                                           |                                                  |         |                |                  |                |              |

| Legend:                                                                                                                       |                                                           |                                                  |         |                |                  |                |              |

| R = Readable                                                                                                                  | bit                                                       | W = Writable I                                   | pit     | U = Unimplem   | nented bit, read | as '0'         |              |

| u = Bit is unch                                                                                                               | nanged                                                    | x = Bit is unkn                                  | own     | -n/n = Value a | t POR and BOR    | R/Value at all | other Resets |

| '1' = Bit is set                                                                                                              |                                                           | '0' = Bit is clea                                | ared    | q = Value dep  | ends on conditio | on             |              |

| bit 7<br>bit 6<br>bit 5                                                                                                       | 1 = EUSART2 module disabled<br>0 = EUSART2 module enabled |                                                  |         |                |                  |                |              |

| bit 5 Unimplemented: Read as '0'<br>bit 4 MSSP1MD: Disable MSSP1 bit<br>1 = MSSP1 module disabled<br>0 = MSSP1 module enabled |                                                           |                                                  |         |                |                  |                |              |

| bit 3-1                                                                                                                       | Unimplement                                               | ted: Read as '0                                  | ,       |                |                  |                |              |

| bit 0                                                                                                                         | 1 = CWG1 m                                                | sable CWG1 bi<br>odule disabled<br>odule enabled | t       |                |                  |                |              |

# REGISTER 16-5: PMD4: PMD CONTROL REGISTER 4

© 2016 Microchip Technology Inc.

DS40001865B-page 232

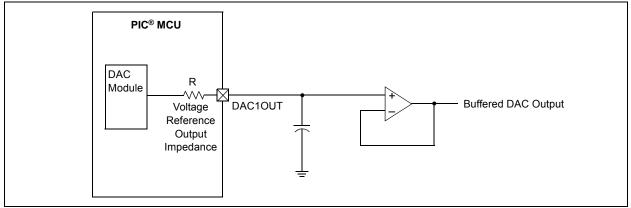

# FIGURE 21-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

© 2016 Microchip Technology Inc.

DS40001865B-page 240

# 22.0 NUMERICALLY CONTROLLED OSCILLATOR (NCO) MODULE

The Numerically Controlled Oscillator (NCO) module is a timer that uses overflow from the addition of an increment value to divide the input frequency. The advantage of the addition method over simple counter driven timer is that the output frequency resolution does not vary with the divider value. The NCO is most useful for application that requires frequency accuracy and fine resolution at a fixed duty cycle.

Features of the NCO include:

- 20-bit Increment Function

- Fixed Duty Cycle mode (FDC) mode

- Pulse Frequency (PF) mode

- Output Pulse Width Control

- Multiple Clock Input Sources

- Output Polarity Control

- Interrupt Capability

Figure 22-1 is a simplified block diagram of the NCO module.

# 22.8 NCO Control Registers

| R/W-0/0          | U-0                                    | R-0/0                               | R/W-0/0         | U-0            | U-0              | U-0              | R/W-0/0      |

|------------------|----------------------------------------|-------------------------------------|-----------------|----------------|------------------|------------------|--------------|

| N1EN             | —                                      | N1OUT                               | N1POL           | —              | _                | —                | N1PFM        |

| bit 7            |                                        |                                     |                 |                |                  |                  | bit 0        |

|                  |                                        |                                     |                 |                |                  |                  |              |

| Legend:          |                                        |                                     |                 |                |                  |                  |              |

| R = Readable     | bit                                    | W = Writable                        | bit             | U = Unimpler   | nented bit, read | l as '0'         |              |

| u = Bit is unch  | anged                                  | x = Bit is unkr                     | nown            | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |                                        | '0' = Bit is cle                    | ared            |                |                  |                  |              |

|                  |                                        |                                     |                 |                |                  |                  |              |

| bit 7            | N1EN: NCO1                             |                                     |                 |                |                  |                  |              |

|                  |                                        | odule is enable<br>odule is disable |                 |                |                  |                  |              |

| bit 6            |                                        |                                     | -               |                |                  |                  |              |

|                  | -                                      | ted: Read as '                      | 0               |                |                  |                  |              |

| bit 5            | N1OUT: NCO                             | of Output bit output v              | value of the NC |                |                  |                  |              |

| bit 4            | N1POL: NCC                             | -                                   |                 | of module.     |                  |                  |              |

| bit 4            |                                        | tput signal is in                   | verted          |                |                  |                  |              |

|                  | 0 = NCO1 output signal is not inverted |                                     |                 |                |                  |                  |              |

| bit 3-1          | Unimplemented: Read as '0'             |                                     |                 |                |                  |                  |              |

| bit 0            |                                        | 01 Pulse Frequ                      | •               |                |                  |                  |              |

|                  |                                        | erates in Pulse                     |                 |                | _                |                  |              |

|                  | 0 = NCO1 op                            | erates in Fixed                     | Duty Cycle m    | ode, divide by | 2                |                  |              |

|                  |                                        |                                     |                 |                |                  |                  |              |

# REGISTER 22-1: NCO1CON: NCO CONTROL REGISTER

# PIC16(L)F15325/45

| R/W-0/0          | R/W-0/0                                                                                                                                                                                                                                                    | R/W-0/0                                                                  | R/W-0/0        | R/W-0/0                                              | R/W-0/0          | R/W-0/0 | R/W-0/0 |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------|------------------------------------------------------|------------------|---------|---------|--|

|                  | T0CS<2:0>                                                                                                                                                                                                                                                  |                                                                          | TOASYNC        |                                                      | T0CKP            | S<3:0>  |         |  |

| bit 7            |                                                                                                                                                                                                                                                            |                                                                          |                |                                                      |                  |         | bit (   |  |

|                  |                                                                                                                                                                                                                                                            |                                                                          |                |                                                      |                  |         |         |  |

| Legend:          |                                                                                                                                                                                                                                                            |                                                                          |                |                                                      |                  |         |         |  |

| R = Readable     | bit                                                                                                                                                                                                                                                        | W = Writable                                                             | bit            | U = Unimplen                                         | nented bit, read | as '0'  |         |  |

| u = Bit is unch  | anged                                                                                                                                                                                                                                                      | x = Bit is unknown                                                       |                | -n/n = Value at POR and BOR/Value at all other Reset |                  |         |         |  |

| '1' = Bit is set |                                                                                                                                                                                                                                                            | '0' = Bit is cleared                                                     |                |                                                      |                  |         |         |  |

| bit 7-5<br>bit 4 | 111 = LC1_c<br>110 = SOSC<br>101 = MFINT<br>100 = LFINT<br>010 = FOSC/<br>001 = TOCK<br>000 = TOCK                                                                                                                                                         | ;<br>FOSC (500 kHz<br>OSC<br>FOSC<br>4<br>IPPS (Inverted)<br>IPPS (True) | :)             |                                                      |                  |         |         |  |

|                  | <b>TOASYNC:</b> TMR0 Input Asynchronization Enable bit<br>1 = The input to the TMR0 counter is not synchronized to system clocks<br>0 = The input to the TMR0 counter is synchronized to Fosc/4                                                            |                                                                          |                |                                                      |                  |         |         |  |

| bit 3-0          | <b>TOCKPS&lt;3:</b> (<br>1111 = 1:32<br>1110 = 1:16:<br>1101 = 1:819<br>1000 = 1:409<br>1011 = 1:20<br>1010 = 1:100<br>1001 = 1:100<br>1001 = 1:512<br>1000 = 1:250<br>0111 = 1:129<br>0100 = 1:40<br>0011 = 1:8<br>0010 = 1:4<br>0001 = 1:2<br>0000 = 1:1 | 384<br>92<br>96<br>48<br>24<br>2<br>6<br>8                               | ate Select bit |                                                      |                  |         |         |  |

| R/W-0/0                | R/W-0/0                                                   | R/W-0/0                                        | R/W-0/0         | R/W-0/0            | R/W-0/0            | R/W-0/0           | R/W-0/0          |

|------------------------|-----------------------------------------------------------|------------------------------------------------|-----------------|--------------------|--------------------|-------------------|------------------|

| PSYNC <sup>(1, 2</sup> | ) CKPOL <sup>(3)</sup>                                    | CKSYNC <sup>(4, 5)</sup>                       |                 |                    | MODE<4:0>(6, 7)    |                   |                  |

| bit 7                  |                                                           |                                                |                 |                    |                    |                   | bit 0            |

|                        |                                                           |                                                |                 |                    |                    |                   |                  |

| Legend:                |                                                           |                                                |                 |                    |                    |                   |                  |

| R = Readabl            | e bit                                                     | W = Writable bit                               |                 | U = Unimpleme      | ented bit, read as | '0'               |                  |

| u = Bit is und         | hanged                                                    | x = Bit is unknov                              | vn              | -n/n = Value at    | POR and BOR/Va     | alue at all other | Resets           |

| '1' = Bit is se        | t                                                         | '0' = Bit is cleare                            | ed              |                    |                    |                   |                  |

| bit 7                  | DEVNC. Time                                               | rx Prescaler Synch                             | ronization Enc  | blo bit(1, 2)      |                    |                   |                  |

|                        |                                                           | escaler Output is s                            |                 |                    |                    |                   |                  |

|                        |                                                           | escaler Output is n                            |                 |                    |                    |                   |                  |

| bit 6                  | CKPOL: Timerx Clock Polarity Selection bit <sup>(3)</sup> |                                                |                 |                    |                    |                   |                  |

|                        | 0                                                         | dge of input clock o                           |                 |                    |                    |                   |                  |

|                        | •                                                         | lge of input clock c                           | •               |                    |                    |                   |                  |

| bit 5                  |                                                           | nerx Clock Synchro                             |                 |                    |                    |                   |                  |

|                        | 0                                                         | ter bit is synchroniz<br>ter bit is not synchi | _               |                    |                    |                   |                  |

| bit 4-0                | •                                                         | Timerx Control Mo                              |                 | - ·                |                    |                   |                  |

| 51( 4-0                | See Table 27-1                                            |                                                |                 |                    |                    |                   |                  |

| Note 1:                | Setting this bit ens                                      | ures that reading 1                            | MRx will retur  | n a valid value.   |                    |                   |                  |

| 2:                     | When this bit is '1'                                      | , Timer2 cannot op                             | erate in Sleep  | mode.              |                    |                   |                  |

| 3:                     | CKPOL should not                                          | t be changed while                             | ON = 1.         |                    |                    |                   |                  |

| 4:                     | Setting this bit ens                                      | ures glitch-free op                            | eration when th | ne ON is enabled   | or disabled.       |                   |                  |

| 5:                     | When this bit is se                                       | t then the timer op                            | eration will be | delayed by two Tl  | MRx input clocks   | after the ON bit  | is set.          |

| 6:                     | Unless otherwise in of TMRx).                             | ndicated, all modes                            | s start upon ON | I = 1 and stop upo | on ON = 0 (stops o | occur without aff | ecting the value |

# REGISTER 27-3: T2HLT: TIMERx HARDWARE LIMIT CONTROL REGISTER

7: When TMRx = PRx, the next clock clears TMRx, regardless of the operating mode.

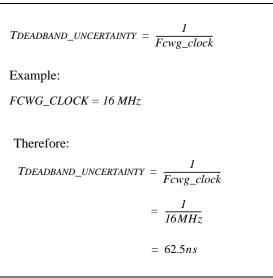

#### 30.8 **Dead-Band Uncertainty**

When the rising and falling edges of the input source are asynchronous to the CWG clock, it creates uncertainty in the dead-band time delay. The maximum uncertainty is equal to one CWG clock period. Refer to Equation 30-1 for more details.

## EQUATION 30-1: DEAD-BAND UNCERTAINTY

# MODE0 CWG1A CWG1B CWG1C CWG1D No delay CWG1DBR 🕂 No delay CWG1DBF CWG1\_data Note 1: WGPOL{ABCD} = 0 2: The direction bit MODE<0> (Register 30-1) can be written any time during the PWM cycle, and takes effect at the next rising CWG1 data. 3: When changing directions, CWG1A and CWG1C switch at rising CWG1\_data; modulated CWG1B and CWG1D are held inactive for the dead band duration shown; dead band affects only the first pulse after the direction change.

#### **FIGURE 30-8: EXAMPLE OF PWM DIRECTION CHANGE**

# 31.1 CLCx Setup

Programming the CLCx module is performed by configuring the four stages in the logic signal flow. The four stages are:

- · Data selection

- · Data gating

- Logic function selection

- Output polarity

Each stage is setup at run time by writing to the corresponding CLCx Special Function Registers. This has the added advantage of permitting logic reconfiguration on-the-fly during program execution.

# 31.1.1 DATA SELECTION

There are 40 signals available as inputs to the configurable logic. Four 40-input multiplexers are used to select the inputs to pass on to the next stage.

Data selection is through four multiplexers as indicated on the left side of Figure 31-2. Data inputs in the figure are identified by a generic numbered input name.

Table 31-2 correlates the generic input name to the actual signal for each CLC module. The column labeled 'LCxDyS<4:0> Value' indicates the MUX selection code for the selected data input. LCxDyS is an abbreviation to identify specific multiplexers: LCxD1S<4:0> through LCxD4S<4:0>.

Data inputs are selected with CLCxSEL0 through CLCxSEL3 registers (Register 31-3 through Register 31-6).

# TABLE 31-2: CLCx DATA INPUT SELECTION

| LCxDyS<4:0><br>Value   | CLCx Input Source      |  |  |

|------------------------|------------------------|--|--|

| 101000 to 111111 [40+] | Reserved               |  |  |

| 100111 <b>[39]</b>     | CWG1B output           |  |  |

| 100110 <b>[38]</b>     | CWG1A output           |  |  |

| 100101 [37]            | Reserved               |  |  |

| 100100 <b>[36]</b>     | Reserved               |  |  |

| 100011 [35]            | MSSP1 SCK output       |  |  |

| 100010 <b>[34]</b>     | MSSP1 SDO output       |  |  |

| 100001 [33]            | EUSART2 (TX/CK) output |  |  |

| 100000 <b>[32]</b>     | EUSART2 (DT) output    |  |  |

| 011111 [31]            | EUSART1 (TX/CK) output |  |  |

| 011110 [30]            | EUSART1 (DT) output    |  |  |

| 011101 [29]            | CLC4 output            |  |  |

| 011100 [28]            | CLC3 output            |  |  |

| 011011 [27]            | CLC2 output            |  |  |

| 011010 [26]            | CLC1 output            |  |  |

| 011001 [25]            | IOCIF                  |  |  |

| 011000 [24]            | ZCD output             |  |  |

| 010111 [23]            | C2OUT                  |  |  |

| 010110 [22]            | C1OUT                  |  |  |

| 010101 <b>[21]</b>     | NCO1 output            |  |  |

| 010100 <b>[20]</b>     | PWM6 output            |  |  |

| 010011 [19]            | PWM5 output            |  |  |

| 010010 [18]            | PWM4 output            |  |  |

| 010001 [17]            | PWM3 output            |  |  |

| 010000 [16]            | CCP2 output            |  |  |

| 001111 [15]            | CCP1 output            |  |  |

| 001110 [14]            | Timer2 overflow        |  |  |

| 001101 [13]            | Timer1 overflow        |  |  |

| 001100 <b>[12]</b>     | Timer0 overflow        |  |  |

| 001011 [11]            | CLKR                   |  |  |

| 001010 [10]            | ADCRC                  |  |  |

| 001001 <b>[9]</b>      | SOSC                   |  |  |

| 001000 <b>[8]</b>      | MFINTOSC (32 kHz)      |  |  |

| 000111 [7]             | MFINTOSC (500 kHz)     |  |  |

| 000110 <b>[6]</b>      | LFINTOSC               |  |  |

| 000101 [5]             | HFINTOSC               |  |  |

| 000100 [4]             | Fosc                   |  |  |

| 000011 [3]             | CLCIN3PPS              |  |  |

| 000010 [2]             | CLCIN2PPS              |  |  |

| 000001 [1]             | CLCIN1PPS              |  |  |

| 000000 <b>[0]</b>      | CLCIN0PPS              |  |  |

| R/W-x/u              | R/W-x/u                                                                                           | R/W-x/u                                                                                                                  | R/W-x/u              | R/W-x/u                            | R/W-x/u       | R/W-x/u          | R/W-x/u     |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------------------|---------------|------------------|-------------|--|--|--|

| LCxG3D4T             | LCxG3D4N                                                                                          | LCxG3D3T                                                                                                                 | LCxG3D3N             | LCxG3D2T                           | LCxG3D2N      | LCxG3D1T         | LCxG3D1N    |  |  |  |

| bit 7                |                                                                                                   |                                                                                                                          |                      |                                    |               |                  | bit (       |  |  |  |

|                      |                                                                                                   |                                                                                                                          |                      |                                    |               |                  |             |  |  |  |

| Legend:              |                                                                                                   |                                                                                                                          |                      |                                    |               | ( <b>a</b> )     |             |  |  |  |

| R = Readable         |                                                                                                   | W = Writable bit                                                                                                         |                      | U = Unimplemented bit, read as '0' |               |                  |             |  |  |  |

| u = Bit is unchanged |                                                                                                   | x = Bit is unknown                                                                                                       |                      | -n/n = Value a                     | at POR and BO | R/Value at all c | ther Resets |  |  |  |

| '1' = Bit is set     |                                                                                                   | '0' = Bit is clea                                                                                                        | '0' = Bit is cleared |                                    |               |                  |             |  |  |  |

| bit 7                |                                                                                                   | Noto 2 Doto 4 1                                                                                                          | True (non inve       | rtad) bit                          |               |                  |             |  |  |  |

|                      |                                                                                                   | Gate 2 Data 4 1                                                                                                          |                      | ,                                  |               |                  |             |  |  |  |

|                      |                                                                                                   | <ul> <li>1 = CLCIN3 (true) is gated into CLCx Gate 2</li> <li>0 = CLCIN3 (true) is not gated into CLCx Gate 2</li> </ul> |                      |                                    |               |                  |             |  |  |  |

| bit 6                |                                                                                                   |                                                                                                                          |                      |                                    |               |                  |             |  |  |  |

|                      | LCxG3D4N: Gate 2 Data 4 Negated (inverted) bit<br>1 = CLCIN3 (inverted) is gated into CLCx Gate 2 |                                                                                                                          |                      |                                    |               |                  |             |  |  |  |

|                      | 0 = CLCIN3 (inverted) is not gated into CLCx Gate 2                                               |                                                                                                                          |                      |                                    |               |                  |             |  |  |  |

| bit 5                | LCxG3D3T: Gate 2 Data 3 True (non-inverted) bit                                                   |                                                                                                                          |                      |                                    |               |                  |             |  |  |  |

|                      | 1 = CLCIN2 (                                                                                      | = CLCIN2 (true) is gated into CLCx Gate 2                                                                                |                      |                                    |               |                  |             |  |  |  |

|                      | 0 = CLCIN2 (true) is not gated into CLCx Gate 2                                                   |                                                                                                                          |                      |                                    |               |                  |             |  |  |  |

| bit 4                | LCxG3D3N: Gate 2 Data 3 Negated (inverted) bit                                                    |                                                                                                                          |                      |                                    |               |                  |             |  |  |  |

|                      |                                                                                                   | CLCIN2 (inverted) is gated into CLCx Gate 2                                                                              |                      |                                    |               |                  |             |  |  |  |

|                      |                                                                                                   | IN2 (inverted) is not gated into CLCx Gate 2                                                                             |                      |                                    |               |                  |             |  |  |  |

| bit 3                |                                                                                                   | Gate 2 Data 2 T                                                                                                          | · ·                  |                                    |               |                  |             |  |  |  |

|                      |                                                                                                   | CIN1 (true) is gated into CLCx Gate 2<br>CIN1 (true) is not gated into CLCx Gate 2                                       |                      |                                    |               |                  |             |  |  |  |

| bit 2                |                                                                                                   | Gate 2 Data 2                                                                                                            |                      |                                    |               |                  |             |  |  |  |

|                      |                                                                                                   | (inverted) is ga                                                                                                         | • ·                  | ,                                  |               |                  |             |  |  |  |

|                      |                                                                                                   | (inverted) is no                                                                                                         |                      |                                    |               |                  |             |  |  |  |

| bit 1                | <b>LCxG3D1T:</b> Gate 2 Data 1 True (non-inverted) bit                                            |                                                                                                                          |                      |                                    |               |                  |             |  |  |  |

|                      |                                                                                                   | (true) is gated into CLCx Gate 2                                                                                         |                      |                                    |               |                  |             |  |  |  |

|                      | 0 = CLCIN0                                                                                        | (true) is not gat                                                                                                        | ted into CLCx        | Gate 2                             |               |                  |             |  |  |  |

| bit 0                | LCxG3D1N:                                                                                         | Gate 2 Data 1 I                                                                                                          | Negated (inver       | rted) bit                          |               |                  |             |  |  |  |

|                      |                                                                                                   | (inverted) is ga                                                                                                         |                      |                                    |               |                  |             |  |  |  |

|                      | 0 = CLCIN0                                                                                        | (inverted) is no                                                                                                         | t gated into Cl      | Cx Gate 2                          |               |                  |             |  |  |  |

# REGISTER 31-9: CLCxGLS2: GATE 2 LOGIC SELECT REGISTER

#### 32.4.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT bit of the SSP1CON3 register. Hold time is the time SDA is held valid after the falling edge of SCL. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

| TABLE 32-1: | I <sup>2</sup> C BUS TERMS |

|-------------|----------------------------|

|-------------|----------------------------|

| TERM                | Description                                                                                                                                                                                                     |  |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                                                  |  |  |  |  |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                                                   |  |  |  |  |

| Master              | The device that initiates a transfer, generates clock signals and termi-<br>nates a transfer.                                                                                                                   |  |  |  |  |

| Slave               | The device addressed by the master.                                                                                                                                                                             |  |  |  |  |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                                               |  |  |  |  |

| Arbitration         | Procedure to ensure that only one<br>master at a time controls the bus.<br>Winning arbitration ensures that<br>the message is not corrupted.                                                                    |  |  |  |  |

| Synchronization     | Procedure to synchronize the clocks of two or more devices on the bus.                                                                                                                                          |  |  |  |  |

| Idle                | No master is controlling the bus,<br>and both SDA and SCL lines are<br>high.                                                                                                                                    |  |  |  |  |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                                                    |  |  |  |  |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                                                    |  |  |  |  |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSP1ADD.                                                                                                                             |  |  |  |  |

| Write Request       | Slave receives a matching<br>address with R/W bit clear, and is<br>ready to clock in data.                                                                                                                      |  |  |  |  |

| Read Request        | Master sends an address byte with<br>the $R/\overline{W}$ bit set, indicating that it<br>wishes to clock data out of the<br>Slave. This data is the next and all<br>following bytes until a Restart or<br>Stop. |  |  |  |  |

| Clock Stretching    | When a device on the bus hold SCL low to stall communication.                                                                                                                                                   |  |  |  |  |

| Bus Collision       | Any time the SDA line is sampled<br>low by the module while it is out-<br>putting and expected high state.                                                                                                      |  |  |  |  |

#### 32.4.5 START CONDITION

The  $I^2C$  specification defines a Start condition as a transition of SDA from a high to a low state while SCL line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an active state. Figure 32-12 shows wave forms for Start and Stop conditions.

32.4.6 STOP CONDITION

A Stop condition is a transition of the SDA line from low-to-high state while the SCL line is high.

| Note: | At least one SCL low time must appear         |

|-------|-----------------------------------------------|

|       | before a Stop is valid, therefore, if the SDA |

|       | line goes low then high again while the SCL   |

|       | line stays high, only the Start condition is  |

|       | detected.                                     |

### 32.4.7 RESTART CONDITION

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 32-13 shows the wave form for a Restart condition.

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes, the master can issue a Restart and the high address byte with the R/W bit set. The slave logic will then hold the clock and prepare to clock out data.

#### 32.4.8 START/STOP CONDITION INTERRUPT MASKING

The SCIE and PCIE bits of the SSP1CON3 register can enable the generation of an interrupt in Slave modes that do not typically support this function. Slave modes where interrupt on Start and Stop detect are already enabled, these bits will have no effect.

# 32.5.3 SLAVE TRANSMISSION

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSP1STAT register is set. The received address is loaded into the SSP1BUF register, and an ACK pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCL pin is held low (see **Section 32.5.6** "**Clock Stretching**" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSP1BUF register which also loads the SSP1SR register. Then the SCL pin should be released by setting the CKP bit of the SSP1CON1 register. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time.

The  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. This  $\overline{ACK}$ value is copied to the ACKSTAT bit of the SSP1CON2 register. If ACKSTAT is set (not  $\overline{ACK}$ ), then the data transfer is complete. In this case, when the not  $\overline{ACK}$  is latched by the slave, the slave goes idle and waits for another occurrence of the Start bit. If the SDA line was low ( $\overline{ACK}$ ), the next transmit data must be loaded into the SSP1BUF register. Again, the SCL pin must be released by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSP1IF bit must be cleared by software and the SSP1STAT register is used to determine the status of the byte. The SSP1IF bit is set on the falling edge of the ninth clock pulse.

# 32.5.3.1 Slave Mode Bus Collision

A slave receives a read request and begins shifting data out on the SDA line. If a bus collision is detected and the SBCDE bit of the SSP1CON3 register is set, the BCL1IF bit of the PIR3 register is set. Once a bus collision is detected, the slave goes idle and waits to be addressed again. User software can use the BCL1IF bit to handle a slave bus collision.

## 32.5.3.2 7-bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 32-18 can be used as a reference to this list.

- 1. Master sends a Start condition on SDA and SCL.

- 2. S bit of SSP1STAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit set is received by the Slave setting SSP1IF bit.

- 4. Slave hardware generates an ACK and sets SSP1IF.

- 5. SSP1IF bit is cleared by user.

- 6. Software reads the received address from SSP1BUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSP1BUF.

- 9. CKP bit is set releasing SCL, allowing the master to clock the data out of the slave.

- 10. SSP1IF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSP1IF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

- Note 1: If the master ACKs the clock will be stretched.

- ACKSTAT is the only bit updated on the rising edge of SCL (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSP1IF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.

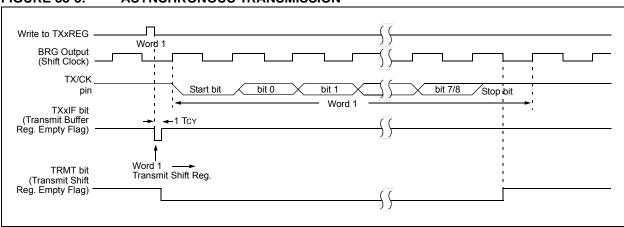

# 33.1.1.5 TSR Status

The TRMT bit of the TXxSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXxREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

| Note: | The TSR register is not mapped in data      |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

|       | memory, so it is not available to the user. |  |  |  |  |  |

# 33.1.1.6 Transmitting 9-Bit Characters

The EUSART supports 9-bit character transmissions. When the TX9 bit of the TXxSTA register is set, the EUSART will shift nine bits out for each character transmitted. The TX9D bit of the TXxSTA register is the ninth, and Most Significant data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TXxREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXxREG is written.

A special 9-bit Address mode is available for use with multiple receivers. See **Section 33.1.2.7** "Address **Detection**" for more information on the Address mode.

# 33.1.1.7 Asynchronous Transmission Set-up:

- Initialize the SPxBRGH, SPxBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 33.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If 9-bit transmission is desired, set the TX9 control bit. A set ninth data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- 4. Set SCKP bit if inverted transmit is desired.

- 5. Enable the transmission by setting the TXEN control bit. This will cause the TXxIF interrupt bit to be set.

- If interrupts are desired, set the TXxIE interrupt enable bit of the PIE3 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded into the TX9D data bit.

- 8. Load 8-bit data into the TXxREG register. This will start the transmission.

# FIGURE 33-3: ASYNCHRONOUS TRANSMISSION

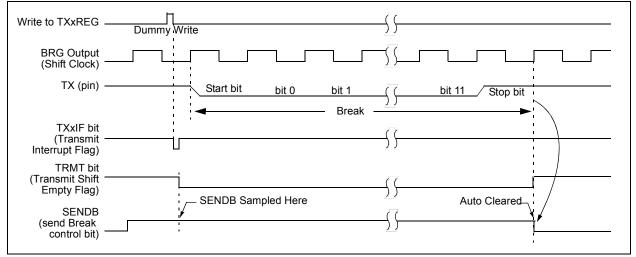

# 33.3.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RCxSTA register and the received data as indicated by RCxREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when:

- · RXxIF bit is set

- · FERR bit is set

- RCxREG = 00h

The second method uses the Auto-Wake-up feature described in **Section 33.3.3 "Auto-Wake-up on Break"**. By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RXxIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUDxCON register before placing the EUSART in Sleep mode.

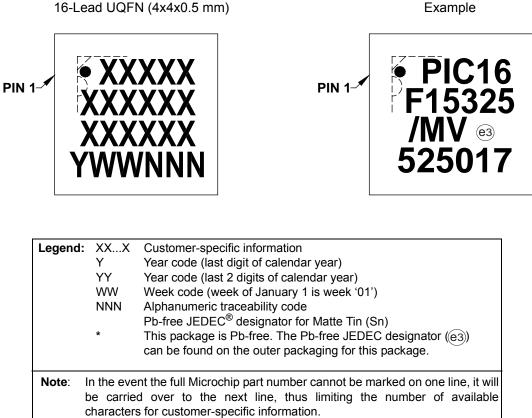

#### 40.1 Package Marking Information (Continued)

16-Lead UQFN (4x4x0.5 mm)

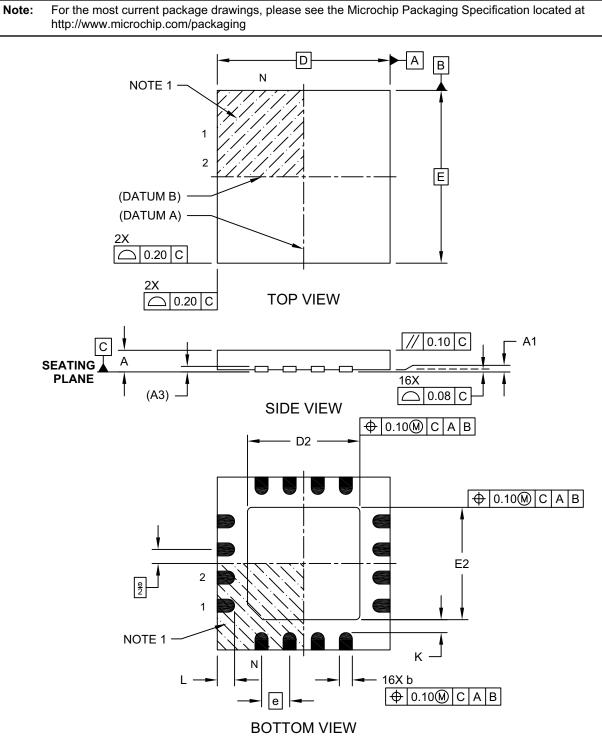

# 16-Lead Ultra Thin Plastic Quad Flat, No Lead Package (JQ) - 4x4x0.5 mm Body [UQFN]

Microchip Technology Drawing C04-257A Sheet 1 of 2

# 16-Lead Ultra Thin Plastic Quad Flat, No Lead Package (JQ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  | Ν         | <b>IILLIMETER</b> | S    |  |  |

|-------------------------|--------|-----------|-------------------|------|--|--|

| Dimension               | Limits | MIN       | NOM               | MAX  |  |  |

| Number of Pins          | N      | 16        |                   |      |  |  |

| Pitch                   | е      | 0.65 BSC  |                   |      |  |  |

| Overall Height          | Α      | 0.45      | 0.50              | 0.55 |  |  |

| Standoff                | A1     | 0.00      | 0.02              | 0.05 |  |  |

| Terminal Thickness      | A3     | 0.127 REF |                   |      |  |  |

| Overall Width           | E      |           | 4.00 BSC          |      |  |  |

| Exposed Pad Width       | E2     | 2.50      | 2.60              | 2.70 |  |  |

| Overall Length          | D      | 4.00 BSC  |                   |      |  |  |

| Exposed Pad Length      | D2     | 2.50      | 2.60              | 2.70 |  |  |

| Terminal Width          | b      | 0.25      | 0.30              | 0.35 |  |  |

| Terminal Length         | L      | 0.30      | 0.40              | 0.50 |  |  |

| Terminal-to-Exposed-Pad | K      | 0.20      | -                 | -    |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-257A Sheet 2 of 2