Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 18                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 17x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 20-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15345t-i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 4-2: MEMORY ACCESS PARTITION

|         |                                                                                                     | Partition                           |                              |                              |                                     |  |

|---------|-----------------------------------------------------------------------------------------------------|-------------------------------------|------------------------------|------------------------------|-------------------------------------|--|

| REG     | Address                                                                                             | <u>BBEN</u> = 1<br>SAFEN = 1        | <u>BBEN</u> = 1<br>SAFEN = 0 | <u>BBEN</u> = 0<br>SAFEN = 1 | <u>BBEN</u> = 0<br>SAFEN = 0        |  |

|         | 00 0000h<br>•••<br>Last Boot Block Memory<br>Address                                                |                                     | APPLICATION                  | BOOT BLOCK <sup>(4)</sup>    | BOOT BLOCK <sup>(4)</sup>           |  |

| PFM     | Last Boot Block Memory<br>Address + 1 <sup>(1)</sup><br>•••<br>Last Program Memory<br>Address - 80h | APPLICATION<br>BLOCK <sup>(4)</sup> | BLOCK <sup>(4)</sup>         | APPLICATION                  | APPLICATION<br>BLOCK <sup>(4)</sup> |  |

|         | Last Program Memory<br>Address - 7Fh <sup>(2)</sup><br>•••<br>Last Program Memory<br>Address        |                                     | SAF <sup>(4)</sup>           | BLOCK <sup>(4)</sup>         | SAF <sup>(4)</sup>                  |  |

| CONF IG | Config Memory Address <sup>(3)</sup>                                                                |                                     | COI                          | NFIG                         | 1                                   |  |

Note 1: Last Boot Block Memory Address is based on BBSIZE<2:0> given in Table 5-1.

2: Last Program Memory Address is the Flash size given in Table 4-1.

3: Config Memory Address are the address locations of the Configuration Words given in Table 13-2.

**4:** Each memory block has a corresponding write protection fuse defined by the WRTAPP, WRTB and WRTC bits in the Configuration Word (Register 5-4).

# 5.2 Register Definitions: Configuration Words

| REGISTER          | 5-1: CC                                                                                                                                                                                                                                              | NFIGURATIO                                                                                                                                                                     | N WORD 1:                                                                             | OSCILLATO                                                                     | DRS                                                            |                                       |                    |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------|--------------------|

|                   |                                                                                                                                                                                                                                                      | R/P-1                                                                                                                                                                          | U-1                                                                                   | R/P-1                                                                         | U-1                                                            | U-1                                   | R/P-1              |

|                   |                                                                                                                                                                                                                                                      | FCMEN                                                                                                                                                                          | _                                                                                     | CSWEN                                                                         | _                                                              | _                                     | CLKOUTEN           |

|                   |                                                                                                                                                                                                                                                      | bit 13                                                                                                                                                                         |                                                                                       |                                                                               |                                                                |                                       | bit                |

| U-1               | R/P-1                                                                                                                                                                                                                                                | R/P-1                                                                                                                                                                          | R/P-1                                                                                 | U-1                                                                           | R/P-1                                                          | R/P-1                                 | R/P-1              |

| _                 | RSTOSC2                                                                                                                                                                                                                                              | RSTOSC1                                                                                                                                                                        | RSTOSC0                                                                               | _                                                                             | FEXTOSC2                                                       | FEXTOSC1                              | FEXTOSC0           |

| bit 7             | 11010002                                                                                                                                                                                                                                             | 1010001                                                                                                                                                                        | 1010000                                                                               |                                                                               | TEXTOODE                                                       |                                       | bit                |

| Legend:           |                                                                                                                                                                                                                                                      |                                                                                                                                                                                |                                                                                       |                                                                               |                                                                |                                       |                    |

| R = Readable      | bit                                                                                                                                                                                                                                                  | P = Programma                                                                                                                                                                  | able bit                                                                              | x = Bit is unkn                                                               | own                                                            | U = Unimpleme<br>'1'                  | nted bit, read as  |

| '0' = Bit is clea | ared                                                                                                                                                                                                                                                 | '1' = Bit is set                                                                                                                                                               |                                                                                       | W = Writable b                                                                | bit                                                            | n = Value when<br>Erase               | blank or after Bul |

| bit 13            | FCMEN: Fail-<br>1 = FSCM ti<br>0 = FSCM ti                                                                                                                                                                                                           |                                                                                                                                                                                | or Enable bit                                                                         |                                                                               |                                                                |                                       |                    |

| bit 12            | Unimplemen                                                                                                                                                                                                                                           | ted: Read as '1'                                                                                                                                                               |                                                                                       |                                                                               |                                                                |                                       |                    |

| bit 11            | 1 = Writing t                                                                                                                                                                                                                                        | ck Switch Enable<br>to NOSC and NDI<br>SC and NDIV bits                                                                                                                        | ✓ is allowed                                                                          | nged by user sof                                                              | tware                                                          |                                       |                    |

| bit 10-9          | Unimplemen                                                                                                                                                                                                                                           | ted: Read as '1'                                                                                                                                                               |                                                                                       |                                                                               |                                                                |                                       |                    |

|                   | 1 = CLKOUT                                                                                                                                                                                                                                           | <u>= EC (high, mid or</u><br>function is disable<br>function is enable<br>ored.                                                                                                | ed; I/O or oscill                                                                     | ator function on                                                              |                                                                |                                       |                    |

| bit 7             | -                                                                                                                                                                                                                                                    | ted: Read as '1'                                                                                                                                                               |                                                                                       |                                                                               |                                                                |                                       |                    |

| bit 6-4           | This value is           111 =         EXTO           110 =         HFIN           101 =         LFIN           100 =         SOS           011 =         Rese           010 =         EXTO           011 =         Rese           010 =         EXTO | С                                                                                                                                                                              | value for COSC<br>r FEXTOSC bits<br>Q = 3'b010<br>with EXTOSC of<br>with EXTOSC of    | C and selects the<br>s (device manufa<br>operating per FE<br>operating per FE | acturing default)<br>XTOSC bits                                | ed by user softwa                     | re.                |

| bit 3             |                                                                                                                                                                                                                                                      | ted: Read as '1'                                                                                                                                                               |                                                                                       |                                                                               |                                                                |                                       |                    |

| bit 2-0           | FEXTOSC<2           111 =         EC (           110 =         EC (           101 =         EC (           100 =         Osci           011 =         Rese           010 =         HS (           001 =         XT (                                 | :0>:FEXTOSC Ex<br>External Clock) at<br>External Clock) fo<br>External Clock) be<br>Ilator not enabled<br>erved (do not use)<br>Crystal oscillator) ;<br>Crystal oscillator) ; | ove 8 MHz; PF<br>r 100 kHz to 8 ľ<br>elow 100 kHz<br>above 4 MHz; F<br>above 100 kHz, | M set to high po<br>MHz; PFM set to<br>PFM set to high<br>below 4 MHz; F      | wer (device manu<br>medium power<br>power<br>PFM set to mediur | , , , , , , , , , , , , , , , , , , , |                    |

## REGISTER 5-1: CONFIGURATION WORD 1: OSCILLATORS

## 5.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection and data memory are controlled independently. Internal access to the program memory is unaffected by any code protection setting.

#### 5.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Self-writing the program memory is dependent upon the write protection setting. See **Section 5.4** "Write **Protection**" for more information.

## 5.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as boot loader software, can be protected while allowing other regions of the program memory to be modified.

The WRTAPP, WRTSAF, WRTB, WRTC bits in Configuration Words (Register 5-4) define whether the corresponding region of the program memory block is protected or not.

### 5.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See Section 13.3.6 "NVMREG Access to Device Information Area, Device Configuration Area, User ID, Device ID and Configuration Words" for more information on accessing these memory locations. For more information on checksum calculation, see the "PIC16(L)F153xx Memory Programming Specification" (DS40001838).

#### REGISTER 17-7: IOCCP: INTERRUPT-ON-CHANGE PORTC POSITIVE EDGE REGISTER

| R/W-0/0                           | R/W-0/0               | R/W-0/0         | R/W-0/0      | R/W-0/0                                            | R/W-0/0 | R/W-0/0 | R/W-0/0      |

|-----------------------------------|-----------------------|-----------------|--------------|----------------------------------------------------|---------|---------|--------------|

| IOCCP7 <sup>(1)</sup>             | IOCCP6 <sup>(1)</sup> | IOCCP5          | IOCCP4       | IOCCP3                                             | IOCCP2  | IOCCP1  | IOCCP0       |

| bit 7                             |                       |                 |              |                                                    |         | •       | bit 0        |

|                                   |                       |                 |              |                                                    |         |         |              |

| Legend:                           |                       |                 |              |                                                    |         |         |              |

| R = Readable bit W = Writable bit |                       |                 | U = Unimpler | nented bit, read                                   | as '0'  |         |              |

| u = Bit is uncha                  | anged                 | x = Bit is unkr | iown         | -n/n = Value at POR and BOR/Value at all other Res |         |         | other Resets |

bit 7-0

'1' = Bit is set

IOCCP<7:0>: Interrupt-on-Change PORTC Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive-going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin

'0' = Bit is cleared

#### REGISTER 17-8: IOCCN: INTERRUPT-ON-CHANGE PORTC NEGATIVE EDGE REGISTER

| R/W-0/0               | R/W-0/0               | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-----------------------|-----------------------|---------|---------|---------|---------|---------|---------|

| IOCCN7 <sup>(1)</sup> | IOCCN6 <sup>(1)</sup> | IOCCN5  | IOCCN4  | IOCCN3  | IOCCN2  | IOCCN1  | IOCCN0  |

| bit 7                 |                       |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

**IOCCN<7:0>:** Interrupt-on-Change PORTC Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative-going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin

#### REGISTER 17-9: IOCCF: INTERRUPT-ON-CHANGE PORTC FLAG REGISTER

| R/W/HS-0/0            | R/W/HS-0/0            | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-----------------------|-----------------------|------------|------------|------------|------------|------------|------------|

| IOCCF7 <sup>(1)</sup> | IOCCF6 <sup>(1)</sup> | IOCCF5     | IOCCF4     | IOCCF3     | IOCCF2     | IOCCF1     | IOCCF0     |

| bit 7                 |                       |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0 **IOCCF<7:0>:** Interrupt-on-Change PORTC Flag bits

- 1 = An enabled change was detected on the associated pin

- Set when IOCCPx = 1 and a rising edge was detected on RCx, or when IOCCNx = 1 and a falling edge was detected on RCx.

- 0 = No change was detected, or the user cleared the detected change

**Note 1:** Present only on the PIC16(L)F15345 20-pin devices.

| FIGURE 26-6:           | TIMER1 GATE SINGLE-PULSE AND TOGGLE COMBINED MODE                                                                                        |        |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------|

| TMRxGE                 |                                                                                                                                          |        |

| TxGPOL                 |                                                                                                                                          |        |

| TxGSPM                 |                                                                                                                                          |        |

| TxGTM                  |                                                                                                                                          |        |

| TxGG <u>O/</u><br>DONE | ← Cleared by hardware c<br>← Cleared by hardware c<br>falling edge of TxGVAL<br>Counting enabled on<br>rising edge of selected source    | n<br>- |

| Selected gate          |                                                                                                                                          |        |

| ТхСКІ                  |                                                                                                                                          |        |

| TxGVAL                 |                                                                                                                                          |        |

| TMRxH:TMRxL<br>Count   | $N \qquad \qquad$ |        |

| TMRxGIF                | Set by hardware on Cleared by software falling edge of TxGVAL> Cleared by software                                                       |        |

### 27.4 Timer2 Interrupt

Timer2 can also generate a device interrupt. The interrupt is generated when the postscaler counter matches one of 16 postscale options (from 1:1 through 1:16), which are selected with the postscaler control bits, OUTPS<3:0> of the T2CON register. The interrupt is enabled by setting the TMR2IE interrupt enable bit of the PIE4 register. Interrupt timing is illustrated in Figure 27-3.

| FIGURE 27-3: | TIMER2 PRESCALER, POSTSCALER, AND INTERRUPT TIMING DIAGRAM |

|--------------|------------------------------------------------------------|

|              |                                                            |

|                 | Rev. 10-000005<br>47/2010                                |        |

|-----------------|----------------------------------------------------------|--------|

| CKPS            | 0b010                                                    |        |

|                 |                                                          | L<br>L |

| PRx             | 1                                                        |        |

|                 | 01.000.4                                                 | ٦      |

| OUTPS           | 0b0001                                                   |        |

| TMRx_clk        |                                                          | -      |

| TMRx            |                                                          | )      |

| TMRx_postscaled |                                                          | _      |

| TMRxIF          | (1) (1)                                                  | -      |

| Note 1:<br>2:   | Synchronization may take as many as 2 instruction cycles |        |

## 28.0 CAPTURE/COMPARE/PWM MODULES

The Capture/Compare/PWM module is a peripheral that allows the user to time and control different events, and to generate Pulse-Width Modulation (PWM) signals. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate Pulse-Width Modulated signals of varying frequency and duty cycle.

The Capture/Compare/PWM modules available are shown in Table 28-1.

| TABLE 28-1: A | VAILABLE CCP | MODULES |

|---------------|--------------|---------|

|---------------|--------------|---------|

| Device            | CCP1 | CCP2 |

|-------------------|------|------|

| PIC16(L)F15325/45 | •    | •    |

The Capture and Compare functions are identical for all CCP modules.

- Note 1: In devices with more than one CCP module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the CCP1CON and CCP2CON control the same operational aspects of two completely different CCP modules.

- 2: Throughout this section, generic references to a CCP module in any of its operating modes may be interpreted as being equally applicable to CCPx module. Register names, module signals, I/O pins, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

| Name     | Bit 7                 | Bit 6                                        | Bit 5       | Bit 4       | Bit 3  | Bit 2      | Bit 1      | Bit 0  | Register<br>on Page |  |

|----------|-----------------------|----------------------------------------------|-------------|-------------|--------|------------|------------|--------|---------------------|--|

| T2CON    | ON                    | CKPS<2:0>                                    |             |             |        |            | OUTPS<3:0> |        |                     |  |

| T2TMR    | Holding Regi          | Holding Register for the 8-bit TMR2 Register |             |             |        |            |            |        | 290*                |  |

| T2PR     | TMR2 Period           | TMR2 Period Register                         |             |             |        |            |            |        | 290*                |  |

| RxyPPS   | —                     | _                                            | —           |             | R      | xyPPS<4:0> |            |        | 200                 |  |

| CWG1ISM  | —                     | _                                            | —           | — — IS<3:0> |        |            |            |        | 356                 |  |

| CLCxSELy | _                     | _                                            | LCxDyS<5:0> |             |        |            |            | 367    |                     |  |

| TRISA    | —                     | _                                            | TRISA5      | TRISA4      | —      | TRISA2     | TRISA1     | TRISA0 | 178                 |  |

| TRISC    | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup>                        | TRISC5      | TRISC4      | TRISC3 | TRISC2     | TRISC1     | TRISC0 | 189                 |  |

Legend: - = Unimplemented locations, read as '0'. Shaded cells are not used by the PWMx module.

\* Page with Register information.

Note 1: Present on PIC16(L)F15345 only.

| R/W/HS-0/0                                                                                                                                  | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0/0          | R/W-1/1 | R/W-0/0        | R/W-1/1         | U-0            | U-0            |

|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------|----------------|-----------------|----------------|----------------|

| SHUTDOWN <sup>(1, 2)</sup>                                                                                                                  | REN                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  | )<1:0>  | LSAC           | <1:0>           | _              | _              |

| bit 7                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |         |                |                 |                | bit 0          |

|                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |         |                |                 |                |                |

| Legend:                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |         |                |                 |                |                |

| HC = Bit is cleared                                                                                                                         | by hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |         | HS = Bit is se | et by hardware  | 9              |                |

| R = Readable bit                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | W = Writable     | bit     | U = Unimpler   | nented bit, rea | ad as 'O'      |                |

| u = Bit is unchange                                                                                                                         | ed                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | x = Bit is unk   | nown    | -n/n = Value a | at POR and B    | OR/Value at al | I other Resets |

| '1' = Bit is set                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | '0' = Bit is cle | eared   | q = Value dep  | pends on conc   | dition         |                |

| bit 7 <b>SHUTDOWN:</b> Auto-Shutdown Event Status bit<br>1 = An Auto-Shutdown state is in effect<br>0 = No Auto-shutdown event has occurred |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |         |                |                 |                |                |

| bit 6                                                                                                                                       | REN: Auto-R<br>1 = Auto-res<br>0 = Auto-res                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  | bit     |                |                 |                |                |

| bit 5-4                                                                                                                                     | LSBD<1:0>: CWG1B and CWG1D Auto-Shutdown State Control bits<br>11 =A logic '1' is placed on CWG1B/D when an auto-shutdown event is present<br>10 =A logic '0' is placed on CWG1B/D when an auto-shutdown event is present<br>01 =Pin is tri-stated on CWG1B/D when an auto-shutdown event is present<br>00 =The inactive state of the pin, including polarity, is placed on CWG1B/D after the required dead-<br>band interval                                                    |                  |         |                |                 |                |                |

| bit 3-2                                                                                                                                     | <ul> <li>LSAC&lt;1:0&gt;: CWG1A and CWG1C Auto-Shutdown State Control bits</li> <li>11 =A logic '1' is placed on CWG1A/C when an auto-shutdown event is present</li> <li>10 =A logic '0' is placed on CWG1A/C when an auto-shutdown event is present</li> <li>01 =Pin is tri-stated on CWG1A/C when an auto-shutdown event is present</li> <li>00 =The inactive state of the pin, including polarity, is placed on CWG1A/C after the required dead-<br/>band interval</li> </ul> |                  |         |                |                 |                |                |

| bit 1-0 Unimplemented: Read as '0'                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |         |                |                 |                |                |

|                                                                                                                                             | <b>Note 1:</b> This bit may be written while EN = 0 (CWG1CON0 register) to place the outputs into the shutdown configuration.                                                                                                                                                                                                                                                                                                                                                    |                  |         |                |                 |                |                |

## REGISTER 30-5: CWG1AS0: CWG1 AUTO-SHUTDOWN CONTROL REGISTER 0

2: The outputs will remain in auto-shutdown state until the next rising edge of the input signal after this bit is cleared.

| U-1                                      | U-1                             | U-1                                                                       | R/W-0/0     | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |  |  |  |

|------------------------------------------|---------------------------------|---------------------------------------------------------------------------|-------------|----------------|------------------|------------------|-------------|--|--|--|

| —                                        | —                               | —                                                                         | AS4E        | AS3E           | AS2E             | AS1E             | AS0E        |  |  |  |

| bit 7                                    |                                 |                                                                           |             |                |                  |                  | bit 0       |  |  |  |

|                                          |                                 |                                                                           |             |                |                  |                  |             |  |  |  |

| Legend:                                  |                                 |                                                                           |             |                |                  |                  |             |  |  |  |

| R = Readabl                              | e bit                           | W = Writable                                                              | bit         | U = Unimplei   | mented bit, read | l as '0'         |             |  |  |  |

| u = Bit is und                           | changed                         | x = Bit is unkr                                                           | iown        | -n/n = Value   | at POR and BO    | R/Value at all c | ther Resets |  |  |  |

| '1' = Bit is se                          | t                               | '0' = Bit is clea                                                         | ared        | q = Value de   | pends on condit  | ion              |             |  |  |  |

|                                          |                                 |                                                                           |             |                |                  |                  |             |  |  |  |

| bit 7-5                                  | Unimplemen                      | ted: Read as '                                                            | )'          |                |                  |                  |             |  |  |  |

| bit 4                                    | AS4E: CLC2                      | Output bit                                                                |             |                |                  |                  |             |  |  |  |

|                                          |                                 | 1 = LC2_out shut-down is enabled                                          |             |                |                  |                  |             |  |  |  |

|                                          | 0 = LC2_out                     | shut-down is d                                                            | isabled     |                |                  |                  |             |  |  |  |

| bit 3                                    | AS3E: Compa                     | arator C2 Outp                                                            | ut bit      |                |                  |                  |             |  |  |  |

|                                          |                                 | 1 = C2 output shut-down is enabled<br>0 = C2 output shut-down is disabled |             |                |                  |                  |             |  |  |  |

| L:1 0                                    | •                               |                                                                           |             |                |                  |                  |             |  |  |  |

| bit 2                                    | •                               | arator C1 Outp                                                            |             |                |                  |                  |             |  |  |  |

|                                          | •                               | 1 = C1 output shut-down is enabled<br>0 = C1 output shut-down is disabled |             |                |                  |                  |             |  |  |  |

| bit 2                                    | AS1E: TMR2 Postscale Output bit |                                                                           |             |                |                  |                  |             |  |  |  |

| 5112                                     |                                 | 1 = TMR2 Postscale shut-down is enabled                                   |             |                |                  |                  |             |  |  |  |

| 0 = TMR2 Postscale shut-down is disabled |                                 |                                                                           |             |                |                  |                  |             |  |  |  |

| bit 0 AS0E: CWG1 Input Pin bit           |                                 |                                                                           |             |                |                  |                  |             |  |  |  |

|                                          |                                 | selected by CV                                                            |             |                |                  |                  |             |  |  |  |

|                                          | 0 = Input pin                   | selected by CV                                                            | VG1PPS shut | -down is disab | led              |                  |             |  |  |  |

## REGISTER 30-6: CWG1AS1: CWG1 AUTO-SHUTDOWN CONTROL REGISTER 1

| R/W-x/u          | R/W-x/u                                             | R/W-x/u                                                                                                                  | R/W-x/u         | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |  |  |  |

|------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|------------------|------------------|-------------|--|--|--|

| LCxG3D4T         | LCxG3D4N                                            | LCxG3D3T                                                                                                                 | LCxG3D3N        | LCxG3D2T       | LCxG3D2N         | LCxG3D1T         | LCxG3D1N    |  |  |  |

| bit 7            |                                                     |                                                                                                                          |                 |                |                  |                  | bit (       |  |  |  |

|                  |                                                     |                                                                                                                          |                 |                |                  |                  |             |  |  |  |

| Legend:          |                                                     |                                                                                                                          |                 |                |                  | ( <b>a</b> )     |             |  |  |  |

| R = Readable     |                                                     | W = Writable                                                                                                             |                 |                | nented bit, read |                  |             |  |  |  |

| u = Bit is unch  | anged                                               | x = Bit is unkr                                                                                                          |                 | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |  |  |  |

| '1' = Bit is set |                                                     | '0' = Bit is clea                                                                                                        | ared            |                |                  |                  |             |  |  |  |

| bit 7            |                                                     | Noto 2 Doto 4 1                                                                                                          | True (non inve  | rtad) bit      |                  |                  |             |  |  |  |

|                  |                                                     | Gate 2 Data 4 1<br>(true) is gated i                                                                                     |                 | ,              |                  |                  |             |  |  |  |

|                  |                                                     | (true) is not gate                                                                                                       |                 |                |                  |                  |             |  |  |  |

| bit 6            |                                                     | Gate 2 Data 4 I                                                                                                          |                 |                |                  |                  |             |  |  |  |

|                  |                                                     | (inverted) is ga                                                                                                         | •               |                |                  |                  |             |  |  |  |

|                  | 0 = CLCIN3 (inverted) is not gated into CLCx Gate 2 |                                                                                                                          |                 |                |                  |                  |             |  |  |  |

| bit 5            | LCxG3D3T: 0                                         | LCxG3D3T: Gate 2 Data 3 True (non-inverted) bit                                                                          |                 |                |                  |                  |             |  |  |  |

|                  | 1 = CLCIN2 (                                        | 1 = CLCIN2 (true) is gated into CLCx Gate 2                                                                              |                 |                |                  |                  |             |  |  |  |

|                  | 0 = CLCIN2                                          | (true) is not gat                                                                                                        | ed into CLCx    | Gate 2         |                  |                  |             |  |  |  |

| bit 4            | LCxG3D3N:                                           | Gate 2 Data 3                                                                                                            | Negated (inver  | rted) bit      |                  |                  |             |  |  |  |

|                  |                                                     | <ul> <li>CLCIN2 (inverted) is gated into CLCx Gate 2</li> <li>CLCIN2 (inverted) is not gated into CLCx Gate 2</li> </ul> |                 |                |                  |                  |             |  |  |  |

|                  |                                                     | , ,                                                                                                                      | •               |                |                  |                  |             |  |  |  |

| bit 3            |                                                     | Gate 2 Data 2 T                                                                                                          | · ·             |                |                  |                  |             |  |  |  |

|                  |                                                     | (true) is gated i<br>(true) is not gat                                                                                   |                 |                |                  |                  |             |  |  |  |

| bit 2            |                                                     | Gate 2 Data 2                                                                                                            |                 |                |                  |                  |             |  |  |  |

|                  |                                                     | (inverted) is ga                                                                                                         | • ·             | ,              |                  |                  |             |  |  |  |

|                  |                                                     | (inverted) is no                                                                                                         |                 |                |                  |                  |             |  |  |  |

| bit 1            |                                                     | Sate 2 Data 1 1                                                                                                          | •               |                |                  |                  |             |  |  |  |

|                  |                                                     | N0 (true) is gated into CLCx Gate 2                                                                                      |                 |                |                  |                  |             |  |  |  |

|                  | 0 = CLCIN0                                          | (true) is not gat                                                                                                        | ted into CLCx   | Gate 2         |                  |                  |             |  |  |  |

| bit 0            | LCxG3D1N:                                           | Gate 2 Data 1 I                                                                                                          | Negated (inver  | rted) bit      |                  |                  |             |  |  |  |

|                  |                                                     | (inverted) is ga                                                                                                         |                 |                |                  |                  |             |  |  |  |

|                  | 0 = CLCIN0                                          | (inverted) is no                                                                                                         | t gated into Cl | Cx Gate 2      |                  |                  |             |  |  |  |

## REGISTER 31-9: CLCxGLS2: GATE 2 LOGIC SELECT REGISTER

| TABLE 31-4: | SUMMARY OF REGISTERS ASSOCIATED WITH CLCx (continued) |

|-------------|-------------------------------------------------------|

|-------------|-------------------------------------------------------|

| Name      | Bit 7 | Bit 6 | Bit 5          | Bit 4          | Bit 3    | Bit 2    | Bit 1    | Bit 0    |     |

|-----------|-------|-------|----------------|----------------|----------|----------|----------|----------|-----|

| CLC4GLS1  | —     | _     | LC4G2D3T       | LC4G2D3N       | LC4G2D2T | LC4G2D2N | LC4G2D1T | LC4G2D1N | 369 |

| CLC4GLS2  | _     | _     | LC4G3D3T       | LC4G3D3N       | LC4G3D2T | LC4G3D2N | LC4G3D1T | LC4G3D1N | 370 |

| CLC4GLS3  | _     | _     | LC4G4D3T       | LC4G4D3N       | LC4G4D2T | LC4G4D2N | LC4G4D1T | LC4G4D1N | 371 |

| CLCIN0PPS | _     | _     |                | CLCIN0PPS<5:0> |          |          |          |          |     |

| CLCIN1PPS | _     | _     |                | CLCIN1PPS<5:0> |          |          |          |          |     |

| CLCIN2PPS | _     | _     | CLCIN2PPS<5:0> |                |          |          |          |          | 199 |

| CLCIN3PPS | _     | _     |                | CLCIN3PPS<5:0> |          |          |          |          |     |

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the CLCx modules.

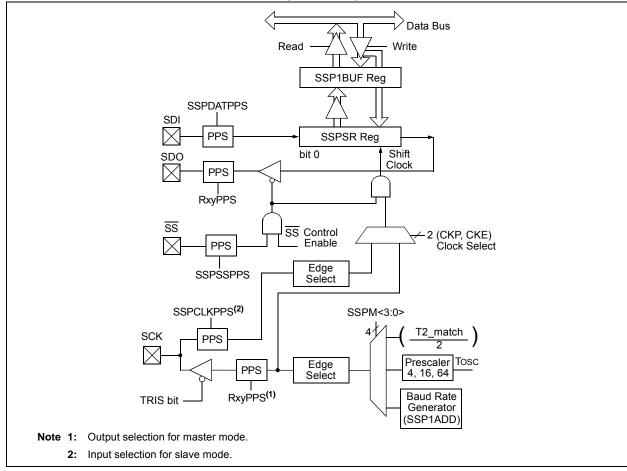

## 32.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP1) MODULE

## 32.1 MSSP Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

The SPI interface supports the following modes and features:

- Master mode

- Slave mode

- Clock Parity

- Slave Select Synchronization (Slave mode only)

- · Daisy-chain connection of slave devices

Figure 32-1 is a block diagram of the SPI interface module.

### 33.3 EUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUDxCON register selects 16-bit mode.

The SPxBRGH, SPxBRGL register pair determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by both the BRGH bit of the TXxSTA register and the BRG16 bit of the BAUDxCON register. In Synchronous mode, the BRGH bit is ignored.

Table 33-1 contains the formulas for determining the baud rate. Example 33-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various Asynchronous modes have been computed for your convenience and are shown in Table 33-3. It may be advantageous to use the high baud rate (BRGH = 1), or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SPxBRGH, SPxBRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is idle before changing the system clock.

### EXAMPLE 33-1: CALCULATING BAUD RATE ERROR

# 37.2 Standard Operating Conditions

| 37.2 Standard Operating Conditions                                                            |  |

|-----------------------------------------------------------------------------------------------|--|

| The standard operating conditions for any device are defined as:                              |  |

| Operating Voltage: $VDDMIN \le VDD \le VDDMAX$ Operating Temperature:TA_MIN \le TA \le TA_MAX |  |

| VDD — Operating Supply Voltage <sup>(1)</sup>                                                 |  |

| PIC16LF15325/45                                                                               |  |

| VDDMIN (Fosc ≤ 16 MHz) +1.8V                                                                  |  |

| VDDMIN (Fosc ≤ 32 MHz)                                                                        |  |

| VDDMAX                                                                                        |  |

| PIC16F15325/45                                                                                |  |

| VDDMIN (Fosc ≤ 16 MHz)                                                                        |  |

| VDDMIN (Fosc ≤ 32 MHz)                                                                        |  |

| VDDMAX                                                                                        |  |

| TA — Operating Ambient Temperature Range                                                      |  |

| Industrial Temperature                                                                        |  |

| Ta_min                                                                                        |  |

| Ta_max                                                                                        |  |

| Extended Temperature                                                                          |  |

| TA_MIN                                                                                        |  |

| Ta_max                                                                                        |  |

| Note 1: See Parameter Supply Voltage, DS Characteristics: Supply Voltage.                     |  |

| TABLE 37-9: PLL SI | PECIFICATIONS |

|--------------------|---------------|

|--------------------|---------------|

|                                                      | •••••                                                                   | 0 0                                     |       |       |                     | Δ     |            |  |  |  |

|------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------|-------|-------|---------------------|-------|------------|--|--|--|

| Standar                                              | Standard Operating Conditions (unless otherwise stated) VDD $\ge 2.5$ V |                                         |       |       |                     |       |            |  |  |  |

| Param.<br>No.                                        | Sym.                                                                    | Characteristic                          | Min.  | Тур†  | Max.                | Units | Conditions |  |  |  |

| PLL01                                                | FPLLIN                                                                  | PLL Input Frequency Range               | 4     | _     | 8                   | MHz   | $\searrow$ |  |  |  |

| PLL02                                                | FPLLOUT                                                                 | PLL Output Frequency Range              | 16    | —     | 32                  | MHz   | Note 1     |  |  |  |

| PLL03                                                | TPLLST                                                                  | PLL Lock Time from Start-up             | _     | 200 🦯 | $\langle - \rangle$ | _µ\$  | -          |  |  |  |

| PLL04                                                | FPLLJIT                                                                 | PLL Output Frequency Stability (Jitter) | -0.25 | _ \   | 0.25                | ~%/   |            |  |  |  |

| * These parameters are characterized but not tested. |                                                                         |                                         |       |       |                     |       |            |  |  |  |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance t only and are not tested.

Note 1: The output frequency of the PLL must meet the Fosc requirements listed in Parameter D002.

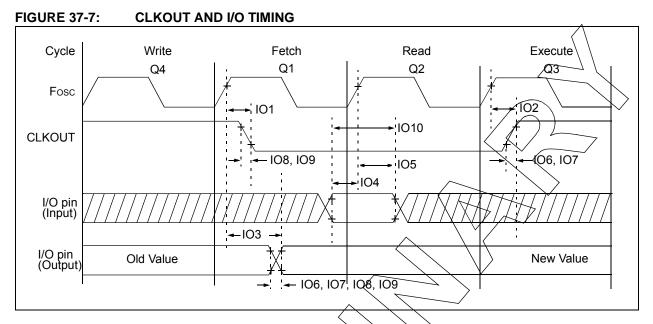

| TABLE 37-10: | I/O AND CLKOUT TIMING SPECIFICATIONS |

|--------------|--------------------------------------|

|--------------|--------------------------------------|

| Param.<br>No. | Sym.                  | Characteristic                                                                     | Min. | Тур† | Max. | Units | Conditions |

|---------------|-----------------------|------------------------------------------------------------------------------------|------|------|------|-------|------------|

| IO1*          | T <sub>CLKOUTH</sub>  | CLKOUT rising edge delay (rising<br>edge Fosc (Q1 cycle) to falling edge<br>CLKOUT | > -  | -    | 70   | ns    |            |

| 102*          | T <sub>CLKOUTL</sub>  | CLKOUT falling edge delay (rising<br>edge Fosc (Q3 cycle) to rising edge<br>CLKOUT | _    | —    | 72   | ns    |            |

| 103*          | T <sub>IO_VALID</sub> | Port output valid time (rising edge<br>Fose (Q1 cycle) to port valid)              | —    | 50   | 70   | ns    |            |

| 104*          | T <sub>IO_SETUP</sub> | Port input setup time (Setup time<br>before rising edge Fosc – Q2 cycle)           | 20   | —    | —    | ns    |            |

| 105*          | T <sub>IO_HOLD</sub>  | Port input hold time (Hold time after rising edge Fosc – Q2 cycle)                 | 50   | —    | —    | ns    |            |

| 106*          | TIOR_SLREN            | Port I/O rise time, slew rate enabled                                              | _    | 25   | —    | ns    | VDD = 3.0V |

| 107*          | TIOR SLADIS           | Port I/O rise time, slew rate disabled                                             | _    | 5    | —    | ns    | VDD = 3.0V |

| 08*           | FIOF SLREN            | Port I/O fall time, slew rate enabled                                              | _    | 25   | —    | ns    | VDD = 3.0V |

| 09*/          |                       | Port I/O fall time, slew rate disabled                                             | —    | 5    | —    | ns    | VDD = 3.0V |

|               | FINT                  | INT pin high or low time to trigger an interrupt                                   | 25   | -    | _    | ns    |            |

| 011*          | T.OC                  | Interrupt-on-Change minimum high or<br>low time to trigger interrupt               | 25   | —    | —    | ns    |            |

| Standard Operating Conditions (unless otherwise st | ate  | d  | $\angle$ |

|----------------------------------------------------|------|----|----------|

| Standard Operating Conditions (unless otherwise si | ιαις | u) |          |

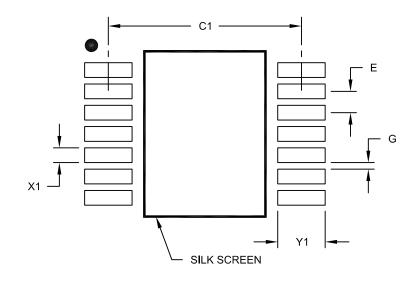

## 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                          | MILLIMETERS      |      |          |      |  |

|--------------------------|------------------|------|----------|------|--|

| Dimension                | Dimension Limits |      | NOM      | MAX  |  |

| Contact Pitch            | E                |      | 0.65 BSC |      |  |

| Contact Pad Spacing      | C1               |      | 5.90     |      |  |

| Contact Pad Width (X14)  | X1               |      |          | 0.45 |  |

| Contact Pad Length (X14) | Y1               |      |          | 1.45 |  |

| Distance Between Pads    | G                | 0.20 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2087A

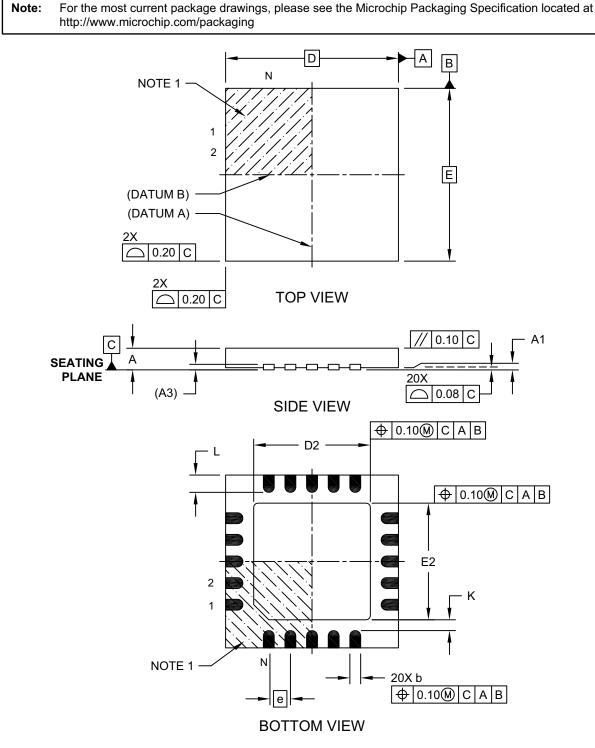

## 20-Lead Ultra Thin Plastic Quad Flat, No Lead Package (GZ) - 4x4x0.5 mm Body [UQFN]

Microchip Technology Drawing C04-255A Sheet 1 of 2