# Microchip Technology - PIC16LF15325-E/P Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 224 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 14-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15325-e-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 10.5 "Automatic Context Saving"** for more information.

## 3.2 16-Level Stack with Overflow and Underflow

These devices have a hardware stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled, will cause a software Reset. See **Section 4.5 "Stack**" for more details.

# 3.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. See **Section 4.6 "Indirect Addressing"** for more details.

# 3.4 Instruction Set

There are 48 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 36.0 "Instruction Set Summary**" for more details.

# TABLE 4-5:PIC16(L)F15325/45 MEMORY MAP, BANKS 8-15

|      | BANK 8        |      | BANK 9        |      | BANK 10       |      | BANK 11       |           | BANK 12       |      | BANK 13       |      | BANK 14       |      | BANK 15       |

|------|---------------|------|---------------|------|---------------|------|---------------|-----------|---------------|------|---------------|------|---------------|------|---------------|

| 400h |               | 480h |               | 500h |               | 580h |               | 600h      |               | 680h |               | 700h |               | 780h |               |

|      | Core Register |      | Core Register |      | Core Register |      | Core Register |           | Core Register |      | Core Register |      | Core Register |      | Core Register |

|      | (Table 4-3)   |      | (Table 4-3)   |      | (Table 4-3)   |      | (Table 4-3)   |           | (Table 4-3)   |      | (Table 4-3)   |      | (Table 4-3)   |      | (Table 4-3)   |

| 40Bh |               | 48Bh |               | 50Bh |               | 58Bh |               | 60Bh      |               | 68Bh |               | 70Bh |               | 78Bh |               |

| 40Ch | —             | 48Ch | _             | 50Ch | _             | 58Ch | NCO1ACCL      | 60Ch      | CWG1CLK       | 68Ch | _             | 70Ch | PIR0          | 78Ch | _             |

| 40Dh | —             | 48Dh | _             | 50Dh | _             | 58Dh | NCO1ACCH      | 60Dh      | CWG1DAT       | 68Dh |               | 70Dh | PIR1          | 78Dh | —             |

| 40Eh | —             | 48Eh | _             | 50Eh | _             | 58Eh | NCO1ACCU      | 60Eh      | CWG1DBR       | 68Eh | _             | 70Eh | PIR2          | 78Eh | _             |

| 40Fh | —             | 48Fh | _             | 50Fh | _             | 58Fh | NCO1INCL      | 60Fh      | CWG1DBF       | 68Fh | —             | 70Fh | PIR3          | 78Fh | _             |

| 410h | —             | 490h | —             | 510h | —             | 590h | NCO1INCH      | 610h      | CWG1CON0      | 690h | —             | 710h | PIR4          | 790h |               |

| 411h | _             | 491h | _             | 511h | —             | 591h | NCO1INCU      | 611h      | CWG1CON1      | 691h | —             | 711h | PIR5          | 791h |               |

| 412h | —             | 492h | —             | 512h | —             | 592h | NCO1CON       | 612h      | CWG1AS0       | 692h | —             | 712h | PIR6          | 792h | —             |

| 413h | —             | 493h | —             | 513h | —             | 593h | NCO1CLK       | 613h      | CWG1AS1       | 693h | —             | 713h | PIR7          | 793h | —             |

| 414h | _             | 494h | —             | 514h | —             | 594h | —             | 614h      | CWG1STR       | 694h |               | 714h |               | 794h | —             |

| 415h |               | 495h | —             | 515h | —             | 595h | —             | 615h      | —             | 695h | _             | 715h | _             | 795h | —             |

| 416h | _             | 496h | —             | 516h | —             | 596h | —             | 616h      | —             | 696h | _             | 716h | PIE0          | 796h | PMD0          |

| 417h | -             | 497h | _             | 517h | —             | 597h | —             | 617h      | —             | 697h | —             | 717h | PIE1          | 797h | PMD1          |

| 418h |               | 498h | _             | 518h | _             | 598h | _             | 618h      | _             | 698h | _             | 718h | PIE2          | 798h | PMD2          |

| 419h |               | 499h | _             | 519h | _             | 599h | _             | 619h      | _             | 699h | _             | 719h | PIE3          | 799h | PMD3          |

| 41Ah |               | 49Ah | _             | 51Ah | _             | 59Ah | _             | 61Ah      | _             | 69Ah | _             | 71Ah | PIE4          | 79Ah | PMD4          |

| 41Bh | _             | 49Bh | _             | 51Bh | —             | 59Bh | —             | 61Bh      | _             | 69Bh | —             | 71Bh | PIE5          | 79Bh | PMD5          |

| 41Ch |               | 49Ch | _             | 51Ch | _             | 59Ch | TMR0          | 61Ch      | _             | 69Ch | _             | 71Ch | PIE6          | 79Ch | _             |

| 41Dh | _             | 49Dh | _             | 51Dh | —             | 59Dh | PR0           | 61Dh      | _             | 69Dh | —             | 71Dh | PIE7          | 79Dh |               |

| 41Eh | _             | 49Eh | _             | 51Eh | —             | 59Eh | TMR0CON0      | 61Eh      | _             | 69Eh | —             | 71Eh | —             | 79Eh |               |

| 41Fh | _             | 49Fh | _             | 51Fh | _             | 59Fh | TMR0CON1      | 61Fh      | _             | 69Fh | —             | 71Fh | —             | 79Fh | _             |

| 420h |               | 4A0h |               | 520h |               | 5A0h |               | 620h      |               | 6A0h |               | 720h |               | 7A0h |               |

|      | General       |      | General       |      | General       |      | General       |           | General       |      |               |      |               |      |               |

|      | Purpose       |      | Purpose       |      | Purpose       |      | Purpose       |           | Purpose       |      | Unimplemented |      | Unimplemented |      | Unimplemented |

|      | Register      |      | Register      |      | Register      |      | Register      |           | Register      |      | ·             |      |               |      |               |

|      | 80 Bytes      |      | 80 Bytes      |      | 80 Bytes      |      | 80 Bytes      | 64Fh      | 48 Bytes      |      | Read as '0'   |      | Read as '0'   |      | Read as '0'   |

|      |               |      |               |      |               |      |               | • · · · · | Unimplemented |      |               |      |               |      |               |

| 46Fh |               | 4EFh |               | 56Fh |               | 5EFh |               | 66Fh      | Read as '0'   | 6EFh |               | 76Fh |               | 7EFh |               |

| 470h | Common RAM    | 4F0h | Common RAM    | 570h | Common RAM    | 5F0h | Common RAM    | 670h      | Common RAM    | 6F0h | Common RAM    | 770h | Common RAM    | 7F0h | Common RAM    |

|      | Accesses      |      | Accesses      |      | Accesses      |      | Accesses      |           | Accesses      |      | Accesses      |      | Accesses      |      | Accesses      |

| 47Fh | 70h-7Fh       | 4FFh | 70h-7Fh       | 57Fh | 70h-7Fh       | 5FFh | 70h-7Fh       | 67Fh      | 70h-7Fh       | 6FFh | 70h-7Fh       | 77Fh | 70h-7Fh       | 7FFh | 70h-7Fh       |

Note 1: Unimplemented locations read as '0'.

-n/n = Value at POR and BOR/Value at all other Resets

| U-0                               | U-0 | R/W-0/0 | R/W-0/0      | U-0              | U-0    | U-0 | R/W-0/0 |

|-----------------------------------|-----|---------|--------------|------------------|--------|-----|---------|

| —                                 | _   | TMR0IE  | IOCIE        |                  | —      | —   | INTE    |

| bit 7                             |     |         |              |                  |        |     | bit 0   |

|                                   |     |         |              |                  |        |     |         |

| Legend:                           |     |         |              |                  |        |     |         |

| R = Readable bit W = Writable bit |     |         | U = Unimpler | mented bit, read | as '0' |     |         |

HS = Hardware set

## REGISTER 10-2: PIE0: PERIPHERAL INTERRUPT ENABLE REGISTER 0

x = Bit is unknown

'0' = Bit is cleared

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                               |  |  |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| bit 5   | <b>TMROIE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt                                                                                  |  |  |  |  |  |

|         | 0 = Disables the Timer0 interrupt                                                                                                                                        |  |  |  |  |  |

| bit 4   | <ul> <li>IOCIE: Interrupt-on-Change Interrupt Enable bit</li> <li>1 = Enables the IOC change interrupt</li> <li>0 = Disables the IOC change interrupt</li> </ul>         |  |  |  |  |  |

| bit 3-1 | Unimplemented: Read as '0'                                                                                                                                               |  |  |  |  |  |

| bit 0   | <ul> <li>INTE: INT External Interrupt Flag bit<sup>(1)</sup></li> <li>1 = Enables the INT external interrupt</li> <li>0 = Disables the INT external interrupt</li> </ul> |  |  |  |  |  |

Note 1: The External Interrupt GPIO pin is selected by INTPPS (Register 15-1).

| Note: | Bit PEIE of the INTCON register must be    |

|-------|--------------------------------------------|

|       | set to enable any peripheral interrupt     |

|       | controlled by PIE1-PIE7. Interrupt sources |

|       | controlled by the PIE0 register do not     |

|       | require PEIE to be set in order to allow   |

|       | interrupt vectoring (when GIE is set).     |

u = Bit is unchanged

'1' = Bit is set

# 13.0 NONVOLATILE MEMORY (NVM) CONTROL

NVM consists of the Program Flash Memory (PFM).

NVM is accessible by using both the FSR and INDF registers, or through the NVMREG register interface.

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

NVM can be protected in two ways; by either code protection or write protection.

Code protection (CP bit in Configuration Word 5) disables access, reading and writing, to the PFM via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be Reset by a device programmer performing a Bulk Erase to the device, clearing all nonvolatile memory, Configuration bits, and User IDs.

Write protection prohibits self-write and erase to a portion or all of the PFM, as defined by the WRT<1:0> bits of Configuration Word 4. Write protection does not affect a device programmer's ability to read, write, or erase the device.

# 13.1 Program Flash Memory (PFM)

PFM consists of an array of 14-bit words as user memory, with additional words for User ID information, Configuration words, and interrupt vectors. PFM provides storage locations for:

- User program instructions

- User defined data

PFM data can be read and/or written to through:

- CPU instruction fetch (read-only)

- FSR/INDF indirect access (read-only) (Section 13.2 "FSR and INDF Access")

- NVMREG access (Section 13.3 "NVMREG Access"

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

Read operations return a single word of memory. When write and erase operations are done on a row basis, the row size is defined in Table 13-1. PFM will erase to a logic '1' and program to a logic '0'.

## TABLE 13-1: FLASH MEMORY ORGANIZATION BY DEVICE

| Device         | Row<br>Erase<br>(words) | Write<br>Latches<br>(words) | Total<br>Program<br>Flash<br>(words) |  |

|----------------|-------------------------|-----------------------------|--------------------------------------|--|

| PIC16(L)F15325 | 32                      | 32                          | 8192                                 |  |

| PIC16(L)F15345 | 32                      | 32                          | 8192                                 |  |

It is important to understand the PFM memory structure for erase and programming operations. PFM is arranged in rows. A row consists of 32 14-bit program memory words. A row is the minimum size that can be erased by user software.

All or a portion of this row can be programmed. Data to be written into the program memory row is written to 14-bit wide data write latches. These latches are not directly accessible, but may be loaded via sequential writes to the NVMDATH:NVMDATL register pair.

| Note: | To modify only a portion of a previously   |

|-------|--------------------------------------------|

|       | programmed row, the contents of the        |

|       | entire row must be read. Then, the new     |

|       | data and retained data can be written into |

|       | the write latches to reprogram the row of  |

|       | PFM. However, any unprogrammed             |

|       | locations can be written without first     |

|       | erasing the row. In this case, it is not   |

|       | necessary to save and rewrite the other    |

|       | previously programmed locations            |

# 13.1.1 PROGRAM MEMORY VOLTAGES

The PFM is readable and writable during normal operation over the full VDD range.

## 13.1.1.1 Programming Externally

The program memory cell and control logic support write and Bulk Erase operations down to the minimum device operating voltage. Special BOR operation is enabled during Bulk Erase (Section 8.2.4 "BOR is always OFF").

## 13.1.1.2 Self-programming

The program memory cell and control logic will support write and row erase operations across the entire VDD range. Bulk Erase is not available when selfprogramming.

| Name | Bit 7   | Bit 6   | Bit 5  | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on page |

|------|---------|---------|--------|---------|--------|--------|--------|--------|---------------------|

| PMD0 | SYSCMD  | FVRMD   | _      | —       | _      | NVMMD  | CLKRMD | IOCMD  | 204                 |

| PMD1 | NCO1MD  | —       | _      | —       | —      | TMR2MD | TMR1MD | TMR0MD | 205                 |

| PMD2 | —       | DAC1MD  | ADCMD  | —       | —      | CMP2MD | CMP1MD | ZCDMD  | 206                 |

| PMD3 | —       | _       | PWM6MD | PWM5MD  | PWM4MD | PWM3MD | CCP2MD | CCP1MD | 207                 |

| PMD4 | UART2MD | UART1MD | —      | MSSP1MD | —      | —      | —      | CWG1MD | 208                 |

| PMD5 | —       |         |        | CLC4MD  | CLC3MD | CLC2MD | CLC1MD | —      | 209                 |

TABLE 16-1:

SUMMARY OF REGISTERS ASSOCIATED WITH THE PPS MODULE

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the PPS module.

# 17.0 INTERRUPT-ON-CHANGE

An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual pin, or combination of pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- · Individual pin interrupt flags

Figure 17-1 is a block diagram of the IOC module.

## 17.1 Enabling the Module

To allow individual pins to generate an interrupt, the IOCIE bit of the PIE0 register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

## 17.2 Individual Pin Configuration

For each pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated bit of the IOCxP register is set. To enable a pin to detect a falling edge, the associated bit of the IOCxN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting the associated bits in both of the IOCxP and IOCxN registers.

# 17.3 Interrupt Flags

The bits located in the IOCxF registers are status flags that correspond to the interrupt-on-change pins of each port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the PIR0 register reflects the status of all IOCxF bits.

### 17.3.1 CLEARING INTERRUPT FLAGS

The individual status flags, (IOCxF register bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

#### EXAMPLE 17-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

# 17.4 Operation in Sleep

The interrupt-on-change interrupt event will wake the device from Sleep mode, if the IOCIE bit is set.

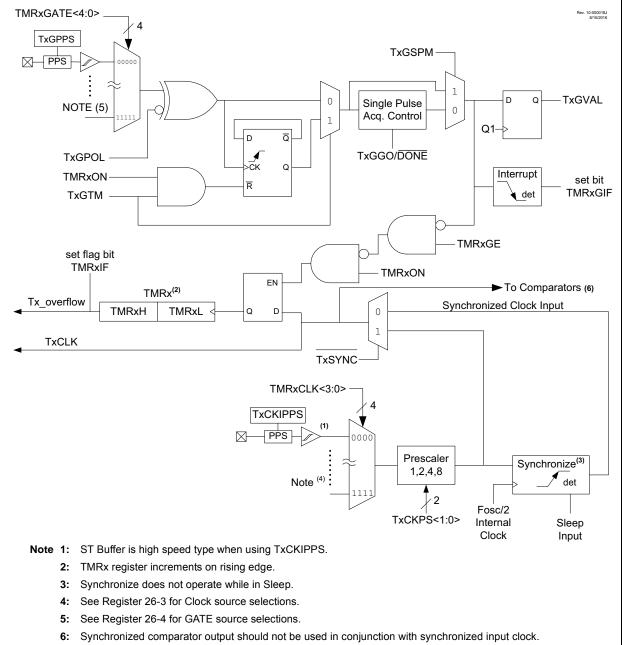

# 26.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is 16-bit timer/counters with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- Programmable internal or external clock source

- · 2-bit prescaler

- Clock source for optional comparator synchronization

- Multiple Timer1 gate (count enable) sources

- · Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- · Time base for the Capture/Compare function

- Auto-conversion Trigger (with CCP)

- · Selectable Gate Source Polarity

- · Gate Toggle mode

- · Gate Single-Pulse mode

- · Gate Value Status

- · Gate Event Interrupt

Figure 26-1 is a block diagram of the Timer1 module. This device has one instance of Timer1 type modules.

## FIGURE 26-1: TIMER1 BLOCK DIAGRAM

### 28.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 26.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

### 28.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIE6 register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIR6 register following any change in Operating mode.

| Note: | Clocking Timer1 from the system clock   |

|-------|-----------------------------------------|

|       | (Fosc) should not be used in Capture    |

|       | mode. In order for Capture mode to      |

|       | recognize the trigger event on the CCPx |

|       | pin, Timer1 must be clocked from the    |

|       | instruction clock (Fosc/4).             |

## 28.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxMODE<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 28-1 demonstrates the code to perform this function.

#### EXAMPLE 28-1: CHANGING BETWEEN CAPTURE PRESCALERS

| ;Set Bank bits to point |

|-------------------------|

| ;to CCPxCON             |

| ;Turn CCP module off    |

| ;Load the W reg with    |

| ;the new prescaler      |

| ;move value and CCP ON  |

| ;Load CCPxCON with this |

| ;value                  |

|                         |

## 28.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (FOSC/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

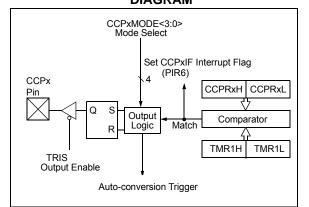

## 28.2 Compare Mode

Compare mode makes use of the 16-bit Timer1 resource. The 16-bit value of the CCPRxH:CCPRxL register pair is constantly compared against the 16-bit value of the TMR1H:TMR1L register pair. When a match occurs, one of the following events can occur:

- Toggle the CCPx output

- Set the CCPx output

- Clear the CCPx output

- · Generate an Auto-conversion Trigger

- · Generate a Software Interrupt

The action on the pin is based on the value of the CCPxMODE<3:0> control bits of the CCPxCON register. At the same time, the interrupt flag CCPxIF bit is set, and an ADC conversion can be triggered, if selected.

All Compare modes can generate an interrupt and trigger and ADC conversion.

Figure 28-2 shows a simplified diagram of the compare operation.

#### FIGURE 28-2: COMPARE MODE OPERATION BLOCK DIAGRAM

## 30.10 Auto-Shutdown

Auto-shutdown is a method to immediately override the CWG output levels with specific overrides that allow for safe shutdown of the circuit. The shutdown state can be either cleared automatically or held until cleared by software. The auto-shutdown circuit is illustrated in Figure 30-12.

#### 30.10.1 SHUTDOWN

The shutdown state can be entered by either of the following two methods:

- Software generated

- External Input

#### 30.10.1.1 Software Generated Shutdown

Setting the SHUTDOWN bit of the CWG1AS0 register will force the CWG into the shutdown state.

When the auto-restart is disabled, the shutdown state will persist as long as the SHUTDOWN bit is set.

When auto-restart is enabled, the SHUTDOWN bit will clear automatically and resume operation on the next rising edge event.

## 30.10.2 EXTERNAL INPUT SOURCE

External shutdown inputs provide the fastest way to safely suspend CWG operation in the event of a Fault condition. When any of the selected shutdown inputs goes active, the CWG outputs will immediately go to the selected override levels without software delay. Several input sources can be selected to cause a shutdown condition. All input sources are active-low. The sources are:

- Comparator C1OUT\_sync

- Comparator C2OUT\_sync

- · Timer2 TMR2\_postscaled

- CWG1IN input pin

Shutdown inputs are selected using the CWG1AS1 register (Register 30-6).

Note: Shutdown inputs are level sensitive, not edge sensitive. The shutdown state cannot be cleared, except by disabling auto-shutdown, as long as the shutdown input level persists.

## 30.11 Operation During Sleep

The CWG module operates independently from the system clock and will continue to run during Sleep, provided that the clock and input sources selected remain active.

The HFINTOSC remains active during Sleep when all the following conditions are met:

- CWG module is enabled

- · Input source is active

- HFINTOSC is selected as the clock source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and the CWG clock source, when the CWG is enabled and the input source is active, then the CPU will go idle during Sleep, but the HFINTOSC will remain active and the CWG will continue to operate. This will have a direct effect on the Sleep mode current.

| R/W-0/0          | U-0                                                                                                                                       | U-0               | U-0           | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u      |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------|----------------|------------------|------------------|--------------|--|

| LCxPOL           | —                                                                                                                                         | —                 | _             | LCxG4POL       | LCxG3POL         | LCxG2POL         | LCxG1POL     |  |

| bit 7            |                                                                                                                                           |                   |               |                |                  |                  | bit 0        |  |

|                  |                                                                                                                                           |                   |               |                |                  |                  |              |  |

| Legend:          |                                                                                                                                           |                   |               |                |                  |                  |              |  |

| R = Readable     | bit                                                                                                                                       | W = Writable      | bit           | U = Unimpler   | mented bit, read | l as '0'         |              |  |

| u = Bit is uncha | anged                                                                                                                                     | x = Bit is unkn   | iown          | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |  |

| '1' = Bit is set |                                                                                                                                           | '0' = Bit is clea | ared          |                |                  |                  |              |  |

|                  |                                                                                                                                           |                   |               |                |                  |                  |              |  |

| bit 7            | LCxPOL: CLO                                                                                                                               | CxOUT Output      | Polarity Cont | trol bit       |                  |                  |              |  |

|                  |                                                                                                                                           | ut of the logic o |               |                |                  |                  |              |  |

|                  | •                                                                                                                                         | ut of the logic o |               | erted          |                  |                  |              |  |

| bit 6-4          | Unimplemen                                                                                                                                | ted: Read as '    | )'            |                |                  |                  |              |  |

| bit 3            |                                                                                                                                           | Gate 3 Output     |               |                |                  |                  |              |  |

|                  |                                                                                                                                           | •                 |               | applied to the | logic cell       |                  |              |  |

| 1.11 Q           | •                                                                                                                                         | ut of gate 3 is r |               |                |                  |                  |              |  |

| bit 2            |                                                                                                                                           | Gate 2 Output I   | 5             |                | 1                |                  |              |  |

|                  | <ul> <li>1 = The output of gate 2 is inverted when applied to the logic cell</li> <li>0 = The output of gate 2 is not inverted</li> </ul> |                   |               |                |                  |                  |              |  |

| bit 1            | <b>LCxG2POL:</b> Gate 1 Output Polarity Control bit                                                                                       |                   |               |                |                  |                  |              |  |

|                  | <ul> <li>1 = The output of gate 1 is inverted when applied to the logic cell</li> <li>0 = The output of gate 1 is not inverted</li> </ul> |                   |               |                |                  |                  |              |  |

| bit 0            | LCxG1POL: Gate 0 Output Polarity Control bit                                                                                              |                   |               |                |                  |                  |              |  |

|                  | <ul> <li>1 = The output of gate 0 is inverted when applied to the logic cell</li> <li>0 = The output of gate 0 is not inverted</li> </ul> |                   |               |                |                  |                  |              |  |

## REGISTER 31-2: CLCxPOL: SIGNAL POLARITY CONTROL REGISTER

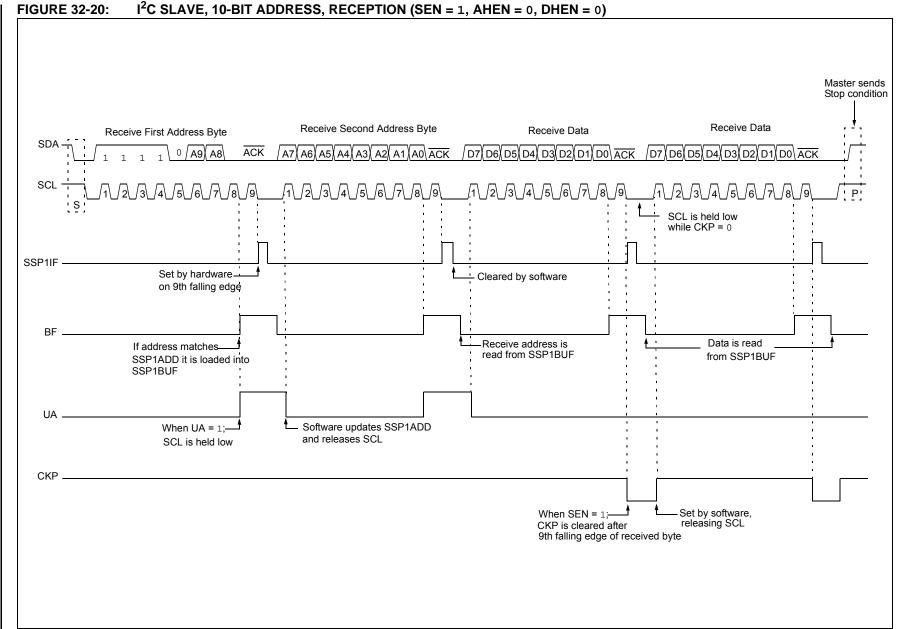

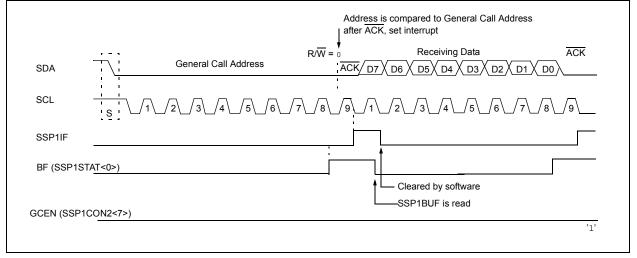

#### 32.5.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the  $I^2C$  protocol, defined as address  $0 \ge 0.00$ . When the GCEN bit of the SSP1CON2 register is set, the slave module will automatically ACK the reception of this address regardless of the value stored in SSP1ADD. After the slave clocks in an address of all zeros with the R/W bit clear, an interrupt is generated and slave software can read SSP1BUF and respond. Figure 32-24 shows a general call reception sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode.

If the AHEN bit of the SSP1CON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the eighth falling edge of SCL. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

32.5.9 SSP MASK REGISTER

An SSP Mask (SSP1MSK) register (Register 32-5) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSP1SR register during an address comparison operation. A zero ('0') bit in the SSP1MSK register has the effect of making the corresponding bit of the received address a "don't care". This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP operation until written with a mask value.

The SSP Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0> only. The SSP mask has no effect during the reception of the first (high) byte of the address.

## 33.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH Mark state which represents a '1' data bit, and a VoL Space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the Mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 33-3 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 33.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 33-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXxREG register.

#### 33.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXxSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXxSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCxSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

**Note:** The TXxIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

## 33.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXxREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXxREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXxREG until the Stop bit of the previous character has been transmitted. The pending character in the TXxREG is then transferred to the TSR in one TcY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXxREG.

#### 33.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDxCON register. The default state of this bit is '0' which selects high true transmit idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true idle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See **Section 33.4.1.2 "Clock Polarity"**.

#### 33.1.1.4 Transmit Interrupt Flag

The TXxIF interrupt flag bit of the PIR3 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXxREG. In other words, the TXxIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXxREG. The TXxIF flag bit is not cleared immediately upon writing TXxREG. TXxIF becomes valid in the second instruction cycle following the write execution. Polling TXxIF immediately following the TXxREG write will return invalid results. The TXxIF bit is read-only, it cannot be set or cleared by software.

The TXxIF interrupt can be enabled by setting the TXxIE interrupt enable bit of the PIE3 register. However, the TXxIF flag bit will be set whenever the TXxREG is empty, regardless of the state of TXxIE enable bit.

To use interrupts when transmitting data, set the TXxIE bit only when there is more data to send. Clear the TXxIE interrupt enable bit upon writing the last character of the transmission to the TXxREG.

#### 33.1.2.8 Asynchronous Reception Setup:

- Initialize the SPxBRGH, SPxBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 33.3 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RXxIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set the RX9 bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RXxIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RXxIE interrupt enable bit was also set.

- 8. Read the RCxSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCxREG register.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

ASYNCHRONOUS RECEPTION

#### 33.1.2.9 9-bit Address Detection Mode Setup

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPxBRGH, SPxBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 33.3 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RXxIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- 6. Enable address detection by setting the ADDEN bit.

- 7. Enable reception by setting the CREN bit.

- The RXxIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RXxIE interrupt enable bit was also set.

- 9. Read the RCxSTA register to get the error flags. The ninth data bit will always be set.

- 10. Get the received eight Least Significant data bits from the receive buffer by reading the RCxREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

| RX/DT pin                                      | Start<br>bit bit 0 / bit 1 / 5 / bit 7/8 / Stop<br>bit bit / bit 0 / 5 / bit 7/8 / Stop bit / bit 7/8 / Stop bit / bit 7/8 / Stop bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rcv Shift<br>Reg →<br>Rcv Buffer Reg.<br>RCIDL | Word 1 Word 2 Screen Sc |

| Read Rcv<br>Buffer Reg.<br>RCxREG              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RXxIF<br>(Interrupt Flag)                      | <u></u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OERR bit                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CREN                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                | s timing diagram shows three words appearing on the RX input. The RCxREG (receive buffer) is read after the third word, sing the OERR (overrun) bit to be set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

**FIGURE 33-5:**

# 33.4 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 33.4.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for synchronous master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXxSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXxSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCxSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCxSTA register enables the EUSART.

## 33.4.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TX/CK pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

## 33.4.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDxCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock.

## 33.4.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXxREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXxREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXxREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXxREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

| Note: | The TSR register is not mapped in data      |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|

|       | memory, so it is not available to the user. |  |  |  |  |  |  |

- 33.4.1.4 Synchronous Master Transmission Set-up:

- Initialize the SPxBRGH, SPxBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 33.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. If interrupts are desired, set the TXxIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXxREG register.

# 33.4.2.3 EUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 33.4.1.5 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is never idle

- · SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCxREG register. If the RXxIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 33.4.2.4 Synchronous Slave Reception Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for both the CK and DT pins (if applicable).

- 3. If interrupts are desired, set the RXxIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Set the CREN bit to enable reception.

- The RXxIF bit will be set when reception is complete. An interrupt will be generated if the RXxIE bit was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCxSTA register.

- 8. Retrieve the eight Least Significant bits from the receive FIFO by reading the RCxREG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCxSTA register or by clearing the SPEN bit which resets the EUSART.

# 34.0 REFERENCE CLOCK OUTPUT MODULE

The reference clock output module provides the ability to send a clock signal to the clock reference output pin (CLKR).

The reference clock output module has the following features:

- Selectable input clock

- Programmable clock divider

- Selectable duty cycle

# 34.1 CLOCK SOURCE

The reference clock output module has a selectable clock source. The CLKRCLK register (Register 34-2) controls which input is used.

## 34.1.1 CLOCK SYNCHRONIZATION

Once the reference clock enable (CLKREN) is set, the module is ensured to be glitch-free at start-up.

When the reference clock output is disabled, the output signal will be disabled immediately.

Clock dividers and clock duty cycles can be changed while the module is enabled, but glitches may occur on the output. To avoid possible glitches, clock dividers and clock duty cycles should be changed only when the CLKREN is clear.

## 34.2 PROGRAMMABLE CLOCK DIVIDER

The module takes the system clock input and divides it based on the value of the CLKRDIV<2:0> bits of the CLKRCON register (Register 34-1).

The following configurations can be made based on the CLKRDIV<2:0> bits:

- Base clock value

- · Base clock value divided by 2

- · Base clock value divided by 4

- Base clock value divided by 8

- · Base clock value divided by 16

- Base clock value divided by 32

- Base clock value divided by 64

- Base clock value divided by 128

The clock divider values can be changed while the module is enabled; however, in order to prevent glitches on the output, the CLKRDIV<2:0> bits should only be changed when the module is disabled (CLKREN = 0).

# 34.3 SELECTABLE DUTY CYCLE

The CLKRDC<1:0> bits of the CLKRCON register can be used to modify the duty cycle of the output clock. A duty cycle of 25%, 50%, or 75% can be selected for all clock rates, with the exception of the undivided base Fosc value.

The duty cycle can be changed while the module is enabled; however, in order to prevent glitches on the output, the CLKRDC<1:0> bits should only be changed when the module is disabled (CLKREN = 0).

Note: The CLKRDC1 bit is reset to '1'. This makes the default duty cycle 50% and not 0%.

# 34.4 OPERATION IN SLEEP MODE

The reference clock output module clock is based on the system clock. When the device goes to Sleep, the module outputs will remain in their current state. This will have a direct effect on peripherals using the reference clock output as an input signal.

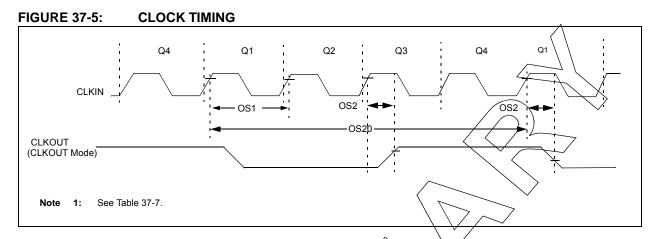

# TABLE 37-7: EXTERNAL CLOCK/OSCILLATOR TIMING REQUIREMENTS

| Param.<br>No.  | Sym.                | Characteristic         | Min. | Турт              | Max.  | Units | Conditions       |

|----------------|---------------------|------------------------|------|-------------------|-------|-------|------------------|

| ECL Oscillator |                     |                        |      |                   |       |       |                  |

| OS1            | F <sub>ECL</sub>    | Clock Frequency        |      | $\square$         | > 500 | kHz   |                  |

| OS2            | T <sub>ECL_DC</sub> | Clock Duty Cycle       | 40   |                   | 60    | %     |                  |

| ECM Oscillator |                     |                        |      |                   |       |       |                  |

| OS3            | F <sub>ECM</sub>    | Clock Frequency        |      | $\rangle -$       | 4     | MHz   |                  |

| OS4            | T <sub>ECM_DC</sub> | Clock Duty Cycle       | 40   | —                 | 60    | %     |                  |

| ECH Os         | cillator            |                        |      |                   |       |       | ·                |

| OS5            | F <sub>ECH</sub>    | Clock Frequency        | > -  |                   | 32    | MHz   |                  |

| OS6            | T <sub>ECH_DC</sub> | Clock Duty Sycle       | 40   | —                 | 60    | %     |                  |

| LP Oscil       | lator               |                        |      |                   |       |       | •                |

| OS7            | F <sub>LP</sub>     | Clock Frequency        | _    | —                 | 100   | kHz   | Note 4           |

| XT Oscil       | lator /             |                        |      |                   |       |       | ·                |

| OS8            | F <sub>XT</sub>     | Clock Frequency        | —    |                   | 4     | MHz   | Note 4           |

| HS Osci        |                     |                        | •    |                   |       | •     |                  |

| OS9            | FHS)                | Clock Frequency        | —    |                   | 20    | MHz   | Note 4           |

| System         | Oscillator          |                        |      |                   |       |       |                  |

| 0S20           | Fose                | System Clock Frequency | —    | _                 | 32    | MHz   | (Note 2, Note 3) |

| ØS21           | FCY                 | Instruction Frequency  | _    | Fosc/4            |       | MHz   |                  |

| 0522/          | /т <sub>сү</sub>    | Instruction Period     | 125  | 1/F <sub>CY</sub> | _     | ns    |                  |

These parameters are characterized but not tested.

Rata in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note** 1: Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

2: The system clock frequency (FOSC) is selected by the "main clock switch controls" as described in Section 9.0 "Oscillator Module (with Fail-Safe Clock Monitor)".

- 3: The system clock frequency (Fosc) must meet the voltage requirements defined in the Section 37.2 "Standard Operating Conditions".

- 4: LP, XT and HS oscillator modes require an appropriate crystal or resonator to be connected to the device. For clocking the device with the external square wave, one of the EC mode selections must be used.

| TABLE 37-9: PLL SI | PECIFICATIONS |

|--------------------|---------------|

|--------------------|---------------|

| Standard Operating Conditions (unless otherwise stated) VDD $\ge 2.5V$ |         |                                             |       |       |                     |       |            |

|------------------------------------------------------------------------|---------|---------------------------------------------|-------|-------|---------------------|-------|------------|

| Param.<br>No.                                                          | Sym.    | Characteristic                              | Min.  | Тур†  | Max.                | Units | Conditions |

| PLL01                                                                  | FPLLIN  | PLL Input Frequency Range                   | 4     | _     | 8                   | MHz   | $\searrow$ |

| PLL02                                                                  | FPLLOUT | PLL Output Frequency Range                  | 16    | —     | 32                  | MHz   | Note 1     |

| PLL03                                                                  | TPLLST  | PLL Lock Time from Start-up                 | _     | 200 🦯 | $\langle - \rangle$ | _µ\$  | -          |

| PLL04                                                                  | FPLLJIT | PLL Output Frequency Stability (Jitter)     | -0.25 | _ \   | 0.25                | ~%/   |            |

| *                                                                      | These p | arameters are characterized but not tested. |       |       |                     |       |            |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance t only and are not tested.

Note 1: The output frequency of the PLL must meet the Fosc requirements listed in Parameter D002.

## 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |          |      |  |  |

|--------------------------|-------------|----------|----------|------|--|--|

| Dimension                | Limits      | MIN      | NOM      | MAX  |  |  |

| Number of Pins           | Ν           |          | 14       |      |  |  |

| Pitch                    | е           |          | 0.65 BSC |      |  |  |

| Overall Height           | Α           | -        | -        | 1.20 |  |  |

| Molded Package Thickness | A2          | 0.80     | 1.00     | 1.05 |  |  |

| Standoff                 | A1          | 0.05     | -        | 0.15 |  |  |

| Overall Width            | Е           | 6.40 BSC |          |      |  |  |

| Molded Package Width     | E1          | 4.30     | 4.40     | 4.50 |  |  |

| Molded Package Length    | D           | 4.90     | 5.00     | 5.10 |  |  |

| Foot Length              | L           | 0.45     | 0.60     | 0.75 |  |  |

| Footprint                | (L1)        | 1.00 REF |          |      |  |  |

| Foot Angle               | φ           | 0°       | -        | 8°   |  |  |

| Lead Thickness           | С           | 0.09     | -        | 0.20 |  |  |

| Lead Width               | b           | 0.19     | -        | 0.30 |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or

protrusions shall not exceed 0.15mm per side.

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing No. C04-087C Sheet 2 of 2