Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXE

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 224 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                              |

| Supplier Device Package    | 14-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15325-i-sl |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IADLE 4        | Bank 60  | _,     | Bank 61   | , _,           | Bank 62               |         | Bank 63 |

|----------------|----------|--------|-----------|----------------|-----------------------|---------|---------|

| 1E0Ch          | _        | 1E8Ch  | _         | 1F0Ch          | _                     | 1F8Ch   | _       |

| 1E0Dh          | _        | 1E8Dh  | _         | 1F0Dh          | _                     | 1F8Dh   | _       |

| 1E0Eh          | _        | 1E8Eh  | _         | 1F0Eh          | _                     | 1F8Eh   | _       |

| 1E0Fh          | CLCDATA  | 1E8Fh  | PPSLOCK   | 1F0Fh          | _                     | 1F8Fh   | _       |

| 1E10h          | CLC1CON  | 1E90h  | INTPPS    | 1F10h          | RA0PPS                | 1F90h   | _       |

| 1E11h          | CLC1POL  | 1E91h  | TOCKIPPS  | 1F11h          | RA1PPS                | 1F91h   | _       |

| 1E12h          | CLC1SEL0 | 1E92h  | T1CKIPPS  | 1F12h          | RA2PPS                | 1F92h   | _       |

| 1E13h          | CLC1SEL1 | 1E93h  | T1GPPS    | 1F13h          | RA3PPS                | 1F93h   | _       |

| 1E14h          | CLC1SEL2 | 1E94h  | _         | 1F14h          | RA4PPS                | 1F94h   | _       |

| 1E15h          | CLC1SEL3 | 1E95h  | _         | 1F15h          | RA5PPS                | 1F95h   | _       |

| 1E16h          | CLC1GLS0 | 1E96h  | _         | 1F16h          |                       | 1F96h   | _       |

| 1E17h          | CLC1GLS1 | 1E97h  | _         | 1F17h          | _                     | 1F97h   | _       |

| 1E18h          | CLC1GLS2 | 1E98h  | _         | 1F18h          | _                     | 1F98h   | _       |

| 1E19h          | CLC1GLS3 | 1E99h  |           | 1F19h          | _                     | 1F99h   | _       |

| 1E1Ah          | CLC2CON  | 1E9Ah  | _         | 1F1Ah          | _                     | 1F9Ah   | _       |

| 1E1Bh          | CLC2POL  | 1E9Bh  | _         | 1F1Bh          | _                     | 1F9Bh   | _       |

| 1E1Ch          | CLC2SEL0 | 1E9Ch  | T2INPPS   | 1F1Ch          | RB4PPS <sup>(1)</sup> | 1F9Ch   |         |

|                |          |        |           |                | RB5PPS <sup>(1)</sup> |         |         |

| 1E1Dh          | CLC2SEL1 | 1E9Dh  |           | 1F1Dh          |                       | 1F9Dh   |         |

| 1E1Eh          | CLC2SEL2 | 1E9Eh  |           | 1F1Eh          | RB6PPS <sup>(1)</sup> | 1F9Eh   | —       |

| 1E1Fh          | CLC2SEL3 | 1E9Fh  | _         | 1F1Fh          | RB7PPS <sup>(1)</sup> | 1F9Fh   | _       |

| 1E20h          | CLC2GLS0 | 1EA0h  | —         | 1F20h          | RC0PPS                | 1FA0h   | —       |

| 1E21h          | CLC2GLS1 | 1EA1h  | CCP1PPS   | 1F21h          | RC1PPS                | 1FA1h   | _       |

| 1E22h          | CLC2GLS2 | 1EA2h  | CCP2PPS   | 1F22h          | RC2PPS                | 1FA2h   | _       |

| 1E23h          | CLC2GLS3 | 1EA3h  | _         | 1F23h          | RC3PPS                | 1FA3h   | _       |

| 1E24h          | CLC3CON  | 1EA4h  | —         | 1F24h          | RC4PPS                | 1FA4h   | —       |

| 1E25h          | CLC3POL  | 1EA5h  | —         | 1F25h          | RC5PPS                | 1FA5h   | —       |

| 1E26h          | CLC3SEL0 | 1EA6h  | —         | 1F26h          | RC6PPS <sup>(1)</sup> | 1FA6h   | —       |

| 1E27h          | CLC3SEL1 | 1EA7h  | _         | 1F27h          | RC7PPS <sup>(1)</sup> | 1FA7h   | _       |

| 1E28h          | CLC3SEL2 | 1EA8h  |           | 1F28h          | _                     | 1FA8h   | _       |

| 1E29h          | CLC3SEL3 | 1EA9h  | _         | 1F29h          | _                     | 1FA9h   | _       |

| 1E2Ah          | CLC3GLS0 | 1EAAh  | _         | 1F2Ah          | _                     | 1FAAh   | _       |

| 1E2Bh          | CLC3GLS1 | 1EABh  | _         | 1F2Bh          | _                     | 1FABh   | _       |

| 1E2Ch          | CLC3GLS2 | 1EACh  | _         | 1F2Ch          | _                     | 1FACh   | _       |

| 1E2Dh          | CLC3GLS3 | 1EADh  |           | 1F2Dh          | _                     | 1FADh   | _       |

| 1E2Eh          | CLC4CON  | 1EAEh  |           | 1F2Eh          | _                     | 1FAEh   | _       |

| 1E2Fh          | CLC4POL  | 1EAFh  | _         | 1F2Fh          | _                     | 1FAFh   | _       |

| 1E30h          | CLC4SEL0 | 1EB0h  | _         | 1F30h          | _                     | 1FB0h   | _       |

| 1E31h          | CLC4SEL1 | 1EB1h  | CWG1PPS   | 1F31h          | _                     | 1FB1h   | _       |

| 1E32h          | CLC4SEL2 | 1EB2h  | _         | 1F32h          | _                     | 1FB2h   | _       |

| 1E33h          | CLC4SEL3 | 1EB3h  | _         | 1F33h          | _                     | 1FB3h   | _       |

| 1E34h          | CLC4GLS0 | 1EB4h  | _         | 1F34h          | _                     | 1FB4h   | _       |

| 1E35h          | CLC4GLS1 | 1EB5h  | _         | 1F35h          | _                     | 1FB5h   | _       |

| 1E36h          | CLC4GLS2 | 1EB6h  | _         | 1F36h          | _                     | 1FB6h   | _       |

| 1E37h          | CLC4GLS3 | 1EB7h  |           | 1F37h          | _                     | 1FB7h   | _       |

| 1E38h          | _        | 1EB8h  |           | 1F38h          | ANSELA                | 1FB8h   | _       |

| 1E39h          | _        | 1EB9h  |           | 1F39h          | WPUA                  | 1FB9h   | _       |

| 1E3Ah          |          | 1EBAh  |           | 1F3Ah          | ODCONA                | 1FBAh   | _       |

| 1E3Ah          | _        | 1EBBh  | CLCIN0PPS | 1F3An          | SLRCONA               | 1FBBh   | _       |

| 1E3Dh          |          | 1EBCh  | CLCIN1PPS | 1F3Dh          | INLVLA                | 1FBCh   |         |

| 1E3Dh          | _        | 1EBDh  | CLCIN2PPS | 1F3Dh          | IOCAP                 | 1FBDh   | _       |

| 1E3Dh          |          | 1EBDh  | CLCIN3PPS |                | IOCAP                 | 1FBEh   | _       |

| 1E3En          |          | 1EBEN  |           | 1F3Eh<br>1F3Fh | IOCAN                 | 1FBEh   | _       |

| 1E3Fn<br>1E40h | _        | 1EBFN  | _         | 1F3Fn<br>1F40h |                       | 1FC0h   | _       |

|                | _        | IECUII |           | 164011         |                       | 11 0011 |         |

## TABLE 4-8: PIC16(L)F15325/45 MEMORY MAP, BANKS 60, 61, 62, AND 63

Legend: = Unimplemented data memory locations, read as '0'

Note 1: Present only in PIC16(L)F15345.

## PIC16(L)F15325/45

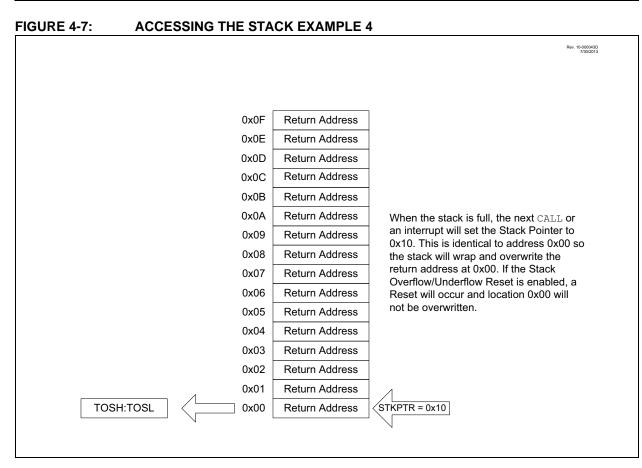

## 4.5.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Words (Register 5-2) is programmed to '1', the device will be Reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

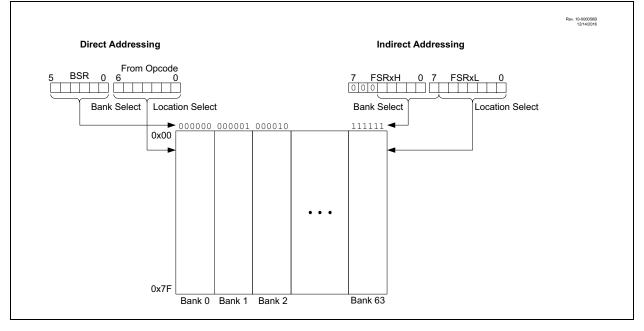

## 4.6 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- Traditional/Banked Data Memory

- Linear Data Memory

- Program Flash Memory

## 4.6.1 TRADITIONAL/BANKED DATA MEMORY

The traditional or banked data memory is a region from FSR address 0x000 to FSR address 0x1FFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

## FIGURE 4-9: TRADITIONAL/BANKED DATA MEMORY MAP

## 8.3 Register Definitions: Brown-out Reset Control

Legend:

REGISTER 8-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u               | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|-----------------------|-----|-----|-----|-----|-----|-----|--------|

| SBOREN <sup>(1)</sup> | _   | —   | —   | —   | —   | —   | BORRDY |

| bit 7                 |     |     |     |     |     |     | bit 0  |

|                       |     |     |     |     |     |     |        |

| Logona.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | SBOREN: Software Brown-out Reset Enable bit <sup>(1)</sup> |

|---------|------------------------------------------------------------|

|         | If BOREN <1:0> in Configuration Words $\neq 01$ :          |

|         | SBOREN is read/write, but has no effect on the BOR.        |

|         | If BOREN <1:0> in Configuration Words = 01:                |

|         | 1 = BOR Enabled                                            |

|         | 0 = BOR Disabled                                           |

| bit 6-1 | Unimplemented: Read as '0'                                 |

| bit 0   | BORRDY: Brown-out Reset Circuit Ready Status bit           |

|         | 1 = The Brown-out Reset circuit is active                  |

0 = The Brown-out Reset circuit is inactive

**Note 1:** BOREN<1:0> bits are located in Configuration Words.

## 12.7 Register Definitions: Windowed Watchdog Timer Control

## REGISTER 12-1: WDTCON0: WATCHDOG TIMER CONTROL REGISTER 0

| U-0           | U-0                                                                                                                          | R/W <sup>(3)</sup> -q/q <sup>(2)</sup>                             | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W-0/0    |

|---------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|------------|

| -             | -                                                                                                                            |                                                                    |                                        | WDTPS<4:0>(1)                          |                                        |                                        | SWDTEN     |

| bit 7         |                                                                                                                              |                                                                    |                                        |                                        |                                        |                                        | bit C      |

|               |                                                                                                                              |                                                                    |                                        |                                        |                                        |                                        |            |

| Legend:       |                                                                                                                              |                                                                    |                                        |                                        |                                        |                                        |            |

| R = Reada     | ble bit                                                                                                                      | W = Writable b                                                     | pit                                    | U = Unimplem                           | nented bit, read                       | l as '0'                               |            |

| u = Bit is u  | nchanged                                                                                                                     | x = Bit is unkno                                                   | own                                    | -n/n = Value a                         | t POR and BO                           | R/Value at all ot                      | her Resets |

| 1' = Bit is s | set                                                                                                                          | ʻ0' = Bit is clea                                                  | red                                    | q = Value dep                          | ends on condit                         | ion                                    |            |

| bit 7-6       | Unimplome                                                                                                                    | ntod. Dood oo 'o                                                   | 3                                      |                                        |                                        |                                        |            |

|               | -                                                                                                                            | ented: Read as '0<br>0>: Watchdog Tin                              |                                        | alaat hita(1)                          |                                        |                                        |            |

| bit 5-1       |                                                                                                                              | Prescale Rate                                                      | ner Prescale S                         |                                        |                                        |                                        |            |

|               |                                                                                                                              |                                                                    |                                        | tom (a) (1.20)                         |                                        |                                        |            |

|               | •                                                                                                                            | eserved. Results                                                   | in minimum in                          | iterval (1:32)                         |                                        |                                        |            |

|               | •                                                                                                                            |                                                                    |                                        |                                        |                                        |                                        |            |

|               | •                                                                                                                            |                                                                    |                                        |                                        |                                        |                                        |            |

|               | 10011 <b>=</b> R                                                                                                             | eserved. Results                                                   | in minimum in                          | terval (1:32)                          |                                        |                                        |            |

|               | 10010 = <b>1</b>                                                                                                             | :8388608 (2 <sup>23</sup> ) (II                                    | nterval 256s no                        | ominal)                                |                                        |                                        |            |

|               | 10010 = 1:8388608 (2 <sup>23</sup> ) (Interval 256s nominal)<br>10001 = 1:4194304 (2 <sup>22</sup> ) (Interval 128s nominal) |                                                                    |                                        |                                        |                                        |                                        |            |

|               | 10000 = 1:2097152 (2 <sup>21</sup> ) (Interval 64s nominal)                                                                  |                                                                    |                                        |                                        |                                        |                                        |            |

|               | 01111 = 1                                                                                                                    | :1048576 (2 <sup>20</sup> ) (lı                                    | nterval 32s nor                        | minal)                                 |                                        |                                        |            |

|               | 01110 = 1                                                                                                                    | :524288 (2 <sup>19</sup> ) (Int<br>:262144 (2 <sup>18</sup> ) (Int | terval 16s nom                         | inal)                                  |                                        |                                        |            |

|               | 01101 = 1                                                                                                                    | :262144 (2 <sup>10</sup> ) (Ini                                    | terval 8s nomin                        | nal)                                   |                                        |                                        |            |

|               |                                                                                                                              | :131072 (2 <sup>17</sup> ) (Int<br>:65536 (Interval 2              |                                        |                                        |                                        |                                        |            |

|               |                                                                                                                              | :32768 (Interval 2                                                 |                                        | eset value)                            |                                        |                                        |            |

|               |                                                                                                                              | :16384 (Interval 5                                                 | ,                                      | d)                                     |                                        |                                        |            |

|               |                                                                                                                              | :8192 (Interval 25                                                 |                                        |                                        |                                        |                                        |            |

|               |                                                                                                                              | :4096 (Interval 12                                                 |                                        |                                        |                                        |                                        |            |

|               | 00110 = 1                                                                                                                    | :2048 (Interval 64                                                 | ms nominal)                            |                                        |                                        |                                        |            |

|               |                                                                                                                              | :1024 (Interval 32                                                 | ,                                      |                                        |                                        |                                        |            |

|               |                                                                                                                              | :512 (Interval 16)                                                 | ,                                      |                                        |                                        |                                        |            |

|               |                                                                                                                              | :256 (Interval 8 m                                                 | ,                                      |                                        |                                        |                                        |            |

|               |                                                                                                                              | :128 (Interval 4 m                                                 |                                        |                                        |                                        |                                        |            |

|               |                                                                                                                              | :64 (Interval 2 ms<br>:32 (Interval 1 ms                           | ,                                      |                                        |                                        |                                        |            |

| oit O         |                                                                                                                              | Software Enable/                                                   |                                        | tchdog Timer bi                        | it                                     |                                        |            |

|               | If WDTE<1:                                                                                                                   |                                                                    |                                        | U U                                    |                                        |                                        |            |

|               | This bit is ig                                                                                                               |                                                                    |                                        |                                        |                                        |                                        |            |

|               | If WDTE<1:                                                                                                                   |                                                                    |                                        |                                        |                                        |                                        |            |

|               | 1 = WDT is                                                                                                                   |                                                                    |                                        |                                        |                                        |                                        |            |

|               | 0 = WDT is                                                                                                                   |                                                                    |                                        |                                        |                                        |                                        |            |

|               | If WDTE<1:                                                                                                                   |                                                                    |                                        |                                        |                                        |                                        |            |

|               | This bit is ig                                                                                                               | nored.                                                             |                                        |                                        |                                        |                                        |            |

- **Note 1:** Times are approximate. WDT time is based on 31 kHz LFINTOSC.

- 2: When WDTCPS <4:0> in CONFIG3 = 11111, the Reset value of WDTPS<4:0> is 01011. Otherwise, the Reset value of WDTPS<4:0> is equal to WDTCPS<4:0> in CONFIG3.

- **3:** When WDTCPS <4:0> in CONFIG3  $\neq$  11111, these bits are read-only.

# PIC16(L)F15325/45

## 14.5 Register Definitions: PORTB

## REGISTER 14-9: PORTB: PORTB REGISTER

| R/W-x/u                                 | R/W-x/u | R/W-x/u | R/W-x/u | U-0                                                   | U-0 | U-0 | U-0   |  |

|-----------------------------------------|---------|---------|---------|-------------------------------------------------------|-----|-----|-------|--|

| RB7                                     | RB6     | RB5     | RB4     | —                                                     | —   | —   | _     |  |

| bit 7                                   |         |         |         |                                                       |     |     | bit 0 |  |

|                                         |         |         |         |                                                       |     |     |       |  |

| Legend:                                 |         |         |         |                                                       |     |     |       |  |

| R = Readable bit W = Writable bit       |         |         | bit     | U = Unimplemented bit, read as '0'                    |     |     |       |  |

| u = Bit is unchanged x = Bit is unknown |         |         | nown    | -n/n = Value at POR and BOR/Value at all other Resets |     |     |       |  |

| 0                |                      |

|------------------|----------------------|

| '1' = Bit is set | '0' = Bit is cleared |

|                  |                      |

| bit 7-4 | <b>RB&lt;7:4&gt;</b> : PORTB I/O Value bits <sup>(1)</sup> |

|---------|------------------------------------------------------------|

|         | 1 = Port pin is <u>&gt;</u> Vін                            |

|         | 0 = Port pin is <u>&lt;</u> VIL                            |

|         |                                                            |

bit 3-0 Unimplemented: Read as '0'

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. The actual I/O pin values are read from the PORTB register.

## REGISTER 14-10: TRISB: PORTB TRI-STATE REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| TRISB7  | TRISB6  | TRISB5  | TRISB4  | _   | —   | _   | —     |

| bit 7   | •       |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | <b>TRISB&lt;7:4&gt;:</b> PORTB Tri-State Control bit<br>1 = PORTB pin configured as an input (tri-stated) |

|---------|-----------------------------------------------------------------------------------------------------------|

| bit 3-0 | <ul> <li>PORTB pin configured as an output</li> <li>Unimplemented: Read as '0'</li> </ul>                 |

## 16.0 PERIPHERAL MODULE DISABLE

The PIC16(L)F15325/45 provides the ability to disable selected modules, placing them into the lowest possible Power mode.

For legacy reasons, all modules are ON by default following any Reset.

## 16.1 Disabling a Module

Disabling a module has the following effects:

- All clock and control inputs to the module are suspended; there are no logic transitions, and the module will not function.

- The module is held in Reset:

- Writing to SFRs is disabled

- Reads return 00h

## 16.2 Enabling a module

When the register bit is cleared, the module is reenabled and will be in its Reset state; SFR data will reflect the POR Reset values.

Depending on the module, it may take up to one full instruction cycle for the module to become active. There should be no interaction with the module (e.g., writing to registers) for at least one instruction after it has been re-enabled.

## 16.3 Disabling a Module

When a module is disabled, all the associated PPS selection registers (Registers xxxPPS Register 15-1, 15-2, and 15-3), are also disabled.

## 16.4 System Clock Disable

Setting SYSCMD (PMD0, Register 16-1) disables the system clock (Fosc) distribution network to the peripherals. Not all peripherals make use of SYSCLK, so not all peripherals are affected. Refer to the specific peripheral description to see if it will be affected by this bit.

#### 18.3 **Register Definitions: FVR Control**

#### REGISTER 18-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0 | R-q/q                 | R/W-0/0             | R/W-0/0              | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|-----------------------|---------------------|----------------------|---------|---------|---------|---------|

| FVREN   | FVRRDY <sup>(1)</sup> | TSEN <sup>(3)</sup> | TSRNG <sup>(3)</sup> | CDAF\   | /R<1:0> | ADFVF   | R<1:0>  |

| bit 7   |                       |                     |                      |         |         |         | bit 0   |

| Legend:         |                                  |                                                                                                                                                             |                                                       |  |  |

|-----------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|

| R = Readab      | le bit                           | W = Writable bit                                                                                                                                            | U = Unimplemented bit, read as '0'                    |  |  |

| u = Bit is un   | changed                          | x = Bit is unknown                                                                                                                                          | -n/n = Value at POR and BOR/Value at all other Resets |  |  |

| '1' = Bit is se | et                               | '0' = Bit is cleared                                                                                                                                        | q = Value depends on condition                        |  |  |

| bit 7           | 1 = Fixed                        | Fixed Voltage Reference Ena<br>I Voltage Reference is enable<br>I Voltage Reference is disable                                                              | ed                                                    |  |  |

| bit 6           | 1 = Fixed                        | Fixed Voltage Reference Re<br>Voltage Reference output is<br>Voltage Reference output is                                                                    | s ready for use                                       |  |  |

| bit 5           | 1 = Temp                         | mperature Indicator Enable to<br>perature Indicator is enabled<br>perature Indicator is disabled                                                            | pit <sup>(3)</sup>                                    |  |  |

| bit 4           | 1 = Temp                         | Temperature Indicator Range<br>erature in High Range<br>erature in Low Range                                                                                | e Selection bit <sup>(3)</sup>                        |  |  |

| bit 3-2         |                                  |                                                                                                                                                             |                                                       |  |  |

| bit 1-0         | 11 = ADC<br>10 = ADC<br>01 = ADC | I: <b>0&gt;:</b> ADC FVR Buffer Gain 5<br>FVR Buffer Gain is 4x, (4.09<br>FVR Buffer Gain is 2x, (2.04<br>FVR Buffer Gain is 1x, (1.02<br>FVR Buffer is off | 96V)(2)<br>48V) <sup>(2)</sup>                        |  |  |

|                 | VRRDY is alv                     | vays '1'.<br>Reference output cannot exc                                                                                                                    | eed VDD.                                              |  |  |

|                 | •                                | •                                                                                                                                                           | <b>Module</b> " for additional information.           |  |  |

See Section 19.0 "Temperature Indicator Module" for additional information.

#### REGISTER 22-3: NCO1ACCL: NCO1 ACCUMULATOR REGISTER – LOW BYTE

| R/W-0/0         R/W-0/0 <t< th=""><th>Lonondi</th><th></th><th></th><th></th><th></th><th></th><th></th><th></th></t<> | Lonondi |         |         |         |         |         |         |         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|

| NCO1ACC<7:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |         |         |         |         |         |         |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 7   |         |         |         |         |         |         | bit 0   |

| R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |         |         | NCO1A   | CC<7:0> |         |         |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0/0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 NCO1ACC<7:0>: NCO1 Accumulator, Low Byte

#### REGISTER 22-4: NCO1ACCH: NCO1 ACCUMULATOR REGISTER – HIGH BYTE

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | NCO1ACC | C<15:8> |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| L       |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

| Legenu.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 NOC1ACC<15:8>: NCO1 Accumulator, High Byte

#### REGISTER 22-5: NCO1ACCU: NCO1 ACCUMULATOR REGISTER – UPPER BYTE<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|----------|---------|

| —     | —   | _   | —   |         | NCO1AC  | C<19:16> |         |

| bit 7 |     |     |     |         |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 NCO1ACC<19:16>: NCO1 Accumulator, Upper Byte

**Note 1:** The accumulator spans registers NCO1ACCU:NCO1ACCH: NCO1ACCL. The 24 bits are reserved but not all are used. This register updates in real-time, asynchronously to the CPU; there is no provision to guarantee atomic access to this 24-bit space using an 8-bit bus. Writing to this register while the module is operating will produce undefined results.

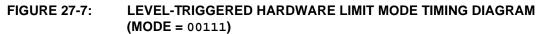

#### 27.5.4 LEVEL-TRIGGERED HARDWARE LIMIT MODE

In the Level-Triggered Hardware Limit Timer modes the counter is reset by high or low levels of the external signal TMRx\_ers, as shown in Figure 27-7. Selecting MODE<4:0> = 0.0110 will cause the timer to reset on a low level external signal. Selecting MODE<4:0> = 0.0111 will cause the timer to reset on a high level external signal. In the example, the counter is reset while TMRx\_ers = 1. ON is controlled by BSF and BCF instructions. When ON = 0 the external signal is ignored.

When the CCP uses the timer as the PWM time base then the PWM output will be set high when the timer starts counting and then set low only when the timer count matches the CCPRx value. The timer is reset when either the timer count matches the PRx value or two clock periods after the external Reset signal goes true and stays true.

The timer starts counting, and the PWM output is set high, on either the clock following the PRx match or two clocks after the external Reset signal relinquishes the Reset. The PWM output will remain high until the timer counts up to match the CCPRx pulse width value. If the external Reset signal goes true while the PWM output is high then the PWM output will remain high until the Reset signal is released allowing the timer to count up to match the CCPRx value.

#### 27.5.10 LEVEL-TRIGGERED HARDWARE LIMIT ONE-SHOT MODES

The Level-Triggered Hardware Limit One-Shot modes hold the timer in Reset on an external Reset level and start counting when both the ON bit is set and the external signal is not at the Reset level. If one of either the external signal is not in Reset or the ON bit is set then the other signal being set/made active will start the timer. Reset levels are selected as follows:

- Low Reset level (MODE<4:0> = 10110)

- High Reset level (MODE<4:0> = 10111)

When the timer count matches the PRx period count, the timer is reset and the ON bit is cleared. When the ON bit is cleared by either a PRx match or by software control the timer will stay in Reset until both the ON bit is set and the external signal is not at the Reset level.

When Level-Triggered Hardware Limit One-Shot modes are used in conjunction with the CCP PWM operation the PWM drive goes active with either the external signal edge or the setting of the ON bit, whichever of the two starts the timer.

## 27.6 Timer2 Operation During Sleep

When PSYNC = 1, Timer2 cannot be operated while the processor is in Sleep mode. The contents of the TMR2 and T2PR registers will remain unchanged while processor is in Sleep mode.

When PSYNC = 0, Timer2 will operate in Sleep as long as the clock source selected is also still running. Selecting the LFINTOSC, MFINTOSC, or HFINTOSC oscillator as the timer clock source will keep the selected oscillator running during Sleep.

| R/W-1/1          | R/W-1/1                                                                                 | R/W-1/1          | R/W-1/1 | R/W-1/1        | R/W-1/1          | R/W-1/1                    | R/W-1/1      |

|------------------|-----------------------------------------------------------------------------------------|------------------|---------|----------------|------------------|----------------------------|--------------|

|                  |                                                                                         |                  | SSP1N   | ISK<7:0>       |                  |                            |              |

| bit 7            |                                                                                         |                  |         |                |                  |                            | bit 0        |

|                  |                                                                                         |                  |         |                |                  |                            |              |

| Legend:          |                                                                                         |                  |         |                |                  |                            |              |

| R = Readable     | e bit                                                                                   | W = Writable     | bit     | U = Unimpler   | nented bit, read | l as '0'                   |              |

| u = Bit is unch  | nanged                                                                                  | x = Bit is unkr  | nown    | -n/n = Value a | at POR and BO    | R/Value at all o           | other Resets |

| '1' = Bit is set |                                                                                         | '0' = Bit is cle | ared    |                |                  |                            |              |

|                  |                                                                                         |                  |         |                |                  |                            |              |

| bit 7-1          |                                                                                         | 7:1>: Mask bits  |         |                |                  |                            |              |

|                  |                                                                                         | eived address b  |         |                |                  | I <sup>2</sup> C address m | atch         |

|                  | 0 = The received address bit n is not used to detect I <sup>2</sup> C address match     |                  |         |                |                  |                            |              |

| bit 0            | SSP1MSK<0>: Mask bit for I <sup>2</sup> C Slave mode, 10-bit Address                    |                  |         |                |                  |                            |              |

|                  | I <sup>2</sup> C Slave mode, 10-bit address (SSPM<3:0> = 0111 or 1111):                 |                  |         |                |                  |                            |              |

|                  | 1 = The received address bit 0 is compared to SSP1ADD<0> to detect $I^2C$ address match |                  |         |                |                  |                            |              |

|                  | 0 = The received address bit 0 is not used to detect $I^2C$ address match               |                  |         |                |                  |                            |              |

|                  | I <sup>2</sup> C Slave mode, 7-bit address:                                             |                  |         |                |                  |                            |              |

## REGISTER 32-5: SSP1MSK: SSP1 MASK REGISTER

MSK0 bit is ignored.

## REGISTER 32-6: SSP1ADD: MSSP1 ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | SSP1AD  | D<7:0>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### Master mode:

| bit 7-0 | SSP1ADD<7:0>: Baud Rate Clock Divider bits      |

|---------|-------------------------------------------------|

|         | SCL pin clock period = ((ADD<7:0> + 1) *4)/Fosc |

#### <u>10-Bit Slave mode – Most Significant Address Byte:</u>

- bit 7-3 **Not used:** Unused for Most Significant Address Byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 SSP1ADD<2:1>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

#### <u>10-Bit Slave mode – Least Significant Address Byte:</u>

bit 7-0 SSP1ADD<7:0>: Eight Least Significant bits of 10-bit address

#### 7-Bit Slave mode:

- bit 7-1 SSP1ADD<7:1>: 7-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

## 33.4 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 33.4.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for synchronous master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXxSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXxSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCxSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCxSTA register enables the EUSART.

## 33.4.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TX/CK pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

## 33.4.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUDxCON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock.

### 33.4.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXxREG register. If the TSR still contains all or part of a previous character the new character data is held in the TXxREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXxREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXxREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

- 33.4.1.4 Synchronous Master Transmission Set-up:

- Initialize the SPxBRGH, SPxBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 33.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. If interrupts are desired, set the TXxIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXxREG register.

## 36.3 Instruction Descriptions

| ADDFSR           | Add Literal to FSRn                                                                              |

|------------------|--------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDFSR FSRn, k                                                                           |

| Operands:        | $-32 \le k \le 31$<br>n $\in$ [ 0, 1]                                                            |

| Operation:       | $FSR(n) + k \rightarrow FSR(n)$                                                                  |

| Status Affected: | None                                                                                             |

| Description:     | The signed 6-bit literal 'k' is added to<br>the contents of the FSRnH:FSRnL<br>register pair.    |

|                  | FSRn is limited to the range<br>0000h-FFFFh. Moving beyond these<br>bounds will cause the FSR to |

| ANDLW            | AND literal with W                                                                                              |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                        |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                             |  |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                 |  |  |  |  |

| Status Affected: | Z                                                                                                               |  |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |  |  |  |  |

| ADDLW            | Add literal and W                                                                                             |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                      |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                           |  |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                             |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                      |  |  |  |  |

| Description:     | The contents of the W register are added to the 8-bit literal 'k' and the result is placed in the W register. |  |  |  |  |

wrap-around.

| ANDWF            | AND W with f                                                                                                                                                    |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                               |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |  |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |  |

| Description:     | AND the W register with register 'f'. If<br>'d' is '0', the result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f'. |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                               |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                           |

| Status Affected: | C, DC, Z                                                                                                                                                                        |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the result is<br>stored in the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |

| ASRF             | Arithmetic Right Shift                                                                                                                                                                                                              |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label]ASRF f{,d}                                                                                                                                                                                                                   |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                         |  |  |

| Operation:       | (f<7>)→ dest<7><br>(f<7:1>) → dest<6:0>,<br>(f<0>) → C,                                                                                                                                                                             |  |  |

| Status Affected: | C, Z                                                                                                                                                                                                                                |  |  |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. The MSb remains unchanged. If<br>'d' is '0', the result is placed in W. If 'd'<br>is '1', the result is stored back in<br>register 'f'. |  |  |

| ADDWFC ADD W and CARRY bit to f |

|---------------------------------|

|---------------------------------|

| Syntax:          | [ label ] ADDWFC f {,d}                                                                                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |

| Operation:       | $(W) + (f) + (C) \rightarrow dest$                                                                                                                                        |

| Status Affected: | C, DC, Z                                                                                                                                                                  |

| Description:     | Add W, the Carry flag and data mem-<br>ory location 'f'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed in data memory location 'f'. |

## 37.2 Standard Operating Conditions

| 37.2 Standard Operating Conditions                                                            |  |

|-----------------------------------------------------------------------------------------------|--|

| The standard operating conditions for any device are defined as:                              |  |

| Operating Voltage: $VDDMIN \le VDD \le VDDMAX$ Operating Temperature:TA_MIN \le TA \le TA_MAX |  |

| VDD — Operating Supply Voltage <sup>(1)</sup>                                                 |  |

| PIC16LF15325/45                                                                               |  |

| VDDMIN (Fosc ≤ 16 MHz) +1.8V                                                                  |  |

| VDDMIN (Fosc ≤ 32 MHz)                                                                        |  |

| VDDMAX                                                                                        |  |

| PIC16F15325/45                                                                                |  |

| VDDMIN (Fosc ≤ 16 MHz)                                                                        |  |

| VDDMIN (Fosc ≤ 32 MHz)                                                                        |  |

| VDDMAX                                                                                        |  |

| TA — Operating Ambient Temperature Range                                                      |  |

| Industrial Temperature                                                                        |  |

| Ta_min                                                                                        |  |

| Ta_max                                                                                        |  |

| Extended Temperature                                                                          |  |

| TA_MIN                                                                                        |  |

| Ta_max                                                                                        |  |

| Note 1: See Parameter Supply Voltage, DS Characteristics: Supply Voltage.                     |  |

| TABLE 37-9: PLL SI | PECIFICATIONS |

|--------------------|---------------|

|--------------------|---------------|

| Standar       | d Operatir | ng Conditions (unless otherwise stated) VD  | D ≥ 2.5V |       |                     | $\langle \rangle$ |            |

|---------------|------------|---------------------------------------------|----------|-------|---------------------|-------------------|------------|

| Param.<br>No. | Sym.       | Characteristic                              | Min.     | Тур†  | Max.                | Units             | Conditions |

| PLL01         | FPLLIN     | PLL Input Frequency Range                   | 4        | _     | 8                   | MHz               | $\searrow$ |

| PLL02         | FPLLOUT    | PLL Output Frequency Range                  | 16       | —     | 32                  | MHz               | Note 1     |

| PLL03         | TPLLST     | PLL Lock Time from Start-up                 | _        | 200 🦯 | $\langle - \rangle$ | _µ\$              | -          |

| PLL04         | FPLLJIT    | PLL Output Frequency Stability (Jitter)     | -0.25    | _ \   | 0.25                | ~%/               |            |

| *             | These p    | arameters are characterized but not tested. |          |       |                     |                   |            |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance t only and are not tested.

Note 1: The output frequency of the PLL must meet the Fosc requirements listed in Parameter D002.

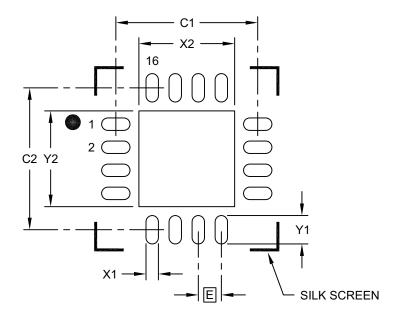

## 16-Lead Ultra Thin Plastic Quad Flat, No Lead Package (JQ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

| Units                      |    | MILLIMETERS |      |      |

|----------------------------|----|-------------|------|------|

| Dimension Limits           |    | MIN         | NOM  | MAX  |

| Contact Pitch              | E  | 0.65 BSC    |      |      |

| Optional Center Pad Width  | X2 |             |      | 2.70 |

| Optional Center Pad Length | Y2 |             |      | 2.70 |

| Contact Pad Spacing        | C1 |             | 4.00 |      |

| Contact Pad Spacing        | C2 |             | 4.00 |      |

| Contact Pad Width (X16)    | X1 |             |      | 0.35 |

| Contact Pad Length (X16)   | Y1 |             |      | 0.80 |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2257A